Настоящее изобретение относится к полупроводниковому запоминающему устройству, содержащему схему обнаружения и корректировки ошибок (ECC). В более узком смысле, это изобретение относится к схеме обнаружения и корректировки множественных ошибок (ECC), вмонтированной в полупроводниковое запоминающее устройство, имеющее некоторое множество подобластей памяти.

В связи с тем, что удельная емкости (плотность монтажа) полупроводниковых запоминающих устройств постоянно увеличивается, серьезным фактором, в значительной степени влияющим на эффективность и надежность полупроводниковых запоминающих устройств, становятся сбойные или синдромные биты, образовавшиеся на стадии изготовления или в результате воздействия на кристалл памяти пиковых напряжений. В настоящее время включение схемы ECC является общей тенденцией, особенно, для таких запоминающих устройств, как программируемые постоянные запоминающие устройства с электрическим стиранием (EEPROM - electrically erasable and programmable read only memory) или запоминающие устройства для хранения масок, которые, будучи энергонезависимыми запоминающими устройствами, требуют высокой надежности. Хотя применение схемы ECC создает дополнительные проблемы, такие как увеличение размеров микросхемы ввиду необходимости размещения ячеек для хранения битов четности, а также снижение быстродействия, тем не менее, повышенный в результате уровень надежности и эффективности достаточно велик, чтобы компенсировать эти неудобства. В частности, в высоко интегрированном ПЗУ применение резервирования затруднено, поэтому для повышения эффективности и надежности такого устройства целесообразно использование схемы ECC. Принцип действия схемы ECC заключается в следующем. В процессе операции ввода на основании входных данных формируются биты четности, которые затем хранятся вместе с информационными битами. В процессе операции вывода информационные биты и сформированные на основании входных данных биты четности сравниваются между собой для обнаружения и корректировки ошибок. Таким образом, биты четности содержат информацию, полученную на основании входных данных. Например, число требуемых битов четности на основании определенного числа информационных битов определяется в соответствии с кодом Хемминга, получаемым из следующего неравенства:

2k ≥ m + k + 1,

где m обозначает число информационных битов, а k число битов четности. Следовательно, согласно этому неравенству, когда число информационных битов равно восьми, число битов четности будет равно четырем. Аналогичным образом, для шестнадцати информационных битов получим пять битов четности.

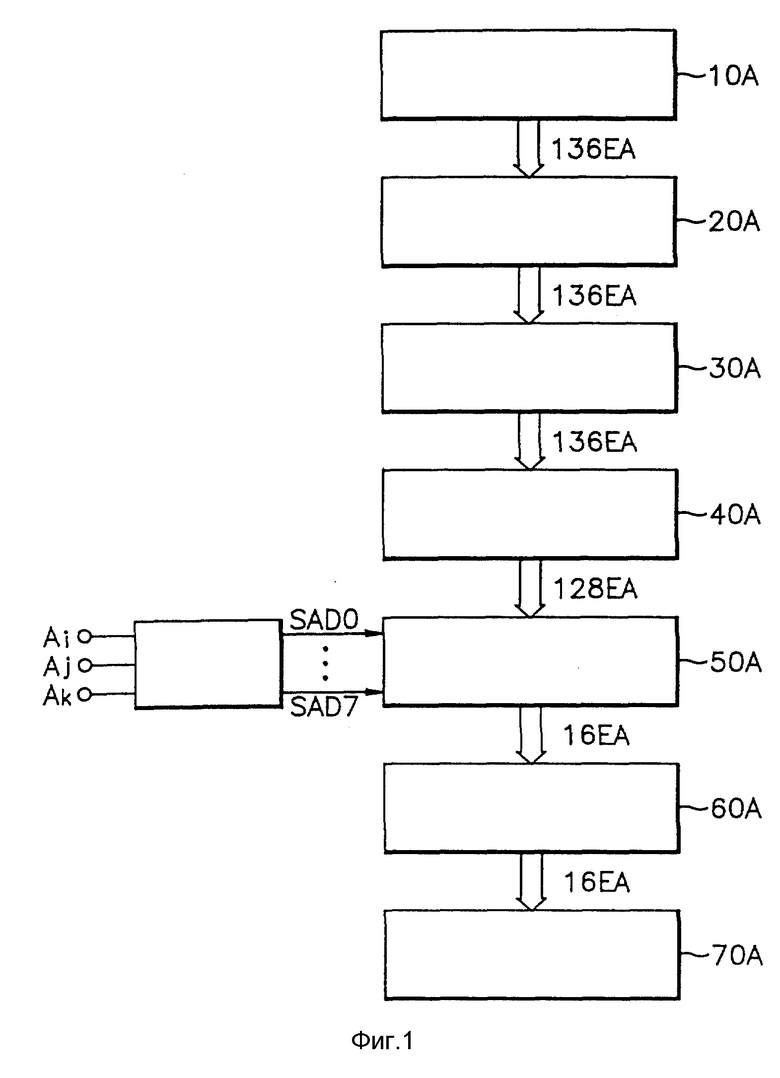

В связи с этим, на фиг. 1 представлена блок-схема известного полупроводникового запоминающего устройства, имеющего схему ECC на 128 бит, а число битов четности равно восьми. Полупроводниковое запоминающее устройство, представленное на фиг. 1, включает в себя область памяти 10A, группу усилителей считывания 20A, следующих для считывания данных из области памяти 10A, схему защелки 30A для запирания выходного сигнала группы усилителей 20A, схему ECC 40A для восстановления синдромного бита, выходной дешифратор для последовательного доступа к 128 битам блоками по 16 бит посредством сигналов предварительной дешифрации SAD0-SAD7, генерируемых предварительным дешифратором 80A, выходной буфер данных 60A для выдачи выходных данных на выходную шину 70A блоками по 16 бит. В процессе доступа к данным полупроводникового запоминающего устройства, представленного на фиг. 1, 128 битов данных, пройдя группу усилителей считывания 20A, схему защелки 30A и схему ECC 40A, поступают на выход последовательными блоками по 16 бит таким образом, что доступ к данным может быть осуществлен с высокой скоростью. Такой быстрый способ доступа к памяти называется "постраничным режимом", где блок данных состоит из 16 битов. Однако, ввиду того, что группа усилителей считывания 20A, схема защелки 30A и схема ECC 40A активизируются одновременно как в нормальном, так и в постраничном режимах, то потребление энергии в обоих режимах одинаково. В целях эффективного потребления энергии необходимо проводить четкую границу между постраничным и нормальным режимами. Однако, в случае представленной на фиг. 1 обычной архитектуры разграничение между нормальным и постраничным режимами неосуществимо.

Краткое описание изобретения

Целью настоящего изобретения является создание полупроводникового запоминающего устройства со встроенной схемой ECC, сокращающего потребление энергии в процессе операции доступа к данным в нормальном режиме.

Другой целью настоящего изобретения является создание полупроводникового запоминающего устройства со встроенной схемой ECC, обладающего простым способом разграничения между нормальным и постраничным режимами.

Таким образом, в соответствии с настоящим изобретением полупроводниковое запоминающее устройство включает в себя область памяти, разделенную на некоторое множество подобластей памяти, каждая из которых имеет как обычные ячейки памяти, так и ячейки для хранения битов четности,

совокупность групп усилителей считывания, каждая из которых соединена с соответствующей подобластью памяти из указанного множества подобластей для осуществления операции считывания данных из подобластей памяти,

совокупность схем обнаружения и корректировки ошибок, каждая из которых соединена с соответствующей группой усилителей считывания для исправления синдромных битов в соответствующей подобласти памяти,

выходные дешифраторы, каждый из которых соединен с выходом соответствующей схемы обнаружения и корректировки ошибок.

Таким образом, в том случае, если полупроводниковое запоминающее устройство будет функционировать в нормальном режиме, то будет задействована только одна подобласть памяти, а если полупроводниковое запоминающее устройство будет функционировать в постраничном режиме, то будут задействованы сразу же подобласти памяти.

Преимущество настоящего изобретения заключается в том, что в полупроводниковом запоминающем устройстве, имеющем функцию ECC, потребление энергии в нормальном режиме доступа к данным ниже по сравнению с постраничным режимом.

Еще одним преимуществом настоящего изобретения является то, что переход между нормальным и постраничным режимами доступа к данным может осуществляться посредством изменения металлического слоя, который формируется в верхней части полупроводникового запоминающего устройства.

Краткое описание рисунков.

Преимущества и цели настоящего изобретения станут более очевидными в процессе подробного описания предпочтительного варианта, которое иллюстрируется прилагаемыми рисунками.

На фиг. 1 представлена блок-схема полупроводникового запоминающего устройства, использующего известную схему ECC на 128 бит.

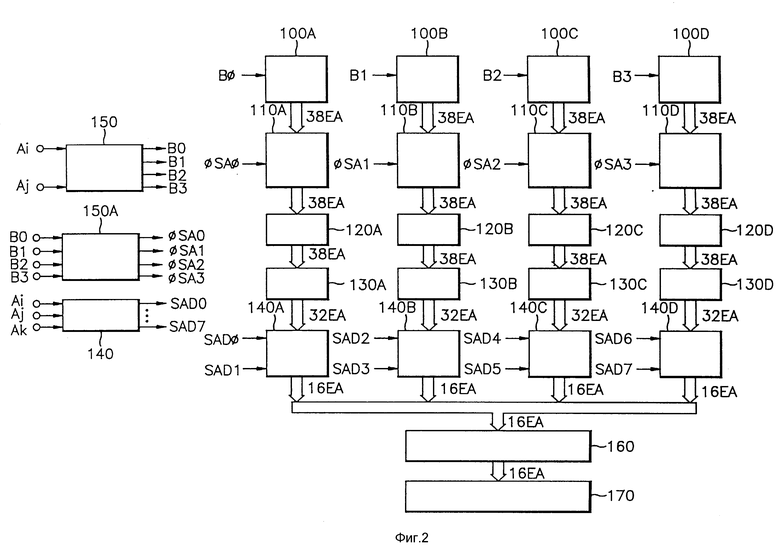

На фиг. 2 представлена блок-схема полупроводникового запоминающего устройства, использующего схему обнаружения и корректировки множественных ошибок (multy-ECC), причем полупроводниковое запоминающее устройство находится в нормальном режиме доступа к данным в соответствии с настоящим изобретением.

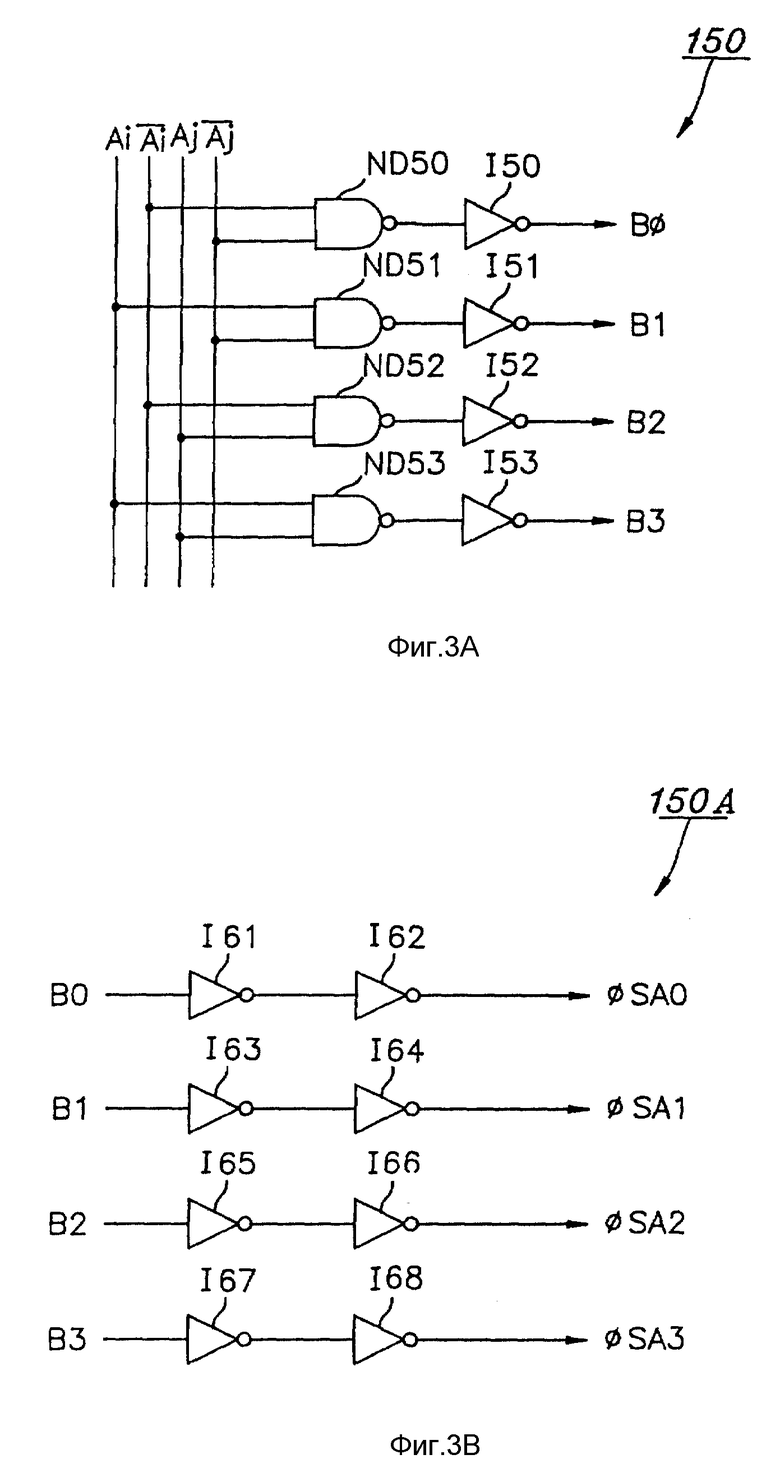

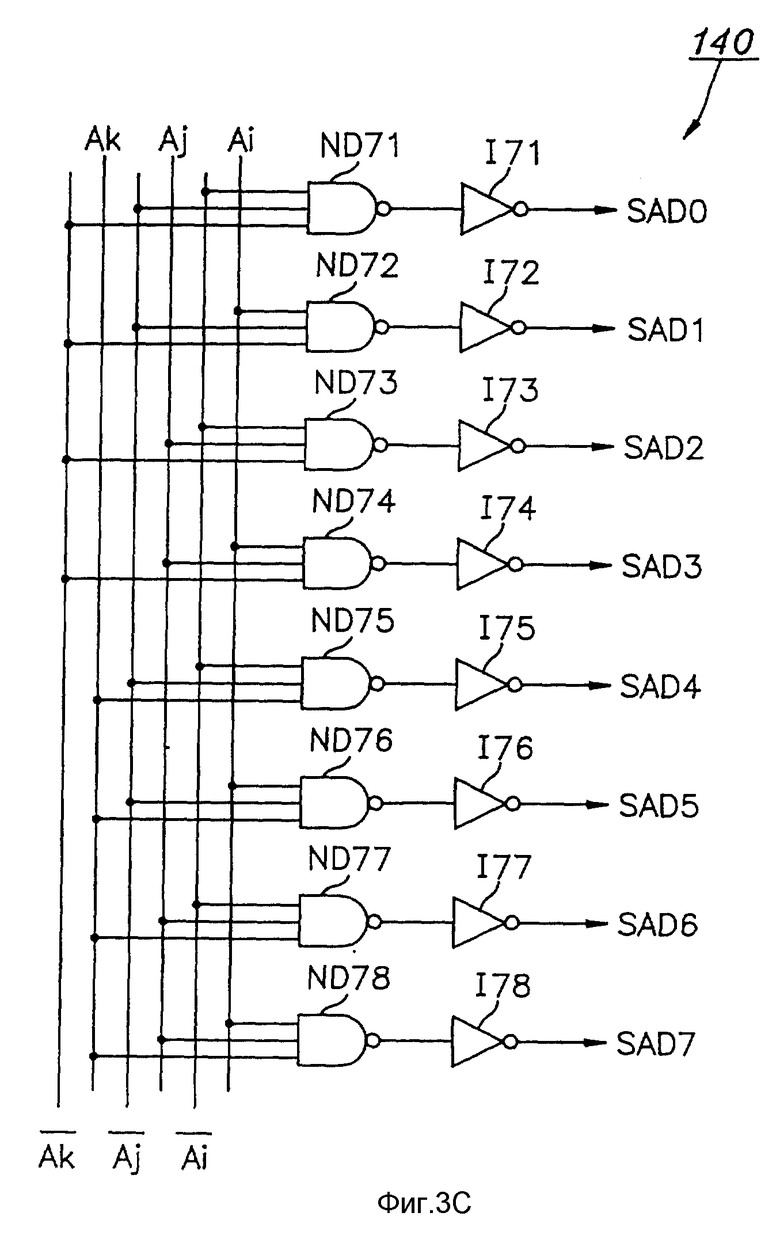

На фиг. 3A представлена схема первого дешифратора, представленного на фиг. 2.

На фиг. 3B представлена схема устройства определения адреса перехода, представленного на фиг. 2.

На фиг. 3C представлена схема второго дешифратора, представленного на фиг. 2.

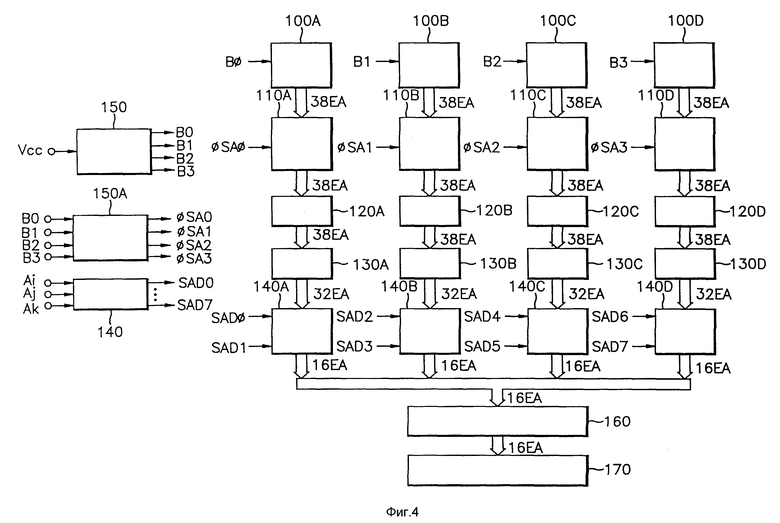

На фиг. 4 представлена функциональная блок-схема полупроводникового запоминающего устройства, использующего схему multy-ECC, причем полупроводниковое запоминающее устройство находится в постраничном режиме доступа к данным в соответствии с настоящим изобретением.

Подробное описание предпочтительного варианта.

На фиг. 2 представлена архитектура полупроводникового запоминающего устройства, содержащего схему multy-ECC в соответствии с настоящим изобретением, когда полупроводниковое запоминающее устройство функционирует в нормальном режиме доступа к данным (здесь и далее для кратности будет называться "нормальный режим"). Область памяти разбивается на четыре подобласти памяти 100A, 100B, 100C, 100D, каждая из которых содержит обычные ячейки памяти и ячейки для хранения битов четности. Внешние схемы, соответствующие подобластям памяти, делятся на четыре части, состоящие из четырех групп усилителей считывания 110A, 110B, 110C, 110D, каждая из которых содержит усилители информационного сигнала и усилители сигнала четности, причем четыре группы усилителей соединены с четырьмя подобластями памяти 100A, 100B, 100C, 100D, соответственно,

четырех схем защелки 120A, 120B, 120C, 120D для запирания выходных сигналов, поступающих от групп усилителей считывания 110A, 110B, 110C, 110D соответственно,

четырех схем ECC 130A, 130B, 130C, 130D (все вместе могут также называться "схема multy-ECC"), соединенных соответственно через четыре схемы защелки 120A, 120B, 120C, 120D с четырьмя группами усилителей считывания 110A, 110B, 110C, 110D для исправления синдромных битов,

выходных дешифраторов 140A, 140B, 140C, 140D, соединенных соответственно со схемами ECC 130A, 130B, 130C, 130D,

выходного буфера 160 для приема выходных сигналов от дешифраторов 140A, 140B, 140C, 140D, и

выходной шины 170. Кроме того имеется схема 150 выбора блока памяти, получающая в нормальном режиме адресные сигналы Ai, Aj (в постраничном режиме на вход схемы выбора блока подается напряжение питания VCC) и генерирующая сигналы В0-В3 выбора блока памяти, использующиеся для выбора одной из подобластей памяти 100A, 100B, 100C, 100D. Имеется также схема 150A выбора группы усилителей считывания, получающая сигналы В0-В3 выбора блока памяти от схемы 150 выбора блока памяти и генерирующая сигналы ФSA0-ФSA3 для выбора одной из групп усилителей считывания 110A, 110B, 110C, 110D. Кроме того, имеется предварительный дешифратор 140, получающий адресные сигналы Ai, Aj, Ak и генерирующий сигналы предварительной дешифрации SAD0-SAD7, которые поступают на выходные дешифраторы 140A, 140B, 140C, 140D, посредством чего 32-битовые выходные сигналы соответствующих схем ECC 130A, 130B, 130C, 130D делятся в каждом дешифраторе на блоки по 16 бит и последовательно передаются в выходной буфер 160.

Как показано на фиг. 3A, схема 150 выбора блока памяти состоит из четырех элементов "НЕ-И" ND50-ND53, получающих в нормальном режиме адресные сигналы Ai, Aj и четырех инверторов 150-153, получающих выходные сигналы, сгенерированные элементами "НЕ-И" ND50-ND53. Необходимо заметить, что в постраничном режиме на четыре входные линии адресных сигналов Ai, Aj подается напряжение VCC посредством внутренних соединений металлического слоя.

Схема 150A выбора группы усилителей считывания, как показано на фиг. 3B, содержит четыре одинаковые схемы, соответствующие четырем сигналам выбора блока памяти. Каждая схема состоит из двух инверторов. Инверторы 161, 163, 165, 167 получают сигналы B0-B3 выбора блока памяти, а инверторы 162, 164, 166, 168, получая выходные сигналы инверторов 161, 163, 165, 167, генерируют сигналы фSA0-фSA3 выбора группы усилителей считывания.

Предварительный дешифратор 140, как показано на фиг. 3c, состоит из элементов "НЕ-И", которые получают адресные сигналы Ai, Aj, Ak и инверторов 171-178, которые генерируют сигналы предварительной дешифрации SAD0-SAD7 для управления количеством данных, проходящих через выходные дешифраторы 140A, 140B, 140C, 140D (фиг. 2).

Так как область памяти разделена на четыре подобласти, то группы усилителей считывания, схемы защелки, схемы ECC и выходные дешифраторы делятся на четыре секции в соответствии с количеством подобластей памяти. Обратимся к фиг. 2. Каждой группе усилителей считывания требуется 38 усилителей. Это объясняется тем, что требуется 32 усилителя считывания для считывания обычных данных и 6 усилителей считываемых битов четности для исправления одиночных синдромных битов среди 32 битов данных.

Отличительные черты архитектуры, представленной на фиг. 3, заключаются в том, что область памяти разделена на четыре подобласти памяти в целях сокращения потребляемой энергии и повышения быстродействия. В то же время она содержит схему ECC, причем для каждой подобласти памяти имеется своя ECC для исправления синдромных битов. Поскольку четыре подобласти памяти 100A, 100B, 100C, 100D обрабатываются независимо друг от друга, для каждой из подобластей памяти 100A, 100B, 100C, 100D имеется соответствующая схема ECC 130A, 130B, 130C, 130D. Таким образом, конкретная схема, принадлежащая определенной подобласти памяти, изолирована от помех со стороны смежных групп усилителей считывания, относящихся к другой подобласти памяти. В то время, как в обычной схеме, представленной на фиг. 1, схема ECC функционирует на основании комбинации входных сигналов от 128 усилителей считывания, настоящее изобретение вместо этого предлагает архитектуру, в которой 32 битовые схемы ECC функционируют на основании комбинации выходных сигналов от 32 усилителей считывания для каждой подобласти памяти.

На фиг. 4 представлена архитектура описанного полупроводникового запоминающего устройства, находящегося в постраничном режиме доступа к данным X (здесь и далее для краткости будет называться "постраничный режим"). Архитектура полупроводникового запоминающего устройства в этом режиме такая же, как и в нормальном, за исключением того, что на вход схемы 150 выбора блока памяти подаются не адресные сигналы Ai, Aj, а напряжение питания VCC.

Это может быть достигнуто посредством изменения шаблона внутренних соединений металлического слоя, определяющего какие именно сигналы подаются на вход схемы 150 выбора блока памяти (адресные сигналы Ai, Aj или напряжение питания VCC). Такая операция осуществляется на стадии формирования металлического слоя в процессе изготовления полупроводникового запоминающего устройства.

Ниже будет описано функционирование в нормальном и постраничном режимах в соответствии со схемами, представленными на фиг. 2 и 4.

В нормальном режиме на вход схемы 150 выбора памяти подаются адресные сигналы Ai, Aj, после чего выбирается одна из подобластей памяти. Предположим, что был активизирован сигнал B0 выбора памяти и выбрана подобласть памяти 100A. Далее данные считываются из подобласти памяти 100A и усиливаются группой усилителей считывания 110A, причем информационные биты считываются усилителями информационного сигнала, а биты четности считываются усилителями сигналов четности из группы усилителей считывания 110A. Затем данные запираются в схеме защелки 120A и проходят схему ECC 130A. После этого данные дешифруются в выходном дешифраторе 140A и поступают в выходной буфер 160. В данном режиме невыбранные подобласти памяти 100B, 100C, 100D группы усилителей считывания 110B, 110C, 110D, схемы защелки 120B, 120C, 120D и выходные дешифраторы 140B, 140C, 140D находятся в отключенном состоянии, в то время как задействованы выбранная подобласть памяти 100A, группа усилителей считывания 110A, схема защелки 120A, схема ECC 130A, и выходной дешифратор 140A. Таким образом, потребление энергии, очевидно, ниже чем в случае обычной схемы полупроводникового запоминающего устройства, функционирующего в нормальном режиме доступа к данным.

В то же самое время, полупроводниковое запоминающее устройство может использоваться и в постраничном режиме (одна страница эквивалента восьми словам) с помощью металлического слоя, составляющего верхнюю часть микросхемы, в результате чего на вход схемы 150 выбора блока памяти подается напряжение питания VCC вместо адресных сигналов Ai, Aj. Обратимся к фиг. 4. 38-битовые данные, состоящие из 32 информационных битов и 6 битов четности, считываются в определенном порядке из каждой подобласти памяти 100A-100D, поскольку активизированы все сигналы B0-B3 выбора блока памяти благодаря высокому логическому уровню напряжения питания. Обратимся к фиг. 3A. Так как в постраничном режиме на входы элементов "НЕ-И" ND50-ND53 подается напряжение питания, которое является напряжением высокого логического уровня для схем типа КМОП (CMOS), следовательно, сигналы B0-B3 выбора блока памяти, будучи выходными сигналами инверторов 150-153, имеют высокий логический уровень сигнала, т.е. они активизированы. Поэтому выбираются сразу все подобласти памяти 100A-100D. Обратимся к фиг. 3B. Активизированные сигналы B0-B3 выбора блока памяти вызывают активизацию сигналов фSA0-фSA3 выбора группы усилителей считывания, что влечет за собой активизацию всех групп усилителей считывания 110A-110D. После операции параллельного доступа к подобластям памяти 100A-100D, пройдя схемы защелки 120A-120D, 38-битовые данные, содержащие 32 информационных бита и 6 битов четности, поступают на вход каждой из схем ECC 130A-130D. В результате их работы с помощью 6 битов четности обнаруживается и исправляется синдромный бит в составе 32 информационных битов в каждой схеме ECC. Затем восстановленные в каждой из схем ECC 130A-130D 32-битовые данные поступают в выходные дешифраторы 140A-140D. Каждый выходной дешифратор направляет 16-битовые блоки данных в выходной буфер 160 под управлением сигналов SAD0-SAD7 предварительной дешифрации, генерируемых предварительным дешифратором 140, представленным на фиг. 3C. Функционирование выходных дешифраторов 140A-140D такое же, как и выходного дешифратора 50A на фиг. 1.

Примеры архитектур, представленные на фиг. 2 и 4, являются наиболее предпочтительными вариантами настоящего изобретения. Для специалиста в данной области должно быть совершено очевидно, что в предлагаемую архитектуру могут вносится различные изменения, касающиеся формы элементов и некоторых деталей.

Как описано выше, настоящее изобретение реализует схему обнаружения и корректировки множественных ошибок (multy-ECC), в которой совокупности областей памяти соответствует совокупность схем ECC. Более того, архитектура полупроводникового запоминающего устройства делает возможным переход между нормальным и постраничным режимами посредством изменения соединений металлического слоя, в частности, со средствами выбора блока памяти. В результате, настоящее изобретение обладает существенным преимуществом, сокращая потребление энергии полупроводниковым запоминающим устройством, имеющим функцию ECC.

Описание к фиг. 1

10A - Область памяти

20A - Группа усилителей считывания

30A - Схема защелки

40A - Схема обнаружения и корректировки ошибок (ECC)

50A - Выходной дешифратор

60A - Выходной буфер

70A - Выходная шина

pre-decoder - выходной дешифратор.

Описание к фиг. 2

100A, 100B, 100C, 100D - Подобласть памяти

110A, 110B, 110C, 110D - Группа усилителей считывания

120A, 120B, 120C, 120D - Схема защелки

130A, 130B, 130C, 130D - Схема обнаружения и корректировки ошибок (ECC)

140A, 140B, 140C, 140D - Выходной дешифратор

140 - Предварительный дешифратор

150 - Схема выбора блока памяти

150A - Схема выбора группы усилителей считывания

160 - Выходной буфер

170 - Выходная шина.

Описание к фиг. 4

100A, 100B, 100C, 100D - Подобласть памяти

110A, 110B, 110C, 110D - Группа усилителей считывания

120A, 120B, 120C, 120D - Схема защелки

130A, 130B, 130C, 130D - Схема обнаружения и корректировки ошибок (ECC)

140A, 140B, 140C, 140D - Выходной дешифратор

140 - Предварительный дешифратор

150 - Схема выбора блока памяти

150A - Схема выбора группы усилителей считывания

160 - Выходной буфер

170 - Выходная шина

VCC - Напряжение питания (V - voltage - напряжение, cc - continious current - постоянный ток)

Изобретение относится к полупроводниковому запоминающему устройству, содержащему схему обнаружения и исправления множественных ошибок. Технический результат изобретения заключается в сокращении потребления энергии в процессе доступа к данным в нормальном режиме. Запоминающее устройство состоит из области памяти, разделенной на множество подобластей памяти. Каждая из подобластей имеет как обычные ячейки памяти, так и ячейки для хранения битов четности. Устройство также включает совокупность групп усилителей считывания. Каждая группа усилителей соединена с соответствующей подобластью памяти. В состав устройства входит совокупность схем обнаружения и корректировки ошибок, каждая из которых служит для исправления синдромных битов в составе данных памяти, а также выходные дешифраторы. Каждый из дешифраторов соединен с выходом соответствующей схемы обнаружения и корректировки ошибок. Когда полупроводниковое запоминающее устройство функционирует в нормальном режиме, активизируется только одна из подобластей памяти. Когда устройство функционирует в постраничном режиме, активизируются сразу все подобласти памяти. 1 з.п.ф-лы, 6 ил.

| US 5056089 A, 08.10.91 | |||

| US 4937830 A, 26.06.90 | |||

| US 4706249 A, 10.11.87 | |||

| US 4878220 A, 31.10.89 | |||

| Селлерс Ф | |||

| Методы обнаружения ошибок в работе ЭЦВМ | |||

| - М.: Мир, 1972, с.265 - 268. |

Авторы

Даты

1999-08-20—Публикация

1993-07-29—Подача