УРОВЕНЬ ТЕХНИКИ

Турбокодирование является мощным алгоритмом непосредственного исправления ошибок (FEC), который достигает эффективности кодирования, близкого к пределу Шеннона. Турбокодеры и турбодекодеры приняты для использования на физических уровнях в ряде стандартов беспроводной связи, включающих в себя WCDMA (широкополосный CDMA), CDMA2000 (кодовое разделение каналов с многостанционным доступом), IEEE-802.16e (т.е. беспроводной широкополосный доступ, WiBro) и другие. Эти стандарты действуют при разных скоростях передачи данных и реализуют турбокодеры и турбодекодеры, которые оптимизированы только для одного или двух конкретных стандартов. Также большинство традиционных турбокодеров/декодеров действует при относительно низких скоростях передачи данных.

Программно-определяемое радиоустройство (SDR) использует перестраиваемое (реконфигурируемое) аппаратное обеспечение, которое может быть запрограммировано эфирно для функционирования по различным стандартам беспроводной связи. Например, приемопередатчик SDR в беспроводном портативном компьютере или PDA может конфигурироваться с помощью различных загрузок программного обеспечения, чтобы функционировать в беспроводной сети IEEE-802.11x, беспроводной сети CDMA2000, беспроводной сети OFDM/OFDMA (мультиплексирование с ортогональным частотным разделением сигналов/доступ к OFDM), беспроводной сети GSM (глобальная система связи с подвижными объектами) или в других типах сетей. Многие из этих стандартов беспроводной связи требуют использования турбодекодеров.

Однако традиционные турбодекодеры имеют значительные недостатки в отношении приложений SDR. Как отмечено выше, традиционные турбодекодеры оптимизированы для декодирования только одного или двух конкретных стандартов. Если устройству SDR необходимо поддерживать много стандартов беспроводной связи, должен быть внедрен более чем один турбодекодер в устройстве SDR. Это ведет к сложной конструкции приемопередатчика, которая делает неэффективной использование пространства микросхемы и имеет высокую мощность рассеивания. Кроме того, некоторые из более новых стандартов беспроводной связи действуют при относительно высоких скоростях передачи данных (например, WiBro, технология высокоскоростной пакетной передачи в нисходящем канале (HSDPA) и тому подобное). Турбодекодер, который оптимизирован на основе скорости и потребляемой мощности для стандарта низкой скорости передачи данных, вряд ли должен быть оптимизирован на основе скорости и потребляемой мощности для стандарта высокой скорости передачи данных и наоборот. Таким образом, традиционные конструкции турбодекодера не подходят для использования в приложениях SDR.

Следовательно, существует необходимость в данной области техники в улучшенном перестраиваемом турбодекодере для использования в программно-определяемой радиосистеме (SDR).

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

Предложен перестраиваемый турбодекодер. Перестраиваемый турбодекодер содержит N обрабатывающих блоков, причем каждый из N обрабатывающих блоков принимает выборки программируемых входных данных и декодирует принятые выборки программируемых входных данных. N обрабатывающих блоков действуют независимо из условия, что первый из N обрабатывающих блоков может быть выбран для декодирования принятых выборок программируемых входных данных, тогда как второй из N обрабатывающих блоков может быть выключен. Число N обрабатывающих блоков, которые выбраны для декодирования принятых выборок программируемых входных данных, определяется скоростью передачи данных принятых выборок программируемых входных данных.

В одном варианте осуществления перестраиваемый турбодекодер дополнительно содержит N запоминающих устройств входных данных, которые хранят принятые выборки программируемых входных данные. Каждый из N обрабатывающих блоков выполнен с возможностью считывания данных из каждого и записи данных в каждое из N запоминающих устройств входных данных.

В другом варианте осуществления перестраиваемый турбодекодер дополнительно содержит N запоминающих устройств внешней информации, которые хранят внешнюю информацию, сформированную с помощью N обрабатывающих блоков. Каждый из N обрабатывающих блоков выполнен с возможностью считывания внешней информации из каждого и записи внешней информации в каждое из N запоминающих устройств внешней информации.

Перед изложением подробного описания изобретения, приведенным ниже, может быть целесообразно изложить определения некоторых слов и фраз, используемых в этом документе: термины "включать в себя" и "содержать", а также их производные означают включение без ограничения; термин "или" является включающим, означающим и/или; фразы "ассоциативно связанный с" и "ассоциативно связанный с этим", а также их производные могут означать включать или быть включенным в, взаимодействовать, связывать(ся), содержать, содержаться в чем-либо, соединяться с чем-то или с помощью чего-то, связываться с чем-то или с помощью чего-то, осуществлять связь с чем-либо, взаимодействовать с чем-либо, перемежаться, располагаться рядом, быть близким к, быть связанным с чем-либо или с помощью чего-либо, иметь, иметь свойство чего-либо, или тому подобное; и термин "контроллер" означает любое устройство, систему или ее часть, которая управляет, по меньшей мере, одной операцией, подобное устройство может быть реализовано в аппаратном обеспечении, встроенном программном обеспечении или программном обеспечении, или в сочетании, по меньшей мере, двух из них. Следует заметить, что функциональные возможности, ассоциативно связанные с любым конкретным контроллером, могут быть централизованными и распределенными, локально либо дистанционно. Определения конкретных слов и фраз предусмотрены в этом документе, обычным специалистам в данной области техники следует понимать, что во многих, если не в большинстве примеров, подобные определения применяют к предшествующему, а также будущему использованию подобным образом определенных слов и фраз.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Для более полного понимания настоящего раскрытия изобретения и его преимуществ, в настоящий момент сделана ссылка на последующее описание при совместном рассмотрении с сопроводительными чертежами, на которых подобные цифры ссылок представляют аналогичные части:

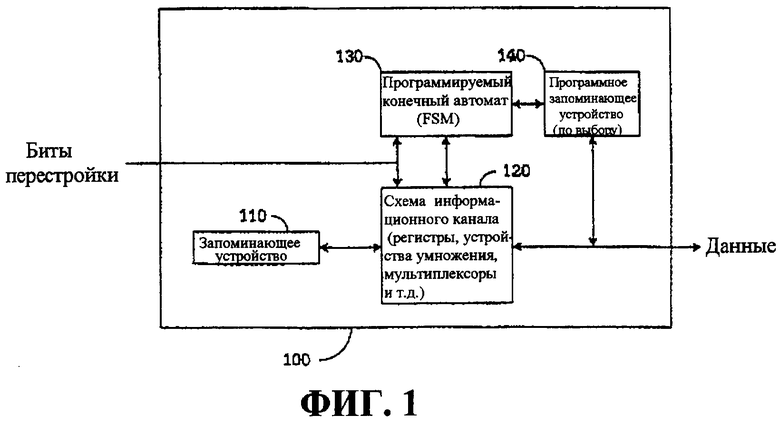

Фиг.1 является блок-схемой CRISP устройства высокого уровня, которое может использоваться для реализации перестраиваемого турбодекодера;

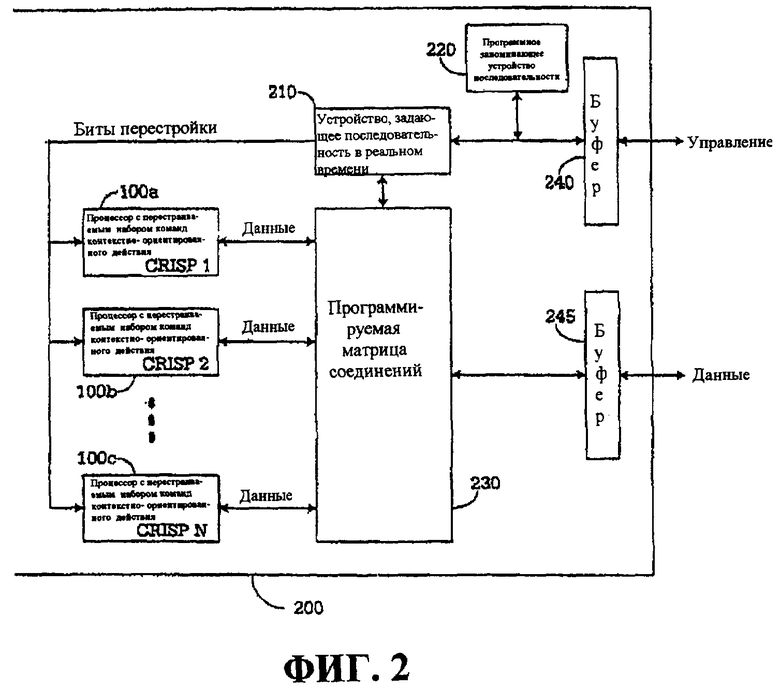

Фиг.2 является блок-схемой перестраиваемой системы обработки высокого уровня;

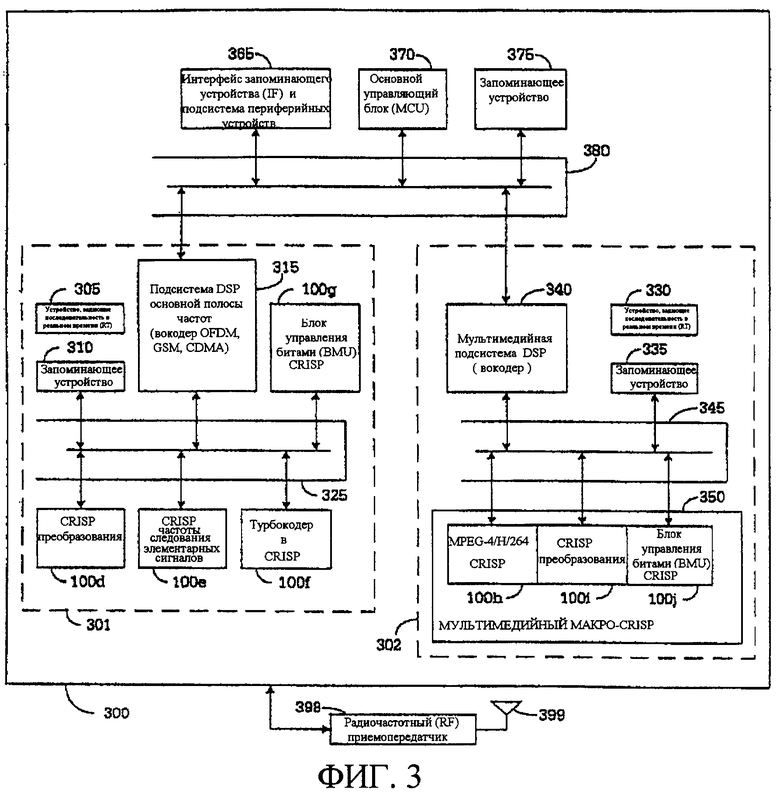

Фиг.3 является блок-схемой многостандартной программно-определяемой радиосистемы (SDR) высокого уровня, которая реализует перестраиваемый турбодекодер, используя, по меньшей мере, одно устройство CRISP;

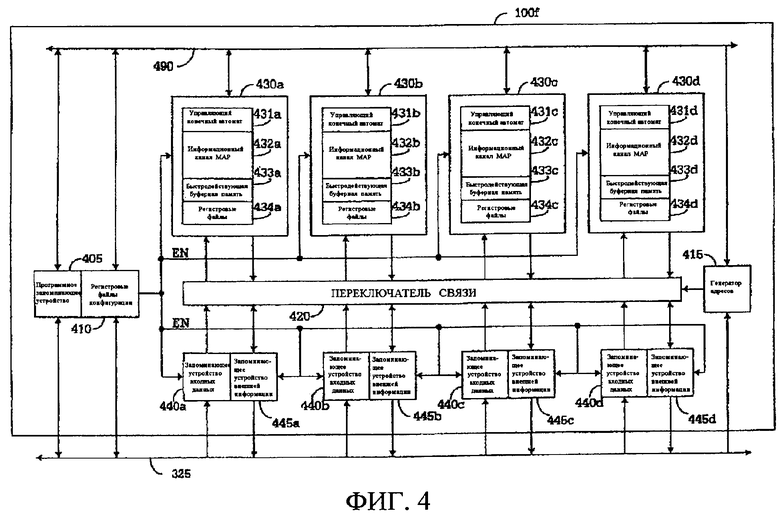

Фиг.4 является блок-схемой перестраиваемого турбодекодера, реализованного в CRISP согласно принципам раскрытия изобретения;

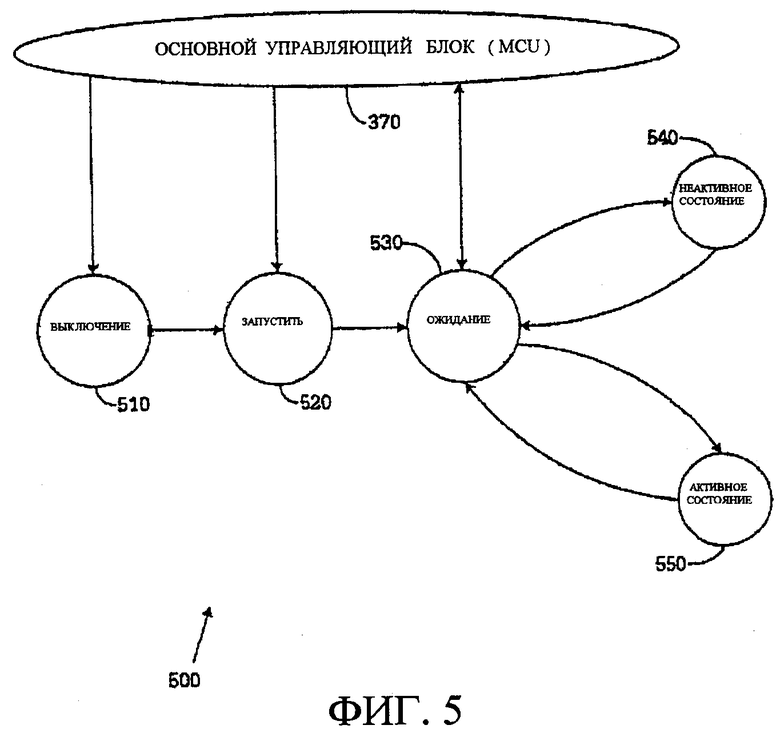

Фиг.5 является диаграммой состояния, которая иллюстрирует операции по управлению мощностью в перестраиваемом турбодекодере CRISP согласно принципам настоящего раскрытия изобретения.

ПОДРОБНОЕ ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Фиг.1-5, рассматриваемые ниже, и различные варианты осуществления, используемые для описания принципов настоящего раскрытия изобретения в этом патентном документе, приведены лишь с помощью изображения и не должны толковаться в любом случае как ограничение объема раскрытия изобретения. Специалисты в данной области техники поймут, что принципы настоящего раскрытия изобретения могут быть реализованы в любой соответствующим образом скомпонованной системе обработки.

Перестраиваемый турбодекодер, раскрытый в данном документе, предусматривает высокую степень параллелизма для поддержки стандартов высокой скорости передачи данных. Конечная скорость нисходящей линии связи WiBro составляет 12 Мб/с и HSDPA достигает пиковой скорости передачи данных до 14,4 Мб/с. Также турбодекодер должен выполнять несколько итераций для достижения оптимального функционирования. Раскрытая архитектура турбодекодера использует параллелизм для достижения необходимой пропускной способности при высоких скоростях передачи данных.

Перестраиваемый турбодекодер поддерживает работу в нескольких режимах для декодирования в различных стандартах передачи данных, включая WCDMA, CDMA2000, IEEE-802.16e (т.е. WiBro) среди других. Раскрытый турбодекодер также предусматривает адаптивность для поддержания различных скоростей передачи данных. Раскрытая архитектура турбодекодера оптимизируется не только для максимальных скоростей передачи данных, но также для различных диапазонов скорости передачи данных.

Перестраиваемый турбодекодер также минимизирует потребляемую мощность для различных стандартов и скоростей передачи данных, так как турбодекодер может быть реализован в портативных устройствах. В конечном счете перестраиваемый турбодекодер согласно принципам настоящего раскрытия изобретения предусматривает гибкость для конечного пользователя. Хотя конструкция имеет целью турбодекодирование, архитектура не требует жестких ограничений по параметрам. Таким образом, конструкция предусматривает общую платформу декодера с апостериорным максимумом (МАР), которая позволяет конечным пользователям выбирать параметры и алгоритмы на основе требований конечного пользователя.

В одном варианте осуществления раскрытия изобретения перестраиваемый турбодекодер, описанный в данном документе, может быть реализован, используя устройство процессора с перестраиваемым набором команд контекстно-ориентированного действия (CRISP). Устройства CRISP описываются подробно в патентной заявке (США) с серийным №11/123,313, которая была включена посредством ссылки выше.

Фиг.1 является блок-схемой высокого уровня процессора 100 с перестраиваемым набором команд контекстно-ориентированного действия (CRISP), который может использоваться для реализации турбодекодера. CRISP 100 содержит запоминающее устройство 110, программируемая схема 120 тракта данных, программируемый конечный автомат 130 и дополнительное программное запоминающее устройство 140. Контекст является группой команд процессора данных, которые относятся к конкретной функции или приложению, например, команды турбодекодирования. Как описано в патентной заявке (США) с серийным №11/123,313, CRISP 100 реализует только подмножество связанных с контекстом команд оптимальным образом.

Процессор 100 с перестраиваемым набором команд контекстно-ориентированного действия (CRISP) определяет базовый блок аппаратного обеспечения, который обычно состоит из процессорных блоков аппаратного обеспечения более высокого уровня. Принципиальное преимущество в CRISP 100 в том, что CRISP 100 разделяет необходимое приложение на две главные области, область управления и область тракта данных и оптимизирует отдельно каждую область. С помощью выполнения турбодекодирования в CRISP 100 раскрытый в изобретении турбодекодер уменьшает проблемы, связанные с гибкостью и потребляемой мощностью, которые влияют на традиционные турбодекодеры.

Область управления реализована с помощью программируемого конечного автомата 130, который может содержать DSP (цифровой сигнальный процессор), MCU (основной блок управления) или иное устройство предшествующего уровня техники. Программируемый конечный автомат 130 (FCM) конфигурируется с помощью перестраиваемых битов, принятых от внешнего контроллера (не показан). Программируемый FCM 130 может выполнять программу, хранящуюся в ассоциативно связанном дополнительном программном запоминающем устройстве 140. Программа может храниться в программном запоминающем устройстве 140 через линию передачи данных от внешнего контроллера (не показан). Запоминающее устройство 110 используется для хранения данных приложения, используемых с помощью схемы 120 тракта данных.

Программируемая схема 120 тракта данных разделена на множество стандартных блоков, которые выполняют конкретные функции (например, регистрирующие устройства, мультиплексоры, устройства умножения и тому подобное). Каждый из стандартных блоков и перестраиваемый, и программируемый, чтобы обеспечить максимальную гибкость. Деление программируемой схемы 120 тракта данных на функциональные блоки зависит от степени возможности перестройки и возможности программирования, необходимой для конкретного приложения.

Так как различные контексты реализованы с помощью отдельных устройств CRISP, которые работают независимо от других устройств CRISP, которые реализуют турбодекодер, использование одного или более устройств CRISP предусматривает схему эффективного управления мощностью, которая может выключать CRISP, когда CRISP не нужен. Это гарантирует, что только те CRISP, которые необходимы в заданный момент времени, являются действующими, в то время как другие бездействующие CRISP не затрачивают значительную мощность.

Фиг.2 является блок-схемой высокого уровня перестраиваемой системы 200 обработки согласно одному варианту осуществления настоящего раскрытия изобретения. Перестраиваемая система 200 обработки содержит N процессоров с перестраиваемым набором команд контекстно-ориентированного действия, включая примерные CRISP 100a, 100b и 100с, которые произвольно промаркированы CRISP 1, CRISP 2 и CRISP N. Перестраиваемая система 200 обработки дополнительно содержит устройство 210, задающее последовательность в реальном времени, программное запоминающее устройство 220 последовательности, программируемую матрицу 230 соединений и буферы 240 и 245.

Биты перестройки могут загружаться в CRISP 100a, 100b и 100с из линии управления через устройство 210, задающее последовательность в реальном времени и буфер 240. Управляющая программа может также загружаться в программное запоминающее устройство 220 последовательности от линии управления через буфер 240. Устройство 210, задающее последовательность в реальном времени, упорядочивает контексты, которые необходимо выполнять с помощью каждого из CRISP 100a-с извлечением программных команд из программного запоминающего устройства 220 и отправлением битов перестройки в CRISP 100a-с. В примерном варианте осуществления устройство 210, задающее последовательность в реальном времени, может содержать стековый процессор, который подходит для функционирования в качестве планировщика реального времени из-за его низкого времени ожидания и простоты.

Перестраиваемая матрица 230 соединений предоставляет возможность соединения между каждым из CRISP 100a-с и внешней шиной данных через двусторонний буфер 245. В примерном варианте осуществления настоящего раскрытия изобретения каждый из CRISP 100a-с может действовать как ведущее устройство перестраиваемой матрицы 230 соединений и может инициировать адресное обращение. Арбитр шины для перестраиваемой матрицы 230 соединений может быть внутренним по отношению к устройству 210, задающему последовательность в реальном времени.

В примерном варианте осуществления перестраиваемая система 200 обработки может являться, например, сотовым телефоном или аналогичным беспроводным устройством или процессором данных для использования в портативном компьютере. В варианте осуществления беспроводного устройства, основанного на программно-определяемой радио (SDR) архитектуре, каждый из CRISP 100a-с отвечает за выполнение подмножества связанных с контекстом команд, которые ассоциативно связаны с конкретной перестраиваемой функцией. Например, CRISP 100a может быть сконфигурирован для выполнения связанных с контекстом команд, которые обрабатывают сигналы основной полосы частот CDMA или сигналы основной полосы частот OFDMA. CRISP 100b может быть сконфигурирован для выполнения связанных с контекстом команд, которые выполняют турбодекодирование или декодирование Витерби.

Так как устройства CRISP в основном независимы и могут запускаться одновременно, турбодекодер, реализованный, используя одно или более устройств CRISP, имеет преимущество параллелизма в выполнении без потери полной мощности, ассоциативно связанной с выполняющимися параллельными операциями. Тесное взаимодействие и независимость устройств CRISP позволяет конфигурировать их для различных систем и функций, которые могут быть отключены отдельно.

Фиг.3 является блок-схемой высокого уровня многостандартной программно-определяемой радиосистемы (SDR) 300, которая реализует перестраиваемый турбодекодер, используя устройство CRISP. Система 300 SDR может содержать беспроводной терминал (или мобильную станцию, абонентскую станцию и т.д.), которая имеет доступ к беспроводной сети, подобного, например, GSM или сотовому телефону CDMA, PDA (персональный цифровой секретарь) с WCDMA, IEEE-802.11x, возможности OFDM/OFDMA или тому подобное.

Многостандартная система 300 SDR содержит подсистему 301 основной полосы частот, подсистему 302 приложений, интерфейс запоминающего устройства (IF) и подсистему 365 периферийных устройств, основной управляющий блок 370 (MCU), запоминающее устройство 375 и межкомпонентное соединение 380. MCU 370 может содержать, например, традиционный микроконтроллер или микропроцессор (например, х86, ARM (усовершенствованное оборудование на основе RISC), RISC (архитектура микропроцессора на основе сокращённого набора команд), DSP и т.д.). Интерфейс запоминающего устройства и подсистема 365 периферийных устройств может соединять систему 300 SDR с внешним запоминающим устройством (не показано) и с внешними периферийными устройствами (не показаны). Запоминающее устройство 375 хранит данные от других компонентов в системе 300 SDR и от внешних устройств (не показаны). Например, запоминающее устройство 375 может хранить поток выборок входных данных, ассоциативно связанных с преобразованным сигналом с понижением частоты, формируемым радиочастотным (RF) приемопередатчиком 398 и антенной 399, ассоциативно связанной с системой 300 SDR. Межкомпонентное соединение 380 действует как системная шина, которая предоставляет перемещение данных между подсистемами 301 и 302, интерфейсом запоминающего устройства и подсистемой 365 периферийных устройств, MCU 370 и запоминающим устройством 375.

Система 301 основной полосы частот содержит устройство 305, задающее последовательность в реальном времени (RT), запоминающее устройство 310, подсистему 315 DSP основной полосы частот, межкомпонентное соединение 325 и множество процессоров с набором команд контекстно-ориентированного действия (CRISP) специального назначения, которые включают в себя CRISP 100d преобразования, CRISP 100е частоты следования элементарных сигналов, турбодекодер в CRISP 100f и блок управления битами (BMU) CRISP 100g. С помощью примера, CRISP 100d преобразования может реализовать функцию быстрого преобразования Фурье (FFT), CRISP 100е частоты следования элементарных сигналов может реализовать функцию корреляции для сигнала CDMA и турбодекодер в CRISP 100f может реализовать функцию турбодекодера или функцию декодера Витерби. В подобном примерном варианте осуществления CRISP 100d преобразования может принимать выборки сигнала промежуточной частоты (IF), хранящиеся в запоминающем устройстве 375, и выполнять функцию FFT, которая формирует последовательность выборок элементарных сигналов в основной полосе частот. Далее, CRISP 100е частоты следования элементарных сигналов принимает выборки элементарных сигналов от CRISP 100d преобразования и выполняет функцию корреляции, которая формирует последовательность символов данных. Далее, турбодекодер в CRISP 100f принимает символьные данные от CRISP 100е частоты следования элементарных сигналов и выполняет турбодекодирование или декодирование Витерби для восстановления пользовательских данных основной полосы частот. Пользовательские данные основной полосы частот могут затем использоваться подсистемой 302 приложений.

В примерном варианте осуществления настоящего раскрытия изобретения турбодекодер в CRISP 100f может содержать два или более CRISP, которые действуют параллельно. Также, с помощью примера, BMU CRISP 100g может реализовать такие функции, как кодирование с переменной длиной слова, проверка при помощи циклического избыточного кода (CRC), сверточное кодирование и тому подобное. Межкомпонентное соединение 325 действует как системная шина, которая предусматривает перемещение данных между устройством 305, задающим последовательность, запоминающим устройством 310, подсистемой 315 DSP основной полосы частот и CRISP 100d-100g.

Подсистема 302 приложений содержит устройство 330, задающее последовательность в реальном времени (RT), запоминающее устройство 335, мультимедийную подсистему 340 DSP, межкомпонентное соединение 345 и мультимедийный макро-CRISP 350. Мультимедийный макро-CRISP 350 содержит множество процессоров с набором команд контекстно-ориентированного действия специального назначения, включая MPEG-4/H.264 CRISP 100h, CRISP 100i преобразования и BMU CRISP 100j. В примерном варианте осуществления раскрытия настоящего изобретения MPEG-4/H.264 CRISP 100h выполняет функции оценки перемещения и CRISP 100d преобразования выполняет функцию дискретного косинусного преобразования (DCT). Межкомпонентное соединение 380 предусматривает передачу данных между RT-устройством 330, задающим последовательность, запоминающим устройством 335, мультимедийной подсистемой 340 DSP и мультимедийным макро-CRISP 350.

В варианте осуществления на фиг.3, использование устройств CRISP позволяет перестраивать подсистему 302 приложений многостандартной системы 300 SDR для поддержки многочисленных видеостандартов с многочисленными параметрами использования и размерами. Кроме того, использование устройств CRISP позволяет перестраивать подсистему 301 основной полосы частот многостандартной системы 300 SDR для поддержки многочисленных стандартов радиоинтерфейса.

Таким образом, система 300 SDR может работать в различных типах беспроводных сетей (например, CDMA, GSM, 802.11x и т.д.) и может выполнять различные типы видео и звуковых форматов. Однако использование CRISP согласно принципам настоящего раскрытия изобретения позволяет системе 300 SDR выполнять эти функции с намного меньшей потребляемой мощностью, чем традиционные беспроводные устройства, которые имеют сравнимые возможности.

Фиг.4 является блок-схемой перестраиваемого турбодекодера, реализованного в турбодекодере в CRISP 100f согласно принципам раскрытия настоящего изобретения. Турбодекодер CRISP 100f содержит программное запоминающее устройство 405, регистровые файлы 410 конфигурации, генератор 415 адресов, переключатель 420 связи, обрабатывающие блоки 430а-430d, запоминающие устройства 440а-440d входных данных, запоминающие устройства 445а-445d внешней информации и внутреннюю шину 490. Каждый из обрабатывающих блоков 430а-430d содержит управляющий конечный автомат (SM), информационный канал с максимальной апостериорной вероятностью (МАР), быстродействующую буферную память и регистровые управляющие файлы. Например, обрабатывающий блок 430 содержит управляющий конечный автомат 431а, информационный канал 432а МАР, быстродействующую буферную память 433а и регистровые управляющие файлы 434а. Хотя на фиг.4 проиллюстрированы четыре обрабатывающих блока 430, это приведено лишь в качестве примера. Другие варианты осуществления турбодекодера CRISP 100f могут реализовать меньше, чем четыре обрабатывающих блока 430, или более, чем четыре обрабатывающих блока 430.

Общая архитектура турбодекодера MAP в целом содержит два исходных функциональных блока: i) каскады с программируемым входом и программируемым выходом (SISO), которые реализуют алгоритм апостериорной вероятности (APP); и ii) перемежитель/деперемежитель, который зашифровывает данные согласно правилам перемежения, за которым следует кодер в передающем устройстве. Другие блоки необходимы для осуществления декодера, например, RAM (оперативное запоминающее устройство) для хранения данных от каждой итерации декодера.

Турбодекодер CRISP 100f включает в себя все стандартные блоки традиционного турбодекодера МАР. В примерном варианте осуществления информационные каналы 432а-432d МАР реализуют алгоритм МАР раздвижного окна. Однако альтернативные варианты осуществления турбодекодера CRISP 100f могут реализовать алгоритмы МАР нераздвижного окна.

Как хорошо известно, традиционный турбокодер использует два постоянных кодера. Первый кодер принимает исходный поток битов и формирует первый поток парных битов. Второй кодер принимает уплотненную копию исходного потока битов и формирует второй поток парных битов. Данные, передаваемые с помощью турбокодера, содержат исходный поток битов, первые парные биты от первого кодера и вторые парные биты от второго кодера.

Традиционный турбодекодер содержит два блока декодера, которые работают в итеративном режиме. Первый блок декодера принимает выборки данных (программируемые значения) от демодулятора, соответствующие исходным битам данных, и первые парные биты от первого кодера. Первый блок декодера использует исходные биты данных и первые парные биты для оценки вероятности, с которой значение каждого исходного бита данных равно 1 или 0. Второй блок декодера принимает выборки данных (программируемые значения) от демодулятора, которые соответствуют уплотненным исходным битам данных, вторые парные биты от второго кодера и вероятностные оценки входного сигнала от первого блока декодера. Процесс декодирования обоими блоками декодера содержит одну итерацию турбодекодера. Традиционный турбодекодер может выполнять фиксированное число итераций или может выполнять итерации, пока некоторый внешний механизм не определит, что дополнительные итерации не улучшат частоту передачи ошибочных битов (BER) для конкретной схемы данных. Затем принимается жесткое решение по последним программируемым выходным данным для определения исходных битов данных.

Как хорошо известно, алгоритм МАР является алгоритмом решетчатого декодирования, аналогичного алгоритму Витерби. Алгоритм МАР в двух блоках декодера действует на программируемые входные данные (т.е. выходные данные демодулятора и оценки вероятности) и создает программируемые выходные данные. Вычисления для алгоритма МАР, выполняемые одним блоком декодера для одной итерации, могут суммироваться, как изложено ниже. На первом этапе традиционный алгоритм МАР вычисляет и хранит показатели перехода, называемые значениями гамма (или γ) для всех переходов решетки. Показатели перехода являются экспоненциальной функцией отрицательных значений расстояний между жесткими значениями кодера и программируемыми значениями, принятыми от демодулятора, деленной на отклонение шума канала, умноженной на оценку вероятности от предыдущего декодера.

На втором этапе традиционный алгоритм MAP выполняет прямую рекурсию на решетке. Прямая рекурсия вычисляет значение альфа (или α) для каждого узла во временных маршрутах. Значение α является суммой i) предыдущих показателей перехода в моменты времени значений α с одним переходом от предыдущего узла и ii) предыдущих показателей перехода в моменты времени значений α с другим переходом от предыдущего узла. На третьем этапе традиционный алгоритм МАР выполняет обратную рекурсию на решетке. Обратная рекурсия вычисляет значение бета (β) для каждого узла во временных маршрутах. Значения β вычисляются способом, аналогичным значениям α, исключая, что обратная рекурсия начинается в конце решетки и продолжается в обратном направлении.

На четвертом этапе традиционный алгоритм MAP вычисляет значение логарифмического коэффициента правдоподобия (LLR или λ) для каждого момента времени t. Это значение является суммой результатов значений α, β и λ для каждого перехода в момент времени t, которое ассоциативно связано со значением 1 в кодере, разделенным на сумму результатов значений α, β и λ для каждого перехода в момент времени t, которое ассоциативно связано со значением 0 в кодере. В конечном итоге традиционный алгоритм MAP вычисляет внешнюю информацию, которая должна быть послана в следующий декодер в последовательности итераций. Внешняя информация является значением LLR за минусом вероятностной оценки входного сигнала.

Вычисления, описанные выше, повторяются в каждой итерации каждым из двух блоков декодера. После того как все итерации завершены, биты декодированной информации могут быть обнаружены с помощью проверки знака бита значения LLR. Если значение LLR является положительным, бит данных равен 1. Если значение LLR является отрицательным, бит данных равен 0. Альтернативно значения LLR могут быть выведены во внешнее устройство, которое принимает решение по каждому биту данных.

В турбодекодере CRISP 100f вычисления, описанные выше, выполняются с помощью информационных каналов МАР 432а, 432b, 432c и 432d. Значения α, β и λ временно хранятся в быстродействующей буферной памяти 433а, 433b, 433c и 433d. Внешняя информация от каждой итерации для каждого блока декодирования хранится в запоминающих устройствах 445а, 445b, 445c и 433d внешней информации через переключатель 420 связи.

В примерном варианте осуществления MCU 370 загружает программу конфигурирования и данные конфигурации в турбодекодер CRISP 100f через внешнюю системную шину (т.е. межкомпонентное соединение 325). Программа конфигурирования хранится в программном запоминающем устройстве 405. MCU 370 загружает данные конфигурации в регистровые файлы 410 конфигурации и регистровые управляющие файлы 434а-434d для того, чтобы запустить регистровые файлы. Регистровые файлы 410 конфигурации и регистровые управляющие файлы 434а-434d используются для управления тем, какие обрабатывающие блоки 430а-430d, запоминающие устройства 440а-440d входных данных и запоминающие устройства 445а-445d внешней информации используются в приложении. Регистровые файлы 410 конфигурации предусматривают разрешающие (EN) сигналы в управляющие обрабатывающие блоки 430, запоминающие устройства 440 входных данных и запоминающие устройства 445 внешней информации. Турбодекодер CRISP 100f считывает выборки входных данных и записывает декодированные выходные данные через системную шину (т.е. межкомпонентное соединение 325).

Для того чтобы достичь высоких скоростей декодирования, турбодекодер CRISP 100f реализует N параллельных обрабатывающих блоков 430а-430d. В этом примере N=4. Обрабатывающие блоки 430а-430d являются независимыми и идентичны друг другу. Каждый из обрабатывающих блоков 430а-430d разрешает соединение с каждым из запоминающих устройств 440а-440d входных данных и запоминающих устройств 445а-445d внешней информации через переключатель 420 связи. Для стандартов с более высокой скоростью передачи данных все из обрабатывающих блоков 430а-430d могут действовать одновременно и параллельно. Для стандартов с более низкой скоростью передачи данных один или более из обрабатывающих блоков 430а-430d может быть установлен в спящий режим (т.е. деактивирован или отключен) для того, чтобы уменьшить потребляемую мощность.

Как отмечено выше, каждый из обрабатывающих блоков 430а-430d содержит управляющий конечный автомат 431, информационный канал 432 МАР, быстродействующую буферную память 433 и регистровые управляющие файлы 434. В примерном варианте осуществления турбодекодера CRISP 100f каждый обрабатывающий блок 430 обрабатывает две выборки программируемых входных данных в один момент времени. Две выборки программируемых входных данных соответствуют двум символам данных. В примерном варианте осуществления каждая выборка программируемых входных данных может содержать 8 бит.

Информационный канал 432 МАР выполняет прямую и обратную рекурсии над решеткой. Во время прямой рекурсии должен быть предоставлен доступ и к входному символу, и к внешней информации для вычисления показателя перехода γ. Для того чтобы снизить расход мощности, связанный с предоставлением доступа к запоминающему устройству, значение γ может быть вычислено и сохранено в быстродействующей буферной памяти 433 в каждом обрабатывающем блоке 430. Если значения α, β и λ не вычисляются одновременно, значение α может также сохраняться в быстродействующей буферной памяти 430 для уменьшения перемещения данных и потребляемую мощность.

Информационный канал 432 МАР может вычислять значения α, β и λ в параллельном или в совмещенном (или последовательном) порядке. Параллельное выполнение является более быстрым, но требует больше сокращающегося пространства и потребляемой мощности. Совмещенная обработка приводит к более длительным задержкам, но требует меньше сокращающегося пространства и меньше потребляемой мощности. В примерном варианте осуществления каждый из информационных каналов 430а-430d МАР вычисляет значения α, β и λ последовательно.

Управляющий конечный автомат 431 декодирует команды от программного запоминающего устройства, принятые через внутреннюю шину 490 и управляет общим функционированием и конфигурацией обрабатывающего блока 430. Так как турбодекодер CRISP 100f может вычислять большие циклы команд, управляющий конечный автомат 431 может использовать аппаратную цепь для уменьшения потерь и потребляемой мощности.

Существует восемь блоков запоминающего устройства в турбодекодере CRISP 100f: четыре запоминающих устройства 440а входных данных, которые удерживают выборки входных данных (или символ) и четыре запоминающих устройства 445 внешней информации, которые удерживают внешнюю информацию, формируемую в каждой итерации турбодекодера. Восемь блоков запоминающего устройства разделены на четыре группы. Каждая группа запоминающих устройства включает в себя одно запоминающее устройство 440 входных данных и одно запоминающее устройство 445 внешней информации. Например, запоминающее устройство 440а входных данных и одно запоминающее устройство 445а внешней информации образуют первую группу запоминающих устройств, запоминающее устройство 440b входных данных и одно запоминающее устройство 445b внешней информации образуют вторую группу запоминающих устройств и так далее.

Каждый из обрабатывающих блоков 430а-430d считывает и записывает в одну группу запоминающих устройств в один момент времени. Каждый из обрабатывающих блоков 430а-430d разрешает запись в каждую из групп запоминающих устройств. Таким образом, никакая из групп запоминающих устройств не выделена конкретному обрабатывающему блоку 430. Например, обрабатывающий блок 430а может быть соединен с помощью переключателя 420 связи в первую группу запоминающих устройств (например, запоминающие устройства 440а и 445а) во время одного цикла памяти и может считывать с или записывать в другую группу запоминающих устройств (например, запоминающие устройства 440с и 445с) во время другого цикла памяти.

Переключатель 420 связи динамически управляет соединениями между обрабатывающими блоками 430а-430d и группами запоминающих устройств, составленными из запоминающих устройств 440а-440d и запоминающих устройств 445а-445d. Порядок соединения или схема определяется действием генератора 415 адресов. В одном варианте осуществления настоящего раскрытия изобретения генератор 415 адресов может быть реализован с помощью запоминающего устройства. В подобном варианте осуществления внешний управляющий DSP/MCU, например, MCU 370, предварительно автономно вычисляет схему перемежителя турбодекодера и записывает схему перемежителя в запоминающее устройство генератора 415 адресов во время фазы запуска. В другом варианте осуществления настоящего раскрытия изобретения генератор 415 адресов может быть спроектирован для формирования схемы перемежителя в реальном времени.

Фиг.5 отображает диаграмму 500 состояний, которая изображает действия по управлению мощностью в турбодекодере CRISP 100f согласно принципам настоящего раскрытия изобретения. В примерном варианте осуществления турбодекодер CRISP 100f действует в нескольких режимах управления мощностью под управлением MCU 370, а именно режим 510 выключения, режим 520 запуска, режим 530 бездействия, режим 540 ожидания и активный режим 550. В альтернативном варианте осуществления турбодекодер CRISP 100f может действовать в различных режимах управления мощностью под управлением подсистемы 315 DSP основной полосы частот.

В режиме 510 выключения турбодекодер CRISP 100f полностью отключен и все тактовые генераторы выключены. В режиме 520 запуска программное запоминающее устройство 405 загружается и регистровые файлы 410 конфигурации и регистровые управляющие файлы 434 конфигурируются. Однако синхронизирующие сигналы связаны только с программным запоминающим устройством 405, регистровыми файлами 410 и 434 и связанными схемами. В режиме 530 бездействия синхронизирующие сигналы предоставляются обрабатывающим блокам 430a-430d и некоторые группы запоминающих устройств включены так, что группы запоминающих устройств могут принимать выборки входных данных. В режиме 540 ожидания пропускаются сигналы синхронизации, предоставляемые обрабатывающим блокам 430a-430d, генератору 415 адресов и некоторым группам запоминающих устройств. В активном режиме 550 только используемая методика управления мощностью является масштабированием действующей частоты синхронизации.

При сбросе системы турбодекодер CRISP 100f находится в режиме 510 выключения. Если MCU 370 загружает программу конфигурации и данные в программное запоминающее устройство 405, регистровые файлы 410 конфигурации и/или регистровые управляющие файлы 434а-434d, состояние турбодекодера CRISP 100f изменяется на режим 520 запуска, в положении которого активизированы лишь программное запоминающее устройство 405, регистровые файлы 410 конфигурации и/или регистровые управляющие файлы 434а-434d и связанные схемы.

Если турбодекодер CRISP 100f заканчивает обработку кадра данных, он устанавливается в режим 530 бездействия. В режиме 530 бездействия турбодекодер CRISP 100f может принимать выборки входных данных от внешней шины (т.е. межкомпонентного соединения 325). Если входные данные полностью загружены в запоминающие устройства 440а-440d входных данных, турбодекодер CRISP 100f входит заново в активный режим 550 и возобновляет обработку.

Если некоторые из обрабатывающих блоков 430, запоминающих устройств 440а-440d входных данных и запоминающих устройств 445а-445d внешней информации не используются, синхронизирующие сигналы в эти компоненты могут быть выключены, чтобы привести эти компоненты в режим 540 ожидания. Обрабатывающие блоки 430, запоминающие устройства 440а-440d входных данных и запоминающие устройства 445а-445d внешней информации, которые используются, остаются в активном режиме 550. Эта схема уменьшает мощность. Если обрабатывающий блок используется, но за интервал времени не выполняется никакой команды, команда NOP (пустая команда) может быть вставлена либо вручную, либо автоматически. Команда NOP запускает только минимальное количество аппаратных ресурсов. Это также уменьшает потребляемую мощность, когда обрабатывающий блок находится в активном режиме 550.

Хотя настоящее раскрытие изобретения описано с помощью примерного варианта осуществления, различные изменения и модификации могут быть предложены специалисту в данной области техники. Подразумевается, что настоящее раскрытие изобретения охватывает подобные изменения и модификации, как попадающие в объем прилагаемой формулы изобретения.

Предложен перестраиваемый турбодекодер, содержащий N обрабатывающих блоков. Каждый из N обрабатывающих блоков принимает выборки программируемых входных данных и декодирует принятые выборки программируемых входных данных. N обрабатывающих блоков действуют независимо из условия, что первый обрабатывающий блок может быть выбран для декодирования принятых выборок программируемых входных данных, тогда как второй обрабатывающий блок может быть выключен. Множество обрабатывающих блоков, выбираемых для декодирования выборок программируемых входных данных, определяют скоростью передачи данных принятых выборок программируемых входных данных. Перестраиваемый турбодекодер также содержит N запоминающих устройств входных данных, которые хранят принятые выборки программируемых входных данных и N запоминающих устройств внешней информации, которые хранят внешнюю информацию, сформированную N обрабатывающими блоками. Каждый из N обрабатывающих блоков выполнен с возможностью считывания из каждого из N запоминающих устройств внешней информации и записи в каждое из N запоминающих устройств входных данных и каждое из N запоминающих устройств внешней информации. Технический результат - обеспечение эффективного кодирования и уменьшение потребляемой мощности. 3 н. и 18 з.п ф-лы, 5 ил.

1. Перестраиваемый турбодекодер, содержащий

N обрабатывающих блоков, причем каждый из N обрабатывающих блоков выполнен с возможностью приема выборок программируемых входных данных и декодирования принятых выборок программируемых входных данных, при этом N обрабатывающих блоков действуют независимо из условия, что первый из N обрабатывающих блоков выбран для декодирования принятых выборок программируемых входных данных, тогда как второй из N обрабатывающих блоков выключен;

N запоминающих устройств входных данных, выполненных с возможностью хранения принятых выборок программируемых входных данных;

N запоминающих устройств внешней информации, выполненных с возможностью хранения внешней информации, сформированной N обрабатывающими блоками;

генератор адресов; и

переключатель связи, выполненный с возможностью динамического управления соединениями между N обрабатывающими блоками и группами запоминающих устройств, составленными из N запоминающих устройств входных данных и N запоминающих устройств внешней информации, причем порядок или схема соединения определяется действием генератора адресов;

при этом число N обрабатывающих блоков, которые выбраны для декодирования принятых выборок программируемых входных данных, определяется скоростью передачи данных принятых выборок программируемых входных данных, и N обрабатывающих блоков соединены с N запоминающими устройствами входных данных и N запоминающими устройствами внешней информации с помощью переключателя связи.

2. Перестраиваемый турбодекодер по п.1, в котором каждый из N обрабатывающих блоков выполнен с возможностью считывания данных из каждого из N запоминающих устройств входных данных и записи данных в каждое из N запоминающих устройств входных данных.

3. Перестраиваемый турбодекодер по п.2, в котором N запоминающих устройств входных данных действуют независимо из условия, что первое из N запоминающих устройств входных данных выбрано для хранения, по меньшей мере, некоторых из принятых выборок программируемых входных данных, тогда как второе из N запоминающих устройств входных данных выключено.

4. Перестраиваемый турбодекодер по п.З, в котором число N запоминающих устройств входных данных, которые выбраны для хранения, по меньшей мере, некоторых из принятых выборок программируемых входных данных, определяется скоростью передачи данных принятых выборок программируемых входных данных.

5. Перестраиваемый турбодекодер по п.2, в котором каждый из N обрабатывающих блоков выполнен с возможностью считывания внешней информации из каждого из N запоминающих устройств внешней информации и записи внешней информации в каждое из N запоминающих устройств внешней информации.

6. Перестраиваемый турбодекодер по п.5, в котором N запоминающих устройств внешней информации действуют независимо из условия, что первое из N запоминающих устройств внешней информации выбрано для хранения, по меньшей мере, части внешней информации, сформированной N обрабатывающими блоками, тогда как второе из N запоминающих устройств внешней информации выключено.

7. Перестраиваемый турбодекодер по п.6, в котором число N запоминающих устройств внешней информации, которые выбраны для хранения, по меньшей мере, части внешней информации, сформированной N обрабатывающими блоками, определяется скоростью передачи данных принятых выборок программируемых входных данных.

8. Программно-определяемая радиосистема (SDR), выполненная с возможностью функционирования при множестве стандартов беспроводной связи, содержащая

радиочастотный (RF) приемопередатчик, выполненный с возможностью приема входящего RF сигнала и формирования преобразованного сигнала с понижением частоты; и

перестраиваемый турбодекодер, выполненный с возможностью приема программируемых входных данных, связанных с преобразованным сигналом с понижением частоты, причем перестраиваемый турбодекодер содержит

N обрабатывающих блоков, причем каждый из N обрабатывающих блоков выполнен с возможностью приема выборок программируемых входных данных и декодирования принятых выборок программируемых входных данных, при этом N обрабатывающих блоков действуют независимо из условия, что первый из N обрабатывающих блоков выбран для декодирования принятых выборок программируемых входных данных, тогда как второй из N обрабатывающих блоков выключен,

N запоминающих устройств входных данных, выполненных с возможностью хранения принятых выборок программируемых входных данных;

N запоминающих устройств внешней информации, выполненных с возможностью хранения внешней информации, сформированной N обрабатывающими блоками;

генератор адресов; и

переключатель связи, выполненный с возможностью динамического управления соединениями между N обрабатывающими блоками и группами запоминающих устройств, составленными из N запоминающих устройств входных данных и N запоминающих устройств внешней информации, причем порядок или схема соединения определяется действием генератора адресов;

при этом число N обрабатывающих блоков, которые выбраны для декодирования принятых выборок программируемых входных данных, определяется скоростью передачи данных принятых выборок программируемых входных данных, и N обрабатывающих блоков соединены с N запоминающими устройствами входных данных и N запоминающими устройствами внешней информации с помощью переключателя связи.

9. Программно-определяемая радиосистема (SDR) по п.8, в которой каждый из N обрабатывающих блоков выполнен с возможностью считывания данных из каждого из N запоминающих устройств входных данных и записи данных в каждое из N запоминающих устройств входных данных.

10. Программно-определяемая радиосистема (SDR) по п.9, в которой N запоминающих устройств входных данных действуют независимо из условия, что первое из N запоминающих устройств входных данных выбрано для хранения, по меньшей мере, некоторых из принятых выборок программируемых входных данных, тогда как второе из N запоминающих устройств входных данных выключено.

11. Программно-определяемая радиосистема (SDR) по п.10, в которой число N запоминающих устройств входных данных, которые выбраны для хранения, по меньшей мере, некоторых из принятых выборок программируемых входных данных, определяется скоростью передачи данных принятых выборок программируемых входных данных.

12. Программно-определяемая радиосистема (SDR), по п.9, в которой каждый из N обрабатывающих блоков выполнен с возможностью считывания внешней информации из каждого из N запоминающих устройств внешней информации и записи внешней информации в каждое из N запоминающих устройств внешней информации.

13. Программно-определяемая радиосистема (SDR) по п.12, в которой N запоминающих устройств внешней информации действуют независимо из условия, что первое из N запоминающих устройств внешней информации выбрано для хранения, по меньшей мере, части внешней информации, сформированной N обрабатывающими блоками, тогда как второе из N запоминающих устройств внешней информации выключено.

14. Программно-определяемая радиосистема (SDR) по п.13, в которой число N запоминающих устройств внешней информации, которые выбраны для хранения, по меньшей мере, части внешней информации, сформированной N обрабатывающими блоками, определяется скоростью передачи данных принятых выборок программируемых входных данных.

15. Способ декодирования в перестраиваемом турбодекодере, содержащем N независимых обрабатывающих блоков, выполненных с возможностью декодирования принятых выборок программируемых входных данных, содержащий этапы, на которых

выбирают, по меньшей мере, один из N обрабатывающих блоков для приема выборок программируемых входных данных;

декодируют, по меньшей мере, некоторые из принятых выборок программируемых входных данных в выбранном, по меньшей мере, одном обрабатывающем блоке;

выключают, по меньшей мере, один из N обрабатывающих блоков, тогда как выбранный, по меньшей мере, один обрабатывающий блок декодирует принятые выборки программируемых входных данных,

сохраняют принятые выборки программируемых входных данных в N запоминающих устройствах входных данных;

сохраняют внешнюю информацию, сформированную N обрабатывающими блоками в N запоминающих устройствах внешней информации; и

посредством переключателя связи динамически управляют соединениями между N обрабатывающими блоками и группами запоминающих устройств, составленными из N запоминающих устройств входных данных и N запоминающих устройств внешней информации, причем порядок или схему соединения определяют действием генератора адресов;

при этом число N обрабатывающих блоков, которые выбирают для декодирования принятых выборок программируемых входных данных, определяют скоростью передачи данных принятых выборок программируемых входных данных, и N обрабатывающих блоков соединены с N запоминающими устройствами входных данных и N запоминающими устройствами внешней информации с помощью переключателя связи.

16. Способ декодирования в перестраиваемом турбодекодере по п.15, причем каждый из N обрабатывающих блоков выполнен с возможностью считывания данных из каждого из N запоминающих устройств входных данных и записи данных в каждое из N запоминающих устройств входных данных.

17. Способ декодирования в перестраиваемом турбодекодере по п.16, в котором N запоминающих устройств входных данных действуют независимо из условия, что первое из N запоминающих устройств входных данных выбрано для хранения, по меньшей мере, некоторых из принятых выборок программируемых входных данных, тогда как второе из N запоминающих устройств входных данных выключено.

18. Способ декодирования в перестраиваемом турбодекодере по п.17, в котором число N запоминающих устройств входных данных, которые выбирают для хранения, по меньшей мере, некоторых из принятых выборок программируемых входных данных, определяют скоростью передачи данных принятых выборок программируемых входных данных.

19. Способ декодирования в перестраиваемом турбодекодере по п.16, причем каждый из N обрабатывающих блоков выполнен с возможностью считывания внешней информации из каждого из N запоминающих устройств внешней информации и записи внешней информации в каждое из N запоминающих устройств внешней информации.

20. Способ декодирования в перестраиваемом турбодекодере по п.19, в котором N запоминающих устройств внешней информации действуют независимо из условия, что первое из N запоминающих устройств внешней информации выбрано для хранения, по меньшей мере, части внешней информации, сформированной N обрабатывающими блоками, тогда как второе из N запоминающих устройств внешней информации выключено.

21. Способ декодирования в перестраиваемом турбодекодере по п.20, в котором число N запоминающих устройств внешней информации, которые выбирают для хранения, по меньшей мере, части внешней информации, сформированной N обрабатывающими блоками, определяют скоростью передачи данных принятых выборок программируемых входных данных.

| US 6697443 В1, 24.02.2004 | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| US 2003014712 A1, 16.01.2003 | |||

| УСТРОЙСТВО И СПОСОБ ТУРБОКОДИРОВАНИЯ/ДЕКОДИРОВАНИЯ ДЛЯ ОБРАБОТКИ ДАННЫХ КАДРА В СООТВЕТСТВИИ С КАЧЕСТВОМ ОБСЛУЖИВАНИЯ | 1999 |

|

RU2210185C2 |

Авторы

Даты

2010-03-10—Публикация

2006-05-18—Подача