Изобретение относится к устройствам для проверки данных. В частности это изобретение относится к техническому обеспечению проверки обработки данных.

Известно, что для технического обеспечения микропроцессора за основу взяты системы с функциями отладки, которые позволяют пользователю опрашивать состояние ядра процессора. Такие отладочные системы позволяют изолировать ядро процессора от других частей устройства обработки данных, и посредством воздействия на ядро процессора при выполнении определенных команд можно наблюдать за внутренним состоянием ядра процессора.

В таких системах, как интегральная схема АМД 29200, вы пускаемая фирмой Advanced Micro Devices, эти отладочные команды не загружаются в ядро процессора через обычную шину команда/данные. Эти отладочные команды последовательно загружаются через схему развертки типа -JTAG и затем в развернутом виде передаются в шину команда/данные. Последовательная за грузка команд в схему развертки происходит под управлением тактового сигнала проверки, согласованного с внешним устройством, от которого поступают последовательные команды. Загруженные таким способом команды выполняются при скорости намного меньше обычной, например, для 32-битовой команды необходимо 32 тактовых цикла проверки для загрузки команды перед тем, как тактовый сигнал проверки может быть послан в ядро, чтобы оно выполнило команду.

В одном аспекте предлагается устройство для обработки данных, содержащее ядро процессора, работающее под управлением программных команд, средство для подачи тактового сигнала системы в ядро процессора, средство для подачи тактового сигнала проверки в ядро процессора, средство выбора тактового сигнала для выбора между тактовым сигналом системы, управляющим работой ядра процессора и тактовым сигналом проверки, управляющим работой ядра процессора, средство выбора тактового сигнала предназначено для выбора тактового сигнала системы в течение нормального режима работы и тактового сигнала проверки при загрузке программных команд во время режима проверки, причем средство выбора тактового сигнала, реагируя на один или более бит выбора тактового сигнала внутри программной команды, выполняет в течение режима проверки выбор либо тактового сигнала проверки, либо тактового сигнала системы для управления ядром процессора при выполнении этой программной команды.

Эта особенность выбора тактового сигнала позволяет ядру процессора выполнять однажды загруженные команды в соответствии с действительным тактовым сигналом системы, который будет использоваться в течение нормального режима работы. Таким образом, можно осуществить более реальную проверку работы ядра процессора.

В предпочтительном варианте изобретение содержит по меньшей мере одну вспомогательную схему, связанную с ядром процессора и управляемую посредством тактового сигнала системы, причем средство выбора тактового сигнала предназначено для выбора тактового сигнала системы в течение режима проверки для выполнения программных команд, использующих вспомогательную схему.

Изобретение обеспечивает крайне необходимую способность устройства проверять состояния вспомогательных схем, связанных с ядром процессора также, как и самого ядра процессора. Ядра процессора могут быть полностью статическими, что позволяет им использовать внешний тактовый сигнал проверки, но вспомогательные схемы такого типа, которые используются с ядрами процессора, не обладают этой способностью (например, DRAM требует постоянного обновления на тактовой частоте системы). В общем, работа ядра процессора со своими вспомогательными схемами требует точного согласования и меньше подвержена отклонению от тактовой частоты системы, например, передачу данных необходимо синхронизировать как с ядром, так и со вспомогательной схемой, использующей подобный тактовый сигнал.

Изобретение позволяет загружать команды, используя тактовый сигнал проверки, а также переключать для выполнения этих команд тактовым сигналом системы. Это повышает возможности использования анализа проверки, который можно осуществить в этом способе.

Как указано выше, вспомогательные схемы, связанные с ядром процессора, могут принимать различные формы. Однако изобретение пригодно для систем, в которых вспомогательные цепи включают схемы памяти и сопроцессоры. Такие вспомогательные схемы можно изготавливать на той же самой интегральной схеме, где расположено ядро процессора, поэтому анализ взаимодействия между этими цепями и ядром процессора будет очень трудно осуществить другими способами.

Предлагается также способ обработки данных, включающий следующие операции:

подают в ядро процессора программные команды,

подают тактовый сигнал системы в ядро процессора,

подают тактовый сигнал проверки в ядро процессора, и

выбирают между тактовым сигналом системы, управляющим работой ядра процессора, и тактовым сигналом проверки, управляющим работой ядра процессора, причем

выбирают тактовый сигнал системы в течение нормального режима работы и выбирают тактовый сигнал проверки при загрузке программных команд во время режима проверки, при этом один или более бит выбора тактового сигнала внутри программной команды выполняют в течение режима проверки управляемый выбор либо тактового сигнала проверки, либо тактового сигнала системы для управления ядром процессора при выполнении этой программной команды.

В предпочтительном варианте способа подают через командный конвейер программные команды в ядро процессора, принимают в средстве выбора тактового сигнала один иди более бит выбора тактового сигнала из того каскада командного конвейера, в котором сохраняют следующую команду, предназначенную для выполнения ядром процессора.

Микропроцессоры с высокими рабочими характеристиками включают в себя командные конвейеры для того, чтобы увеличить скорость обработки. Командный конвейер можно преимущественно использовать в эффективном буфере для бит выбора тактового сигнала совместно со своими подсоединенными программными командами таким образом, чтобы осуществить плавное изменение тактового сигнала, когда это необходимо.

Каждую программную команду в течение режима проверки можно загрузить из отладочной системы управления различными способами, например, параллельным способом через передающую шину. Однако, это является частным преимуществом для системы, в которой до обращения к ядру процессора в течение режима проверки последовательно загружается под управлением тактового сигнала проверки каждая программная команда, включающая один или более бит выбора тактового сигнала.

Последовательная загрузка программных команд в течение режима проверки уменьшает количество выводов устройства, тем самым упрощая конструкцию.

В предпочтительных вариантах с последовательной загрузкой выгодно предусмотреть такую схему развертки, при которой программные команды последовательно загружают в течение режима проверки.

Схему развертки можно использовать для других функций, таких как прием сигнала и приложение управляющего воздействия в течение режима проверки аппаратуры. Таким образом, схему развертки можно сделать такой, чтобы она выполняла более одной функции, обеспечив тем самым расширение функциональных возможностей интегральной схемы.

При нормальном режиме работы биты выбора тактового сигнала не будут иметь значения, так как нормальный режим работы использует тактовый сигнал системы. Соответственно, в предпочтительном варианте в течение нормального режима работы каждую программную команду загружают параллельно из программной памяти, при этом один или более бит выбора тактового сигнала отдельно добавляют в программные команды, считываемые из программной памяти.

Добавление бит выбора тактового сигнала после загрузки программных команд означает, что в памяти, хранящей программные команды для использования в нормальном режиме работы, нет необходимости сохранять биты выбора тактового сигнала, которые являются избыточными, так как они имеют то же значение для таких же программных команд при нормальном режиме работы. В этом случае лучше используется емкость запоминающего устройства программной памяти.

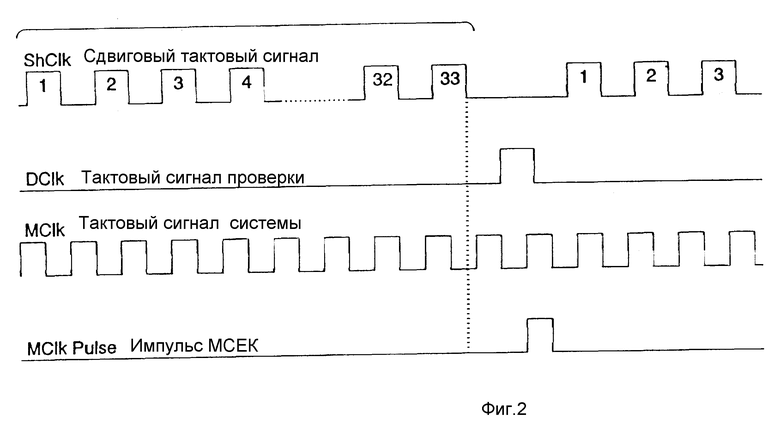

На фиг. 1 изображена интегральная схема, имеющая ядро процессора, работающего в нормальном режиме и в режиме проверки согласно изобретению; на фиг. 2 - тактовые сигналы, используемые в заявленном устройстве, согласно изобретению.

Интегральная схема 2 (фиг. 1) имеет ядро процессора 4.

Вспомогательная схема в виде динамического запоминающего устройства с произвольной выборкой (DRAM) 6 и сопроцессор 8, двунаправленно связанный с ядром 4 процессора. Вокруг ядра 4 процессора предусмотрена схема 10 развертки типа JTAG.

Тактовый сигнал системы MC1k и тактовый сигнал проверки DC1k подают на вход тактового мультиплексора 12, который переключается либо под воздействием внешнего сигнала управления Cnt, либо внутренним сигналом управления, генерируемым синхронизатором 14 тактовых импульсов. На сопроцессор 8 и DRAM 6 постоянно подаются тактовые сигналы системы MC1k.

Программные команды подаются в ядро 4 процессора через командный конвейер 16. Командный конвейер 16 заполняется посредством мультиплексора программной команды 18, который выбирает программные команды либо из шины команда и данные 20, либо из схемы развертки 10. Выход мультиплексора 18 программной команды напрямую соединяется с ядром 4 процессора с учетом состоянии шины команда и данные 20, которая также служит для переноса слов данных, проходящих непосредственно в и из ядра 4 процессора без прохождения через командный конвейер 16. Мультиплексор 18 программной команды переключается посредством логической схемы 22 управления проверкой, которая служит для выбора программных команд, последовательно загружаемых в схему 10 развертки, которые предпочтительнее в режиме проверки, чем программные команды от шины 20 команда и данные, которые используются в течение нормального режима работы. Логическая схема 22 управления проверкой является самоуправляемой за счет внешнего контроллера отладки (не показан).

Ядро 4 процессора работает, используя то, что обычно рассматривается как совокупность 32-битовой команды. 32-битовые программные команды преобразуются посредством добавления S бит выбора тактового сигнала к одному концу программной команды. Это осуществляют 33-бытовые программные команды. S бит выбора тактового сигнала используется для передачи флага, а программная команда, к которой он привязан, будет выполняться, используя тактовый сигнал системы MC1k или тактовый сигнал проверки DC1k. S бит выбора тактового сигнала направляется с выхода последнего каскада командного конвейера 16 в ядро 4 процессора, откуда он поступает в синхронизатор 14. Синхронизатор 14 воздействует на прием бита выбора тактового сигнала, показывающего, что тактовый сигнал системы будет использоваться для переключения тактового мультиплексора 12 в тактовой системе MC1k, когда появляется первый действующий импульс тактового сигнала системы. Синхронизатор 14 служит для того, чтобы предотвратить подачу в ядро 4 процессора импульса тактового сигнала системы, который не будет надежно действовать (например, передний фронт тактового сигнала асинхронной системы, возникающий вскоре после спада тактового сигнала проверки DC1k, по которому ядро 4 обычно срабатывает).

Программные команды в течение режима проверки последовательно загружаются в схему 10 развертки. 33 ячейки схемы 10 развертки служат для хранения одной полной программной команды (S-бит и 32-битовой команды), которая, когда полностью загружена, параллельно переключается через мультиплексор 18 программной команды на вход командного конвейера 16. Когда эта команда достигает командного конвейера, находящегося в состоянии готовности, ее S бит выбора тактового сигнала используется для управления тактовым мультиплексором 12, который выбирает либо тактовый сигнал системы MC1k, либо тактовый сигнал проверки DC1k, чтобы обеспечить необходимый импульс для выполнения этой программной команды внутри ядра 4 процессора.

В случае программной команды, которая вызывает либо DRAM 6, либо сопроцессор 8, используется тактовый сигнал системы MC1k. Например, в случае доступа к памяти DRAM 6, DRAM должна постоянно обновляться и может быть доступной только на определенные интервалы времени внутри этого цикла обновления. Соответственно, тот же самый тактовый сигнал должен использоваться как для ядра 4 сопроцессора так и для DRAM 6, чтобы такой доступ к памяти можно было правильно синхронизировать.

На фиг. 2 на верхней строке изображен сдвиговый тактовый сигнал ShC1k, который используется для управления схемой 10 развертки. Этот сдвиговый тактовый сигнал ShC1k проходит через 33 цикла, в течение которых 33 бита программной команды загружаются в схему 10 развертки. После того, как программная команда загружена, она переходит в командный конвейер 16, так как все команды двигаются вдоль командного конвейера. Команду командного конвейера 16 необходимо выполнить ядру 4 процессора и, соответственно, либо тактовый сигнал проверки DC1k, либо тактовый сигнал системы MC1k должен быть выбран в зависимости от бита выбора тактового сигнала.

В случае программной команды, которая будет выполняться тактовым сигналом проверки DC1k, тактовый сигнал проверки по является на выходе внешнего контролирующего устройства и направляется в ядро 4 процессора через тактовый мультиплексор 12. Это изображено на второй строке фиг. 2.

В случае программной команды, которая будет выполняться тактовым сигналом MC1k, должен быть выбран соответствующий импульс из тактового сигнала системы MC1k. Синхронизатор 14 осуществляет контроль тактового сигнала системы MC1k, следующего за получением соответствующего S бита выбора тактового сигнала, и идентифицирует первый правильный импульс тактового сигнала системы, который можно использовать, и переключает тактовый мультиплексор 12, чтобы направить его в ядро 4 процессора. В изображенном случае, первый импульс тактового сигнала системы, который должен появиться вслед за полной загрузкой программной команды, появляется также вскоре после предыдущего импульса тактового сигнала и поэтому не пригоден для использования.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО И СПОСОБ ОБРАБОТКИ ДАННЫХ С ИСПОЛЬЗОВАНИЕМ НАБОРОВ КОМАНД | 1995 |

|

RU2137183C1 |

| АДРЕСАЦИЯ РЕГИСТРОВ В УСТРОЙСТВЕ ОБРАБОТКИ ДАННЫХ | 1997 |

|

RU2193228C2 |

| ОБРАБОТКА ДАННЫХ С ИСПОЛЬЗОВАНИЕМ НЕСКОЛЬКИХ НАБОРОВ КОМАНД | 2002 |

|

RU2281547C2 |

| ОТОБРАЖЕНИЕ С ПОМОЩЬЮ МУЛЬТИНАБОРОВ КОМАНД | 1995 |

|

RU2137184C1 |

| БЛОКИРОВАНИЕ ИСХОДНЫХ РЕГИСТРОВ В УСТРОЙСТВЕ ОБРАБОТКИ ДАННЫХ | 2002 |

|

RU2282235C2 |

| ЗАПОМИНАНИЕ ОПЕРАНДОВ СТЕКА В РЕГИСТРЕ | 2001 |

|

RU2271565C2 |

| ОБРАБОТКА НЕОБРАБОТАННОЙ ОПЕРАЦИИ В СИСТЕМАХ С МНОЖЕСТВОМ НАБОРОВ КОМАНД | 2002 |

|

RU2287178C2 |

| ОБРАБОТКА ДАННЫХ С ПОМОЩЬЮ СОПРОЦЕССОРА | 2001 |

|

RU2275678C2 |

| ПЕРЕЗАПУСКАЕМЫЕ ТРАНСЛИРОВАННЫЕ КОМАНДЫ | 2001 |

|

RU2263949C2 |

| ЗАЩИТА ДОСТУПА К ПАМЯТИ | 1998 |

|

RU2215321C2 |

Изобретение относится к вычислительной технике. Технический результат заключается в повышении эффективности проверки работы ядра процессора. Устройство обработки данных содержит интегральную схему, которая имеет ядро процессора и схему развертки. Ядро процессора может выполнять программные команды, использующие либо тактовый сигнал системы, либо тактовый сигнал проверки. Тактовый выбор бита внутри программных команд для режима проверки показывает, какой тактовый сигнал следует использовать, а устройство тактового выбора выбирает указанный тактовый сигнал и направляет его в ядро процессора. 2 с. и 7 з.п. ф-лы, 2 ил.

| ЭЛЕКТРИЧЕСКАЯ МАШИНА | 2003 |

|

RU2266606C2 |

| УСТРОЙСТВО ДЛЯ РАЗГРУЗКИ АГЛОМЕРАТА | 0 |

|

SU313848A1 |

| Устройство для тестового контроля цифровых блоков | 1985 |

|

SU1312577A1 |

| ВСЕСОЮЗНАЯ IГ}ШНТНО»Т?ХШ1':?'-КД5^ ВИЕЛИО^г^'Д f | 0 |

|

SU332463A1 |

Авторы

Даты

1999-09-20—Публикация

1995-02-06—Подача