Изобретение относится к области г.иь

ТОМаТИКИ и вычислительной техники, в Ч СТ-ности к средствам автоматического контроля цифровых объектов, и может быть использовано для высокочастотной функциональной проверки блоков ЭВМ, построенных на основе мнкроироцессоров, БИС ОЗУ статического и динамического тина большого объема и прочих с.южных устройств в нроцессе их нроизводства.

Цель изобретения{расширение области ирименеиия за счег обеспечения возможности контроля микронроцессорных элементов с большим об ьемом о 1еративног() запоминающего устройства.

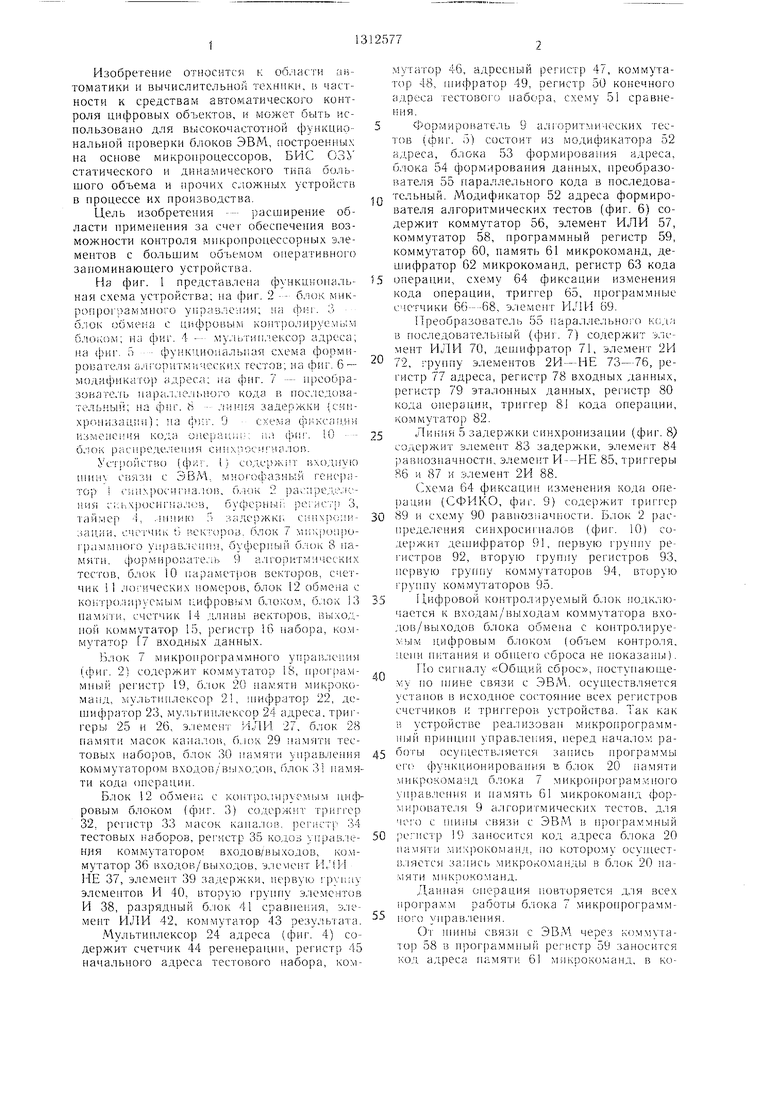

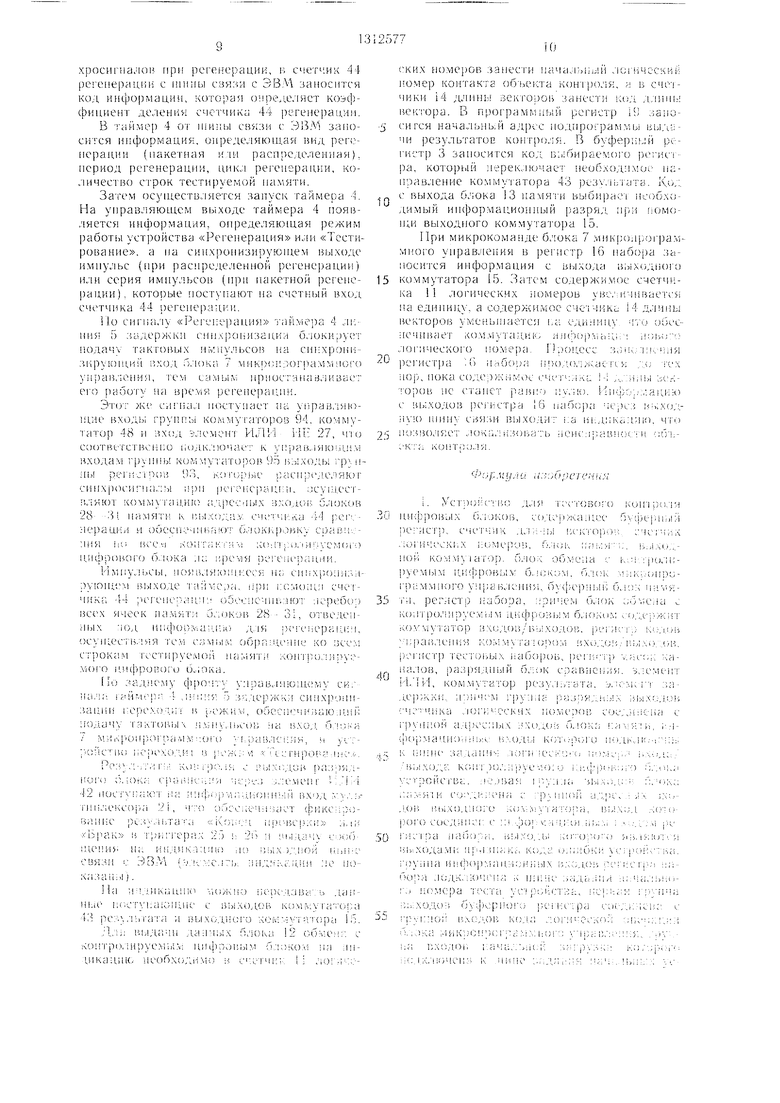

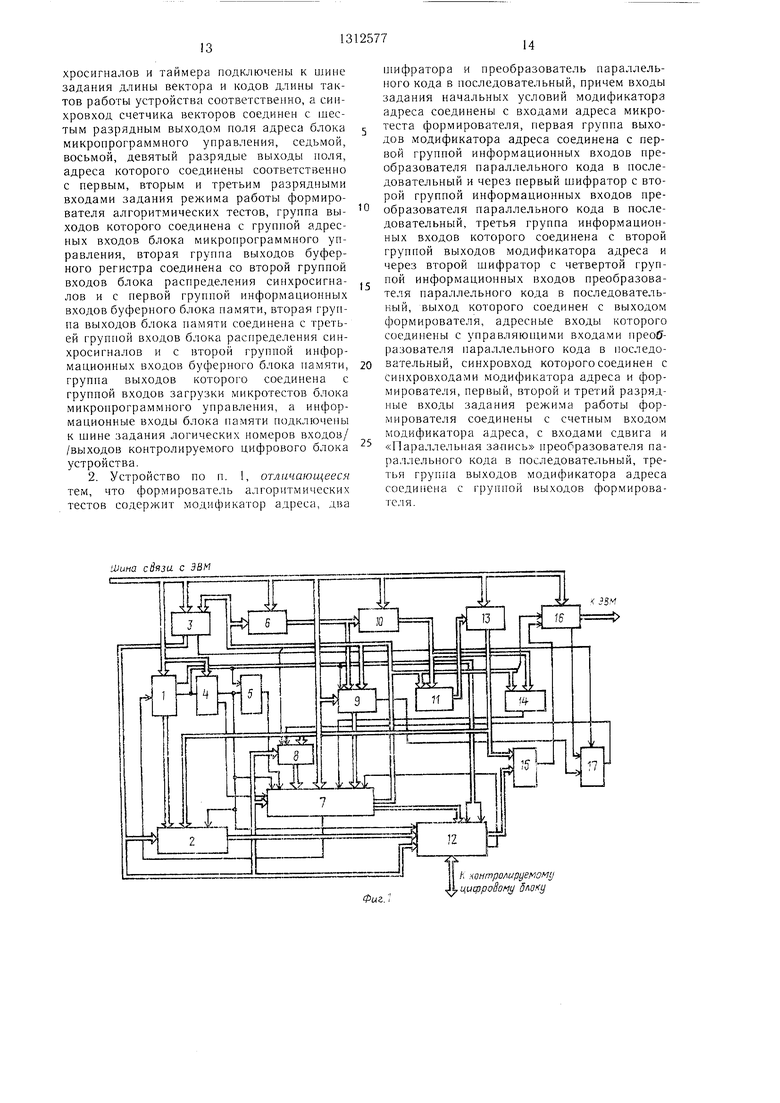

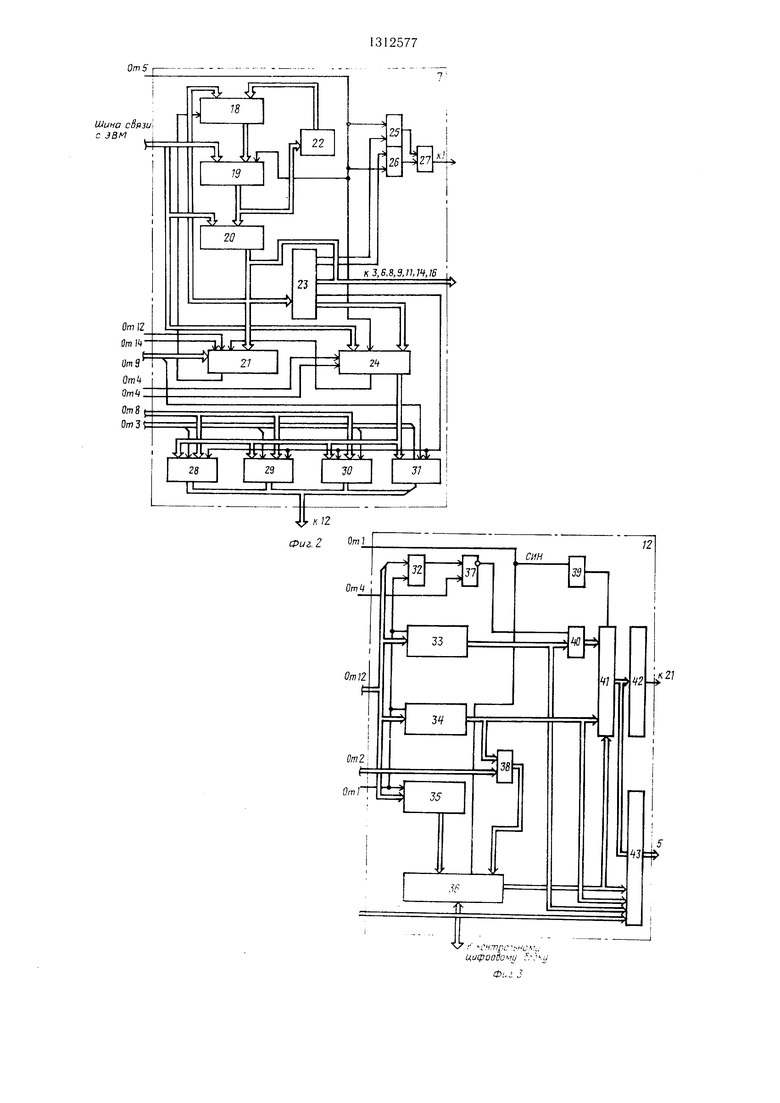

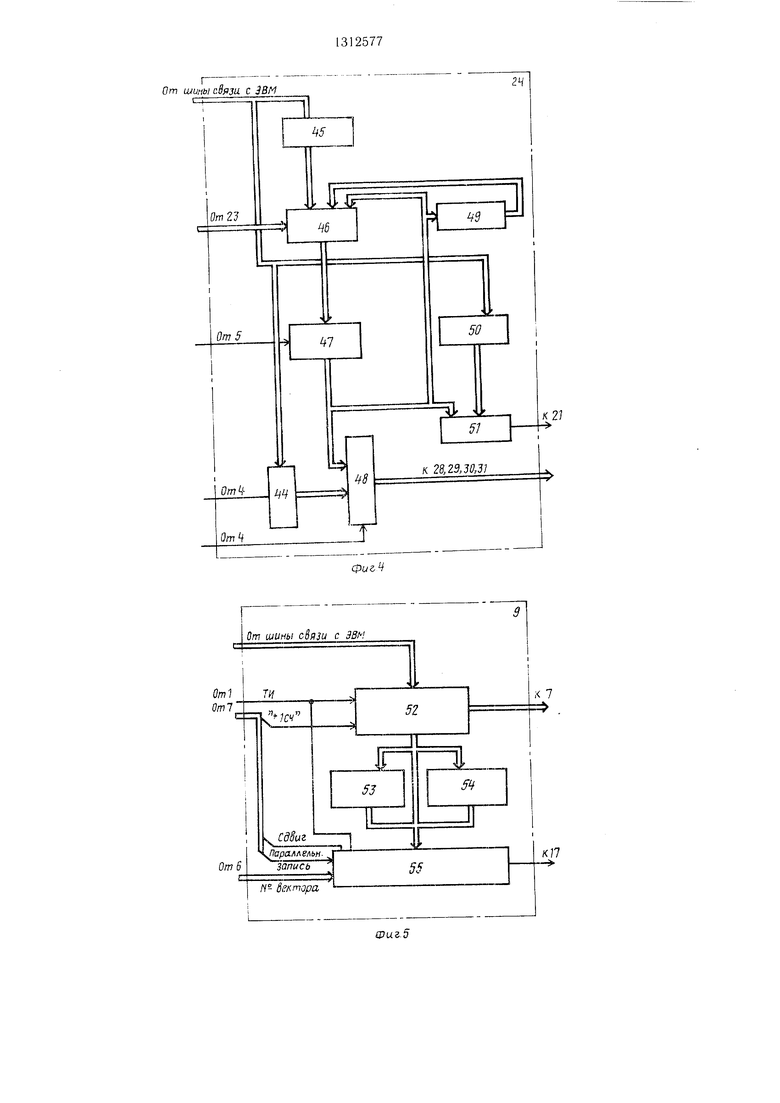

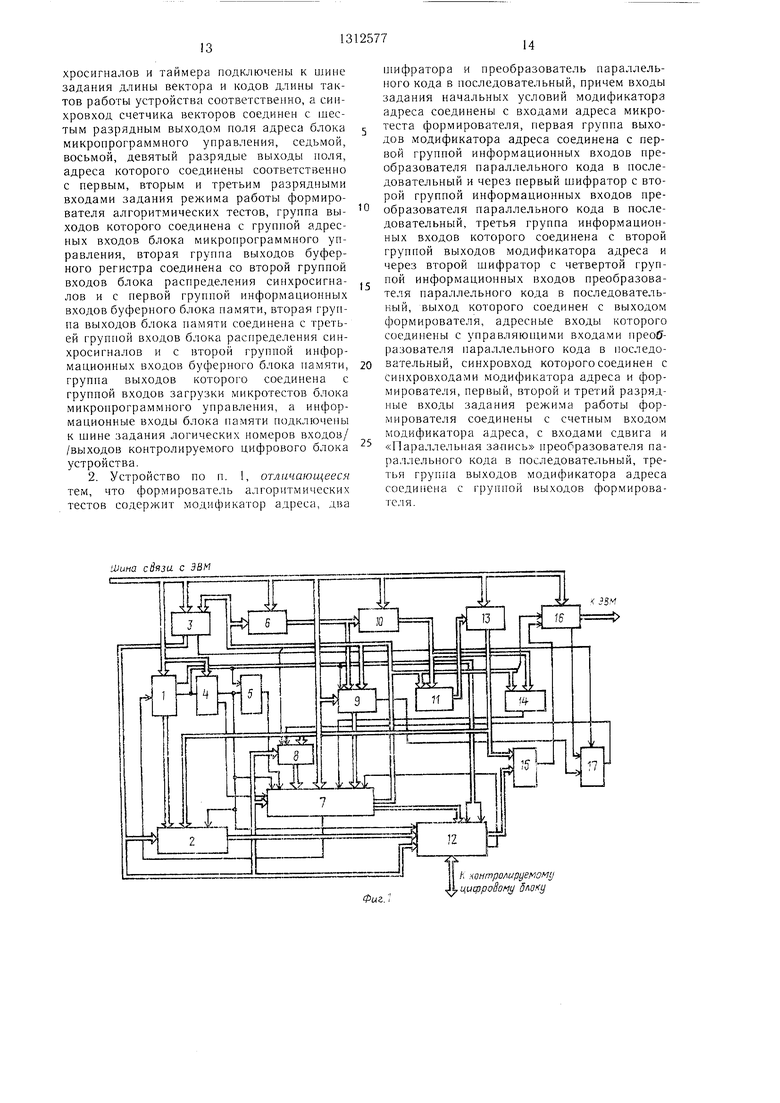

На фиг. 1 представлена функшюмаль- ная схема устройства; на фиг. 2 -- блок микропрограммного у11равле;1ия; на . 3 блок обме1 а с цифровым контролируемым

блоком; иа фиг. 4 - мультии.чексор адреса;

i;a (|)И1 5 - ()уикиио11альиая схема формн- ро)зате.;1я )р ггмическпх гестов; на фиг. б-- модификатор адреса; иа сЬиг. 7 - npcoDj a- зонате.(ь нара../1.ного кода в последова- на фкг. 8 - :1И1-;ия ; адержки (синхронизации); па (риг. 9 фиксап.ии и;4мене1м;я кода onepaiun;; ii.i (риг. К) - - б, раснроде. ;е(1ия сипхросиг нгьюп.

)оистио ((. i) c().:;,.in входную И1ин связи с ЗВМ, миого(Ьазный тор I иих)осигна.lOii, б. ЮК 2 ния г;л-;Ч ;1ОСИ1 налО 3, бх ферны : рс таймер , .IHUHK; 5 : 11дср кк1, с;- ;-;ации, счетчик t; 1 ектор(5;з. блок 7 ми;цк);1ро- rpaMMiiOi O уиравлснш, буферный б.лок 8 памяти, формирователь 9 а. 1го ;1итмичсс-кнх тестов, блок 10 параметров век 1 оров, счетчик П логических номе()ов, блок 12 обмена с контро.пируемым г ифровым блоком, бло1 13 , счетчик 14 длины BCKTOpjOB, вь1ход- ной коммутатор 13, регистр 16 набора, коммутатор f7 входных данных.

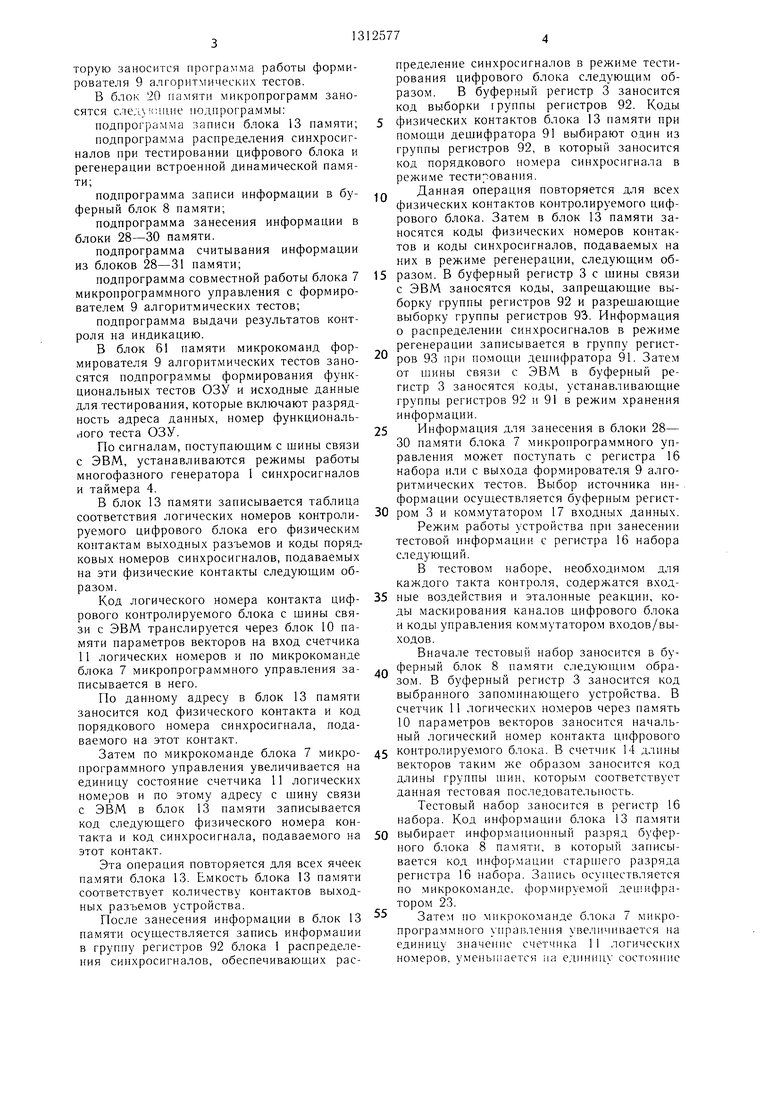

Блок 7 микронрограммног о у11раг лег.ия ((Ьиг. 2) содержит коммутатор 18, нрс)Г)ам- мный регистр 19, 6,:ioK 20 IUIMHTH микрокоманд, мультиплексор 21, нифратор 22, дешифратор 23, мультии.лексор 24 адреса, три|-- геры 25 и 26, элемент ИЛИ 27, блок 28 памяти масок канал.ов, бл(и 29 намятн тес- товьгх наборов, б. шк 30 памяти управления коммутатором входов/В з1хо;1ов, блок 31 намя ти кода оиерации.

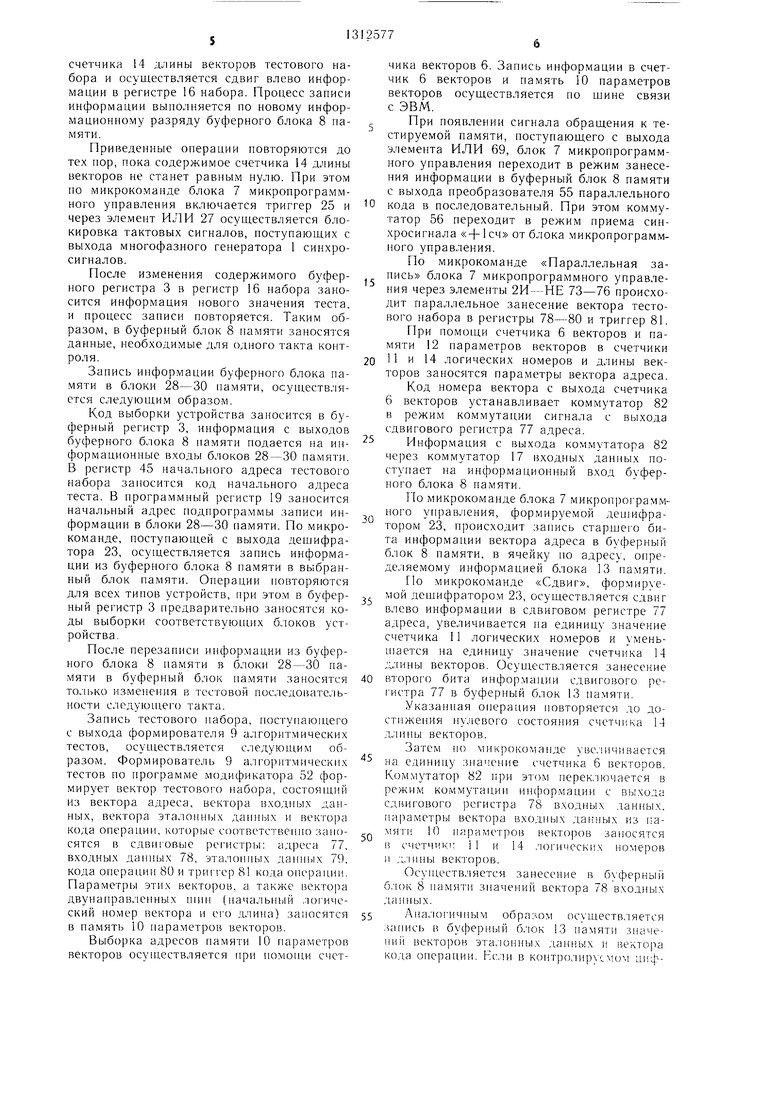

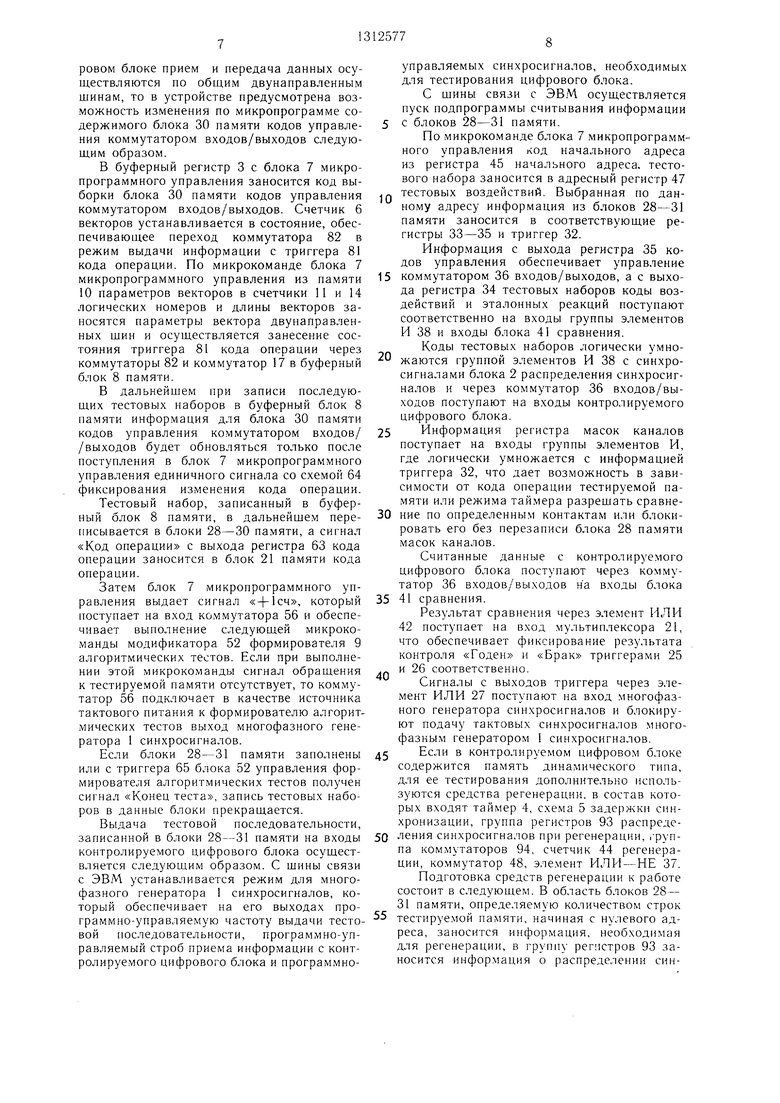

Блок 12 обме1 ;а с ко1Г|-ро.ги 1уем1)1м ци(|)- ровым блоком (срнг. ;) содер; а т три. Ч ср 32, региетр 33 масок каналов, регастг 34 тестовых наборов, регистр 35 ко.,.оз унрав. и;- нля коммутатором входов/выходов, Ko;vi- мутатор 36 в.чодов/выходов, эле 1е1гг ИЛИ ME 37, элемент 39 зад.ержки, Г1ервую гр-сиау элементов И 40. вторую I pyHriy элементов И 38, разрядный блок 41 сравнения, элемент ИЛИ 42, коммутатор 43 резу. ьтата. Мультиплексор 24 адреса (фнг. 4) содержит счетчик 44 регеперапии, регистр 45 начального адреса тестового набора, ком

0

0

5

0

5

0

5

мутатор 46, адресный регистр 4/, коммутатор 48, шифратор 49, регистр 50 конечного адреса тестово1 о набора, схему 51 сравне- н и я.

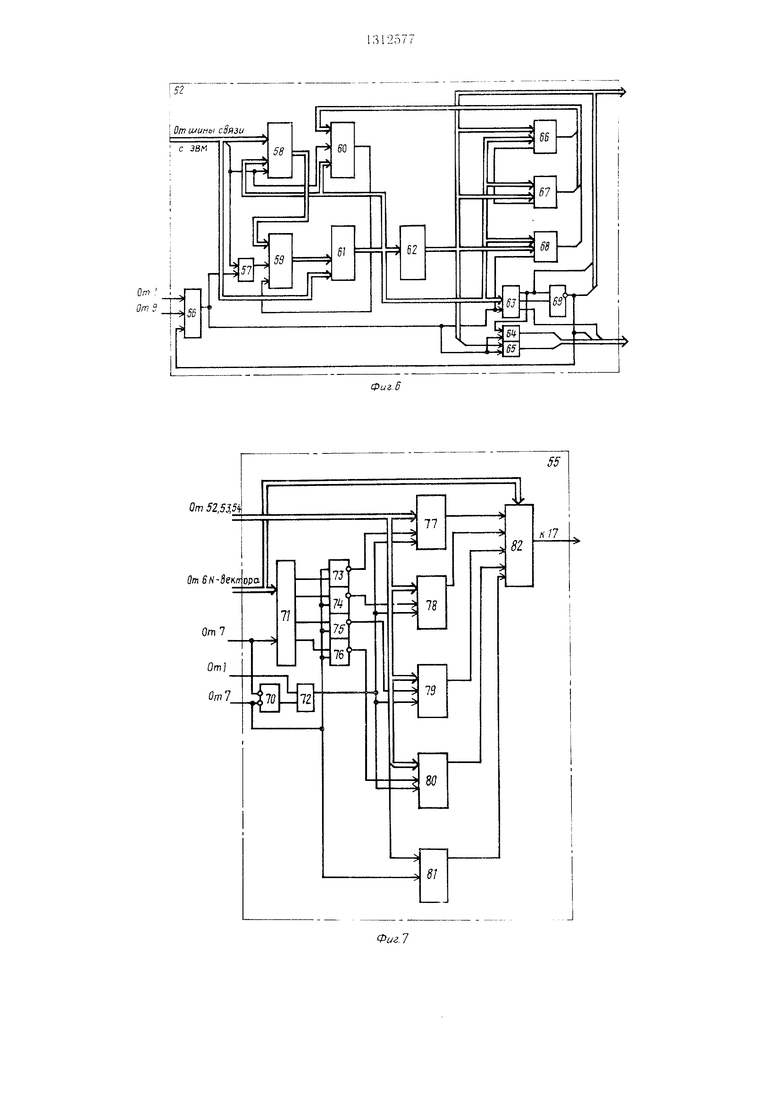

Формироватс.ть 9 а. п оритмических тестов (сЬиг. 5) состоит из модификатора 52 адреса, блока 53 формирования адреса, блока 54 формирования данных, иреобразо- вателя 55 парал. зельного кода в последовательный. Модификатор 52 адреса формирователя алгоритмических тестов (фиг. 6) содержит коммутатор 56, элемент ИЛИ 57, коммутатор 58, программный регистр 59, коммутатор 60, память 61 микрокоманд, дешифратор 62 микрокоманд, регистр 63 кода операции, схему 64 фиксации изменения кода операции, триггер 65, 1рограммные счетчики 6(:)--68, элемеггг ИЛИ 69.

Преобразователь 55 паралле. п но1Х ) код.- в последовательный (фиг. 7) содержит элемент ИЛИ 70, деши(|)ратор 71, элемент 2И 72, группу элементов 2И - ИЕ 73-76, регистр 77 адреса, регистр 78 входных данных, регистр 79 эталонных данных, pei-истр 80 кода onepaiiHH, триггер 81 кода операции, коммутатор 82.

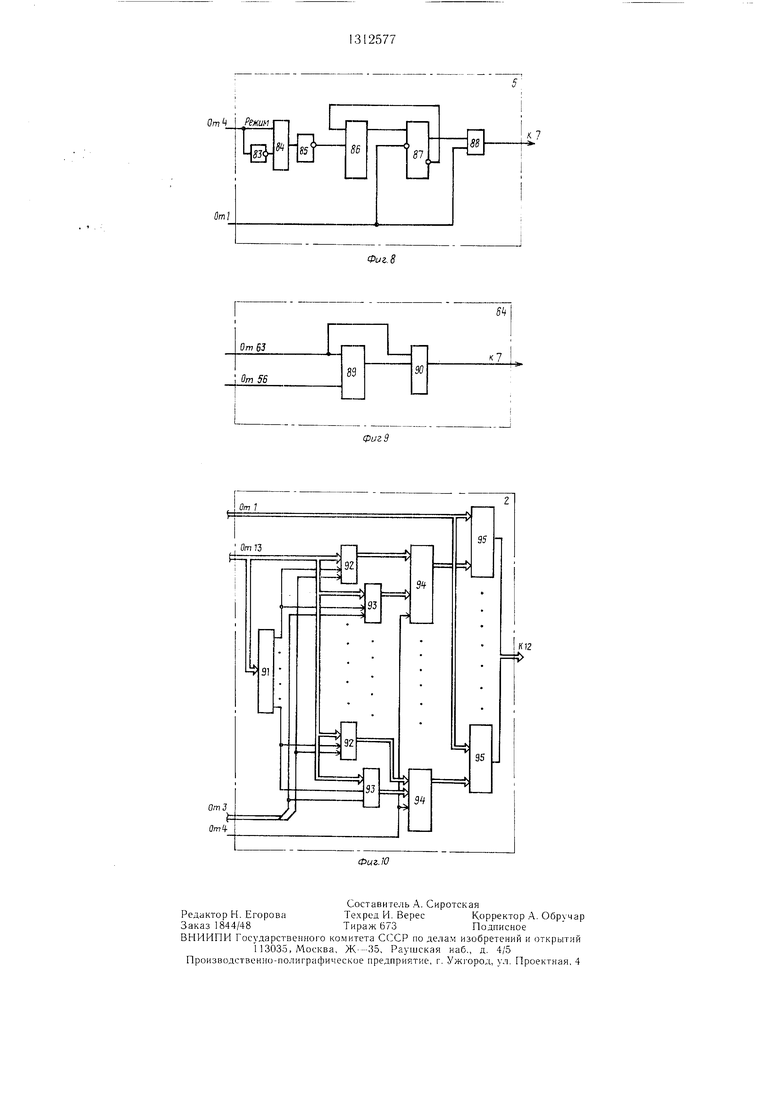

Линия 5 задержки синхронизации (фиг. 8) содержит элемент .83 задержки, элемент 84 равнозначности, э.; емент И--ИЕ 85, триггеры 86 и 87 и элемент 2И 88.

(хема 64 фиксации изменения кода операции (СФИКО, фиг. 9) содержит триггер 89 и схему 90 равнозначности. Б,1ок 2 рас- преде;1ения еинхросигпалов (фиг. 10) со- де)жиг де;пи(}5ратор 91, первую груипу ре- | истров 92, вторую г рупну регистров 93, первую гругшу коммутаторов 94, вторую 1 руину ко.ммутаторов 95.

Цифровой контролируе.мый блок нодк.-по- чается к входам/выходам коммутатора входов/выходов блока обмена с коитро, 1ируе- мым цифровым блоком (объем контроля, пеш иитания и o6mei o сброса не показа1 ы).

По сигналу «Общий сброс, поступакиде- л Гу по пшне связи с ЭВМ. осуществляется устапов в исходное состояние всех регистров счетчиков к тригг еров устройства. Так как в устройстве реализован гликронрограмм- 1П)1Й при1ц.1нн управления, иеред началом работы оеун1.еетвляется зашгсь программы его фу:-п п,иоиирова1П1Я в б..:1ок 20 гшмяти .микроко.мачд блока 7 микрог1()ограммного унравления и намять 61 микрокоманд фор- мнровате.:1Я 9 алгоритмических тестов, для чего с 1НИНЫ связи с ЭВМ в нрограммный )ег11етр 19 ;UIHOCHTCH код адреса б. юка 20 намятн л1И: |1окома}Г |., iio которому осун1ест- в. 1яется за;1ИС1 микрокоманды в блок 20 на- мяти (.команд.

Данная операция повторяется для всех нрограл м работы б. юка 7 микропрограммного унрав.чения.

От 1НИНЫ связи с ЭВМ через к() тор 58 в 1грог)аммный ктистр 59 ;5аносится код адреса гп;мяти 61 микрокоманд, в которую заносится программа работы формирователя 9 алгоритмических тестов.

В блок 20 памяти микропрограмм заносятся c ie;i. ицие иодпрограммы:

подпрограмма записи блока 13 памяти;

подпрограмма распределения синхросигналов при тестировании цифрового блока и регенерации встроенной динамической памяти;

подпрограмма записи информации в буферный блок 8 памяти;

подпрограмма занесения информации в блоки 28-30 памяти.

подпрограмма считывания информации из блоков 28-31 памяти;

подпрограмма совместной работы блока 7 микропрограммного управления с формирователем 9 алгоритмических тестов;

подпрограмма выдачи результатов контроля на индикацию.

В блок 61 памяти микрокоманд формирователя 9 алгоритмических тестов заносятся подпрограммы формирования функциональных тестов ОЗУ и исходные данные для тестирования, которые включают разрядность адреса данных, номер функционального теста ОЗУ.

По сигналам, поступающим с шины связи с ЭВМ, устанавливаются режимы работы многофазного генератора 1 синхросигналов и таймера 4.

В блок 13 памяти записывается таблица соответствия логических номеров контролируемого цифрового блока его физическим контактам выходных разъемов и коды порядковых номеров синхросигналов, подаваемых па эти физические контакты следующим образом.

Код логического номера контакта цифрового контролируемого блока с щины связи с ЭВМ транслируется через блок 10 памяти параметров векторов на вход счетчика 11 логических номеров и по микрокоманде блока 7 микропрограммного управления записывается в него.

По данному адресу в блок 13 памяти заносится код физического контакта и код порядкового номера синхросигнала, подаваемого на этот контакт.

Затем по микрокоманде блока 7 микропрограммного управления увеличивается на единицу состояние счетчика 11 логических номеров и по этому адресу с щину связи с ЭВМ в блок 13 памяти запись вается код следующего физического номера контакта и код синхросигнала, подаваемого на этот контакт.

Эта операция повторяется для всех ячеек памяти блока 13. Емкость блока 13 памяти соответствует количеству контактов выходных разъемов устройства.

После занесения информации в блок 13 памяти осуществляется запись информации в группу регистров 92 блока 1 распределения синхросигналов, обеспечивающих распределение синхросигналов в режиме тестирования цифрового блока следующим образом. В буферный регистр З заносится код выборки группы регистров 92. Коды

5 физических контактов блока 13 памяти при помощи дешифратора 9 выбирают один из группы регистров 92, в который заносится код порядкового номера синхросигнала в режиме тестирования.

Данная операция повторяется для всех физических контактов контролируемого цифрового блока. Затем в блок 13 памяти заносятся коды физических номеров контактов и коды синхросигналов, подаваемых на них в режиме регенерации, следующим об5 разом. В буферный регистр 3 с щины связи с ЭВМ заносятся коды, запрещающие выборку группы регистров 92 и разрешающие выборку группы регистров 93. Информация о распределении синхросигналов в режиме регенерации записывается в группу регист ров 93 при помощи дешифратора 91. Затем от тины связи с ЭВМ в буферный регистр 3 заносятся коды, устанавливающие группы регистров 92 и 91 в режим хранения информации.

5 Информация для занесения в блоки 28- 30 памяти блока 7 микропрограммного управления может поступать с регистра 16 набора нли с выхода формирователя 9 алгоритмических тестов. Выбор источника ин- формации осуществляется буферным регист0 ром 3 и коммутатором 17 входных данных. Режим работы устройства при занесении тестовой информации с регистра 16 набора следующий.

в тестовом наборе, необходимом для каждого такта контроля, содержатся вход5 ные воздействия и эталонные реакции, коды маскирования каналов цифрового блока и коды управления коммутатором входов/выходов.

Вначале тестовый набор заносится в бу,. ферный блок 8 памяти следуюп-1им образом. В буферный регистр 3 заносится код выбранного запоминающего устройства. В счетчик 11 логических номеров через память 10 параметров векторов заносится начальный логический номер контакта цифрового

5 контролируемого блока. В счетчик 14 длнны векторов таким же образом заносится код длины группы П1ИН, которым соответствует данная тестовая последовательность.

Тестовый набор заносится в регистр 16 набора. Код информации блока 13 памяти

0 выбирает информационный разряд буферного блока 8 памяти, в который записывается код информации старшего разряда регистра 16 набора. Запись осуществляется по микрокоманде, формируемой деи ифра- тором 23.

5 Затем по микрокоманде блока 7 микропрограммного управления увеличивается на единицу значение счетчика 11 логических номеров, уменьшается иа единицу состояние

счетчика 14 длины векторов тестового набора и осуществляется сдвиг влево информации в регистре 16 набора. Процесс записи информации выполняется по новому информационному разряду буферного блока 8 па- мяти.

Приведенные операции повторяются до тех пор, пока содержимое счетчика 14 длины векторов не стапет равпым нулю. При этом по микрокоманде блока 7 микропрограммного управления включается триггер 25 и через элемент ИЛП 27 осуществляется блокировка тактовых сигналов, поступающих с выхода многофазного генератора 1 синхросигналов.

После изменения содержимого буферного регистра 3 в регистр 16 набора заносится информация нового значения теста, и процесс записи повторяется. Таким образом, в буферный блок 8 памяти заносятся данные, необходимые для одного такта контроля.

Запись информации буферного блока памяти в блоки 28-30 памяти, осуществляется следуюц 1им образом.

Код выборки устройства заносится в буферный регистр 3, информация с выходов буферного блока 8 памяти подается на информационные входы блоков 28-30 памяти. В регистр 45 начального адреса тестового набора заносится код начального адреса теста. В программный регистр 19 запосится начальный адрес подпрограммы записи информации в блоки 28-30 памяти. По микрокоманде, поступающей с выхода дещифра- тора 23, осуществляется запись информации из буферного блока 8 памяти в выбранный блок памяти. Операции повторяются для всех типов устройств, при этом в буферный регистр 3 предварительпо за}1осятся коды выборки соответствующих блоков устройства.

После перезаписи инфор.мации из буферного блока 8 памяти в блоки 28-30 памяти в буферный блок 1амяти заносятся только изменения в тестовой последовательности следующего такта.

Запись тестового набора, поступающего с выхода формирователя 9 алгоритмических тестов, осуществляется следующим образом. Формирователь 9 алгоритмических тестов по программе модификатора 52 формирует вектор тестового набора, состоящий из вектора адреса, вектора входных данных, вектора эталонных данных и вектора кода операции, которые соответственно запо- сятся в сдвиговые perHCTpi i: адреса 77, входных данных 78, эталоьпц,1х данных 79, кода операции 80 и триггер 81 кода операции. Параметры этих векторов, а также вектора двунаправленных тин (начальный логический номер вектора и его длина) заносятся в память 10 параметров векторов.

Выборка адресов памяти 10 параметров векторов осуществляется при помощи счст

5

0

0

Q 5

0

5

5

чика векторов 6. Запись информации в счетчик 6 векторов и память 10 параметров векторов осуществляется по щине связи с ЭВМ.

При появлении сигнала обращения к тестируемой памяти, поступающего с выхода элемента ИЛИ 69, блок 7 микропрограммного управления переходит в режим занесения информации в буферный блок 8 памяти с выхода преобразователя 55 параллельного кода в последовательный. При этом ком.му- татор 56 переходит в режим приема синхросигнала «+1сч от блока микропрограммного управления.

По микрокоманде «Параллельная запись блока 7 микропрограммного управления через элементы 2И-НЕ 73-76 происходит параллельное занесение вектора тестового набора в регистры 78---80 и триггер 81.

При помощи счетчика 6 векторов и памяти 12 параметров векторов в счетчики 11 и 14 логических номеров и длины векторов заносятся параметры вектора адреса.

Код номера вектора с выхода счетчика 6 векторов устанавливает коммутатор 82 в режим коммутации сигнала с выхода сдвигового регистра 77 адреса.

Информация с выхода коммутатора 82 через коммутатор 17 входных данных поступает на информационный вход буферного блока 8 памяти.

По микрокоманде блока 7 микроп1)ограмм- ного управления, формируемой дец ифра- тором 23, происходит запись старщего бита информации вектора адреса в буферный блок 8 памяти, в ячейку по адресу, определяемому информацией блока 13 памяти.

По микрокоманде «Сдвиг, формир е- мой дещифраторо.м 23, осуществляется сдвиг влево информации в сдвиговом регистре 77 адреса, увеличивается на единицу значение счетчика 11 логических номеров и умень- 1пается на единицу значение счетчика 14 д.:1ины векторов. Осуществляется занесение второго бита информации сдвигового регистра 77 в буферный блок 13 памяти.

Указанная операция повторяется до достижения нулевого состояния счетч1-;ка 14 д;1ины векторов.

Затем по микрокоманде уве. ичивается на единицу значение счетчика 6 векторов. Коммутатор 82 при этом переключается в режим коммутации ин(10рмации с В1з1хода сдвигового регистра 78 входных данных, 11а|1аметры вектора входных даь иых из памяти 10 параметров векторов заносятся ( счетчикк 11 и 14 логическ1 х номеров и длины векторов.

Осуществляется занесение в б ферный 6.;ioK 8 памяти значений вектора 78 входных данных.

Ана:1огич11ым образом осуществляется запись в бу{ 5ерный б.пок 13 памяти зпаче- HHi i векторов эталонных данных и вектора кода операпии. Нсли в контролируемом цифровом блоке прием и передача данных осуществляются по общим двунаправленным шинам, то в устройстве предусмотрена возможность изменения по микропрограмме содержимого блока 30 памяти кодов управления коммутатором входов/выходов следующим образом.

В буферный регистр 3 с блока 7 микропрограммного управления заносится код выборки блока 30 памяти кодов управления коммутатором вход,ов/выходов. Счетчик б векторов устанавливается в состояние, обеспечивающее переход коммутатора 82 в режим выдачи информации с триггера 81 кода операции. По микрокоманде блока 7 микропрограммного управления из памяти 10 параметров векторов в счетчики 11 и 14 логических номеров и длины векторов заносятся параметры вектора двунаправленных щин и осуществляется занесение состояния триггера 81 кода операции через коммутаторы 82 и коммутатор 17 в буферный блок 8 памяти.

В дальнейщем при записи последующих тестовых наборов в буферный блок 8 памяти информация для блока 30 памяти кодов управления коммутатором входов/ /выходов будет обновляться только после поступления в блок 7 микропрограммного управления единичного сигнала со схемой 64 фиксирования изменения кода операции.

Тестовый набор, записанный в буферный блок 8 памяти, в дальнейщем переписывается в блоки 28-30 памяти, а сигна.т «Код операции с выхода регистра 63 кода операции заносится в блок 21 памяти кода операции.

Затем блок 7 микропрограммного управления выдает сигнал «-|-1сч, который поступает на вход ко.ммутатора 56 и обеспечивает выполнение следующей микрокоманды модификатора 52 формирователя 9 алгоритмических тестов. Если при выполнении этой микрокоманды сигнал обращения к тестируемой памяти отсутствует, то коммутатор 56 подключает в качестве источника тактового питания к формирователю алгоритмических тестов выход многофазного генератора 1 синхросигналов.

Если блоки 28-31 памяти заполнены или с триггера 65 блока 52 управления формирователя алгоритмических тестов получен сигнал «Конец теста, запись тестовых наборов в данные блоки прекращается.

Выдача тестовой последовательности, записанной в блоки 28-31 памяти на входы контролируемого цифрового блока осуществляется следующим образом. С щины связи с ЭВМ устанавливается режим для многофазного генератора 1 синхросигналов, который обеспечивает на его выходах программно-управляемую частоту выдачи тестовой последовательности, программно-управляемый строб приема информации с контролируемого цифрового блока и программноуправляемых синхросигналов, необходимых для тестирования цифрового блока.

С щины связи с ЭВМ осуществляется пуск подпрограммы считывания информации 5 с блоков 28-31 памяти.

По микрокоманде блока 7 микропрограммного управления код начального адреса из регистра 45 начального адреса, тестового набора заносится в адресный регистр 47

,,- тестовых воздействий. Выбранная по данному адресу информация из блоков 28-31 памяти заносится в соответствующие регистры 33-35 и триггер 32.

Информация с выхода регистра 35 кодов управления обеспечивает управление

5 коммутатором 36 входов/выходов, а с выхода регистра 34 тестовых наборов коды воздействий и эталоннь х реакций поступают соответственно на входы группы элементов И 38 и входы блока 41 сравнения.

Коды тестовых наборов логически умно жаются группой элементов И 38 с синхросигналами блока 2 распределения синхросигналов и через коммутатор 36 входов/выходов поступают на входы контролируемого цифрового блока.

5 Информация регистра масок каналов поступает на входы группы элементов И, где логически умножается с информацией триггера 32, что дает возможность в зависимости от кода операции тестируемой памяти или режима таймера разрещать сравне0 ние по определенным контактам или блокировать его без перезаписи блока 28 памяти масок каналов.

Считанные данные с контролируемого цифрового блока поступают через коммутатор 36 входов/выходов н а входы блока

5 41 сравнения.

Результат сравнения через элемент ИЛИ 42 поступает на вход мультиплексора 21, что обеспечивает фиксирование результата контроля «Годен и «Брак триггерами 25 и 26 соответственно.

Сигналы с выходов триггера через элемент ИЛИ 27 поступают на вход многофазного генератора синхросигналов и блокируют подачу тактовых синхросигналов многофазным генератором 1 синхросигналов.

5 Если в контролируемом цифровом блоке содержится память динамического типа, для ее тестирования дополнительно используются средства регенерации, в состав которых входят таймер 4, схема 5 задержки синхронизации, группа регистров 93 распреде0 ления синхросигналов при регенерации, I pyn- па коммутаторов 94, счетчик 44 регенерации, коммутатор 48, элемент ИЛИ - НЕ 37. Подготовка средств регенерации к работе состоит в следующем. В область блоков 28 - 31 памяти, определяемую количеством строк

5

тестируемой памяти, начиная с нулевого адреса, заносится информация, необходимая для регенерации, в группу регистров 93 заносится информация о распределении сииxpocupiia.MOH при рег енсрации, i-; счетчик 44 pereiie|iauiiij с ишиы сзй: ,я с ЭВМ заносится код информации, которая оире.амяст коэф- с)ициент делен11И счетчика 44 регенераи,.

В таймер 4 от 1нииы связи с iiM заносится информация, определяющая вид рег; нерации (пакетная icitt распредс.пеиная). период регенерации, цикл регенерации, количество строк тестируемой .

Затем осуществляется запуск таймера . На управляющем выходе таймера 4 поя:;- ляется информация, определяющая режим работы устройства «Ре1 енерация или «Тестирование, а на еиихронизи уюи1,е ubixo/ie имнульс (цри раснределенной регенерации) или серия имнульеов (ири пакетной регеие- рации), которые постуиают на )IЙ вход счетчика 44 регенераци.

11о cni4ia/iy «Регенерация таймера 4 линия 5 задержки сн||лр{1|1иза11ии блоки,)у(т иодачу такго15ых и;-,Г 1ул1:,ео1 на синхрони- ;4г;ру()И1ий зхсзд блока 7 viHKpniiiiorpaMMnoro ираи, ;ения, тем самым нриоетпиавливает ei O работу на время регенерации.

Э 1 О г же сип.а; иос:туиает па управляю- ии-Ц входы грунпы комм 1 аторов 94. коммутатор 48 н иход г леме:гг V LrU-l MI: 27, что cooTBt TCTBeiiiiO 1;од,кл)Очаст к уИ|)авля1о; и М входам )уииь ко п татор()1 95 H ixcvibi иы pei iicinoi; IK S. K; i4}pi ie сасиреде.тяюг си11хросиг |а,:;ь1 при iieiXMicpaHni. : Cvi;u CT- :. ;«)M) TaiUni; a/ipecribix входо;; 5. 1о;иж 28 H памяти к (;;:.aM 44 г;ег .- ;1е1)ации и o6eeiie4 iiiriiO 6,)ак)ч|) соав: . ИИЯ Им liCe V ;-;ОИТИ к ,; ;;( ;:.,. |И Л емг;гО

и,ифрово 0 б,:1ока .la i l ieviH pereiU naiuiii.

1 миульс1м, пс);вля;о;п -:е1;н на einixpouMsu- ру ОИ1ем 15)1ходе ,)а. ири ix Monui счетчика 44 ptM eiienaiia: о5есиечиь:.по1 черебо:; ячеек иамятм ; ), 28-3;, отведеп- Н1)1х чод ии(|1О1)лча:1И|0 д 15: регеиерацич. ое чцест|5. тем caMi.ifi; cj6pnH,e4iie ко ;5еем строкам тестируемой иамяти лоитполигп ;:- мого ци(рроио Ч) 6.:iOKa.

I и) ф)очту- улравлиюпк му си; {ай -юр: 4 ли:;:-;: х- з- держки сиих.1оии- заии1 иерехо ии в режнх ;, 1)Гк СИ :ч ; аю.ий :к) )вы ил;и льеов :it; ixo,i, .

1;е;|ехо;дм i.i Ч сгирова тех-,

I :-: H( i::; ,i;ji ,ia;ui( -. v..:,Baiiiie р1.:-;; Льта а )i :.4 и |)лве|}::и); а,;и iujpaKs ii т;Л;: i ep;sx 2;) i; 2: и ;u.;;u:4 eooo

еиязи e ЗВЛ (-.1. A:e.. ;);1д:-;-„ации ::e ио- .).

jla И ,uiKaiuiio ijene;iai3tr ь .ииг- HLie И(.;|цие с выходов )м.( 44 рез , ib гата и Bi.,ixo. j,ii(.;ro AOui . iVi птора 16.

Л,;: выдачи даччых бл(1ча 12 обмем:: с

ХОИТрО, П-1руеМЬ; ; mUppvJBBlM n;i;):u)M iia ,икацик/ иеобхоД11м;) н ci;e i 4i;:; ; .чогмч;:0

ских номеров занести иачалы:1; Й .югичеекиг iiOMep когсакта об ьекта кон 11)оля, а в сче-|- 14 длищ 1эектО;)ов занести 1;од длины lieieropa. В npoi-раммиый регистр И; заноси гея начальники адрее но.:ц|рограммы Bi)i.4a- чи результатов Kotrrpo,,. В буфе|)и.1,:й ре- 1 иетр 3 заиоеитея Ko;i выбираемого )егие 1- ра. который иере лючает необходимое иа- иравление коммут атора 43 ))ез 1ьтата. 1хо,;, е выхода б;;ока 13 цамяти выбираем необходимый ищ рормациониый разряд иг ,и liOMo- и;и выходного коммутатора 15.

При микрокоманде б.чока 7 .мик ;о11 ;ом-ра:

.iioio М1рав leiit я ь pei и 1г) IM j la

1 еикя иис|.1ормация . з jioi i i(unp iroTa 1э la 1 1оы1Ч(..с1чЧ ч 10 кр 1ь и it t

а с Ц11111Ц а I 1 р/ г V 1 1 KL- в и | II . 1 л 1 J I II 111 ми

к пи )с 11.1 I 1 Iи 1

I II t к с чО1 оJ |1 I 1 I I

1 I I 1 PLnilf 1 Ii I

1 , И01 ail I

0; I I i 1 ill I II li l о JO 5 I V I 1 1 II pi1

1t МИИ I.и 1 1 N и111 1 1 с M

01II It ,11

5

i. N cTporcTBi; д.:1я тестовогч; ко1Г1р Г я luuppoiiLiix блоков, соЛлМ1 ка;цее зуфери;,; регист. счетчик .LIH-MJ В(чегороз счегчих

иои комм 1 ci iX)}). блох обмена с К;:: гро. и;- руемым ци;1;ровыу блск,:;м. блок ;;.);.;- граммпого у1|равлеиия. б фе|5иый бл;)Х тч, реглетр набоаа. чричем блок : 1 о;ггролип ел ы м Д -;фронь м блок1 IM ч .i;:,e;i/KiiT

КОУ 1УТатОр ЗXi.;..TOU/Ii XOД)i;. р:..; l-.o/ii/ii

ч: 1а1 леиия коммхта г ходо:-;; .,;ло, д.и. регистр тестовых 1;аборов, рег-ч тр ,ас;;;: ;.;а- иа.юв, разрял.иый б,х;)К еоавнеиия. зхемсчгг i4. ii 1, комм -татор резу/и/гата. |.;-м;гт за- .|.ер;кки, ч:)ичгм I pyaaa pa.ipw. jxjix зыхо.и.ч; c4C ;4iii a .юги - еских иоу;е; ов c(,ie;.Имена с адрес;ИлХ 3Xo,uj;i б.кжа , ;-чк ии;ие заД( lOi H :ес;-ч; d iior.i, :,.; i,--;,;;.;, ibjixcj;:,;: KOiii )o..:;pve .м): о i: ;q p ;b:;ro :;;.iii.;

Х 1 ;)ОКегВа. JC.iBa i ip /a.ia 31-,i S,;.:,: : :.ч,;..;;

,:аХ И1и со; у1:;:ена с rjjvhniii ; а;;.р:. : ,i j.oii Bixo.i4;.jro I aT(j:;a, вв:х;;ч, ;;о--о j)oro еос Д-i и е 1; с :;i ,ор e-i4,i oi iii,;:,: ; /у. ; v; ;Ч;

ив.ходами i: : и;а1-и, к;;,;:.: и.избкм ;; ва. iiM(;iopMaii.;i::jnH)ix i;;xyj,(;ii -U iiieii-:: набора ЧОЛ.Н, :;очг;;а х ij;i;4L задачи/; :;:.чал ; . if)M(;pa ТесУП; уст ;};. i;epl:.::-; i ,

3:.xo.lo3 буферио ;} pciiuypa eaey.}y;ci;c с иа Bx;y:ioi. гачауз1И.;: загруз;::: i-::: ;:; :ч;Г ;

. ювии устройства, выход нулевого разряда счетчика д.чины вектора и выхо.ч элемента ИЛИ соединены с входами управления переходим блока микрогфограммного унрав- ./ ения, выходы нризнаков микрокоманд которого соединены с информационным: входами регистра масок каналов, регистра т ес- тоного набора, регистра Ko;i,a унраилсння коммутатором вх-)Д(;в/выходоз, иервьи, нто- |1ой, ipef;i; и кмвертый разрядные выходы ноля адреса блока микропрограммного ун- рав.тения соединены с входами сннхрон;1за- ции буферного pei HCTpa, счетчика логических номеров, счетчика длинв векторов и регистра набора соответственно, rpyiHia информационных входов выходного комму- та 1 ора еоединена с грунной вв1ходов ком- My i aTopa оезулыата, выход элемента за- ;iej)KKH соедннен с синхровходслч разрядного блок;; сравнения, rpyiuia выходов «Равно которого соединена с групной входов элемеггга i-iJIi-i и с первой i-pyniioft инфо MaiUiCMiii.ix входов коммутатора результата, iHkjjjaH группа информаниоиных входоз которого соед 1непа с группой выходов комчч - тат(Л)а входов/выходов н с rpyniion зходо ; раз)е нен1-1И соответству1оп1их разрядов раз- )ядного б. юка сравнения, первая группа ипформаннонных входов которого соеди1;е- на с 1 руи11ой В1мходов penieTpa тестового набора н с ретьсГ1 грунной информацион- iH-ifx входов коммутатора результата, четвертая группа информационных входов которого соединена с г } ппой выходов )е1 ист- ра масок каналов, ад()еепые входы коммутатора )1езультата соединены с второй группой вь:Ходов бу(|)ерпого регистра, группа управ.1Я1О1П,И-Х входов коммутатора вхо- л.01 /выходов соединена с групной выходов per ic i j)a кодов управ.тения комм тато- i)0vi 11ходои/1П1 хол,ов, груниа входов/выхоДО КОТО)ОГО ЯПЛЯСТСЯ ГруГН ОЙ ВХОДОВ/БЫx(X4Oi ус 1 ройст15а для подключения к зхо- л. а м / в i )1 X о д а. м к о н т р о л и р у е .м (; го ц н ф р о - ВО1Ч) блока, (лличающееся тем, что, с целью рас1иирсгн1я (области 1грименения за счет обеспечен -:;- возможности кощ-роля микро in)OH( ct;op;ibix с бо;1ыпнм объемом (не1)ативпог() запоминающего устройства, оно соде}1 : 11т сче-гчик векторов, зе.| па- пар;;метрО1) век-горов, мн01-офаз ;ьт ге- рос1:1 н;;л;:, та11мс). ,:1ип;:;о за- :;;о;;р ;:и |-е. п алго|ИГ :ических л распределения сннхроснг- 1-а-гор входных даи:Н.1х. а б/юк i |;1ОЛН1) пифров1: М б/юком содержит триггер, элемент ; Уч-П11Ы э.чементов И, причем HCpiibHi выход Miioro(ha3Horo генератора сии- хросигиа/н.), |,ч еди:|еп с снихровходамн таймера, задержки и формирозате.тя гмпч: :скпх -rec-fOB, со c-rpo6npy OHUiM кс)мм л-а-гора 15х;- дов/ 5ых;;дои ;; с вхо- i ie:i:-;i задери;ки. второ:; выход л;но- ого I eHcna-ropa )С Г :ал;;н i.-oene)a-r(ji) сип . (Ы -гсг гон, ,( па,, ком л: обмена с ко л.опо;ин1-|-е,11ли ИЛИ Hi;, Д1

0

5

0

5

0

5

0

5

дипеп с синхровхо;1ами. регисгра л;асок ка- на.:1ов. регистра TecTOBSix н.аборов, регисг - а кодов управления коммутатором входов/выходов и триггера, 1Ип1ход которого соединен с первым входом элемента ИЛИ -ИВ, выход которого сое,-1ннеп с ирар,.-;яюп1ими входами Э-лел;еиго1 И iiepBOi i i pyniibi, i-рун- па выходов кС Тс рого соединена с-|;торой HHti)Oj)ManHoiiui :x входо ; разряд- HOf-o б.юка сравнения, группа информационных входов элемен-гоп 1-1 первой грунпы соед1П1ена с группой выходов регистра масок каналов, гр)Л1на первых входов э.че- MeirrOB И второй i-pynni)i соединена с груи- ной В1)1ходов регистра тестовых наборов, rpyiHia вторых входов э,-1ементов И в-горой ру1Н1Ы соединена с выходами б/юка расире- де. синхросигна/юв, |-руниа выходов эле- ме;гго}5 -- второй г|)-|нн--1 соединена с 1)уи- иой ипформанпоппььх г ходов коммутатора входов/выходов, BTOpciii вход э, еменга И1: соедниС; с :ервым выходом -гай- мера, с сннхровходом б.-|ока -1аснреде.-1ения с;; 11Х)осигиа;;ов, с ннфор :ац Ч) нходол лп;1ии задержка ii с iixo;u)M иерного 1)азря- да кода иег ехс да блока микропрограммного зп ран.- енпя, зторои разряд кода нере- хода KOTOpoi o coe;;iii;en с выходом .-iniHin задержки, иервая г П ина входов блока рае- 11 5еде;1ения cinixpociiinia.ioB соед1 иена е груиной в з1ход1П1 многофазно1 о генератора eniixpocin i;j.-;oB, 1)ХС)Д |1;- Зре1непия ко-го1-)о;ч) соед)1е1; е выхо. прнзна а г-срехода к с.-тедуюи сй мик|П1команде б, ;и1-,роиро- грамм1-;( ун. группа входов зада- шя условий перехода которО 0 подключена к П1иие задаг и ; -с, :ов1:й перехода уе-грой- ства, i н1ИИч з:;. 1,,: li ,я оиеранин poi o юдключси;.; ;i ;diooMau iOHHi-)ie Х()дь буфепного регистра, зь:ход котор и о соединен с первым -ираБ;1Я О1Иим входол татора входных /lainniix, второй правляк)- Н1ИЙ вход которого соединен е выхо;1ом фор- NHipOBaTe, а,-11Ч)р П мических гестов, адресные входы ко-гог ого соед1 не1Н 1 е 1азряд- ными выходами ече-1-чика векторов и с адрее- FibiMH входами уз.1а нa iяi-и иараме-грС)В векторов, выходы KOTOpoi o соединены с HHibop- маннонпыми входами счетчнка /югичееких номеров н ече-1-Ч :ка д.-щпы (. /г-й улл- ход jiei HCTpa набора (;; длин:; -|-ест(И5Ого набо1-;а) соедннен с и1;фс 1мац1:онньн-1 вхо/иох; гора вхо даннглх. )ро- го соедипоп с вх;;дом счи- 1ЮГО блока на ;я-| 1, зхо;; ;

, 15)1Ходом П1)лм Hiioi - aMXiHoro Иравлс- кода адреса ;икроко:ОД к. с ;; : К ЗХС Дал

еста op i;ip: ;ia-гeля . . i Topvi i :ii.ixo,, - аи:.п;к - о: ро: па : : ного

соединс с П 1 --л аД; 1еса блока tnni. зходы зада л-я манды ч--гройс-г; а i ад;)ееа iiiKpi мических :ес еединсн с rpiM

iCPCXOP.a n.-li;i

хросигналов и таймера подключены к ujHiie задания длины вектора и кодов длины тактов работы устройства соответственно, а син- хровход счетчика векторов соединен с шестым разрядным выходом поля адреса блока микропрограммного управления, седьмой, восьмой, девятый разрядые выходы ноля, адреса которого соединены соответственно с первым, вторым и третьим разрядными входами задания режима работы формирователя алгоритмических тестов, группа выходов которого соединена с группой адресных входов блока микропрограммного управления, вторая группа выходов буферного регистра соединена со второй группой входов блока распределения синхросигналов и с первой группой информационных входов буферного блока намяти, вторая группа выходов блока памяти соединена с третьей групгюй входов блока распределения синхросигналов и с второй группой информационных входов буферного блока намяти, группа выходов которого соединена с группой входов загрузки микротестов блока микропрограммного управления, а информационные входы блока памяти подключены к шине задания логических номеров входов/ /выходов контролируемого цифрового блока устройства.

2. Устройство по п. 1, отличающееся тем, что формирователь алгоритмических тестов содержит модификатор адреса, два

0

5

ишфратора и преобразователь параллельного кода в последовательный, причем входы задания начальных условий модификатора адреса соединены с входами адреса микротеста формирователя, первая группа выходов модификатора адреса соединена с первой группой информационных входов преобразователя параллельного кода в последовательный и через первый шифратор с второй группой информационных входов преобразователя параллельного кода в последовательный, третья группа информационных входов которого соединена с второй группой выходов модификатора адреса и через второй шифратор с четвертой группой информационных входов преобразователя параллельного кода в последовательный, выход которого соединен с выходом формирователя, адресные входы которого соединены с управляющими входами преобразователя параллельного кода в последовательный, синхровход которого соединен с Синхровходами модификатора адреса и формирователя, первый, второй и третий разрядные входы задания режима работы формирователя соединены с счетным входом модификатора адреса, с входами сдвига и «Параллельная запись преобразователя параллельного кода в последовательный, третья группа выходов модификатора адреса соединена с 1 рупной выходов формирователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1425680A2 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1430957A2 |

| Устройство для тестового контроля цифровых блоков | 1984 |

|

SU1251084A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1539782A2 |

| Устройство для тестового контроля цифровых блоков | 1986 |

|

SU1345199A2 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1314344A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для контроля полупроводниковой памяти | 1985 |

|

SU1319079A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1545222A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для проверки блоков ЭВМ, содержаш.их ОЗУ большого объема. Цель изобретения - расширение области применения за счет обеспечения возможности контроля микропроцессорных элементов с большим объемом ОЗУ. Устройство содержит блок микропрограммного управления, блок обмена с контролируемым блоком, формирователь алгоритмических тестов. В устройстве реализован микропрограммный принцип управления. В тестовом наборе содержатся входные воздействия, эталонные реакции, коды маскирования каналов цифрового блока и коды управления коммутатором входов/выходов. 1 зп. ф-лы, 10 ил. сл со ьо ел

Шина сЗяза с ЭВМ

Фиг. :

Т

и /1 нантролируемог у 14ифроЗом(/ Злаку

Шина cSfi3ul с ЭВМ

От 12

ОтЗ От 4 Qm

ОтЗ

. ; М77Л;; с Л ;.UU(pooSo iu ;../

Ф1. J

От шины сйязи. с ЗВМ

К 21

От От 3

От 52,53,511

QmSHОт

Om

/с 7

От 63

От 56

к7

30

Составитель А. Сиротская

Редактор Н. ЕгороваТехред И. ВересКорректор А, Обручар

Заказ 1844/48Тираж 673Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений н открытий

1 13035, Москва, Ж---35, Раушская наб., д. 4/5 Производственно-полиграфическое предприятие, г. Уж1-ород, ул. Проектная, 4

| Устройство тестового контроля | 1982 |

|

SU1075265A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для тестового контроля цифровых блоков | 1984 |

|

SU1251084A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-05-23—Публикация

1985-12-23—Подача