Настоящее изобретение относится к системе временного запоминания информации, содержащей буферную память, регистрирующую структурированные данные в блоки данных фиксированной или переменной длины, имеющие каждый один или несколько элементов данных, множество файлов ожидания, служащих для связывания между собой блоков данных с целью выдачи их селективным образом на индивидуальные выходы, которые могут принадлежать к различным назначениям, и логику управления этими файлами ожидания.

Такая система запоминания с присоединенными к ней соответствующими входами, связанными с буферной памятью, образует устройство коммутации данных, в котором данные, принятые на входах, записываются в буферную память для последующей передачи на выходы в зависимости от индикаций выбора. Эти индикации выбора могут указывать выходное назначение; они могут сопровождать данные, принятые входами, или быть включены в эти данные и будут служить для направления их передачи к по меньшей мере одному выходу указанного выходного назначения. Это устройство коммутации найдет свое применение в коммуникационных сетях. Но система запоминания по изобретению как таковая может найти и другие применения, каждый раз, когда данные, структурированные в блоках данных одного или нескольких элементов данных, должны быть выданы в распоряжение многих выходов, принадлежащих различным назначениям. В экспертной системе, например, такая система запоминания может служить для регистрации обрабатываемых данных и передачи их многочисленным процессорам. Множество процессоров, выполняя параллельную специальную обработку, будут соответствовать одному выходному назначению.

В известной форме реализации, описанной в заявке на патент PCT/EP89/00942 от 9 августа 1989 г., система запоминания имеет очередь ожидания на выходе. Логика (называемая системой) управления очередями ожидания имеет функцию связать идентификатор каждого блока данных (называемого ячейкой), записанного в буферную память, когда он должен быть передан выходному назначению в очередь ожидания выбранного выхода, принадлежащего одному назначению, и это - для одного или нескольких указанных назначений. Выбор выхода среди выходов, которые принадлежат одному и тому же выходному направлению, производится, например, случайным образом.

Преимущество такого решения состоит в кажущейся простоте. Когда один выход становится необходимым, ему достаточно обслуживать свою собственную очередь ожидания на выходе, который выдает идентификатор блока данных, содержащегося в буферной памяти, и который предназначен для него.

С другой стороны, каждый выход должен быть готовым к передачам, которые затребует у него его очередь ожидания, т.е. которая ему была предписана в прошлом без учета ее нынешней ситуации, которая может быть неблагоприятной по отношению к пропускной способности (перегрузка, поломка, обслуживание и т. д.). Кроме того, запись в очередь ожидания не учитывает загрузки передачи информации, уже присвоенной выходу, и не учитывает также в этой загрузке передачи длин различных блоков данных, которые приписаны к нему. Отсюда следует, что такое решение неизбежно неравномерно загружает различные выходы, принадлежащего одному и тому же выходному назначению.

Для устранения этого недостатка различные известные решения состоят в добавлении для каждого выхода устройства измерения срока накопления в очереди ожидания этого выхода или, с другой стороны, количества накопленной и находящейся в ожидании информации для этого выхода, т.е. полное число элементов данных, соответствующих блокам данных переменной длины, находящихся в ожидании. Тогда уравновешивание пропускной способности на выходах выполняется цепью выбора выхода среди группы выходов, цепь измерения сроков которой, аккумулированная в очереди ожидания, указывает меньшее значение, чем значения других выходов этой группы.

Кроме того, часто бывает необходимо, чтобы выбор выхода в группе выхода вводил декорреляцию выходного движения (т.е., чтобы выбор был выполнен независимо от предыдущего потока движения на выходах). Взятое изолированно это требование остается простым для удовлетворения, например путем введения в действие источника случайных сигналов при выборе одного из выходов группы. Однако использование этого механизма становится более дорогим или менее быстрым в случае передачи ячейки от точки к многим точкам; действительно, в последнем случае идентификатор ячейки должен быть записан в несколько очередей ожидания, по одному на выбранный выход, для приема копии ячейки, предназначенной для одной из множества выбранных выходных групп определенного назначения. Тогда нужна либо случайная цепь выбора на группу выходов для параллельной работы и без добавочного срока, либо последовательная работа во времени для различных выбранных выходных групп, что увеличивает длительность исполнения.

Наконец, проблема становится много сложнее, когда два предыдущих требования (уравновешивание движения на различных выходах на группу и случайный выбор этих выходов для декорреляции выходного движения) должны быть удовлетворены одновременно. Действительно, основные алгоритмы, описанные ранее для этих двух требований, рассматриваемые изолированно, являются противоречивыми. Они не могут быть объединены логически просто для удовлетворения этих требований в момент действительной выходной передачи блоков данных на выбранные выходы (считывание очередей ожидания), тогда как эта операция вывода выполняется в момент записи идентификатора блока данных в одной (или нескольких) очереди(ях) ожидания на выходе. Использование решения, комбинирующего алгоритмы, требуемые для удовлетворения этих двух требований, включая случай передачи от точки ко многим точкам, выбирая один выход в каждой группе выходных адресатов, перед использованием в выходной очереди ожидания идентификатора блока данных, приводит к существенной сложности и повышенной стоимости.

Настоящее изобретение предлагает систему временного запоминания информации, имеющую в своем составе буферную память, записывающую структурированные данные в блоки данных фиксированной и переменной длины, каждый из которых имеет один или множество элементов данных, множество очередей ожидания, служащих для связывания между собой блоков данных с целью выдачи их выборочным образом на индивидуальные выходы, которые могут принадлежать различным адресатам, и логику управления этими очередями ожидания, как это определено ранее, которая не имеет указанных недостатков.

Вышеназванные задачи согласно изобретению решаются тем, что система имеет в своем составе логику управления очередями ожидания блоков данных и выбора выхода, содержащую очередь ожидания, предназначенную для каждого выходного назначения так, что поскольку блок данных приписан одному выходному назначению, достаточно связать его идентификатор с очередью ожидания этого выходного назначения, причем логика управления очередями ожидания блоков данных и выбор выхода, включающий средства выбора блока данных, вступают в действие тогда, когда индивидуальный выход должен быть назначен для блока данных, идентифицируя очередь ожидания выходного назначения, которому принадлежит этот выход, получая назначение блока данных и приписывая блок данных рассматриваемому выходу, инициируя передачу этого блока данных к этому индивидуальному выходу.

Таким образом, по изобретению, выравнивание продвижения блоков данных на выходах каждой группы выходов будет получено просто (без добавления цепей супервидения загрузки движения через выход) вследствие того, что каждая очередь ожидания, связанная с группой выходов одного выходного адресата считывается выходами, которые ее обслуживают по мере их соответствующего наличия во времени (следовательно, в функции их соответствующей мгновенной загрузки).

По другому варианту изобретения один и тот же выход может принадлежать многим выходным назначениям, причем указанные средства выбора блоков данных имеют средства выбора выходного назначения для идентификации выходных назначений, к которым принадлежит рассматриваемый выход, для идентификации их среди этих выходных назначений, имеющих, по меньшей мере, один блок данных для передачи, и для выбора выходного назначения среди последних выходных назначений, причем идентификация выбранного выходного назначения позволяет указанным средствам выбора блока данных установить идентификатор очереди ожидания этого выбранного выходного назначения.

По другому варианту изобретения указанные средства выбора выходного назначения разработаны для идентификации выходных назначений, имеющих, по меньшей мере, один блок данных для передачи, рассматривая эти выходные назначения в порядке, основанном на типах назначений, и для выбора выходного назначения среди этих последних выходных назначений на основе указанного порядка.

По другому варианту изобретения указанные средства выбора выходного назначения в целях идентификации выходных назначений, имеющих, по меньшей мере, один блок данных для передачи, имеют в своем составе один счетчик на выходное назначение, дающий число блоков передаваемых данных для этого выходного назначения, а также цепь детектора, определяющая, является ли это число нулем или отлично от него.

По другому варианту изобретения упомянутая логика управления очередями ожидания блоков данных и выбора выхода имеет в своем составе средства выбора, работающие в две последовательные фазы в течение интервалов времени повторяющегося цикла, причем первая фаза предусмотрена для приема с запрошенного индивидуального выхода указаний о том, должен ли принадлежать ему указанный блок данных, а вторая фаза предназначена для выдачи идентификатора выбранного выхода, для которого предназначен блок данных.

По другому варианту изобретения указанный идентификатор выбранного выхода, выданный во второй фазе, есть идентификатор указанного запрашивающего выхода первой, непосредственно предшествующей фазы.

Однако по предпочтительному варианту указанный идентификатор выбранного выхода выдается источником идентификации выбранного выхода так, чтобы идентификатор выбранного выхода был бы определен независимо от идентификатора указанного запрашивающего индивидуального выхода.

По другому варианту изобретения указанный источник является счетчиком, число полезных позиций которого равно числу временных интервалов и который проходит через все эти положения из расчета одно на интервал времени в указанном цикле.

По другому варианту изобретения счетчик указанного источника выполняет один или несколько дополнительных шагов (назад или вперед) с равномерными или неравномерными интервалами.

По другому варианту изобретения счетчик указанного источника выполняет один или несколько дополнительных шагов (вперед или назад) один раз в каждом цикле.

По другому варианту изобретения выполнение указанных дополнительных шагов затормаживает один цикл на N, причем N - ни кратно, ни подкратно числу временных интервалов цикла.

По другому варианту изобретения указанное число дополнительных шагов каждый раз выдается источником последовательных числовых значений случайного или псевдослучайного характера.

По другому варианту изобретения указанный счетчик устанавливается в точно определенное положение в начале каждого цикла.

По другому варианту изобретения точно определенное положение выдается на основе и с учетом источника последовательных численных значений случайного или псевдослучайного характера.

По другому варианту изобретения указанный источник численных значений является источником идентификатора выбранного выхода.

Различные объекты и признаки изобретения будут представлены более детально в ходе приведенного ниже описания примера реализации изобретения, данного в качестве неограничивающего примера со ссылками на чертежи, на которых показаны:

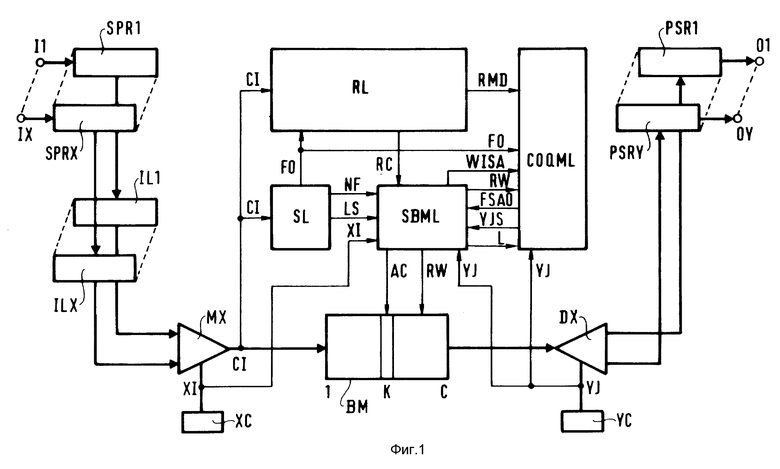

на фиг. 1 - известная диаграмма цепей примера элементарного коммутатора ISE, в котором применено настоящее изобретение;

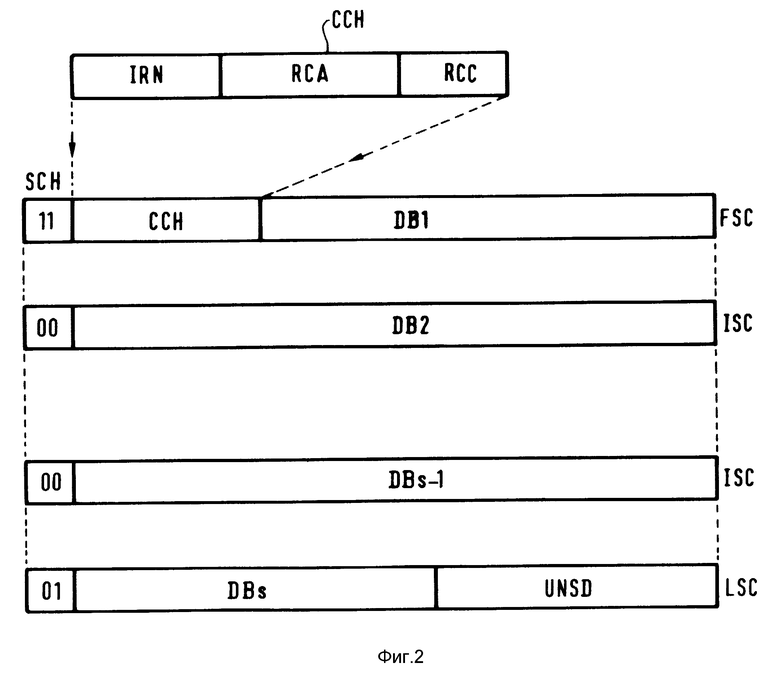

на фиг. 2 - формат блока данных, называемого ячейкой, скоммутированного элементарным коммутатором фиг. 1 в соответствии с настоящим изобретением;

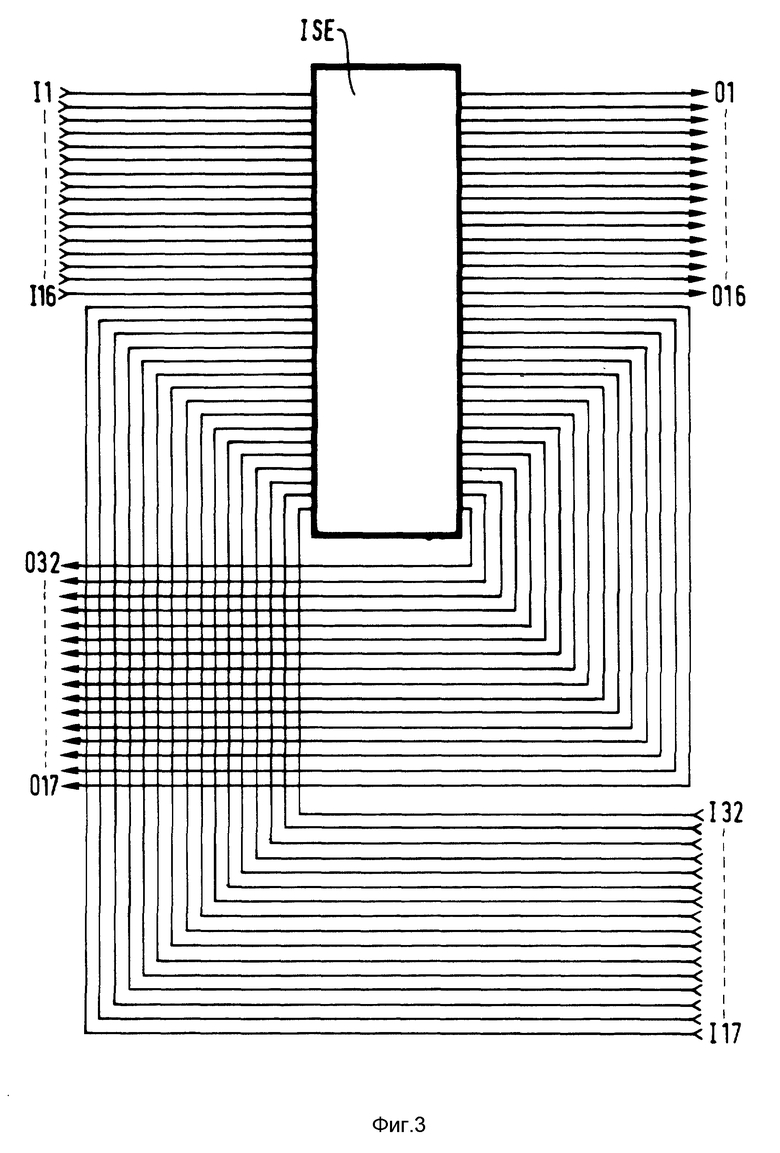

на фиг. 3 - диаграмма варианта применения коммутатора по фиг. 1 для отправки ячеек в двух противоположных направлениях;

на фиг. 4 - диаграмма цепи отправки RL по фиг. 1, обеспечивающая использование элементарного коммутатора по фиг. 1 в соответствии с диаграммой по фиг. 3;

на фиг. 5 - детальная диаграмма логики управления памяти подъячеек SBML фиг. 1;

на фиг. 6 - общая диаграмма варианта реализации логики управления очередями ожидания ячеек и выбором выхода COQML фиг. 1;

на фиг. 7 - детальная диаграмма цепей примера реализации блока очередей ожидания OQU логики управления очередями ожидания ячеек и выбором выхода COQML фиг. 6;

на фиг. 8 - детальная диаграмма варианта реализации логики управления очередями ожидания ячеек и выбора выхода COQML фиг. 6;

на фиг. 9 - диаграмма первого варианта реализации цепи выбора выхода OSC фиг. 8;

на фиг. 10 - диаграмма второго варианта реализации цепи выбора выхода OSC фиг. 8.

Описание, которое следует ниже, выполнено со ссылками на чертежи, относящиеся к случаю применения изобретения к коммутации блоков данных с помощью элементарного коммутатора, включенного в многоступенчатую сеть коммутации таких элементарных коммутаторов. Этот элементарный коммутатор описан в заявке на патент PCT/EP89/00942 от 9 августа 1989 г., и он включен в сеть коммутации, множество примеров которых описаны в заявке на европейский патент N 90401393.5; тот и другой не опубликованы. Описания, относящиеся к фиг. 1-5, которые необходимы для понимания настоящего изобретения, были активно использованы из этих предшествующих заявок на патент. Для облегчения настоящего текста они упрощались каждый раз, когда это было возможным.

На фиг. 1-5 также для упрощения различные связи показаны как простые провода, хотя в них может быть встроено множество таких проводов. Кроме того, не показаны все цепи управления, причем их реализация вытекает с очевидностью для специалиста из содержания описания.

Элементарный коммутатор, показанный на фиг. 1, имеет X входов I1/IX и Y выходов 01/0Y (X и Y не равны одновременно 1), Y - выходным назначениям. Одному и тому же выходному назначению принадлежат один или несколько выходов, образующих группу выходов. Один и тот же выход может принадлежать многим выходным назначениям. Это будет детализировано ниже.

Этот элементарный коммутатор разработан для коммутации цифровых данных, сгруппированных в блоки данных фиксированной или переменной длины. Такие блоки данных часто называют пакетами или ячейками в методах передачи и коммутации, используемых в коммуникации данных. В следующем ниже тексте, принимая язык коммуникаций с асинхронным временным мультиплексированием, будем применять слово ячейки для обозначения таких блоков данных. Пример ячейки, отправляемой элементарным коммутатором по фиг. 1, показан на фиг. 2. Эта ячейка образована непрерывным рядом последовательных подъячеек, имеющим первую подъячейку FSC, одну или несколько промежуточных подъячеек ISC и одну конечную подъячейку LSC (все равной длины, например 162 бита либо 2 бита и 20 символов по 8 бит). Каждая из этих подъячеек содержит одно поле управления подъячеек CH (по 2 бита) и блок данных DBI-DBS. Первая подъячейка FSC содержит, кроме того, этикетку ячейки CCH, которая в свою очередь содержит информацию отсылки, позволяющую элементарному коммутатору определить к какому(им) выходному(ым) адресу(ам) или выходной(ым) группе(ам) все подъячейки, принадлежащие к одной и той же ячейке, должны быть переданы последовательно и без прерывания, причем эта передача выполняется в каждой группе выходов на один и тот же выход. Поле управления подъячейкой SCH имеет явное двоичное значение 11, 00 или 01, указывая, что подъячейка является соответственно первой подъячейкой FSC, промежуточной подъячейкой ISC или последней подъячейкой LSC ячейки.

Этикетка CCH имеет в свою очередь три части: поле управления отправкой RCC, индикацию назначения в форме выходного адреса сети RCA и номер внутренней ссылки дерева распространения IRN.

Поле управления RCC, которое может иметь 5 бит, содержит данные варианта отправления, могущего означать вариант отправления от точки к точке или вариант отправления от точки ко многим точкам, или еще любой другой предусмотренный вариант отправки, некоторые из которых будут пояснены далее. Если для рассматриваемого элементарного коммутатора поле управления RCC означает вариант отправки от точки к точке, анализ выходного адреса сети RCA дает идентификатор группы выходов адресации. Если поле управления RCC указывает вариант отправки распространения, номер ссылки дерева распространения IRN служит для считывания памяти, которая выдает идентификаторы групп выхода, соответствующие включениям, которые необходимо выполнить для этого дерева в рассматриваемом элементарном коммутаторе.

Фиг. 3 представляет с этого момента для удобства редакции вариант использования элементарного коммутатора ISE по фиг. 1 в случае двунаправленной отправки с возможностью отражения.

Элементарный коммутатор ISE в примере по фиг. 3 имеет 32 входа I1-I32 и 32 выхода 01-032. Входы I1-I32 распределены на два множества входов I1-I16 и I17-I32. Выходы распределены на два выходных множества выходов 01-016 и 017-032. Внутренним образом, кроме случая отражения, элементарный коммутатор разработан для обеспечения нормальной отправки слева направо от входов I1-I16 к выходам 01-016, а также параллельно, но справа налево по варианту внешней разводки кабелей от входов I17-I32 к выходам 017-032. В случае отражения коммутатор позволяет обеспечить отправку входов I1-I16 к выходам 017-032, или входов I17-I32 к выходам 01-016. В таком коммутаторе связь входов с направлениями отправки заранее определена. Она может быть указана битом 10, соединенным с каждым входом и который указывает, принадлежит ли она к "входному" направлению (I1-I16, например, направляя нормальное движение, предназначенное множеству выходов 01-016) или к противоположному "выходному" направлению (I17-I32, по тому же примеру, направляя движение, нормально предназначенное множеству выходов 017-032).

Множество 16 выходов каждого направления может быть, например, распределено на 8 групп (максимально), по меньшей мере двух выходов, предназначенных для 8 выходных назначений, а отправка любой ячейки на выходы одной из групп может выполняться просто идентификацией в слове из 8 бит (один бит на группу) группы или групп, на которые ячейка должна быть передана, причем подразумевается, что ячейка передана на один выход каждой группы, идентифицированной таким образом. Одни и те же выходы могут, кроме того, принадлежать все одному и тому же выходному назначению, что позволит отправить ячейку на один из рассматриваемых выходов в группе. В противоположность этому 16 выходов могут еще принадлежать стольким же выходным назначениям для обеспечения отправки на индивидуальные выходы. Из этих примеров, которые не являются избыточными, понятно, что один и тот же выход может принадлежать многим выходным назначениям.

Кроме того, хотя этого и не видно на фиг. 3, элементарный коммутатор по фиг. 1 имеет один дополнительный вход и один дополнительный выход, соединенные (один и другой) с оборудованием тестирования и управления (не показано и не описано), которое может быть выполнено известным образом и которое выходит за рамки настоящего изобретения.

Вновь обращаясь к фиг. 1, видно, что входы I1/IX элементарного коммутатора соединены с соответствующими входами данных мультиплексора MX посредством каскадного соединения соответствующих последовательно-параллельных преобразователей SPR1/SPRX и соответствующих буферных регистров IL1/ILX. Выход данных CI мультиплексора MX соединен со входом данных, также CI, буферной памяти подъячейки BM типа ОЗУ, тогда как выбранный вход X1 мультиплексора MX устанавливается цепью часов входа XC, которая может соединить последовательно каждый из X-входов мультиплексора с выходом мультиплексора CI в течение периода подъячейки. Tакой период подъячейки есть интервал времени, в течение которого одна подъячейка принимается в последовательной форме в цепь последовательно-параллельного преобразователя SPR1-SPRX.

Выход данных буферной памяти BM соединен со входом данных демультиплексора DX, Y-выходы данных которого соединены с соответствующими выходами 01/0Y с помощью цепей параллельно-последовательных преобразователей PSR1/PSRY соответственно. Вход выбора YJ демультиплексора DX управляется цепью часов выхода YC, которая может соединить последовательно вход демультиплексора с Y-выходами демультиплексора в процессе периода подъячейки.

Буферная память BM разделяется между всеми входами и всеми выходами. Она подразделяется в C, 512, например, ячеек буферной памяти подъячейки, каждая из которых может зарегистрировать одну подъячейку; она имеет адресный вход AC, а также вход выбора считывание/запись RW соответственно, соединенные с выходами того же наименования логики управления буферной памятью подъячеек SBML.

Элементарный коммутатор имеет, кроме того, логику подъячейки SL и логику отправки RL, которые соединены с выходом данных CI мультиплексора MX.

Логика подъячейки SL есть принципиально цепь супервидения, предусмотренная для детектирования и проверки поля управления подъячейкой SCH каждой подъячейки (см. фиг. 2) и для выдачи активных выходных сигналов LS, FO или NF в зависимости от того, является ли эта подъячейка последней подъячейкой LSC, первой подъячейкой FSC или не является первой подъячейкой.

Логика отсылки RL выполняет анализ отправляемой информации этикетки CCH каждой первой подъячейки FSC ячейки и выдает активные сигналы отправки RMD и RC в функции отправляемой информации. Более конкретно, сигналы RMD выдают идентификацию одной или нескольких групп выбранных выходов, на один и тот же выход каждой из которых должны быть переданы подъячейки ячейки, тогда как сигнал RC указывает число этих выбранных групп выхода, т.е. 1 для передачи от точки к точке и одно значение, превышающее 1, для передачи от точки ко многим точкам.

Логика управления очередями ожидания ячеек и выбора выхода COQML выполняет одновременно управление очередями ожидания ячеек на выходе и функцию выбора выхода в группе выходов. Именно в этой логике ожидания COQML применяется настоящее изобретение.

В процессе приема первой подъячейки в буферной памяти BM логика управления буферной памятью SBML выдает логике управления очередями ожидания ячеек и выбором выхода COQML сигнал управления записью RW, сопровождаемый адресом WISA размещения памяти, в которую записывается эта первая подъячейка. Логика управления COQML выставляет этот адрес в одну или несколько соответствующих очередей ожидания, как это будет видно впоследствии, в зависимости от сигналов отправки выхода PMD, выдаваемых логикой RL с целью передачи ячейки на выход группы выходов или выхода каждой из многих групп выходов.

В процессе передачи первой подъячейки ячейки на выход именно логика управления очередями ожидания ячейки и выбора выхода COQML, который идентифицирует эту ячейку, передает адрес первой подъячейки выхода FSAO к логике SBML одновременно с идентификатором выбранного выхода YJS.

Логика управления буферной памятью подъячейки SBML соединена с упомянутыми ранее выходами LS, NF логики SL, RC логики RL, XI цепи часов входа XC, FSAO, и YJS логики управления очередями ожидания ячеек и выбором выхода COQML, и YJ цепи часов выхода YC. Она управляет использованием ячеек буферной памяти BM, выдавая адрес свободных ячеек, делая их занятыми, когда они используются и высвобождая их, когда они больше не используются. Под управлением сигналов, поданных на эти входы, она управляет также через сигнал выбора запись/считывание RW циклами операций считывания и записи в буферную память BM и работой логики управления COQML, образуя списки цепей, связывающих адрес буферной памяти подъячеек одной и той же ячейки. Это необходимо вследствие того, что подъячейки одной и той же ячейки записываются в некоррелированные ячейки буферной памяти BM, тогда как они должны быть отправлены на тот или те же выбранные выходы 01/0Y, и это в том же порядке и без прерывания, поскольку они были к своему приходу на входах I1/IX.

Ниже кратко описана работа элементарного коммутатора по фиг. 1.

Когда подъячейка ячейки постоянной или переменной длины такая, как та, которая представлена на фиг. 2, появляется на одном из входов I1/IX, например элементарного коммутатора, она принимается цепью последовательно-параллельного коммутатора SPRI. Выданная этой цепью преобразователя SPRI параллельная версия подъячейки передается на соответствующий буферный регистр ILI, через который она выдается мультиплексору MX. Под управлением сигнала часов XI, выдаваемого на вход того же наименования цепью часов входа XC, подъячейка в определенный момент соответствует этому входу I1, выдаваемому на вход данных CI буферной памяти BM, а также на логику подъячейки SL и на логику передачи RL. Выходные сигналы LS, NF и RC этих двух логик подаются на логику управления буферной памятью подъячейки SBML, а сигналы отправки выхода RMD на логику управления очередями ожидания ячеек и выбором выхода COQML.

Под управлением сигнала часов XI логика SBML выдает адрес WISA свободной ячейки буферной памяти на вход адреса AC буферной памяти BM, вследствие чего подъячейка, находящаяся на входе данных CI буферной памяти BM, записывается в ее ячейку, например K, имеющую адрес WISA. Этот адрес WISA оказывается занятым и добавляется в список цепи адресов всех уже принятых подъячеек той же ячейки. В этом списке адреса располагаются в том же порядке, что и подъячейки ячейки.

В процессе операции считывания подъячейки в памяти BM для ее передачи на один из выходов 01-0Y элементарного коммутатора под управлением сигнала часов YJ, выдаваемого на вход того же наименования цепью часов выхода YC, логика управления буферной памяти SBML выдает адрес этой подъячейки на адресный вход AC буферной памяти BM, а подъячейка, содержащаяся в соответствующем месте памяти, считывается и передается на выход данных буферной памяти BM. Оттуда она выдается с помощью демультиплексора DX на выход, указанный сигналом YJ.

Логика управления очередями ожидания ячеек и выбора выхода COQML информируется о приеме этих ячеек, зарегистрированных в буферной памяти BM, а также их назначении; она также информируется о передаче последней подъячейки некоторой ячейки на выход, идентифицирует другую ячейку, зарегистрированную в буферной памяти BM, которая должна быть передана затем на рассматриваемый выход.

Среди различных логик, образующих элементарный коммутатор по фиг. 1, логика подъячейки SL есть всего лишь простая цепь декодирования. Ее реализация является доступной для специалиста и нет необходимости давать ее подробное описание.

Теперь перейдем к описанию со ссылками на фиг. 4 варианта реализации цепи отправки RL фиг. 1, обеспечивающего двунаправленную работу в соответствии с тем, что показано на фиг. 3.

Цепи по фиг. 4 принимают в регистр IR этикетку ячейки CCH, показанную на фиг. 1, для выдачи на выход информации, отмечающей связь управления RMD, которая выдается на логику управления очередей ожидания ячеек, и выбирает с выхода COQML информацию, характеризующую выбранный вариант отправки (ES, MC, DI, RS, PH), а также отправляемые данные (RG, PO).

Информация варианта отправки связи RMD следующая:

- сигнал варианта "группа" RS, который имеется, когда ячейка должна быть повторно передана на один из выходов группы выходов в случае отправки от точки к точке;

- сигнал варианта "распространение" MC, который имеет место, когда ячейка должна быть передана на один из выходов каждой из многих групп выходов в случае отправки от точки ко многим точкам;

- сигнал варианта "распределение" DI, который имеет место, когда ячейка должна быть повторно передана на один из выходов множества выходов в смысле, выявленном со ссылкой на фиг. 3, в случае двунаправленного элементарного коммутатора или на один из всех выходов элементарного коммутатора в случае однонаправленного элементарного коммутатора, выполняя вследствие этого общее распределение;

- сигнал режима "служебный" ES, который указывает на то, что принятая ячейка предназначена специальному выходу управления;

- сигнал режима "направленная передача" PH, который указывает, что ячейка должна быть вновь передана на заранее определенный выход для тестирования, например.

Данные отправки связи RMD имеют:

- сигналы идентификации группы PG, которые идентифицируют группу или группы, на выходе которой или которых должна быть передана принятая ячейка для режимов отправки RS и MC;

- сигнал выходного направления IOD, который идентифицирует одно из двух множеств выходов в случае двунаправленного элементарного коммутатора;

- сигналы идентификации индивидуального выхода PO, используемые с режимом отправки PH.

Цепи на фиг. 4 принимают, кроме того, в зависимости от входа, на который поступает принятая ячейка, указатель входящего направления 10, который выдается, например, приемной цепью, выдающей ячейку, с которой идет речь, на входной мультиплексор по фиг. 1, специфицируя соответствующее входное направление в смысле, упомянутом со ссылкой на фиг. 3.

Цепи по фиг. 4 имеют следующие элементы:

- уже упомянутый регистр IR для приема этикетки CCH каждой принятой ячейки, которая включает, как указывалось, информацию RCC, RCA и IRN;

- память перевода команд RCCTM; регистрирующую 32 слова по 16 бит, называемые параметрами отправки, включающие каждый код режима отправки MT из трех бит, указатель или бит отражения EF, поле "входной" группы отправки RPI из 6 бит и поле "выходной" группы отправки RPO также из 6 бит;

- память распространения MCM, записывающую множество слов маски MSK из 8 бит, по биту на выходную группу, идентифицирующему каждый различные группы отправки, к которым должна быть выпущена копия;

- декодер режима отправки TD, декодирующий код режима отправки MT и выдающий впоследствии один из пяти сигналов режима отправки, упомянутых ранее;

- селектор направления RD, выбирающий либо поле "входящей" группы отправки RPI, либо поле "выходящей" группы отправки RPO памяти перевода команды RCCTM, в функции бита отражения EF и индикатора входного направления IO;

- селектор группы выходов MS, имеющий два параллельных входа по 8 бит и выдающий сигналы идентификации группы PG, каждый также по 8 бит, каждый из которых соответствует одной группе из 8 возможных групп отправки;

- регистр со смещением на 14 бит SR, имеющий выход PO по 5 проводников; в случае, когда режим отправки является "физическим" PH, этот выход идентифицирует выход, на который должна быть отправлена принятая ячейка;

- декодер группы отправки GD;

- порт ИСКЛЮЧАЮЩЕЕ ИЛИ XOR;

- и два порта И, AN1 и AN2.

Логические цепи отправки по фиг. 4 работают, как это будет указано, когда заголовок принятой ячейки присутствует на входном мультиплексоре (фиг. 1), этикетка которой CCH выдается на регистр IR, тогда как бит 10 указывает входное направление отправки. Как это было указано выше, часы тактируют соответствующим образом работу цепей в соответствии с текущей практикой в данной области.

Информация управления RCC, характерная для последовательности передачи через любую сеть коммутации, не указывает непосредственно на применяемый режим отправки в рассматриваемом элементарном коммутаторе. Этот режим отправки является функцией типа сети коммутации и положения элементарного коммутатора в ней.

Информация управления должна быть интерпретирована, а для этого она используется как адрес для считывания в памяти перевода команд RCCTM параметров отправки, которые там были записаны ранее классическими средствами управления, такими как аппаратура тестирования и управления, упомянутая ранее; эти параметры отправки имеют элементы MT, EF, RPI и RPO, определенные выше.

Код применяемого режима отправки MT расшифровывается декодером режима отправки TD, который выдает один из сигналов режима R, MC, ES, DI или PH.

Указатель входного направления IO подается на один из входов порта ИСКЛЮЧАЮЩЕЕ ИЛИ XOR, тогда как бит отражения EF подается на другой вход. Выход порта XOR выдает сигнал управления IOD селектором выходного направления RD. Последний выбирает либо поле "входной" группы отправки RPI, либо поле "выходной" группы отправки RPO, специфицируя для одного и другого выходных множеств характерную часть адреса назначения RCA, предназначенную для выдачи идентификатора группы отправки, на выход которого должна быть передана принятая ячейка. Каждое из этих полей имеет указатель положения ROS на 4 бита и индикатор размера RGS на 2 бита. Указатель положения POS управляет регистром смещения SR так, чтобы информация RCA была там смещена и чтобы часть из трех бит, которую она содержит, подходила в три каскада слева на фиг. 4 из регистра SR, или еще чтобы часть из пяти бит, которые она содержит, подходила в пять каскадов слева на фиг. 4 от регистра SR. Указатель размера RGS указывает, сколько из трех бит, упомянутых в первом, должны быть использованы для определения идентификатора группы отправки. Таким образом, бит слева из этих трех бит передается непосредственно из регистра смещения SR на декодер номера группы GD, следующий бит передается портом И AN1, обусловленным одним из сигналов RGS, а третий бит - портом и AN2, обусловленным другими сигналами RGS. Декодер номера группы GD выдает слово в 8 бит, которое образует идентификатор группы отправки, выдаваемый селектору MS. В этом слове один бит является 1, например, а все другие равны 0.

Одновременно номер внутренней ссылки дерева распределения на 14 бит IRN подается через регистр IR к номеру распределения MCM, где он служит адресом для считывания слова маски в 8 бит MSK. Как указывалось ранее, это слово маски идентифицирует одну или несколько групп отправки в слове из 8 бит, из которых один или несколько равны 1, а другие - 0. Оно отсылается также на селектор MS.

Если сигнал режима отправки, выданный декодером TD является сигналом режима "группа" RS, то селектор MS выдает на своем выходе сигнал идентификатора группы RG, который является сигналом, выдаваемым декодером GD; если речь идет о сигнале режима "распространение" MC, то сигнал RG, переданный селектором MS, есть сигнал MSK.

Кроме того, пять ступеней слева регистра смещения SR после смещения, обусловленного указателем положения POS, выдают непосредственно идентификатор PO выхода, на который должна быть передана принятая ячейка в случае "физического" режима отправки PH.

В специальном случае режима "распределение" DI никакая группа выходов не имеет необходимости быть идентифицированной, поскольку речь идет об одной лишь группе, имеющей все выходы рассматриваемого множества в соответствующем направлении передачи. В случае "служебного" режима ES соответствующий выход непосредственно известен, поскольку принятая ячейка предназначена для упомянутого выше дополнительного выхода управления.

Таким образом, видно, что информация, содержащаяся в памяти перевода команд RCCTM, определяет в элементарном коммутаторе интерпретацию того, что этот коммутатор должен сделать 32 возможных последовательности передачи, обозначающих информацию управления RCC для определения применяемого режима отправки в соответствии с данными отправки, содержащимися в этикетке принятой ячейки. Это приводит к объединению информации отправки ячейки, не меняющейся тогда, когда ячейка проходит коммутаторы различных каскадов сети коммутации с параметрами отправки рассматриваемого элементарного коммутатора, вытекающими из его положения в сети, например, принадлежащими каждому каскаду и приводящими к специальному режиму отправки в каждом каскаде и для каждой последовательности отправки.

Информация, содержащаяся в памяти перевода управления RCCMT, является полупостоянной и может быть записана при включении каждого элементарного коммутатора. С другой стороны, информация, содержащаяся в памяти распространения MCM, должна быть модифицирована в процессе эксплуатации для установления каждого дерева распространения.

Далее дается описание со ссылками на фиг. 5 варианта реализации логики управления буферной памяти подъячейки SBML фиг. 1.

Как уже упоминалось, эта логика управления буферной памяти подъячейки имеет входы LS, NF, RC, XI, YJ, FSAO, YJS и выходы AC, L, RW и WISA. Она имеет цепь управления свободными ячейками памяти FMLMC, память образования цепочек подъячеек SLM, память указателей входных подъячеек ISPM и память указателей выходных подъячеек OSPM.

Цепь FMLMC логики SBML образована памятью очереди ожидания свободных ячеек FQ, которая является, например, памятью очереди ожидания типа FIFO (первый вход-первый выход), регистрируя адреса всех свободных ячеек буферной памяти BM. Цепь FMLMC имеет вход ROSA, выход WISA и выводы управления QC и RW.

Память образования цепей подъячеек SLM имеет C ячеек памяти, соответствуя C ячейкам BM, и записывает для каждой из них:

- адрес сцепления подъячеек со следующей подъячейкой (NCB);

- число копий подъячейки, которые должны быть считаны (NC);

- индикатор последней подъячейки ячейки (L).

Поле памяти SLM связано с обратным счетчиком DC так, чтобы значение NC было декрементировано на единицу с каждой операцией считывания памяти SLM; затем новое значение регистрируется на месте предыдущего. Очевидно, что когда новое значение достигнет нуля, все копии подъячеек будут считаны, и счетчик DC выдаст сигнал QC, обеспечивающий регистрацию адреса считанной подъячейки (ROSA), которая станет свободной, в цепи управления ячейками свободной буферной памяти FMLMC.

Память указателей входных подъячеек ISPM имеет X ячеек, соответствующих X входам, и она работает синхронно с сигналами часов входа XI, определяя эксплуатацию с временным мультиплексированием X входов. Для каждого входа она записывает:

- адрес в буферной памяти последней принятой подъячейки (LCB);

- число копий подъячеек, которое нужно будет считать позднее (LC);

- индикатор последней подъячейки ячейки (B).

Память указателей выходных подъячеек OSPM имеет Y ячеек, соответствующих Y выходам, и она работает синхронно с сигналами часов выхода YJ, определяя эксплуатацию с временным мультиплексированием Y выходов. Для каждого выхода она записывает адрес ячейки следующей подъячейки, ожидающей передачи ее на рассматриваемый выход (WCB).

Цепь управления запись-считывание RWC выдает различным цепям соответствующие сигналы управления, определяя поочередную работу цепей логики управления буферной памяти SBML, связанную с чередующимися операциями считывания и записи в буферную память BM как результат сигналов часов, переплетенных относительно входов (XI) и выходов (YJ). В соответствии с этим сигнал RW, выданный цепью управления RWC, является активным в течение каждой операции записи в буферную память BM для входа подъячейки и неактивным в течение операции считывания из буферной памяти BM для передачи на выход подъячейки.

Описание следующего принципа охватывает работу, выполняемую логикой управления буферной памяти SBML в процессе чередующихся фаз записи и считывания для каждого из трех типов подъячейки ячейки: первая подъячейка FSC, промежуточная подъячейка ISC и последняя подъячейка ISC.

Сперва будет рассмотрена фаза записи в буферную память BM в случае первой подъячейки FSC, принятой на вход XI. В этом случае выдается сигнал FO и логика управления SBML принимает из логики SL и RL:

- NF = 0, для указания первой подъячейки;

- LS = 0, для указания того, что речь не идет о последней подъячейке;

- RC = 2, полагая, например, случай передачи от точки к многим точкам на две группы выходов.

Поскольку сигнал RW является активным, адрес записи подъячейки WISA выдается цепью управления, которая указывает свободную ячейку буферной памяти, в которую записывается принятая подъячейка. С этой целью адрес WISA передается на связь AC к памяти BM (см. фиг. 1) мультиплексором адресом AM, ориентированным сигналом RW. Адрес WISA также записывается в память указателей ISPM для входа XI с целью записи как адреса последней принятой подъячейки с учетом следующего цикла, относящегося к тому же входу. Кроме того, адрес WISA также выдается на логику COQML, которая будет его записывать как идентификатор отсчета новой принятой ячейки вследствие того, что эта логика принимает сигнал FO со значением 1. Само собой разумеется, что идентификатор отсчета принятых ячеек может быть не адресом первой подъячейки ячейки в буферной памяти, число бит которого зависит от числа ячеек буферной памяти BM, а более коротким отсчетным идентификатором, выдаваемым для каждой принятой ячейки цепью управления идентификаторами отсчета, подобной цепи управления свободными ячейками буферной памяти FMLVC.

Что касается цепного запоминающего устройства SLM, вследствие того, что речь идет о первой подъячейке FSC (NF = 0), адрес WISA не записан в поле NCB, поскольку эта новая подъячейка не должна быть сцеплена с последней подъячейкой предыдущей ячейки. Но другие поля данных должны быть и нормально эксплуатироваться в том, что касается этой предыдущей подъячейки, что обеспечивает выбор ее адреса, который выдается полем LCB памяти указателей ISPM, и регистрацию значений LC и B, поступающих из памяти указателей ISPM в полях NC и L памяти SLM соответственно, причем мультиплексор MLM ориентирован вследствие этого сигналом RW. Сигналы управления RC и SL оказываются зарегистрированными, кроме того, в полях LC и B соответственно памяти ISPM для входа XI.

В случае одной промежуточной подъячейки ISC сигнал FO является неактивным, а логика управления буферной памяти подъячеек SBML принимает от логических устройств SL и RL сигналы:

- NF = 1,

- LS = 0,

- сигнал RC не используется с NF = 1.

Как и ранее, сигнал RW является активным, и другой адрес WISA выдается цепью управления FMLMC, адресует ячейку буферной памяти, которая используется для:

- адресации буферной памяти BM и записи туда промежуточной подъячейки ISC,

- регистрации в поле LCB памяти указателей ISPM как нового адреса последней принятой подъячейки ячейки,

- регистрации в поле NCB памяти SLM, которая адресуется содержимым поля LCB памяти ISPM с целью записи туда этого нового адреса WISA как адреса следующей подъячейки, сцепленной с предыдущей, которой присваивается ячейка памяти, выбранная содержимым поля LCB в памяти SLM.

Одновременно данные полей LC и B памяти ISPM передаются в поля NC и L памяти SLM перед тем, как B будет заменено в памяти IPM новым значением, поступающим от сигнала LS (содержимое поля LC остается неизменным, поскольку число копий подъячеек для считывания остается таким же для всех других подъячеек, как и то, которое было установлено для первой подъячейки ячейки).

В случае последней подъячейки LSC сигнал FO является неактивным и логика управления SBML принимает с логических устройств SL и RL:

- NF = 1,

- LS = 1,

- тогда как RC не используется, поскольку NF = 1.

Вновь сигнал RW является активным, и другой адрес WISA выдается цепью FMLMC, а соответствующий адрес ячейки буферной памяти используется в буферной памяти BM и запоминающих устройствах ISAM и SLM точно так же, как в предыдущем случае записи промежуточной подъячейки ISC.

Одновременно значения LC и B памяти ISPM передаются в поля NC и L памяти SLM перед тем, как B будет заменено в памяти ISPM новым значением, поступающим от сигнала LS, указывая в результате, что теперь последняя подъячейка ячейки только что была принята.

Напомним, что точно так же, как это было упомянуто в описании, относящемся к регистрации первой подъячейки FSC, в процессе следующего цикла, относящегося ко входу XI, значения LC и B = 1 будут переданы в поля NC и L памяти SLM адресу рассматриваемой подъячейки (последней), выданному полем LCB памяти ISPM.

Теперь перейдем к обсуждению фазы считывания из буферной памяти BM для передачи подъячейки на выходы O1-OY; фазы, в течение которой сигнал RW является неактивным. Сперва рассмотрим случай считывания первой подъячейки FSC для учета выхода, обозначенного как YJ.

Нужно предположить, что в момент выдачи первой подъячейки содержимое WCB памяти указателей выходящих подъячеек OSPM рассматриваемого выхода YJ было инициализировано и содержит адрес первой подъячейки передаваемой ячейки. Это будет видно далее в процессе считывания последней подъячейки ячейки.

Память указателей OSPM, адресованная идентификатором выхода YJ, выдает вследствие этого адрес, обозначенный как ROSA, выходной подъячейки для считывания, который используется для:

- адресации буферной памяти BM для считывания соответствующей первой подъячейки FSC, причем мультиплексор AM ориентирован на сигнал ROSA неактивным сигналом RW и выдает в результате сигнал ROSA на связь AC,

- выбора памяти SLM в считывании, что дает:

- индикацию NCB, которая передается памяти OSPM для регистрации как новый адрес WBC с учетом следующего цикла, относящегося к выходу YJ, причем мультиплексор SO ориентирован в результате под воздействием сигнала I, поскольку речь не идет о последней подъячейке,

- индикацию NC, которая декрементирована на единицу и переписана как новая индикация NC, если она не равна нулю;

если получено значение нуль, что означает то, что было выполнено требуемое число операций считывания этой подъячейки (выдающее требуемое число копий ее), цепь DC вырабатывает сигнал QC, обеспечивающий цепи FMLMC возможность регистрации того, что ячейка буферной памяти адреса ROSA может быть освобождена и включена в множество свободных ячеек буферной памяти;

- значение I, которое равно нулю, поскольку речь не идет о последней подъячейке ячейки, и которое управляет упомянутым ранее переносом значения NCB памяти SLM в поле WCB памяти OSPM через мультиплексор SO.

В случае промежуточной подъячейки в запоминающих устройствах OSPM и SLM и в цепи FMLMC имеют место те же операции, что и для считывания первой подъячейки FSC.

В случае последней подъячейки LSC память OSPM вновь выдает адрес ROSA выдаваемой подъячейки, который используется для:

- адресации буферной памяти BM для считывания последней подъячейки,

- выбора памяти SLM при считывании, что дает:

- значение NC, которое декрементируется и обрабатывается точно так, как в других случаях считывания подъячейки,

- значение L, равное теперь 1, указывает на присутствие последней подъячейки LSC, что в этом специальном случае запрещает передачу значения NCB памяти SLM ячейке WCB памяти OSPM, поскольку отсутствует следующая подъячейка для рассматриваемой ячейки; вместо этого L = 1 выдается логике COQML для указания на то, что рассматриваемый выход YJ становится доступным для отправки к нему следующей ячейки следующего цикла, причем последняя подъячейка ячейки находится в процессе отсылки.

Затем после выбора логикой COQML соответствующей ячейки, которая должна быть передана на рассматриваемый выход YJ, логика COQML инициализирует значение WBC в памяти OSPM для (что касается выхода YJ) записи там адреса ячейки буферной памяти первой подъячейки FSAO вновь выбранной ячейки перед следующим циклом, относящимся к выходу YJ. Вследствие того что процесс инициализации не обязательно выполняется на протяжении периода часов YJ последней подъячейки LSC, используется асинхронный доступ к памяти OSPM с помощью адреса выхода YJS, выдаваемого логикой COQML.

Тогда как этот пример реализации логики управления буферной памяти подъячеек BMI был описан для иллюстрации принципов управления применяемой буферной памяти подъячеек для передачи ячеек, составленных из подъячеек между любым входом и любым выходом (или выходами) элементарного коммутатора, другие варианты реализации функций этой логики управления SBML, например в том, что касается цепи управления свободными ячейками буферной памяти FMLMC, также включены в типы элементарных коммутаторов, к которым применимо настоящее изобретение.

Теперь следует вернуться к фиг. 1 для рассмотрения логики управления очередями ожидания ячеек и выбора выхода COQML. Из предшествующих описаний видно, что логика управления COQML выполняет следующие функции:

a) прием (на приеме любой первой подъячейки ячейки, указанной активным сигналом FO) идентификатора ссылки, который является (в описанном примере) адресом WISA регистрации этой первой подъячейки, сопровождаемой сигналами отправки RMD, которые указывают по меньшей мере одну группу выходов, на один из которых должна быть передана ячейка;

b) выдача (когда передача ячейки на какой-либо выход YJ закончилась, что сообщается ему сигналом L) ссылочного идентификатора FSAO новой ячейки для передачи на этот выход, который является (как это упомянуто в a) адресом записи первой подъячейки этой ячейки в буферную память BM; кроме того, логика управления COQML, которая обозначила идентификатор рассматриваемого выхода, обозначенного как YJ, выдает назад этот же идентификатор, обозначенный YJS, так, чтобы его отклик мог быть отличным от синхронной обработки выхода YJ.

Другими словами, запись в буферную память каждого из блока данных, которые являются ячейками, отправляемыми элементарным коммутатором по фиг. 1, предназначена (вместе с их выходными адресами) логике управления очередями ожидания ячеек и выбора выхода COQML; этот последний берет эту метку и на основе этой информации отвечает запросам индивидуальных выходов, обслуживающих выходные направления, выдавая каждому из них идентификатор блока данных, который может быть передан на этот индивидуальный выход.

Как это представлено в преамбуле настоящей заявки, это позволяет присвоить блоки данных, предназначенные для одной или многих имеющихся в наличии определенных выходных адресаций, каждый раз одному из многих выходов, принадлежащих каждому из этих определенных выходных адресов.

Логика управления очередями ожидания ячеек и выбора выхода COQML могла бы по известным решениям присвоить сразу каждый блок данных одному из выходов каждого выходного назначения, к которым они принадлежат, причем одна очередь ожидания предусмотрена на каждый выход.

Изобретение предписывает другое решение, более совершенное, пример реализации которого будут теперь дан со ссылками на фиг. 6-9.

Фиг. 6 представляет логику управления очередями ожидания ячеек и выбором выхода COQML в его наиболее общих линиях. Видно, что эта логика управления включает логику управления записью в очереди ожидания QWCL, логику управления выбором выхода и считыванием в очередях ожидания OSQRCL и блок очередей ожидания выхода OQU. Работа комплекса логики управления очередями ожидания ячеек и выбором выхода COQML управляется модулем часов QCM, управляемым сигналом RW (фиг. 1). Модуль QCM в ответ на сигнал RW выдает на логику управления очередей ожидания и выбора выхода COQML различные сигналы часов, среди которых сигнал WR, которые управляют поочередным исполнением фаз записи и считывания в очередях ожидания в зависимости от описаний, которые последуют далее, применяя хорошо известные специалистам методы.

Логика управления записью QWCL работает в ответ на активный сигнал WR и на инструкцию сигнала управления FO, который, напомним, характеризует прием первой подъячейки ячейки, что влечет за собой необходимость записи идентификатора ссылки этой ячейки в очередь ожидания, установленную для обеспечения ее передачи на один или несколько выходов элемента коммутации на фиг. 1. Этот идентификатор ссылки является адресом WISA регистрации этой первой подъячейки в буферную память элементарного коммутатора. Он сопровождается сигналами отправки RMD. Действительно, роль логики управления записью QWCL состоит просто в переводе этих сигналов отправки RMD, которые выдаются цепью отправки RL на группу x проводников и определяют назначение или назначения ячейки (в терминах групп выхода), которая должна быть передана на выход каждой группы выходов, обозначенных таким образом. В зависимости от выбранного режима отправки идентификатор ячейки должен быть вставлен в одну или в несколько очередей ожидания на выходе, по одному на адрес, причем случай, где речь идет о многих очередях ожидания выхода, соответствующий режиму "распространение" MC, в котором ячейка должна быть отправлена на один из выходов нескольких групп выходов (8 или максимально 16, в рассматриваемом примере в зависимости от того, каким является коммутатор - однонаправленным или двунаправленным, как это было пояснено ранее). Для возможности выполнения постановки в очередь ожидания одной ячейки одновременно в столько очередей ожидания этот перевод выдает один или несколько сигналов на 16 проводников WE1-WE16, которые управляют параллельной записью в соответствующие блоки памяти выхода RGM1-RGM16 блока очередей ожидания OQU, как это будет пояснено далее. В рассматриваемом примере реализации очереди ожидания образованы цепными списками в выходной памяти, каждая строка которой, адресованная идентификатором ячейки, содержит идентификатор следующей в очереди ожидания ячейки; одна и та же выходная память может содержать множество цепных списков (множество очередей ожидания), поскольку они являются исключительными, т.е. поскольку каждый идентификатор ячейки принадлежат лишь одной очереди ожидания этой выходной памяти. Таким образом, как это будет пояснено далее, 35 других следующих очередей ожидания находятся также в первом блоке выходной памяти RGM1, в рассматриваемом примере:

- 32 очереди ожидания "направленного переноса" к индивидуальному выходу,

- 1 "служебная" очередь ожидания к 33-му выходу для тестирования и управления,

- 2 очереди ожидания "распределения", по одной на комплекс выходов на выходное направление (лишь одна из них используется в случае однонаправленного коммутатора).

Для указания специальной очереди ожидания в блоке выходной памяти RGMI ее идентификатор кодируется на 6 добавочных проводниках QW1-QW6.

Вообще говоря, будет показано, что по изобретению, каждая из этих очередей ожидания соответствует одному выходному назначению.

Короче говоря, логика записи QWCL заботится о выходах ячеек в выходных очередях ожидания блока очередей ожидания OQU. Она выполняет простой перевод и может принять классическую форму перекодировщика с памятью; поэтому мы не будем описывать ее детально.

Логика выбора выхода и считывания очереди ожидания OSQRCL, работающая когда сигнал WR является неактивным, принимает идентификатор выхода YJ, закодированный на 6 проводниках, который сообщает (сигнал L), что он будет передавать последнюю подъячейку ячейки и требует, чтобы она принадлежала следующей ячейке. Этот выход принадлежит к одной или нескольким группам выходов, и выходы каждой группы обслуживают коллективно выходное назначение.

В первой форме реализации логика OSQRCL действует немедленно и синхронно исполняет выбор очереди ожидания для выхода YJ. С этой целью она идентифицирует выходные назначения, частью которых является рассматриваемый выход, отыскиваемый среди выходных назначений этого выхода, тех, очереди ожидания которых не являются пустыми, выбирая из них одну и выдавая ее идентификатор, маркируя проводники RE1-RE16 и QR1-QR6, которые аналогичны, для считывания, и проводники WE1-WE16 и QW1-QW6 - для записи. С учетом неактивного сигнала WR блок выходных очередей ожидания OQU считывает указанную очередь ожидания и выдает определяемый идентификатор ячейки FSAO, который служит, как и ранее, для идентификатора ссылки WISA, например, адресом записи первой подъячейки ячейки в буферной памяти элементарного коммутатора. Эти два адреса представлены в числе nfc проводников, соответствуя числу бит рассматриваемых адресов записи. Кроме того, логика OSQRCL выдает также сигнал NCO, указывая присутствие идентификатора ссылки ячейки для передачи FSAO, а также обсуждаемого идентификатора YJS выхода. Как указывалось, идентификаторы выхода (32 коммуникационных выхода плюс один служебный выход в рассматриваемом примере) кодируются на 6 проводниках. Снабжение идентификатора выхода YJS могло бы быть устранено в этом первом примере, поскольку он идентичен идентификатору YJ. Его упоминание было сделано лишь для полноты.

Следует отметить, что при описании функции двух логик QWCL и OSQRCL были определены также в общих терминах функции блока очередей ожидания OQU. Более детально они будут описаны немного далее со ссылками на фиг. 7.

Во второй общей форме реализации выбор очереди ожидания для выхода YJ отличается, т.е. является асинхронным по отношению к интервалу времени часов выхода, принадлежащего выходу YJ. Логика OSQRCL после приема заявки передаваемой ячейки выхода YJ не действует немедленно к своей выгоде. Заявка лишь регистрируется. Позднее, после того как другие подобные заявки будут приняты другими выходами, логика OSQRCL выполняет выбор среди зарегистрированных заявок в условиях, которые будут пояснены далее в описании, относящемся к фиг. 10. Этот выбор указывает один выход, как в первой рассматриваемой форме реализации; логика OSQRCL идентифицирует выходные назначения, частью которых является рассматриваемый выход, отыскиваемый среди выходных назначений этого выхода, тех, очереди ожидания которых не являются пустыми, выбирая из них одну и выдавая ее идентификатор блоку очередей ожидания OQU, который считывает указанную очередь ожидания и выдает идентификатор определяемой ячейки. Кроме того, логика OSQRCL выдает также сигнал NCO, указывая присутствие идентификатора ссылки ячейки для передачи FSAO, а также идентификатор YJS обсуждаемого выхода, закодированный на 6 проводниках. Тогда необходима поставка идентификатора выхода YJS для указания SBML, на выход которой должна быть передана указанная ячейка, поскольку ее нет больше в синхронном интервале времени, предназначенном для передачи к этому выходу.

Значение этой второй формы реализации, в более общем виде состоящий в том, чтобы не обслуживать очереди ожидания выхода по мере готовности каждого выхода, состоит в том, чтобы предотвратить то, чтобы очереди ожидания обслуживались бы выходами в порядке, согласованном непосредственно с движением ячеек, полученным ранее. Для этого будет введена, например, декорреляция на поток движения в каждой группе выходов, выполняя случайный или псевдослучайный выбор порядка, в котором различные выходы, формулирующие заявку ячейки, будут обслуживать очереди ожидания на выходе в течение интервала времени, соответствующего циклу временного мультиплексирования обработки комплекса выходов элементарного коммутатора.

Прежде чем дать детальное описание логики выбора выхода и считывания очередей ожидания OSQPCL, нужно вернуться сначала к фиг. 7, представляющему форму реализации блока очередей ожидания OQU.

Этот блок очередей ожидания состоит из блоков выходной памяти RGM1-RGM16. Блоки выходной памяти RGM2-RGM16 идентичны друг другу, и лишь один блок RGM2 показан детально; он содержит очередь ожидания на выходе в выходной памяти M2 для блока выходной памяти RGM2. Блок выходной памяти RGM1 является отличным от него. Он содержит 36 очередей ожидания на выходе в той же выходной памяти M1.

Эти цифры возвращают к примеру элементарного коммутатора по фиг. 3 и к описанию, которое относится к нему. В этом примере элементарный коммутатор имеет 32 выхода в двух комплексах по 16 выходов, и эти выходы могут быть сгруппированы в 16 (2 раза по 8) групп выходов по одному или несколько выходов, каждый из которых соответствует одному выходному назначению. Поскольку в рамках коммуникаций от точки ко многим точкам входная ячейка может быть скопирована на нескольких выходных назначениях, поскольку, кроме того, ячейка обозначена одним ссылочным идентификатором и поскольку, наконец, желательно по причинам рабочего времени способа использование в очереди ожидания различных возможных копий ячеек, соединенных параллельно, отсюда следует, что необходимо предусмотреть автономную память для каждой из этих очередей ожидания на выходе, что приводит к 16 выходным запоминающим устройствам по фиг. 7. Вне этого 32 выхода движения и выхода обслуживания должны иметь возможность быть достигнутыми индивидуально, что представлено 33 выходными назначениями, следовательно, требует 33 дополнительных очереди ожидания. Но вследствие этого индивидуального доступа можно сказать, что запись ячейки в одну из этих выходных очередей ожидания исключает свою запись в любую другую очередь ожидания. Отсюда следует, что эти очереди ожидания могут быть помещены в одну и ту же выходную память и что она может быть, кроме того, одним из 16 выходных запоминающих устройств, упомянутых ранее. Это выходное запоминающее устройство является памятью M1 блока RGM1. Окончательно, как это указывалось ранее, два множества 16 выходов образуют каждое группу выходов, снабженных очередью ожидания, и запись ячейки в одну из этих очередей ожидания исключает, кроме того, запись ячейки в любую другую очередь ожидания. Следствием этого является то, что эти две выходные очереди ожидания также были помещены в память M1, которая содержат также всего 36 выходных очередей ожидания.

Прежде всего нужно рассмотреть наиболее простой случай, блок очереди ожидания RGM2. Он имеет, как уже говорилось, память M2, имеющую столько ячеек памяти, сколько имеется различных идентификаторов ячеек; в примерe этого описания идентификатор ячейки отличается тем, что адрес его первой подъячейки в буферной памяти BM (фиг. 1), а следовательно, и память выхода M2, имеет столько же ячеек, сколько их находится в последней, причем каждая ячейка памяти M2 может записывать адрес ячейки памяти BM, соответствуя первой подъячейке следующей ячейки сцепленного списка, образующего очередь ожидания. Она включает, кроме того, указатель первой ячейки FBC, указатель последней ячейки LBC, а также различные порты, мультиплексор MPX и регистр R. Сошлемся также на описание комплекса логики управления очередями ожидания и выбора выхода COQML, который представляет собой связи входа и выхода.

Для записи в очередь ожидания ячейки часы QCM (фиг. 6) выдают активный сигнал WR и в процессе действия этого сигнала импульс t1, за которым следует импульс t2. Мультиплексор MPX ориентирован сигналом WR так, чтобы содержимое указателя последнeй ячейки LBC было передано адресному регистру R. В процессе действия импульса t1 регистр R загружается этим адресом и адресует его на запись в память M2. Память M2 инициализируется на запись сигналом WE2, определяя, что адрес WISA должен быть связан в выходной очереди ожидания с блоком выходных очередей ожидания RGM2. Этот адрес WISA, который представляет собой идентификатор ссылки ячейки, т.е. адрес WISA записи первой подъячейки ячейки буферной памяти BM по фиг. 1, записан в память M2. В течение импульса t2 порт p12 открыт вследствие того, что сигнал WE2 имеется, так что адрес WISA записывается в указатель последней ячейки LBC. Именно таким образом в записи идентификатор ссылки каждой ячейки прицепляется к выбранной выходной очереди ожидания регистрацией в ячейку выходной памяти, адрес которой соответствует идентификатору последней, сцепленной с идентификатором поступающей ячейки; этот идентификатор записывается затем в указатель последней ячейки с целью сцепления со следующей ячейкой.

Отметим, что запись адреса WISA имеет место идентично одновременно в любом другом также выбранном блоке памяти выхода (за исключением некоторых различных деталей, что касается блока RGM1).

Для считывания идентификатора ссылки ячейки, который является адресом регистрации первой подъячейки ячейки, сигнал RE2, определяя, что идентификатор ссылки затребованной ячейки должен быть считан в блоке выходной памяти RGM2, открывает порт pf2, который передает содержимое указателя первой ячейки FBC как идентификатор ссылки FSAO. Сигнал WR является неактивным, но импульсы t1 и t2 генерированы как для записи. Мультиплексор MPX ориентирован к указателю первой ячейки FBC так, чтобы импульс t1 загружал содержимое указателя в адресный регистр R, который адресует тогда на считывание память M2 (сигнал WE2 является неактивным). Содержимое считанной ячейки, указанное как NFSA на фиг. 1, есть идентификатор ссылки следующей ячейки в очереди ожидания. Импульс t2 открывает тогда порт pnf2, разрешенный сигналом RE2, так что информация NFSA записывается в указатель первой ячейки FBC на место переданного адреса FSAO для того, чтобы сделаться позднее адресом FSAO, в ответ на требование следующего идентификатора ссылки, относящегося к выходной памяти M2. Именно так, в общем виде, при считывании идентификатор ссылки первой ячейки выдается указателем первой ячейки, прицепленной к выбранной выходной очереди ожидания, и служит для считывания в ячейке выходной памяти, адрес которой соответствует первой прицепленной ячейке идентификатора следующей ячейки, который затем записывается в указатель первой ячейки с целью поставки идентификатора ссылки следующей ячейки очереди ожидания.

Другие блоки выходной памяти от RGM3 (не показаны) до RGM16 являются идентичными и отвечают одновременно на сигналы выбора WE3-WE16 и RE3-RE16, импульсы часов WR, T1, T2, адрес WISA, и выдают адрес FSAO через порт ИЛИ pof.

Блок выходной памяти RGM1 подобен блокам, которые были только что описаны, и отличается лишь тем, что он содержит 36 выходных очередей ожидания вместо одной. Для большей ясности идентичные элементы сохранили те же позиции. Для 36 сцепленных списков этих 36 очередей ожидания необходимы 36 указателей первой ячейки и 36 указателей последней ячейки. Они зарегистрированы в памяти указателей MPM, которая имеет 36 ячеек, каждая из которых содержит, как указано, указатель первой ячейки FBC и указатель последней ячейки LBC одной и той же очереди ожидания. Эта память адресуется либо сигналами QW1-QW6, либо сигналами QR1-QR6 с помощью мультиплексора адреса указателя MPXA в зависимости от того, является ли сигнал WR активным или неактивным. Поскольку сигналы W1 и W2 являются неактивными, эта адресация работает на считывание, и содержимое адресуемых ячеек выдается на два выхода памяти MPM. Эти два выхода памяти MPM точно соответствуют выходам двух регистров указателей блока RGM2 так, что находят затем идентично мультиплексор MPX, адресный регистр R, разрешенный импульсом t1 перед памятью выхода M1.

При записи идентификатора ссылки ячейки в очередь ожидания порт p11 играет роль, подобную роли порта p12 в блоке RGM2. Он работает в тот же момент под воздействием импульса часов t2, когда блок выходной памяти PGM1 выбран сигналом WE1. Тогда он выдает сигнал W1, что разрешает запись в память MPM. Информация WISA записана в ячейку, указанную сигналами QW1-QW6, и, более конкретно, в часть этой ячейки, соответствующую указателю последней ячейки LBC, причем содержимое части, соответствующей указателю первой ячейки FBC, защищается.

При считывании идентификатора ссылки ячейки порт pf1 играет точно ту же роль, что и порт pf2 блока RGM2, передавая содержимое указателя первой ячейки FBC ячейки памяти MPM, адресованной на считывание сигналами QR1-QR6, с момента, когда блок RGM1 выбран сигналом RE1. Затем порт pnf1 играет роль, подобную роли порта p12 в блоке RGM2. Он работает в тот же момент под воздействием импульса часов 2, когда блок выходной памяти RGM1 выбран сигналом RE1. Он выдает тогда сигнал W2, что разрешает запись в память MPM. Информация NFSA, считанная в памяти M1, записывается в ячейку, указанную сигналами QR1-QR6, и, более конкретно, в участок этой ячейки, соответствующий указателю первой ячейки FBC, причем содержимое участка, соответствующее указателю последней ячейки LBC, защищается.

Конечно очевидно, что в тех же целях могли быть использованы и другие структуры очередей ожидания, чем те, которые показаны на фиг. 7, и что те, которые были описаны, дают лишь один пример среди других возможных. В частности, можно было бы рассмотреть использование лишь одной выходной памяти для содержания в ней всех файлов ожидания. Запись одной и той же ячейки в несколько файлов ожидания будет выполняться тогда в последовательных циклах памяти. Кроме того, для того чтобы сцепленные списки различных файлов ожидания не были "смешаны" в случае передачи ячейки от точки ко многим точкам, нужно иметь возможность различать ссылочные идентификаторы ячеек записи подъячеек буферной памяти элементарного коммутатора, как это уже рассматривалось ранее, а для этого присвоить один идентификатор различным ссылкам каждой копии одной и той же ячейки, принадлежащей одному специальному выходному назначению.

Одна форма реализации логики управления очередями ожидания ячеек и выбором выхода OSQRCL показана на фиг. 8. Как это уже описывалось ранее, эта логика OSQRCL принимает идентификатор выхода YJ, сопровождаемый сигналом L, который указывает на то, что на этом выходе начинается передача последней подъячейки ячейки и что вследствие этого новая ячейка должна быть зарегистрирована на этом выходе. Роль логики OSQRCL состоит в выборе очереди ожидания группы выходов, которая предназначена для этого выхода, выдавая сигналы считывания очереди ожидания RE1-RE16 и QR1-QR6, которые направляют ее к очереди ожидания по фиг. 7, которая выдаст в ответ ссылочный идентификатор FSAO (фиг. 6 и 7) ячейки. В тот же момент логика OSQRCL выдаст идентификатор YJS выхода, для которого предназначена ячейка, сопровождаемая сигналом NCO.

Логика OSQRCL имеет две части, одна из которых, называемая частью выбора выхода OSC, будет описана позднее в двух формах реализации со ссылками на фиг. 9 и 10, а другая показана детально на фиг. 8. Часть выбора выхода OSC несет функцию приема идентификатора выхода YJ и сигнала L. В ответ на это немедленно или позднее она выдает идентификатор выхода YJS.

Структура и работа цепей по фиг. 8 должны быть рассмотрены в три различных этапа процесса обработки выходов.

Прежде всего предусмотрен один счетчик на выходную очередь ожидания, CLC1 - CLC51 (напомним, что блок очередей ожидания OQU имеет 36 + 15 = 51 очередь ожидания). Каждый из этих счетчиков инкрементируется на единицу с каждой ячейкой, записанной в очередь ожидания; он декрементируется на единицу с каждой ячейкой, извлеченной из очереди ожидания (зарегистрированной на выходе для передачи). Цепь тестирования, связанная с каждым счетчиком OTC1-OTC51, указывает на то, является ли очередь ожидания пустой или, напротив, содержит по меньшей мере одну ячейку в ожидании по значению соответствующего тест-сигнала C1Q1-C1Q51. Инкрементация этих счетчиков имеет место при записи каждой ячейки в очередь ожидания в ответ на сигналы QW1-QW6 и WE1-WE16, которые идентифицируют очередь или очереди ожидания, в которые записана ячейка. Цепь перекодировки WTR, принимая эти сигналы, управляет непосредственно входами инкрементации счетчиков, обозначенными как +1. Те, которые соответствуют выходным очередям ожидания, указанные перекодированными сигналами, видят их содержимое увеличенным на единицу. Декрементация счетчиков имеет место при считывании каждого ссылочного идентификатора ячейки в момент, когда (как это уже упоминалось и как это будет видно далее) сигналы OR1-OR6 и RE1-RE16 указывают очередь ожидания, в которой будет считан этот идентификатор ссылки. Цепь перекодировки RTR, принимая эти последние сигналы, управляет вследствие этого непосредственно входами декрементации счетчиков, обозначенными как -1. Тот, который соответствует очереди ожидания, указанной перекодированными сигналами, видит свое содержимое уменьшенным на единицу.

Затем, когда выход YJ затребует назначение новой ячейки, эта заявка отмечается частью выбора выхода OSC. Немедленно или позднее эта заявка будет обслужена в интервале времени обработки выхода, в ходе которого идентификатор YJS, выданный частью выбора выхода OSC, будет точно YJ, причем эта заявка сопровождается присутствием сигнала OAV, также выдаваемого частью выбора выхода OSC.

Наконец, поскольку выбор выхода выполнен, что выражается выдачей идентификатора выхода YJS, производят назначение очереди ожидания, которая должна выдать идентификатор ссылки ячейки, который будет поставлен на учет выбранным выходом. С этой целью предусмотрена цепь выбора выходных очередей ожидания OQSC, которая принимает, с одной стороны, идентификатор выбранного выхода YJS, а с другой стороны, тест-сигналы CIQ1-CIQ51. Эта цепь выбора OQSC в рассматриваемом примере передает три тест-сигнала максимально из сигналов CIQ1-CIQ51 на выходы выбора CIQR, CIQS и CIQT. Действительно, ранее мы видели, что один и тот же выход может (в рассматриваемом примере) принадлежать одной группе одного или нескольких выходов нормальной транспортировки, а также принадлежать одной группе распределений, включающей множество выходов одного направления, и быть выбранным индивидуально для обслуживания, таким образом, до трех выходных направлений, следовательно, трех очередей ожидания. Поскольку выход выбран так, чтобы для него была предназначена одна ячейка, важно идентифицировать выходные направления, которые он обслуживает, что и реализуется в цепи OQSC. Более подробно, цепь OQSC передает тест-сигналы максимум трех выходных очередей ожидания на выбранных выходах CIQR, CIQS, CIQT в определенном порядке, который соответствует, например, очередям ожидания нормального движения, распределения и обслуживания. Один или несколько из этих выбранных выходов принимают тест-сигнал, указывая, что соответствующая очередь ожидания содержит по меньшей мере одну ячейку. Цепь приоритетов между очередями ожидания OQРS имеет своей функцией выбор между ними. Она передает один тест-сигнал, имеющий такое назначение на один из трех проводников выбора CIQU, CIQV, CIQW. Выходное назначение, которое должно быть обслужено выбранным выходом, является, таким образом, выбранным и идентифицированным. Этот выбор будет выполнен преимущественно по приоритету, определенному, например, в порядке: нормальная передача, распределения, обслуживание. Порт ИЛИ SODS выдает тогда сигнал RST для указания того, что выбранный выход будет действительно принимать идентификатор ссылки ячейки. Кроме того, цепь перекодировки идентификации выходной очереди ожидания OQIC принимает сигнал, присутствующий на одном из проводников выбора CIQU, CIQV, CIQW одновременно с выбранным идентификатором выхода YJS. Она выдает в обмен сигналы OR1-OR6 и RE1-RE16, которые идентифицируют, как это видели ранее, выходную очередь ожидания, которая считывается и выдает искомый идентификатор ссылки ячейки, тогда как соответствующий счетчик CLC1-CLC51 декрементируется.

Следовательно, видно, что цепи по фиг. 8 (причем выбран один выход) идентифицируют выходные назначения, обслуживаемые этим выходом, и тем самым выбирают одно, которое имеет по меньшей мере одну выдаваемую ячейку. Следовательно, остается рассмотреть как выбирается выход в заданное время.

Первый случай, который будет рассмотрен, иллюстрируется фиг. 9, который представляет первый вариант реализации OSC1 части выбора выхода OSC (фиг. 8). В первой фазе идентификатор выхода YJ служит адресом для ориентации демультипликатора выхода DMKS, который передает сигнал L на один из этих 33 выходов, который соответствует 33 выходам элементарного коммутатора (фиг. 3). Один из этих 33 каскадов регистра RD принимает сигнал L на свой вход S. Таким образом, он активизируется, если сигнал L присутствует, т.е. если обсуждаемый выход запрашивает ячейку для передачи. Так происходит в начале каждого интервала времени выхода, каждый раз, когда сигнал L присутствует, и требования ячеек хранятся в регистре RD, тогда как идентификатор выхода YJ временно записывается в регистр RYJ.

Во второй фазе, которая следует непосредственно за первой, регистр RYJ выдает идентификатор выхода YJS. Одновременно мультиплексор MXJS, ориентированный идентификатором YJS, тестирует наличие выхода YJS так, что его выход OAV будет активным, если каскад, соответствующий идентификатору YJS в регистре RD, является активным; присутствие сигнала OAV подтверждает еще не удовлетворенную заявку ячейки для выхода YJS, переданную логическим цепям OSQRCL по фиг. 8. Если, кроме того, одна из этих очередей ожидания, относящаяся к выходным направлениям, обслуживаемым этим выходам, может выдать ячейку, выдается сигнал RST. Он запоминается буферным каскадом RZ для выдачи сигнала NCO. Он также выдается на демультиплексор DMXZ, который ориентирован идентификатором выхода YJS. Этот сигнал подается на реинициализированный вход P каскада регистра RD; заявка ячейки, зарегистрированная в регистре RD, которая только что была удовлетворена, стирается в регистре RD для выхода YJS, т.е. в этом первом случае YJ.

С другой стороны, если выход YJS, т.е. в этом первом случае YJ, не имеется в наличии в регистре RD, неактивный сигнал OAV тормозит работу цепей по фиг. 8 и никакого выбора и считывания очереди ожидания не выполняется логикой OSQRCL, и сигнал остается неактивным. И, наоборот, если сигнал OAV является активным, но если никакое выходное назначение, соответствующее выходу YJ, не может быть выданным ячейкой, рассматриваемый выход, который выдал заявку ячейки, остается затребованным, поскольку ее наличие не стерто в регистре RD, причем сигнал RST остается неактивным.

Преимуществом такого варианта реализации является простота, но он может привести к корреляции между заявками ячеек выхода и записью ячеек в очередь ожидания. Желательно предусмотреть также средства для внесения соответствующих декорреляций. Фиг. 10 дает второй вариант реализации OSC2 части выбора выхода OSC, обеспечивая введение многих средств, имеющих целью такую декорреляцию.

В первой фазе вновь идентификатор выхода YJ служит адресом для ориентации демультиплексора выхода DMXS, который передает сигнал L на один из своих 33 выходов, которые соответствуют выходам элементарного коммутатора (фиг. 3). Один из 33 каскадов регистра RD принимает сигнал L на свой вход S. Таким образом, он активизируется, если присутствует сигнал L, т.е. если обсуждаемый выход требует ячейку для передачи. Это происходит в начале каждого интервала времени выхода каждый раз, когда присутствует сигнал L. Регистр RD хранит заявки ячеек для различных выходов. Кроме того, в цикле временного мультиплексирования обработки выходов все каскады регистра RD будут соответственно активизированы.

Идентификатор выбранного выхода YJS в этом втором случае выдается источником OSS, который в этот момент будет представлен как простой счетчик, вход инкрементации которого принимает один импульс на выходной интервал времени.

Во второй фазе интервала времени, в начале которой идентификатор выхода YJ обеспечивает активизацию соответствующего каскада регистра RD, источник OSS выдает идентификатор выбранного выхода YJS, который необязательно идентичен идентификатору YJ, а бывает обычно отличным от него.

Идентификатор выбранного выхода YJS подается на мультипликатор тестирования доступности выхода MXJS, который передает на проводник OAV состояние каскада регистра RD, соответствующего выбранному выходу YJS. Если выбранный выход выдал еще не удовлетворенную заявку ячейки, сигнал OAV обладает таким уровнем, чтобы была разрешена работа цепей (фиг. 8) по выбору выходного назначения, которое будет обслуживать выбранный выход. Если, кроме того, одна из этих очередей ожидания, относящаяся к выходным назначениям, обслуживаемым этим выходов, может выдать ячейку, выдается сигнал RST. Он записывается в память буферного каскада RZ2 для выдачи сигнала NCO, как и ранее. Он также выдается демультиплексору DMXZ, который ориентирован идентификатором выбранного выхода. Этот сигнал подается на вход реинициализации R каскада регистра RD; заявка ячейки, зарегистрированная в регистре RD, которая только что была удовлетворена, стирается в регистре RD для выхода YJS.