с третьим входом блока адресации. Первый выход оперативной памяти соединен с третьим входом блока передачи данных.

Недостатком этого процессора является относительно низкое быстродействие.

Цель изобретения - повышение быстродействия процессора.

Цель достигается тем, что в процесепр дополнительно введены блок анализа ч избирательной логики, блок обработки командной информации, блок временного сопряжения с памятью, блок аппаратурной имитации. Первые входы блока аппаратурной имитации и блока обработки командной информации соединены с выходом блока передачи данных, первый, второй, третий и четвертый выходы блока аппаратурной имитации связаны соответственно с четвертым и пятым входа-ми местной памяти, с четвертым входом блока преобразования виртуальных адресов и с вторым входом блока обработки командной информации, с первого по седьмой выходы которого соединены соответственно с вторым, третьим и четвертым входами блока аппаратурной имитации, с четвертым входом блока адресации, с вторым и третьим входами буферного блока команд, с четвертым входом буферного блока команд и первым входом блока анализа и избирательной логики, первый и второй выходы которого соединены с третьим и четвертым входами арифметико-логического блока, второй выход которого соединен с вторым входом блока анализа и избирательной логики, третий и четвертый входы которого соединены соответственно с вторым выходом второго коммутатора и с пятым выходом блока микропрограммного управления, шестой, седьмой и восьмой выходы которого соединены соответственно с первым и вторым входами блока временного сопряжения с памятью и с пятым входом блока аппаратурной имитации, шестой, седьмой, восьмой и девятый входы которого соединены соотВетственно с вторыми выходами буферного блока команд, блока базовой адресации, блока преобразования виртуальных адресов и выходом управляюш,ей памяти. Третий и четвертый входы блока обработки командной информации соединены соответственно с третьим выходом буферного блока команд и выходом блока адресации, третий вход, первый и второй выходы блока временного сопряжения с памятью соединены соответственно с вторым выходом и третьим входом оперативной памяти и о вторым входом блока микропрограммного управления.

Блок обработки командной информации содержит узел адресных регистров, регистр управления выборкой команд, матрицу безусловных переходов, дешифратор управления выборкой команд, дешифратор условных переходов, узел синхронизации буфера

команд, коммутатор адреса микрокоманды. Первый вход узла адресных регистров соединен с первым входом блока, второй вход которого соединен с первым входом дешифратора условных переходов, второй вход которого соединен с третьим входом блока, с вторым входом узла адресных регистров и первым входом узла синхронизации буфера команд, первый выход которого соединеп с третьим входом дешифратора условных переходов, четвертый вход которого соединен с первым выходом дешифратора управления выборкой команд, второй выход которого соединен с первым входом

коммутатора адреса микрокоманды, второй и третий входы которого соединены с выходами соответственно дешифратора условных переходов и матрицы без условных Переходов. Четвертый вход блока через регистр управления выборкой команд соединен с входами матрицы безусловных переходов и дешифратора управления выборкой, третий и четвертый выходы которого соединены соответственно с первым и вторым выходами блока, третий и четвертый выходы которого соединены соответственно с первым выходом узла адресных регистров и выходом коммутатора адреса микрокоманды. Пятый выход дешифратора управления выборкой команд соединен с вторым входом узла синхронизации буфера команд, седьмым выходом блока и с третьим входом узла адресных регистров, второй выход которого соединен с пятым выходом блока и третьим входом узла синхронизации буфера команд, второй выход которого соединен с шестым выходом блока. Блок аппаратурной имитации содержит коммутатор передачи адреса, дешифратор

обраш.ения к регистрам, выходной коммутатор, узел индикации включений, элемент И. Входы узла индикации включения со-единены с первым и пятым входами блока, третий и четвертый входы которого соеди«ены с первым и вторым входами коммутатора передачи адр.еса, выход которого соединен с третьим- выходом блока и пе,рвым входом выходного коммутатора, выход которого соединен с вторым выходом блока,

седьмой и девятый входы которого соединены с входами дешифратора обрашения к регистрам, выходы которого соединены соответственно с входом элемента И, третьим входом коммутатора передачи адреса, и

вторым входом выходного коммутатора, третий, четвертый и пятый входы которого соединены соответств-енно с шестым, вторым и восьмым входами блока. Выход узла индикации включения соединен с четвертым выходом блока и через элемент И с первым выходом блока.

Блок анализа и избирательной логики содержит узел формирования константы коммутатор сдвига, дешифратор и регистр

состояний. Первые входы дешифратора,

регистра состоянии п коммутатора сдвига соединены соответственно с первым, вторым и третьим входами блока, четвертый вход которого соединен с вторыми входами дешифратора и регистра состояний, первый выход которого соединен с вторым входом коммутатора сдвига и первым входом узла формирования константы, второй вход которого соединен с нервым выходом дешифратора и третьим входом коммутатора сдвига, выход которого и выход узла формирования константы соединены с первым выходом блока, второй выход которого соединен с вторыми выходами регистра состояний и дешифратора.

Блок временного сопряжения с памятью содержит узел индикации свободной зоны, одновибратор, узел фо,рмирова«ия временной развертки, узел индикации синхронизации, два элемента И, элемент ИЛИ. Первые входы узла индикации синхронизации и первого элемента И соединены с первым входом блока, второй вход которого соединен с первым входом узла индикации свободной зоны, третий вход блока соединен с вторым входом узла индикации свободной зоны и через одновибратор с нервым входом второго элемента И, второй вход которого соединен с выходом узла индикации синхронизации и вторым выходом блока, первый выход которого соединен с первым выходом узла формирования временной развертки, второй выход и вход которого соединены соответственно с вторым входом узла индикации синхронизации и выходом элемента ИЛИ, входы которого соединены соответственно с выходом второго элемента И и через первый элемент И с выходом узла индикации свободной зоны.

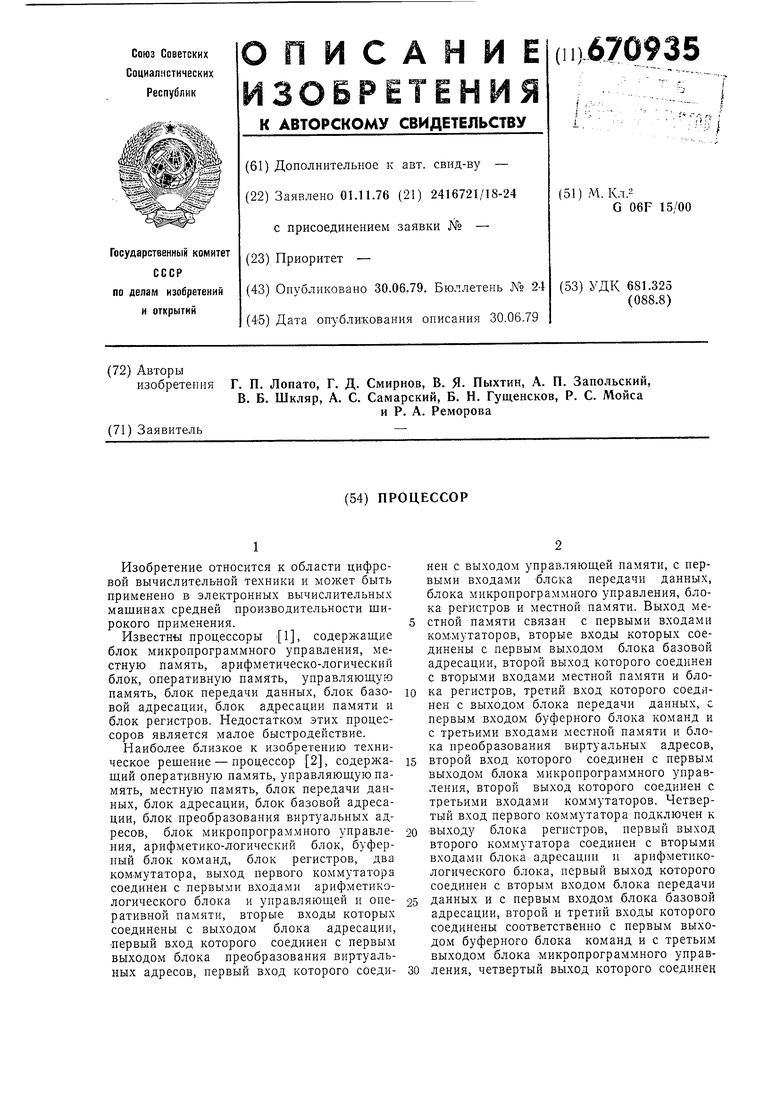

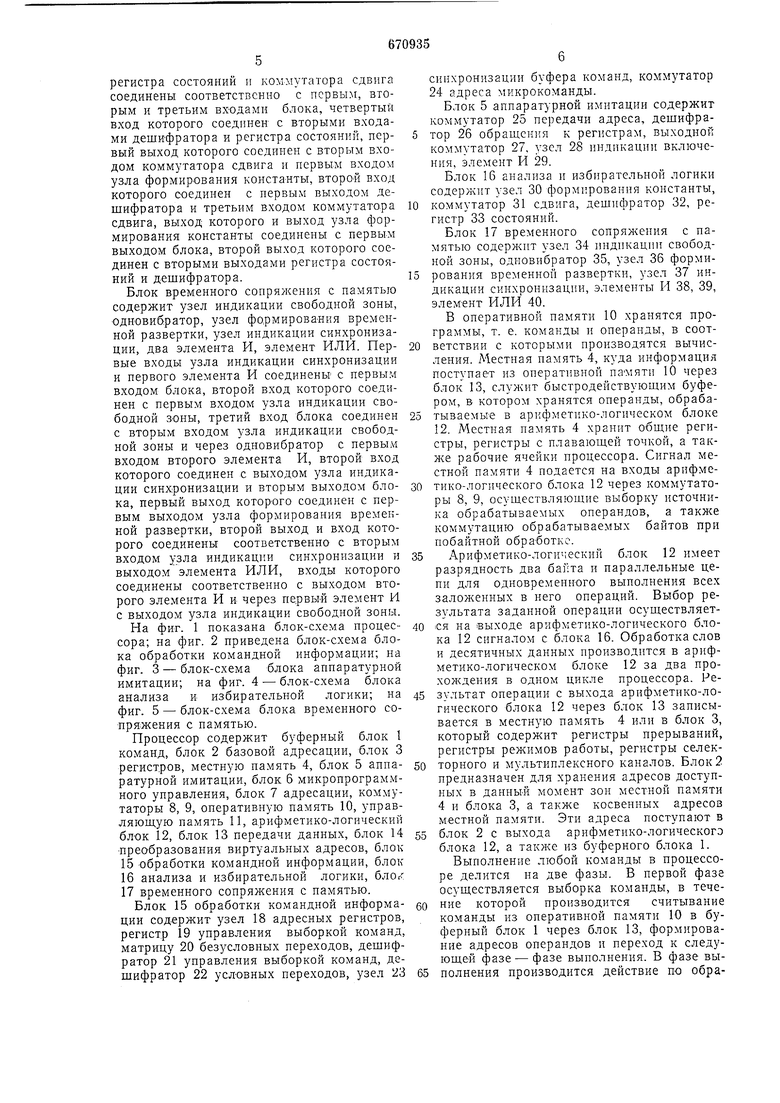

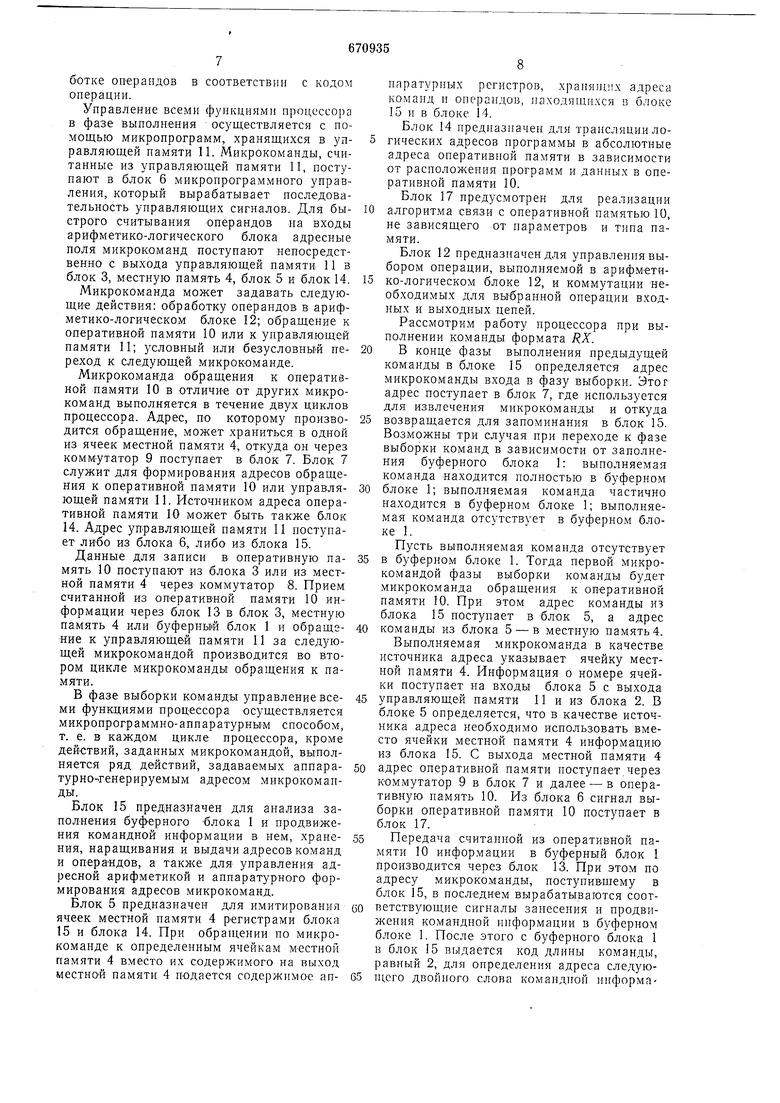

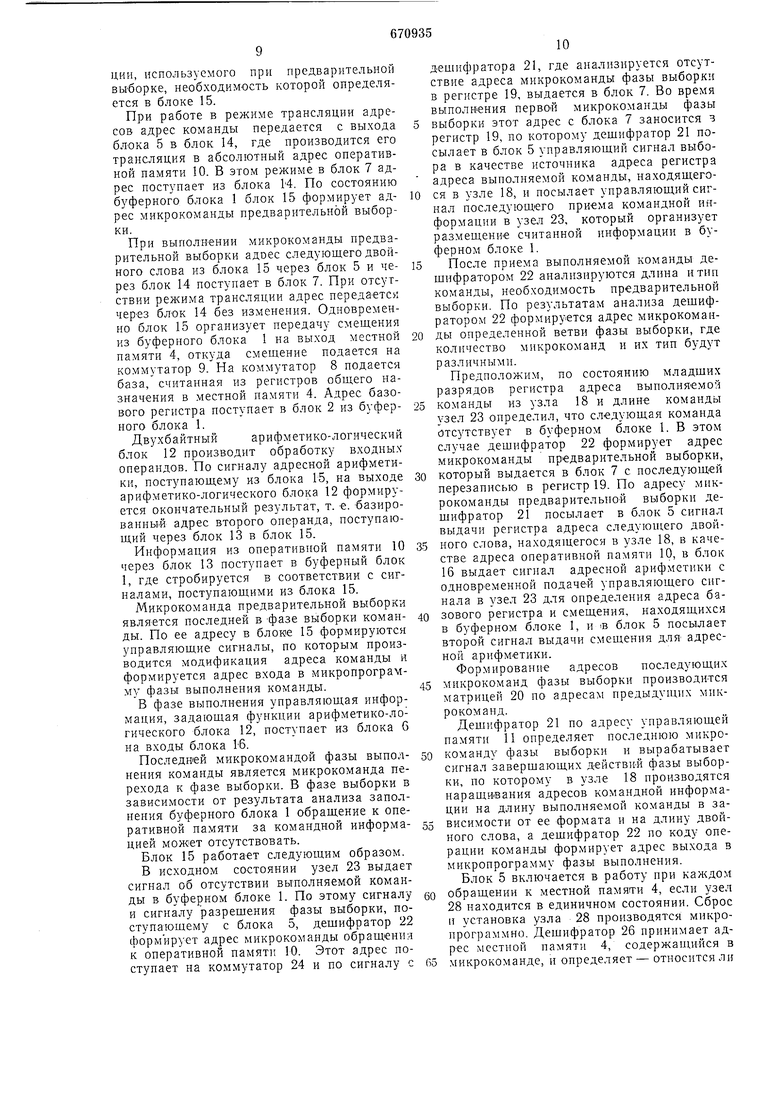

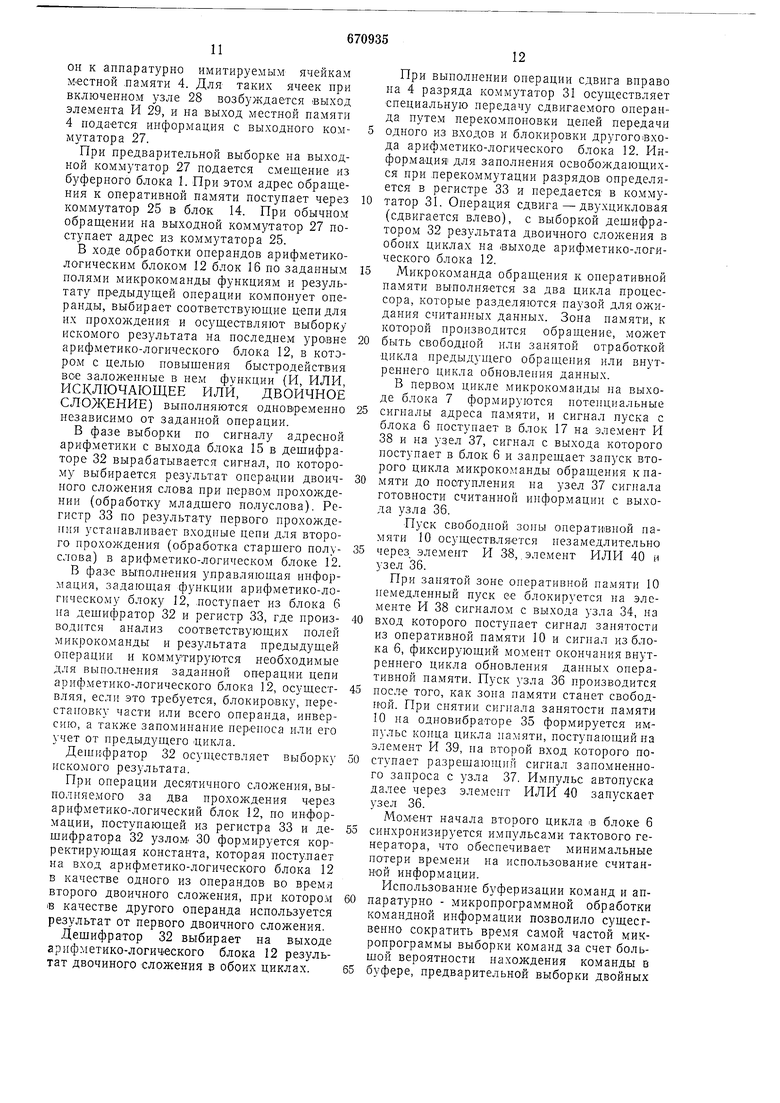

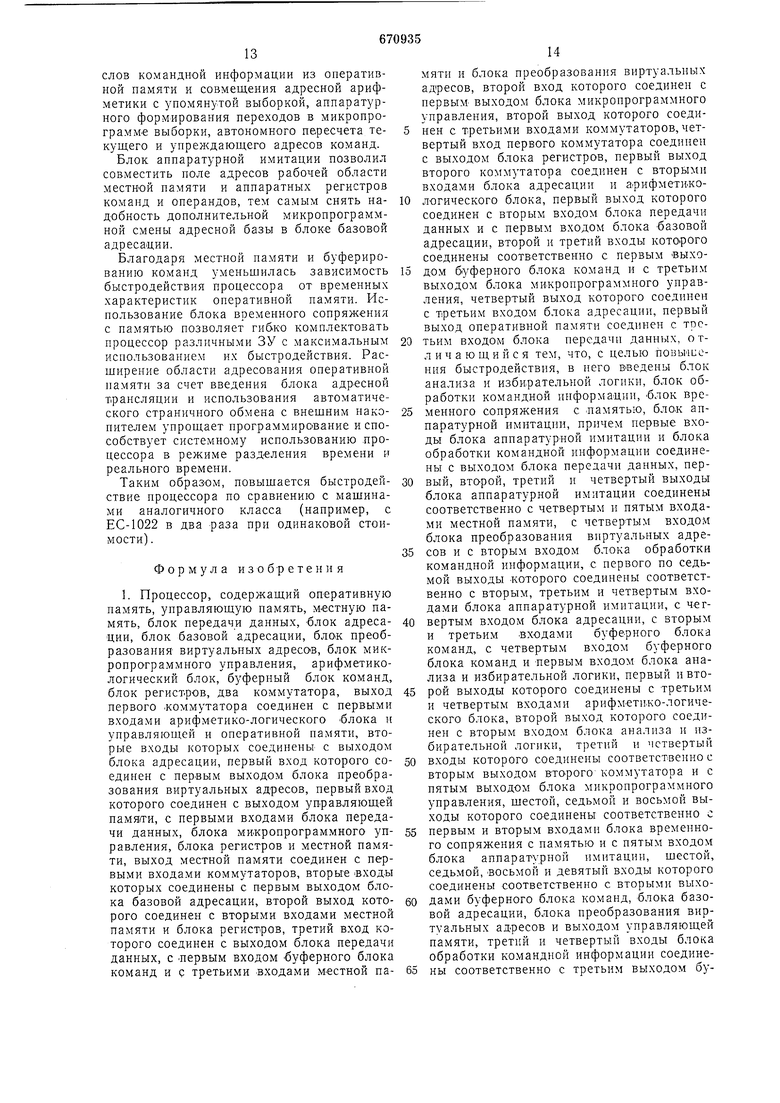

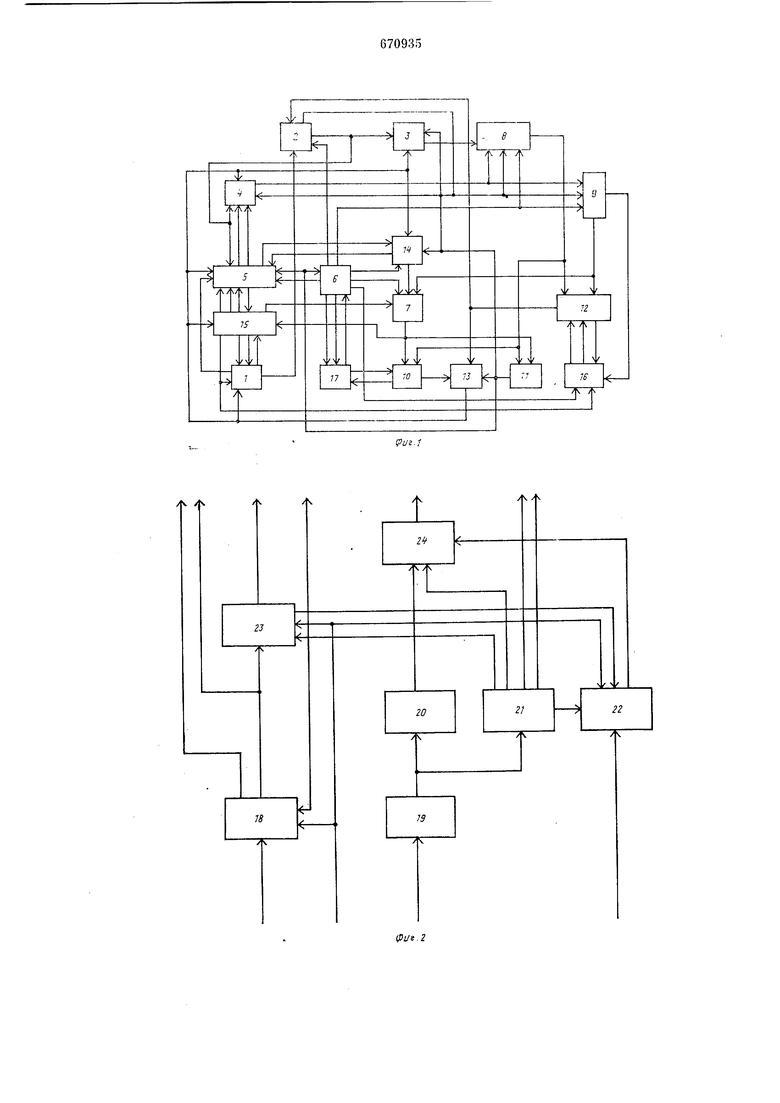

На фиг. 1 показана блок-схема процессора; на фиг. 2 приведена блок-схема блока обработки командной информации; на фиг. 3 - блок-схема блока аппаратурной имитации; на фиг. 4 - блок-схема блока анализа и избирательной логики; на фиг. 5 - блок-схема блока временного сопряжения с памятью.

Процессор содержит буферный блок 1 команд, блок 2 базовой адресации, блок 3 регистров, местную память 4, блок 5 аииаратурной имитации, блок 6 микропрограммного управления, блок 7 адресации, коммутаторы 8, 9, оперативную память 10, управляющую память 11, арифметико-логический блок 12, блок 13 передачи данных, блок 14 преобразования виртуальных адресов, блок

15обработки командной информации, блок

16анализа и избирательной логики, блогг

17временного сопряжения с памятью. Блок 15 обработки командной информации содержит узел 18 адресных регистров, регистр 19 управления выборкой команд, матрицу 20 безусловных переходов, дешифратор 21 управления выборкой команд, дешифратор 22 условных переходов, узел 23

синхронизации буфера команд, коммутатор 24 адреса микрокоманды.

Блок 5 аппаратурной имитации содержит коммутатор 25 передачи адреса, дешифратор 26 обращения к регистрам, выходной коммутатор 27, узел 28 индикации включения, элемент И 29.

Блок 16 анализа и избирательной логики содержит узел 30 формирования константы,

коммутатор 31 сдвига, дешифратор 32, регистр 33 состояний.

Блок 17 временного сопряжения с памятью содержит узел 34 1 ндикацни свободной зоны, одновибратор 35, узел 36 формирования временной развертки, узел 37 индикации синхронизации, элементы И 38, 39, элемент ИЛИ 40.

В оперативной памяти 10 хранятся программы, т. е. команды п операнды, в соответствии с которыми производятся вычисления. Местная память 4, куда информация поступает из оперативной памяти 10 через блок 13, служит быстродействующим буфером, в котором хранятся операнды, обрабатываемые в арифлтетико-логическом блоке 12. Местная память 4 хранит общие регистры, регистры с плавающей точкой, а также рабочие ячейки процессора. Сигнал местной памяти 4 подается на входы арпфметико-логического блока 12 через коммутаторы 8, 9, осуществляющие выборку источника обрабатываемых операндов, а также коммутацию обрабатываемых байтов при побайтной обработке.

Арифметико-логический блок 12 имеет разрядность два байта и параллельные цепи для одновременного выполнения всех заложенных в него операций. Выбор результата заданной операции осуществляетСя на выходе арифметико-логического блока 12 сигналом с блока 16. Обработка слов и десятичных данных производится в арифметико-логическом блоке 12 за два прохождения в одном цикле процессора. Результат операции с выхода арифметико-логического блока 12 через блок 13 записывается в местную память 4 или в блок 3, который содержит регистры прерываний, регистры режимов работы, регистры селекторного и мультиплексного каналов. Блок 2 предназначен для хранения адресов доступных в данный момент зон местной памяти 4 и блока 3, а также косвенных адресов местной памяти. Эти адреса поступают в

блок 2 с выхода арифметико-логического блока 12, а также из буферного блока 1.

Выполнение любой команды в процессоре делится на две фазы. В первой фазе осуществляется выборка команды, в течение которой производится считывание команды из оперативной памяти 10 в буферный блок 1 через блок 13, формирование адресов операндов и переход к следующей фазе - фазе выполнения. В фазе выполнения производится действие по обработке операндов в соответствии с кодом операции.

Управление всеми функциями процессора в фазе выполцения осуществляется с помощью микропрограмм, хранящихся в управляющей памяти 11. Микрокоманды, считанные из управляющей памяти II, поступают в блок 6 микропрограммного управления, который вырабатывает последовательность управляющих сигналов. Для быстрого считывания операндов па входы арифметико-логического блока адресные поля микрокоманд поступают непосредственна с выхода управляющей памяти 11 в блок 3, местную память 4, блок 5 и блок 14.

Микрокоманда может задавать следующие действия: обработку операндов в арифметико-логическом блоке 12; обращение к оперативной памяти 10 или к управляющей памяти 11; )словный или безусловный переход к следующей микрокоманде.

Микрокоманда обращения к оперативной памяти 10 в отличие от других микрокоманд выполняется в течение двух циклов процессора. Адрес, по которому производится обращение, может храниться в одной из ячеек местной памяти 4, откуда он через коммутатор 9 поступает в блок 7. Блок 7 служит для формирования адресов обращения к оперативной памяти 10 или управляющей памяти 11. Источником адреса оперативной памяти 10 может быть также блок 14. Адрес управляющей памяти И поступает либо из блока 6, либо из блока 15.

Данные для записи в оперативную память 10 поступают из блока 3 или из местной памяти 4 через коммутатор 8. Прием считанной из оперативной памяти 10 информации через блок 13 в блок 3, местную память 4 или буферный блок 1 и обращение к управляющей памяти 11 за следующей микрокомандой производится во втором цикле микрокоманды обращения к памяти.

В фазе выборки команды управление всеми функциями процессора осуществляется микропрограммно-аппаратурным способом, т. е. в каждом цикле процессора, кроме действий, заданных микрокомандой, выполняется ряд действий, задаваемых аппаратурно-генерируемым адресом микрокоманды.

Блок 15 предназначен для анализа запоЛНения буферного блока 1 и продвижения командной информации в нем, хранения, наращивания и выдачи адресов команд и операндов, а для управления адресной арифметикой и аппаратурного формирования адресов микрокоманд.

Блок 5 предназначен для имитирования ячеек местной памяти 4 регистрами блока 15 и блока 14. При обращении по микрокоманде к определенным ячейкам м естной памяти 4 вместо их содержимого на выход местной памяти 4 подается содержимо-е аппаратурных регистров, xpaiHinuix адреса команд п операндов, паходящихся в блоке 15 и в блоке 14.

Блок 14 предназначен для трансляции логических адресов программы в абсолютные адреса оперативной памяти в зависимости от расположения программ и данных в оперативной памяти 10. Блок 17 предусмотрен для реализации

алгоритма связи с оперативной памятью 10, не зависящего от параметров и типа памяти.

Блок 12 предназначен для управления выбором операции, выполняемой в арифметико-логическом блоке 12, и коммутации необходимых для вьгбранной операции входных и выходных цепей.

Рассмотрим работу процессора при выполнении команды формата RX.

В конце фазы выполнения предыдущей команды в блоке 15 определяется адрес микрокоманды входа в фазу выборки. Этот адрес поступает в блок 7, где используется для извлечения микрокоманды и откуда

возвращается для запоминания в блок 15. Возможны три случая нри переходе к фазе выборки команд в зависимости от заполнения буферного блока 1: выполняемая команда находится полностью в буферном

блоке 1; выполняемая команда частично находится в буферном блоке 1; выполняемая команда отсутствует в буферном блоке 1. Пусть выполняемая команда отсутствует

в буферном блоке 1. Тогда первой микрокомандой фазы выборки команды будет микрокоманда обращения к оперативной памяти 10. При этом адрес команды из блока 15 ноступает в блок 5, а адрес

команды из блока 5 - в местную память 4. Выполняемая микрокоманда в качестве источника адреса указывает ячейку местной памяти 4. Информация о номере ячейки поступает на входы блока 5 с выхода

управляющей памяти 11 и из блока 2. В блоке 5 определяется, что в качестве источника адреса необходимо использовать вместо ячейки местной памяти 4 информацию из блока 15. С выхода местной памяти 4

адрес оперативной памяти ноступает,через коммутатор 9 в блок 7 и далее - в оперативную намять 10. Из блока 6 сигнал выборки оперативной памяти 10 поступает в блок 17.

Передача считанной из оперативной памяти 10 информации в буферный блок 1 производится через блок 13. При этом по адресу микрокоманды, поступившему в блок 15, в последнем вырабатываются соответствующие сигналы занесения п продвижения командной информации в буферном блоке 1. После этого с буферного блока 1 в блок 15 выдается код длины команды, равный 2, для определения адреса следуюП1,его двойного слова командной информП

9

ции, используемого при предварительиой выборке, необходимость которой определяется в блоке 15.

При работе в режиме трансляции адресов адрес команды передается с выхода блока 5 в блок 14, где производится его трансляция в абсолютный адрес оперативной памяти 10. В этом режиме в блок 7 адрес поступает из блока 14. По состоянию буферного блока 1 блок 15 формирует адрес микрокоманды предварительной выборки.

При выполн-ении микрокоманды предварительной выборки адоес следующего двойного слова из блока 15 через блок 5 и через блок 14 поступает в блок 7. При отсутствии режима трансляции адрес переда ется чер-ез блОк 14 без изменения. Одновременно блок 15 организует передачу смещения из буферного блока 1 на выход местной памяти 4, откуда смещение подается на коммутатор 9. На коммутатор 8 подается база, считанная из регистров общего назначения в местной памяти 4. Адрес базового регистра поступает в блок 2 из буферного блока 1.

Двухбайтный арифметико-логический блок 12 производит обработку входных операндов. По сигналу адресной арифметики, поступающему из блока 15, на выходе арифметико-логического блока 12 формируется окончательный результат, т. «. базированный адрес второго операнда, поступающий через блок 13 в блок 15.

Информация из оперативной памяти 10 через блок 13 поступает в буферный блок 1, где стробируется в соответствии с сигналами, поступающими из блока 15.

Микрокоманда предварительной выборки является последней в фазе выборки команды. По ее адресу в блоке 15 формируются управляющие сигналы, по которым производится модификация адреса команды и формируется адрес входа в микропрограмму фазы выполнения команды.

В фазе выполнения управляющая информация, задающая функции арифметико-логического блока 12, поступает из блока G на входы блока 16.

Последней микрокомандой фазы выполнения команды является микрокоманда перехода к фазе выборки. В фазе выборки в зависимости от результата анализа заполнения буферного блока 1 обращение к оперативной памяти за командной информацией может отсутствовать.

Блок 15 работа ет следующим образом.

В исходном состоянии узел 23 выдает сигнал об отсутствии выполняемой команды в буферном блоке 1. По этому сигналу и сигналу разрешения фазы выборки, поступающему с блока 5, дешифратор 22 формирует адрес микрокоманды обращения к оперативной памят 10. Этот адрес поступает на коммутатор 24 и по сигналу с

10

дешифратора 21, где анализируется отсутствие адреса микрокоманды фазы выборки в регистре 19, выдается в блок 7. Во время выполнения первой микрокоманды фазы выборки этот адрес с блока 7 заносится з регистр 19, по которому дешифратор 21 посылает в блок 5 управляющий сигнал выбора в качестве источника адреса регистра адреса выполняемой команды, находящегося в узле 18, и посылает управляющий сигнал последующего приема командной информации в 23, который организует размещение считанной информации в буферном блоке 1.

После приема выполняемой команды дешифратором 22 анализируются длина итнн команды, необходимость предварительной выборки. По результатам анализа дешифратором 22 формируется адрес микрокоманды определенной ветви фазы выборки, где количество микрокоманд и их тип будут различными.

Предположим, по состоянию младших разрядов регистра адреса выполняемой

команды из узла 18 и длине команды узел 23 определил, что следующая команда отсутствует в буферном блоке 1. В этом случае дешифратор 22 формирует адрес микрокоманды предварительной выборки,

который выдается в блок 7 с последующей перезаписью в регистр 19. По адресу микрокоманды предварительной выборки дешифратор 21 посылает в блок 5 сигнал выдачи регистра адреса следующего двойного слова, находящегося в узле 18, в качестве адреса оперативной памяти 10, в блок 16 выдает сигнал адресной арифметики с одновременной подачей управляющего сигнала в узел 23 для определения адреса базового регистра и смещения, находящихся в буферном блоке 1, и в блок 5 посылает второй сигнал выдачи смещения для адресной арифметики.

Формирование адресов последующих

микрокоманд фазы выборки производится матрицей 20 по адресам предыдущих микрокоманд.

Дещифратор 21 по адресу управляющей памяти 11 определяет последнюю микрокоманду фазы выборки и вырабатывает сигнал завершающих действий фазы выборки, по которому в узле 18 производятся наращивания адресов командной информации на длину выполняемой команды в зависимости от ее формата и на длину двойного слова, а дешифратор 22 по коду операции команды формирует адрес выхода в микропрограмму фазы выполнения. Блок 5 включается в работу при каждом

обращении к местной памяти 4, если узел 28 находится в единичном состоянии. Сброс и установка узла 28 производятся микропрограммно. Дешифратор 26 принимает адрес местной памяти 4, содержащийся в

микрокоманде, и определяет - относится ли

11

он к аппаратурно имитируемым ячейкам Местной .памяти 4. Для таких ячеек при включенном узле 28 возбуждается выход элемента И 29, и на выход местной памяти 4 подается информация с выходного коммутатора 27.

При предварительной выборке на выходной коммутатор 27 подается смещение из буферного блока I. При этом обращения к оперативной памяти поступает через коммутатор 25 в блок 14. При обычном обращении на выходной коммутатор 27 поступает адрес из коммутатора 25.

В ходе обработки операндов арифметикологическим блоком 12 блок 16 по заданным нолями микрокоманды функциям и результату предыдущей операции компонует операнды, выбирает соответствующие цепи для их прохождения и осуществляют выборку искомого результата на последнем уровне арифметико-логического блока 12, в котором с целью повышения быстродействия вое заложенные в нем функции (И, ИЛИ, ИСКЛЮЧАЮЩЕЕ ИЛИ, ДВОИЧНОЕ СЛОЖЕНИЕ) выполняются одновременно независимо от заданной операции.

В фазе выборки по сигналу адресной арифметики с выхода блока 15 в дещифраторе 32 вырабатывается сигнал, по которому выбирается результат опера ции двоичного сложения слова при нервом прохождении (обработку младщего полуслова). Регистр 33 по результату первого нрохождепия устанавливает входные цепи для второго прохождения (обработка старшего полуслова) в арифметико-логическом блоке 12.

В фаЗС выполнения управляющая информация, задающая функции арифметико-логическому блоку 12, .поступает из блока 6 на дешифратор 32 и регистр 33, где производится анализ соответствующих нолей микрокоманды и результата предыдущей операции и коммутируются необходимые для выпо.тнения заданной операции цепи арифметико-логического блока 12, осуществляя, если это требуется, блокировку, перестановку части или всего операнда, инверсию, а также запоминание переноса или его учет от предыдущего цикла.

Дешифратор 32 осуществляет выборку искомого результата.

При операции десятичного сложения, выполняемого за два прохождения через арифметико-логический блок 12, по информации, ноступающей из регистра 33 и дешифратора 32 узлоМ 30 формируется корректирующая константа, которая поступает на вход арифметико-логического блока 12 в качестве одного из операндов во время второго двоичного сложения, при котором iB качестве другого операнда используется результат от первого двоичного сложения.

Дешифратор 32 выбирает на выходе арифметико-логического блока 12 результат двочиного сложения в обоих циклах.

12

При выполнении операции сдвига вправо на 4 разряда коммутатор 31 осуществляет специальную передачу сдвигаемого операнда путем перекомпоновки цепей передачи одного из входов и блокировки другого входа арифметико-логического блока 12. Информация для заполнения освобождающихся при .нерекоммутации разрядов определяется в регистре 33 и передается в коммутатор 31. Операция сдвига - двухцикловая (сдвигается влево), с выборкой дешифратором 32 результата двоичного сложения в обоих циклах на выходе арифметико-логического блока 12.

Микрокоманда обращения к оперативной памяти выполняется за два цикла процессора, которые разделяются паузой для ожидания считанных данных. Зона памяти, к которой производится обращение, может

быть свободной или занятой отработкой цикла предыдущего обращения или внутреннего цикла обновления данных.

В нервом цикле микрокоманды па выходе блока 7 формируются потенциальные

сигналы адреса памяти, и сигнал пуска с блока 6 поступает в блок 17 на элемент И 38 и на узел 37, сигнал с выхода которого поступает в блок 6 и запрещает запуск второго цикла микрокоманды обращения кпамяти до поступления на узел 37 сигнала готовности считанной информации с выхода узла 36.

Пуск свободной зоны оперативной памяти 10 осуществляется незамедлительно

через, элемент И 38, .элемент ИЛИ 40 и узел 36.

При занятой зоне оперативной памяти 10 немедленный пуск ее блокируется на элементе И 38 сигналом с выхода узла 34, на

вход которого поступает сигнал занятости из оперативной памяти 10 и сигнал из блока 6, фиксирующий момент окончания внутреннего цикла обновления данных оперативной памяти. Пуск узла 36 производится

после того, как зона памяти станет свободной. При снятии сигнала занятости памяти 10 на одновибраторе 35 формируется имп}льс конца цикла памяти, поступающий на элемент И 39, па второй вход которого поступает разрешающий сигнал запомненного запроса с узла 37. Импульс автопуска далее через элемент ИЛИ 40 запускает узел 36. Момент начала второго цикла в блоке 6

синхронизируется импульсами тактового генератора, что обеспечивает минимальные потери времени на использование считанной информации. Использование буферизации команд и апнаратурно - микропрограммной обработки командной информации позволило сущесгвенно сократить время самой частой микропрограммы выборки команд за счет больщой вероятности нахождения команды s

буфере, предварительной выборки двойных

слов командной информацин из онеративной памяти и совмещения адресной арифметики с упомянутой выборкой, аппаратурного формирования переходов в микропрограмм.е выборки, автономного пересчета текущего и упреждающего адресов команд.

Блок аппаратурной имитации позволил совместить поле адресов рабочей области местной памяти и аппаратных регистров команд и операндов, тем самым снять надобность дополнительной микропрограммной смены адресной базы в блоке базовой адресации.

Благодаря местной памяти и буферированию команд уменьшилась зависимость быстродействия процессора от временных характеристик оперативной памяти. Использование блока временного сопряжения с памятью позволяет гибко комплектовать процессор различными ЗУ с максимальным использованием их быстродействия. Расщирение области адресования оперативной памяти за счет введения блока адресной трансляции и использования автоматического страничного обмена с внешним накопителем упрощает программирование и способствует системному использованию .процессора в режиме разделения времени и реального времени.

Таким образом, повыщается быстродействие процессора по сравнению с машинами аналогичного класса (например, с ЕС-1022 в два раза при одинаковой стоимости).

Формула изобретения

1. Процессор, содержащий оперативную память, управляющую память, местную память, блок передачи данных, блок адресации, блок базовой адресации, блок преобразования виртуальных адресов, блок микропрограммного управления, арифметикологический блок, буферный блок команд, блок регистров, два коммутатора, выход первого коммутатора соединен с первыми входами арифметико-логического -блока и управляющей и оперативной памяти, вторые входы которых соединены с выходом блока адресации, первый вход которого соединен с первым выходом блока преобразования виртуальных адресов, первый вход которого соединен с выходом управляющей памяти, с первыми входами блока передачи данных, блока микропрограммного управления, блока регистров и местной памяти, выход местной памяти соединен с первыми входами коммутаторов, вторые входы которых соединены с первым выходом блока базовой адресации, второй выход которого соединен с вторыми входами местной памяти и блока регистров, третий вход которого соединен с выходом блока передачи данных, с Первым входом буферного блока команд и с третьими -входами м-естной памяти и блока преобразования виртуальных адресов, второй вход которого соединен с первым выходом блока микропрограммного управления, второй выход которого соединен с третьими входами коммутаторов, четвертый вход первого коммутатора соединен с выходом блока регистро-в, первый выход второго коммутатора соединен с вторыми входами блока адресации и арифмети-кологического блока, первый выход которого соединен с вторым входом блока передачи данных и с первым входом блока -базовой адресации, второй и третий входы которого соединены соответственно с первым выходом буферного блока команд и с третьи.м выходом блока микропрограммного управления, четвертый выход которого соединен с третьим входом блока адресации, первый выход оперативной памяти соединен с трстьим входом блока передачи данных, о тличающийся тем, что, с целью повы-шсния быстродействия, в него в-ведены блок анализа и избирательной логики, блок обработки командной информации, -блок временного сопряжения с .памятью, блок аппаратурной имитации, причем первые входы блока аппаратурной имитации и блока обработки командной информации соединены с выходом блока передачи данных, первый, второй, третий и четвертый выходы блока аппаратурной имитации соединены соответственно с четвертым и пятым входами местной памяти, с четвертым входом блока преобразования виртуальных адресов и с вторым входом блока обработки командной информации, с первого по седьмой выходы которого соединены соответственно с вторым, третьим и четвертым входами блока аппаратурной имитации, с чегвертым входом блока адресации, с вторым и третьим входами буферного блока команд, с четвертым входом буферного блока команд и первым входом блока анализа и избирательной логики, первый ивторой выходы которого соединены с третьи.м и четвертым входами арифметико-логического блока, второй выход которого соединен с вторым входом блока анализа и избирательной логики, третий и четвертый

входы которого соединены соответственно с вторым выходом второго коммутатора и с пятым выходом блока микропрограммного управления, щестой, седьмой и восьмой выходы которого со.единены соответственно с

первым и вторым входами блока временного сопряжения с памятью и с пятым входом блока аппаратурной имитации, щестой, седьмой, восьмой и девятый входы которого соединены соответственно с вторыми выходами буферного блока команд, блока базовой адресации, блока преобразования виртуальных адресов и выходом управляющей памяти, третий и четвертый входы блока обработки командной информации соединены соответственно с третьим выходом буферного блока .команд и выходом блока адресации, третий ВХОД, первый и второй выходы блока временного сопряжения с памятью соединены соответственно с вторым выходом и третьим входом онеративной памяти и с вто,рым входом блока микропрограммного управления.

2.Процессор .по п. I, отличающийся тем, что блок обработки командной информации содержит узел адресных регистров, регистр управления выборкой команд, матрицу безусловных переходов, дешифратор управления выбо-ркой команд, дешифратор условных переходов, узел синхронизации буфера команд, коммутатор адреса микрокоманды, причем первый вход узла адресных регистров соединен с первым входом блока, второй вход которого соединен с пеовым входом дешифратора условных переходов, второй вход которого соединен с третьим ВХОДОМ блока, с вторым входом узла адресных регистров и первым входом узла синхронизации буфера команд, первый выход которого соединен с третьим входом дешифратора условных переходов, четвертый вход которого соединен с нервым выходом дешифратора управления выборкой .команд, второй выход которого соединен с пер.вым входом коммутатора адреса микрокоманды, второй и третий входы которого соединены с выходами соответственно дешифратора условных переходов и матрицы безусловных -переходов, четвертый вход блока через р-егистр управления выборкой .команд .соединен с входами матрицы безусловнь1Х переходов и дешифратора ЗпраВления выборкой, третий и четвертый выходы которого соединены соответств.еино с первым и вторым выходами блока, третий и четвертый выходы которого соединены соответственно с первым выходом узла адресных регистров и выходом коммутатора адреса микрокоманды, пятый выход дешифратора управления .выборкой команд соединен с вторым входом узла синхронизации буфера команд, седьмым выходом блока и с третьим входо.м узла адресных регистров, второй выход которого соединен с пятым выходом блока и третьим входом узла синхронизации буфера .команд, второй выход которого соединен с ш.естым выходом блока.

3.Процессор по п. 1, о т л и ч а ю ш; и и с я тем, что блок аппаратурной имитации содержит коммутатор передачи адреса, дешифратор обраш;ения к регистрам, выходной коммутатор, узел индикации в-ключения, элемент И, причем входы узла индикации Включения соединены с первым и пятым входами блока, третий и четвертый входы которого соединены с первым и вторым входами коммутатора передачи адреса, выход которого со единен .с третьим выходом блока и первым входом выходного коммутатора, выход котор.ого соедипен с

вторым выходом блока, седьмой и девятый входы которого соединены с Входами дешифратора обращения к регистрам, выходы которого соединены соответственно входом элем-ента И, третьим входом коммутатора Передачи адреса и вторым входо.м выходного коммутатора, третий, четвертый и пятый входы которого соединены соответственно с шестым, вторым и восьмым входами блока, .выход узла индикации включения соединен с четвертым выходом блока и через элемент И с первым выходом блока.

4.Процессор по п. 1, отличающийся тем, что бло.к анализа и избирательной логики содержит узел форМ|Ирования константы, коммутатор сдвига, дешифратор и р.егистр состояний, причем первые входы дешифратора, регистра состояний и коммутатора сдвига соединены соответственно с

первым, вторым и третьим входами блока, четвертый вход которого соединен с вторыми входами дешифратора и регистра состояний, первый выход которого соединен с вторым входом коммутатора сдвига и первым входом .узла формирования константы, второй вход которого соединен с первым выходом дешифратора и третьим входом коммутатора сдвига, выход которого и выход узла формиро.вания. коистанты соединены с первым выходом блока, второй выход которого соединен с вторыми выходами регистра состояпий и дешифратора.

5.Процессор по п. 1, отличающийся тем, что блок временного сопряжения с

памятью содержит узел индикации свободной зоны, одновибратор, узел формирования временной .развертки, узел индикации синхронизации, два элемента И, элемеит

ИЛИ, причем первые входы узла индикации синхронизации и первого элемента И соединены с первым входом .блока, второй вход .которого соединен с первым входом узла индикаЦии свободной зоны, третий

вход блока соединен с вторым входом узла индикации свободной зоны и через одновибратор с пер Вым входом второго элемента И, второй вход которого соединен с выходом узла индикаци1И синхронизации и вторым выходом блока, .первый выход которого соедипен с первым выходом узла формирования временной развертки, второй выход и вход которого соединены соответственно с вторым входом узла индикации

синхронизации и выходом элемента ИЛИ, входы которого соединены соответственно с выходом второго элемента И и через первый элемент И с выходом узла индикации свободной зоны.

Источники информации,

принятые во внимание п.ри экспертизе 1. Патент США № 3959777, кл. 340- 172.5, 1976. 2. Патент США № 3656123, кл. 340-

172.6,1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор | 1984 |

|

SU1247884A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1264172A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Процессор | 1984 |

|

SU1246108A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Процессор с микропрограммным управлением | 1975 |

|

SU525956A1 |

| Микропрограммный процессор | 1978 |

|

SU741269A1 |

и

33

Авторы

Даты

1979-06-30—Публикация

1976-11-01—Подача