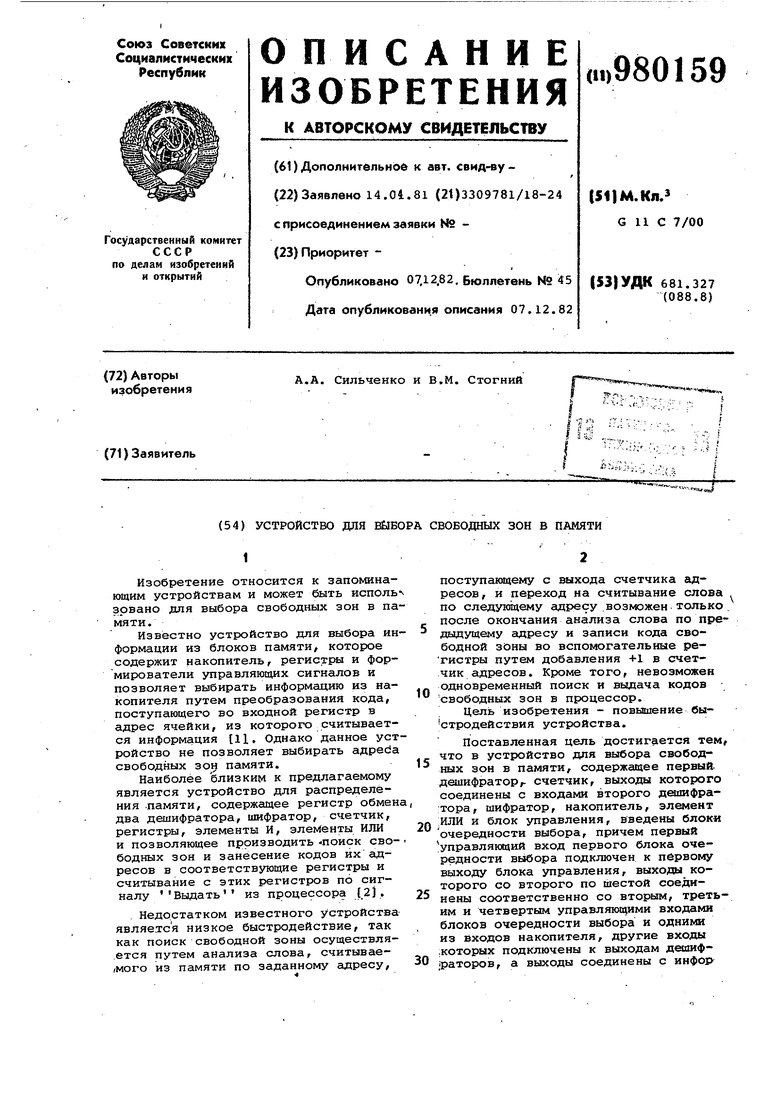

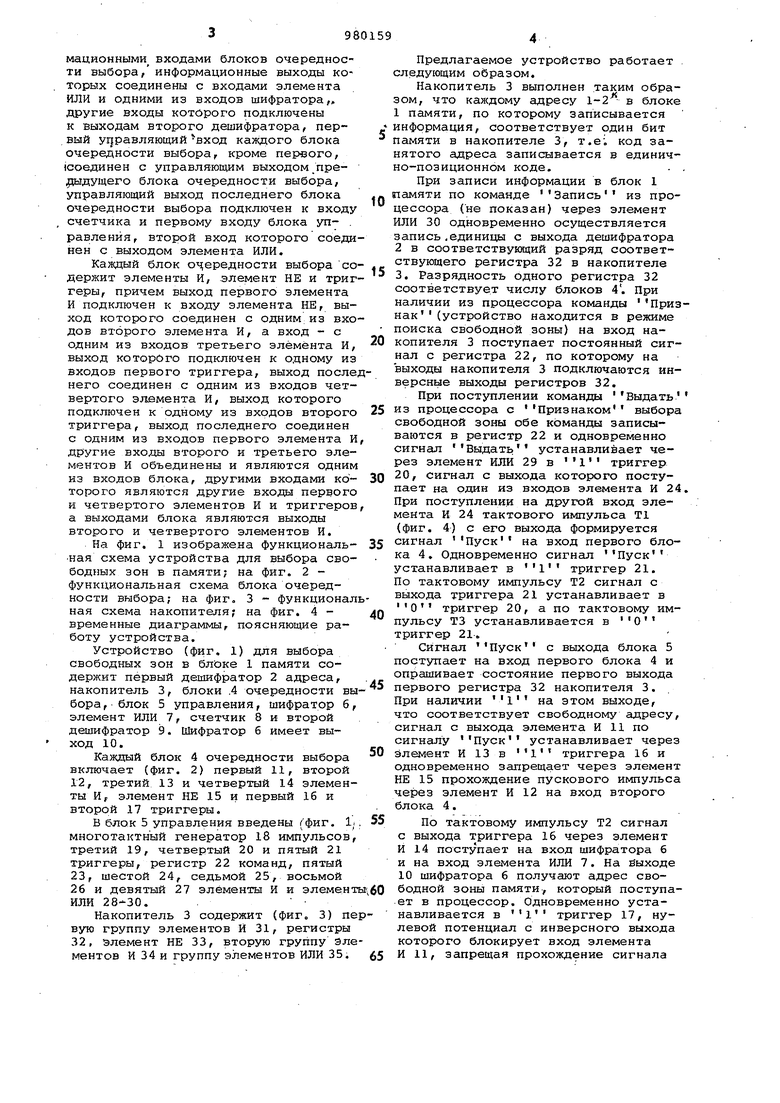

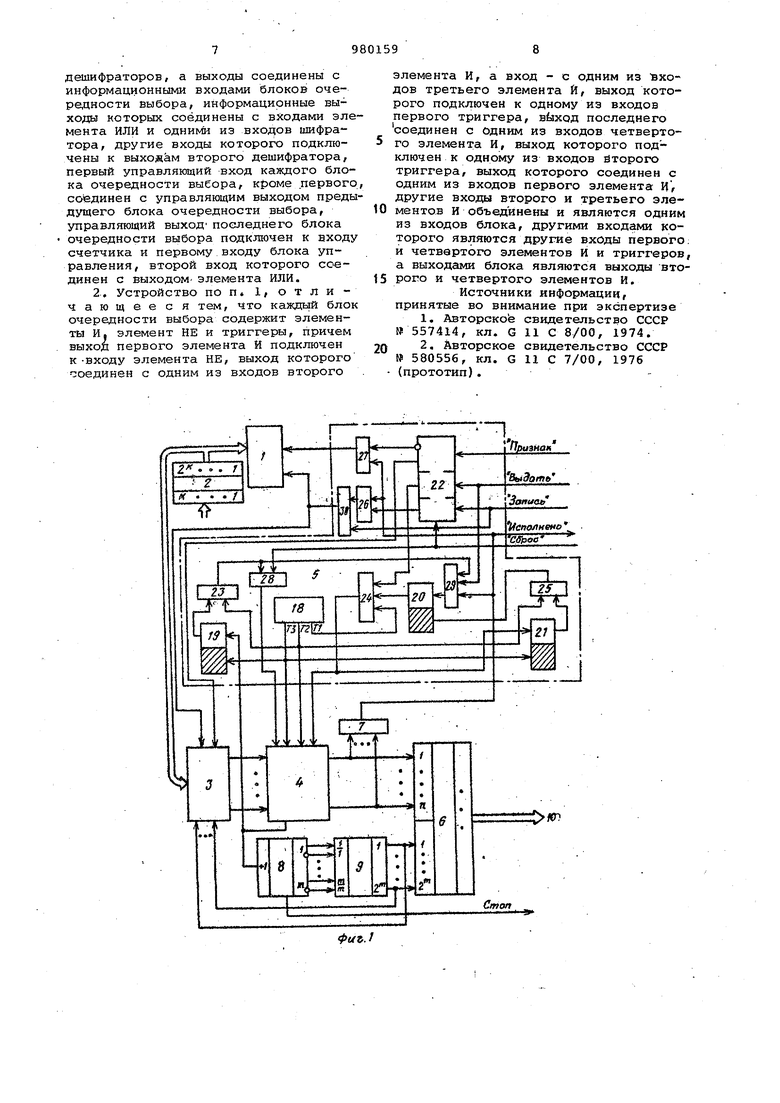

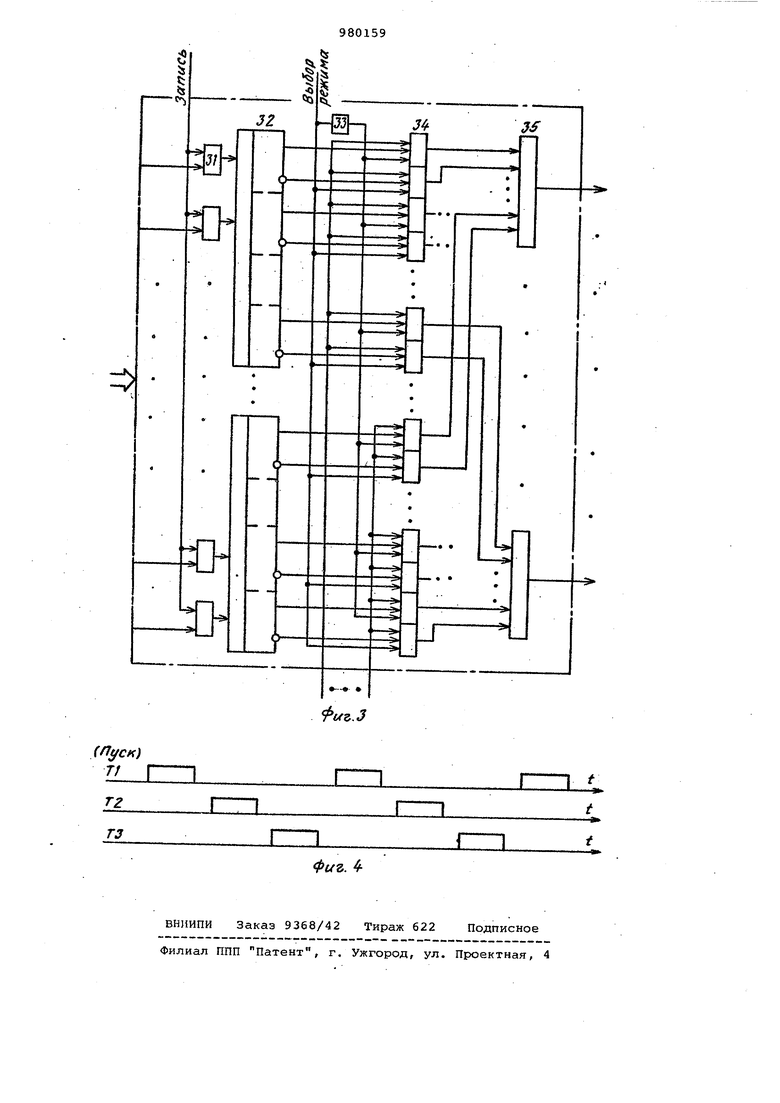

(54) УСТРОЙСТЮ ДЛЯ ВЫБОРА СВОБОДНЫХ ЗОН В ПАМЯТИ Изобретение относится к запоминающим устройствам и может быть иcпoль зрвано для выбора свободных зон в па мяти. Известно устройство для выбора ин формации из блоков памяти, которое содержит накопитель, регистры и формирователи управляющих сигналов и позволяет выбирать информацию из накопителя путем преобразования кода, поступающего во входной регистр в адрес ячейки, из которого считывается информация 11. Однако данное уст ройство не позволяет выбирать адреса свободных зон памяти. Наиболее близким к предлагаемому является устройство для распределения .памяти, содержащее регистр обмен два дешифратора, шифратор, счетчик, регистры, элементы И, элементы ИЛИ и позволяющее производить -поиск сво бодных зон и занесение кодов их адресов в соответствующие регистры и считывание с этих регистров по сигналу Выдать из процессора .2. Недостатком известного устройства является низкое быстродействие, так как поиск свободной зоны осуществляется путем анализа слова, считывае,мого из памяти по заданному адресу, поступающему с выхода счетчика адресов , и переход на считывание слова по следунлцему адресу возможен только . после окончания анализа слова по предыдущему сщресу и записи кода свободной зоны во вспомогательные реТистры путем добавления -Ы в счетчик адресов. Кроме того, невозможен одновременный поиск и выдача кодов свободных зон в процессор. Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем, что в устройство для выбора свободных зон в памяти, содержащее первый дешифратор,- счетчик, выходы которого соединены с входами второго детяифратора, шифратор, накопитель, элемент ИЛИ и блок управления, введены блоки очередности выбора, причем первый управлякхций вход первого блока очередности выбора подключен к первому выходу блока управления, выходы которого со второго по шестой соединены соответственно со вторым, третьим и четвертым управляющими входами блоков очередности выбора и одними из входов накопителя, другие входы :которых подключены к выходам дешифраторов, а выходы соединены с инфор мационными входами блоков очередности выбора/ информационные выходы которых соединены с входами элемента ИЛИ и одними из входов шифратора,, другие входы которого подключены к выходам второго дешифратора, пер, вый уг}равляющий вход каждого блока очередности выбора, кроме первого, (соединен с управляющим выходом пре дущего блока очередности выбора, управляющий выход последнего блока очередности выбора подключен к входу , счетчика и первому входу блока уп . равленйя, второй вход которого соеди нен с выходом элемента ИЛИ. Каждый блок очередности выбора со держит элементы И, элемент НЕ и триг геры, причем выход первого элемента И подключен к входу элемента НЕ, выход которого соединен с одним из вхо дов второго элемента И, а вход - с одним из входов третьего элемента И выход которого подключен к одному из входов первого триггера, выход после него соединен с одним из входов четвертого элемента И, выход которого подключен к одному из входов второго триггера, выход последнего соединен с одним из входов первого элемента И другие входы второго и третьего элементов И объединены и являются одним из входов блока, другими входами которого являются другие входы первого и четвертого элементов И и триггеров а выходами блока являются выходы второго и четвертого элементов И. На фиг. 1 изображена функциональная схема устройства для выбора свободных зон в памяти; на фиг. 2 функциональная схема блока очередности выбора; на фиг, 3 - функционал ная схема накопителя; на фиг. 4 временные диаграммы, поясняющие работу устройства. Устройство (фиг. 1) для выбора свободных зон в блоке 1 памяти содержит первый дешифратор 2 адреса, накопитель 3, блоки .4 очередности вы бора, блок 5 управления, шифратор б элемент ИЛИ 7, счетчик 8 и второй дешифратор 9. Шифратор 6 имеет выход 10. Каждый блок 4 очередности выбора включает (фиг. 2) первый 11, второй 12, третий 13 и четвертый 14 элемен ты И, элемент НЕ 15 и первый 16 и второй 17 триггеры. В блок 5 управления введены (фиг. 1 многотактный генератор 18 импульсов третий 19, четвертый 20 и пятый 21 триггеры, регистр 22 команд, пятый 23, шестой 24, седьмой 25, восьмой 26 и девятый 27 элементы И и элемен ИЛИ 28-30. . Накопитель 3 содержит (фиг. 3) п вую группу элементов И 31, регистры 32, элемент НЕ 33, вторую группу эл ментов И 34 и группу элементов ИЛИ 35. Предлагаемое устройство работает следующим образом. Накопитель 3 выполнен таким образом, что каждому адресу 1-2 в блоке 1памяти, по которому записывается информация, соответствует один бит памяти в накопителе 3, т.е; код занятого адреса записывается в единично-позиционном коде.. . При записи информации в блок 1 памяти по команде Запись из процессора (не показан) через элемент ИЛИ 30 одновременно осуществляется запись .единицы с выхода дешифратора 2в соответствующий разряд соответствующего регистра 32 в накопителе 3. Разрядность одного регистра 32 соответствует числу блоков 4. При наличии из процессора команды Признак (устройство находится в режиме поиска свободной зоны) на вход накопителя 3 поступает постоянный сигнал с регистра 22, по которому на выходы накопителя 3 подключаются инверсные выходы регистров 32. При поступлении команды Выдать из процессора с Признаком выбора свободной зоны обе команды записываются в регистр 22 и одновременно сигнал Выдать устанавливает через элемент ИЛИ 29 в Ч триггер 20, сигнал с выхода которого поступает на один из входов элемента И 24. При поступлении на другой вход элемента И 24 тактового импульса Т1 (фиг. 4) с его выхода формируется сигнал Пуск на вход первого блока 4 . Одновременно сигнгш Пуск устанавливает в триггер 21. По тактовому импульсу Т2 сигнал с выхода триггера 21 устанавливает в О триггер 20, а по тактовому импульсу ТЗ устанавливается в О триггер 21. Сигнал Пуск с выхода блока 5 поступает на вход первого блока 4 и опрашивает состояние первого выхода первого регистра 32 накопителя 3. При наличии на этом выходе. что соответствует свободному адресу, сигнал с выхода элемента И 11 по сигналу Пуск устанавливает через элемент И 13 в Ч триггера 16 и одновременно запрещает через элемент НЕ 15 прохождение пускового импульса через элемент И 12 на вход второго блока 4. По тактовому импульсу Т2 сигнал с выхода триггера 16 через элемент И 14 поступает на вход шифратора 6 и на вход элемента ИЛИ 7. На быходе 10 шифратора 6 получают адрес свободной зоны памяти, который поступает в процессор. Одновременно устанавливается в 1 триггер 17, нулевой потенциал с инверсного выхода которого блокирует вход элемента И 11, запрещая прохождение сигнала с входа элемента И 11 на вход элеме та И 13. Затем по тактовому импульс ТЗ, поступающему с блока 5 управления, устанавливается в О тригге 16. По сигналу с выхода элемента ИЛИ 7 фор1«1руется донесение в процессор Исполнено о наличии на выходах устройства адреса свободной зоны. Одновременно, если совместно с сигналом Выдать -процессор выдал и сигнал Запись, по сигналу Исполнено формируется через эле менты И 26 и ИЛИ 30 сигнал Запись по которому при наличии в процессор информации для записи может сразу ж быть записана информация по выбран.ному адресу. Сигнал с выхода элемента ИЛИ 7 устанавливает через элемент ИЛИ 29 в Ч триггер 20, с выхода которо го через элемент И 24 по тактовому импульсу Т1 формируется повторный сигнал Пуск в блоки 4. Так как на вход элемента И 11 поступает нулевой сигнал с инверсного выхода триггера 17, сигнал с выхода элемен та И 11 запрещает прохождение второ го импульса Пуск через элемент И 13 и разрешает через элемент НЕ 1 прохождение пускового импульса на пусковой вход второго блока 4 через элемент И 12. Сигнал Пуск проходит на вход элемента И 11 второго блока 4 и опрашивает состояние второго входа блока 4. При наличии на формируется адрес .этом входе второй свободной зоны. При наличии О(т.е. адрес за на втором входе нят) пусковой сигнал через элемент И 12 второго блока 4 поступает на пусковой вход третьего блока 4 и опрашивает состояние третьего входа, и, если на его входе присутствует О , пусковой импульс сра.зу же поступает на пусковой вход четвертого блока 4, т.е. время опроса занятых адресов обусловлен только задержкой на элементах И 12 блоков 4 и только при опросе адреса свободной .зоны про исходит задержка на время выдачи адреса свободной зоны на выходные шины адреса и формирования сигнала Исполнено. Пусковой сигнал с выхода последнего блока 4 поступает на входы счет чика 8 и блок. 5 управления. Счетчик 8 переходит в следующее состояние, сигналы кода состояния с его выходов поступают на входы дешифратора 9, на выходе которого формируется управляющий сигнал, который поступает на вход, накопителя 3 и подключает выходы второго регистра к входам блоков Одновременно сигнал с выхода последнего блока 4 поступает на вход блока 5 управления и устанавливает , в триггер 19, с выхода которого по тактовому импульсу Т2 через элементы И 23 и ИЛИ 28 формируется сигнал Сброс в блоки 4, по которому все триггеры 17 всех блоков 4 устанавливаются в О , сигнал с выхода элe teнтa И 23 поступает также на вход ИЛИ 29 и устанавливает в триггер 20, с выхода которого через элемент И 24 по тактовому импульсу Т1 формируется сигнал Пуск в блоки 4, по которому начикается опрос второго регистра накопителя 3. Таким образом, осуществляется опрос всех регистров накопителя 3. Сигнал переполнения счетчика 8 поступает на выход Стоп устройства, служит для прекращения поиска свободной зоны памяти и одновременно является донесением об отсутствии свободных зон в блоке 1 памяти. По сигналу Выдать без Признака выбора свободной зоны с процессора, на-входе накопителя 3 отсутствует постоянный сигнал. При отсутствии этого сигнала осуществляется через элемент НЕ 33 подключение к входам блоков 4 прямых, а не инверсных выходов регистров 32 накопителя 3, что позволяет осуществлять оперативный поиск занятых, зон блока 1 памяти с выводоминформации по сигналу Считывание, формируемому бло- . ком 5 управления при нахождении каждого адреса занятой зоны, и одновременной выдачей адресов занятых зон на выходы устройства. -Конструктивные особенности предлагаемого технического решения позволяют повысить быстродействие устройства путем .введения блоков очередности выбора, позволяющих производить автомати еский пропуск адресов занятых зон памяти,а также вследствие того, что время выборки свободных зон памяти определяется только количеством свободных адресов памяти. ; Формула изобретения 1. Устройство для выбора свободных зон в памяти, содержащее первый дешифратор, счетчик, выводы которого соединены с входами второго дешифратора, шифратор, накопитель, элемент ИЛИ и блок управления, отличаюЩ е е с я тем, что, с целью повышения быстродействия устройства, в него . введены блоки очередности выбора, причем первый управляющий вход первого блока очередности выбораподключен к первому выходу блока управления, выходы которого со второго по шестой соединены соответственно со вторым, третьим и четвертым управляющими вхоами блоков очередности выбора и одними из входов накопителя, другие входы которых подключены к выходам

дешифраторов, а выходы соединены с информационными входами блоков очере,цности выбора, информационные выходы которых соединены с входами элемента ИЛИ и одними из входов шифратора, другие входы которого подключены к выходам второго дешифратора, первый управляющий вход каждого блока очередности выбора, первого соединен с управляющим выходом предыдущего блока очередности выбора, управляющий ВЫХОД последнего блока очередности выбора подключен к входу счетчика и первому входу блока управления, второй вход которого соединен с выходом- элемента ИЛИ.

2. Устройство поп 1, отли чающее ся тем, что каждый блок очередности выбора содержит элементы И, элемент НЕ и триггеры, причем выход первого элемента И подключен к-входу элемента НЕ, выход которого соединен с одним из входов второго

элемента И, а вход - с одним из входов третьего элемента И, выход которого подключен к одному из входов первого триггера, вйход последнего соединен с одним из входов четвертого элемента И, выход которого подключен к одному из входов йторого триггера, выход которого соединен с одним из входов первого элемента Ц , другие входы второго и третьего элементов И объединены и являются одним из входов блока, другими входами которого являются другие входы первого и четвертого элементов И и триггеров а выходами блока являются выходы втоtS рого и четвертого элементов И.

Источники информации, принятые во внимание при экспертизе

1. Авторской свидетельство СССР № 557414, кл. G 11 С 8/00, 1974. 20 2. Авторское свидетельство СССР

№ 580556, кл. G И С 7/00, 1976 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное оперативное запоминающее устройство | 1988 |

|

SU1559379A1 |

| Микропрограммный процессор | 1981 |

|

SU980095A1 |

| Вероятностное устройство для решения конечно-разностных уравнений | 1980 |

|

SU888119A1 |

| Буферное запоминающее устройство | 1989 |

|

SU1654875A1 |

| Устройство для контроля знаний обучаемых | 1981 |

|

SU1005152A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

| Устройство приоритета | 1982 |

|

SU1108450A1 |

| Устройство для сопряжения ЦВМ и накопителя информации | 1985 |

|

SU1265780A1 |

| Перестраиваемый микропрограммный процессор | 1981 |

|

SU983713A1 |

| Устройство для моделирования узлов коммутации сообщений | 1985 |

|

SU1278879A1 |

, 1J

L.

Фи&.2

Фи,3

Авторы

Даты

1982-12-07—Публикация

1981-04-14—Подача