причем одна записывает в нее результат (с обычной точпостыо), а другая считывает операнд (с удвоенной точностью). ПроизвОлТ,ительность устройства в случае программ, оперпрующих с чпслами различной точностп, уменьшается.

При динамическом распределении ячеек информация в команде об этих ячейках представляется избыточной. Спстема команд ЭВМ, в которой распределение ячеек производится динамически, по своей сути не должна явным образом содержать адреса ячеек, пспользуемых для хранепия операндов н промежуточных результатов. Наиболее подходящей для этой цели является безадресная, или стековая, система команд. Обращение к ячейкам в стековом формате не привязано к ним до реального выполпепия команд, поэтому он удобен для динамического распределения ячеек.

Наличие адресов в поле команды, а также команды загрузки и считывания ячеек блока буферной памяти в блок оперативной памяти увеличивают длину программ. Необходимость указания в командах адресов по блоку буферной памяти усложняет программирование.

Наиболее близким к предлагаемому по технической сущности является устройство 2, содержащее регистр операций, блок управления, блок адресации и блок буферной памяти, информационные вход и выход которого соединены соответственно с информационным входом и первым информационным выходом устройства, адресный вход--с выходом блока адресации, вход и выход регистра операций соединены соответственно с первым входом устройства и с первым управляющим входом блока управления, второй управляющий вход которого соединен с первым управляющим входом устройства.

Устройство входит в состав высокопроизводительной вычислительной машины и управляет связью между блоками оперативной памяти и арифметическим блоком, осуществляемой через два быстродействующих регпстра блока буферной памяти, являющихся верхними ячейками стека. Следующие за ними ячейки стека в блоке буферной памяти также выполнены на быстродействующих регистрах, являющихся как бы продолжением основной оперативной памяти. При этом возможно произвольное обращение к любому из этих регистров и передача хранимой в них информации в регистры связи с арифметическим блоко.м.

Стековая (безадресная) система команд не содернсит явным образом адреса ячеек блока буферной памяти, используемых для хранения операндов и промежуточных результатов. Устройство формирует внутренний формат команды с адресами быстродействующих регистров, являющихся верхними ячейками стека, которые затем направляются в арифметический блок.

Эффективность ЭВМ с поточной обработкой комапд в большой мере зависит от распределения быстродействующих регистров, используемых для быстрого доступа к промежуточным результатам, так как планпрованпе параллельного выполнения независимых команд происходит за счет резервирования различных быстродействующих регистров для операндов, вызывае.мых из блока оператпвпой памяти, а также под результаты параллельно выполняемых команд.

В известном устройстве только два быстродействующих регистра блока буферной памяти, являющихся верхними ячейками стека, связаны с арифметическим блоком. Поэтому известное устройство не в состоянии обеспечить параллельную обработку нескольких команд в арифмет1 ческом блоке и, следовательно, не позволяет организовать параллельное выполнение команд по принципу поточной линии.

Цель изобретения - повышенпе производительности устройства в работе.

Это достигается тем, что в предлагаемое устройство введепы стек дешифрированных адресов, блок указателей стека дешифрированных адресов, стек свободных адресов, блок указателей стека свободных адресов, формирователь кода операции, коммутатор адресов, буферная память команд и блок восстановления, первые вход и выход которого подключены соответственпо к второму управляющему входу устройства и к входу блока управления, вторые вход и выход блока восстановления подключены соответственно к первому выходу блока управлення н к первому входу блока указателей стека свободных адресов, второй выход блока управления соединен с управляющими входами регистра операций, стека дешифрированных адресов, с управляющим выходом устройства, с первым входом блока указателей стека дещифрированпых адресов и с вторым входом блока указателей стека свободных адресов, третий выход блока уиравления соединен с управляюпдими входа.ми формирователя кода операции, коммутатора адресов, с третьим входом блока указателей стека свободных адресов, с вторым входом блока указателей стека дещифрированных адресов, вход блока управления соединен с управляющими выходами буферной памяти команд, блока указателей стека дешифрированных адресов, блока указателей стека свободных адресов, первый и второй выходы которого подключены к первому и второму адреспым входам стека свободных адресов, вход и выход которого соединены соответственно с иервым адресным входом устройства, с первым входом блока адресации и с первым входом коммутатора адресов, второй вход которого соединен с выходом стека дешифрированных адресов, выход коммутатора адресов соединен с первым входом буферной памяти команд и с входом стека дешифрированных адресов, адресный

вход которого подключен к выходу блока указателей стека дешифрированных адресов, выход регистра операций соединен через формирователь кода операции с вторым входом буферной памяти команд, управляющий вход которого соединен с третьим управляющим входом устройства, выход буферной памяти команд соединен с выходом устройства и с вторым входом блока адресации, третий вход которого соединен с вторым адресным входом устройства, выход блока адресации соединен с адресным выходом устройства, информационный вход устройства соединен с вторым информационным выходом устройства.

Это позволяет организовать в стековой ЭВМ обработку информации по принципу поточной линии, обеспечить параллельную обработку независимых команд, сохранить необходимый порядок среди зависимых команд и существенно повысить тем самым производительность устройства и вычислительной мащины в целом.

Отображение стекового формата команды во внутренний адресный формат команды производится динамически, непосредственно перед выполнением команды, причем для назначения ячеек командам используется все множество ячеек блока буферной памяти. Это полностью исключает коифликты по исиользованию блока буферной памяти.

При написании программ отпадает необходимость ведения учета по использованию блока буферной памяти, что облегчает программирование.

Отсутствие в стековом формате команд адресов по буферной памяти приводит к сокращению длины программ.

Поскольку адреса ячеек блока буферной памяти не присутствуют в стековом формате команды, количество их может быть выбрано таким, чтобы оно соответствовало максимальному количеству одновременно обрабатываемых команд, т. е. для очередной команды всегда имелась хотя бы одна свободная ячейка из блока буферной памяти под результат.

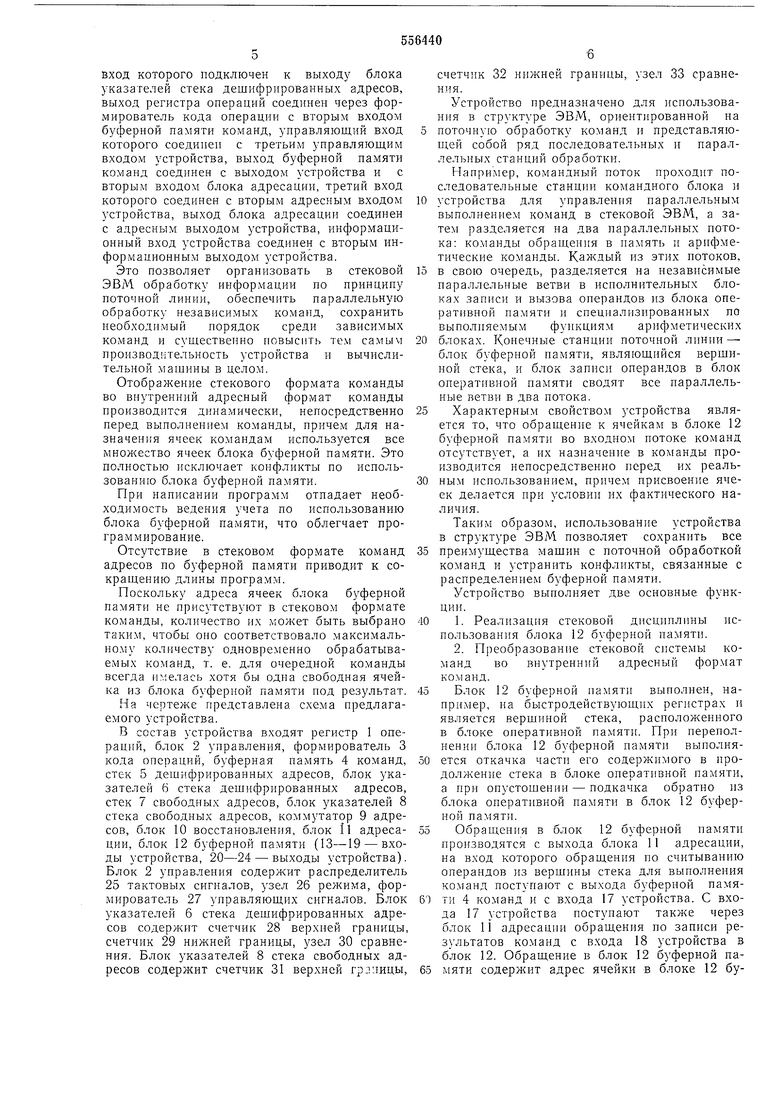

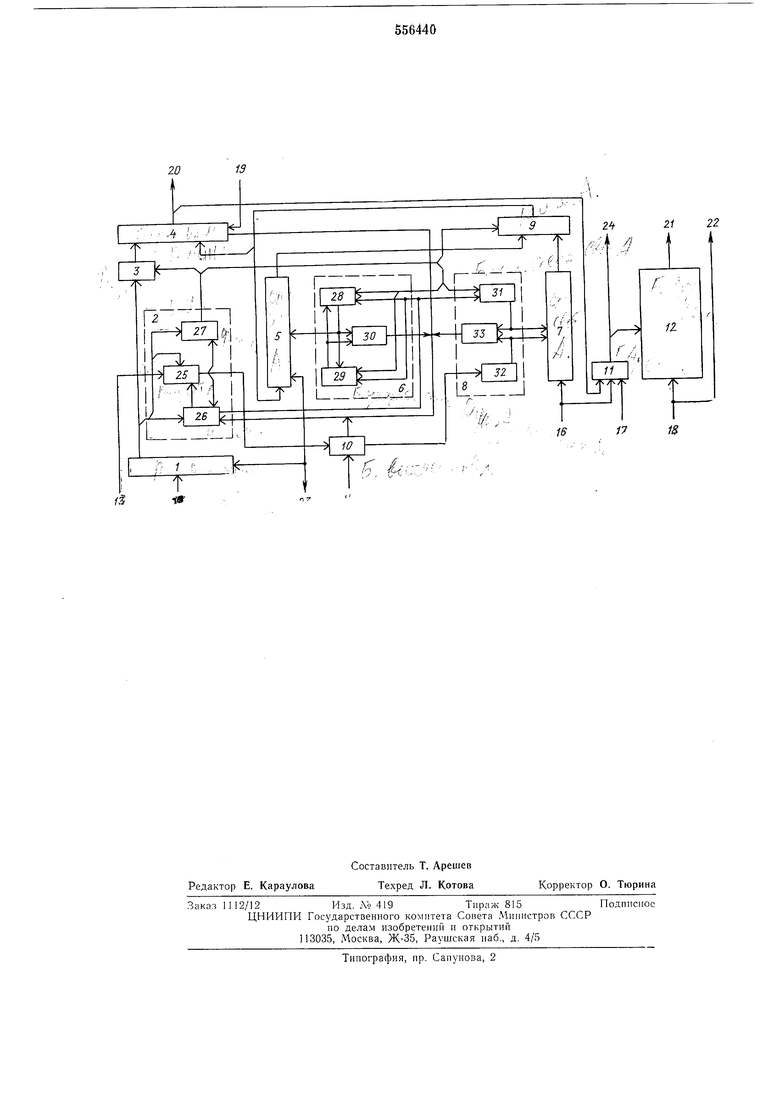

На чертеже представлена схема иредлагаемого устройства.

В состав устройства входят регистр 1 операций, блок 2 управления, формирователь 3 кода операций, буферная память 4 команд, стек 5 дешифрированных адресов, блок указателей 6 стека дешифрированных адресов, стек 7 свободных адресов, блок указателей 8 стека свободных адресов, коммутатор 9 адресов, блок 10 восстановления, блок П адресации, блок 12 буферной памяти (13-19 - входы устройства, 20-24 - выходы устройства). Блок 2 управления содержит распределитель 25 тактовых сигна.тов, узел 26 режима, формирователь 27 управляющих сигналов. Блок указателей 6 стека дешифрированных адресов содержит счетчик 28 верхней границы, счетчик 29 нижней границы, узел 30 сравнения. Блок указателей 8 стека свободных адресов содержит счетчик 31 верхней грлпицы.

счетчик 32 нижней границы, узел 33 сравнения.

Устройство предназначено для использования в структуре ЭВМ, ориентированной на поточную обработку команд и представляюи;ей собой ряд последовательных и параллельных станций обработки.

Например, командный поток проходит последовательные станции командного блока и

устройства для управления параллельным выполнением команд в стековой ЭВМ, а затем разделяется на два параллельных потока: команды обрашения в намять и арифметические команды. Каждый из этих потоков,

в свою очередь, разделяется на независимые параллельные ветви в исполнительных блоках записи и вызова операндов из блока оперативной памяти и специализированных по выполняемым функциям арифметических

блоках. Конечные станции поточной линии - блок буферной памяти, являющийся вершиной стека, и блок записи операндов в блок оперативной памяти сводят все параллельные ветви в два потока.

Характерным свойством устройства является то, что обращение к ячейкам в блоке 12 буферной памяти во входном потоке команд отсутствует, а их назначение в команды производится непосредственно перед их реальным использованием, прпчем присвоение ячеек делается при условии их фактического наличия.

Таким образом, использованне устройства в структуре ЭВМ позволяет сохранить все

преимущества мащин с поточной обработкой команд и устранить конфлнкты, связанные с распределением буферной памяти.

Устройство выполняет две основные функции.

1. Реализация стековой дисциплины использования блока 12 буферной памяти.

2. Преобразование стековой системы команд во внутренний адресный формат команд.

Блок 12 буферной памяти выполнен, например, на быстродействующих регистрах и является верщиной стека, расположенного в блоке оперативной памяти. При переполнении блока 12 буферной памяти выиолняется откачка части его содержимого в продолжение стека в блоке оперативной памяти, а при опустошении - подкачка обратно из блока оперативной памяти в блок 12 буфериой памяти.

Обращения в блок 12 буферной памяти производятся с выхода блока 11 адресации, на вход которого обращения по считыванию операндов из вершины стека для выполнения команд поступают с выхода буферной памяти 4 команд и с входа 17 устройства. С входа 17 устройства поступают также через блок И адресации обрашения по записи результатов команд с входа 18 устройства в блок 12. Обращение в блок 12 буферной памяти содержит адрес ячейки в блоке 12 буферной памяти и признак записи или считывания.

В блоке 11 адресации индикатор заполненности, соответствуюш,ий ячейке, к которой производится обращение, устанавливается в одно из двух состояний, например единичное при обращении в блок 12 по записи, когда в ячейку записывается информация. Индикатор заполненности ячейки переводится в нулевое состояние после выполнения команды, в которой она использовалась в качестве операнда. Адреса освободивпли.хся ячеек поступают с входа 16 устройства на входы стека 7 свободных адресов и блока 11.

Вся работа по поддержанию стековой днсциплины использования ячеек блока 12 буферной памяти производится не над cii.niMn ячейками, а над их адресами. Вся буфеоная память рассматривается как ресурс ячеек, назначаемых в стековую память под результаты очередных команд и возвращаемых обратно после использования в качестве операндов в последующих командах. Для этого р устройстве служат две малоразрядные памяти для хранения адресов ячеек блока 12 буферной памяти. Первая память - стек 5 дешифрированных адресов содержит адреса ячеек блока 12 буферной памяти, занятых в стеке на момент дещифрацнн очерел.ной команды. Эти адреса размещены в порядке стековой дисниплиньт обработки команд. Вторая память - стек 7 свободных адресов содержит адреса всех неиспользованных в данный момент ячеек блока 12 буферной памяти. Стек 7 вободных адресов используется по принципу очереди. Управление записью и считываннем адресов в стеке 5 детпифрированных адресов производится при помои1,и блока указателей 6 стека дешнфрированных адресов, а в стеке 7 свободных адресов - при помощи блока указателей 8 стека свободпых адресов.

Для очередной команды, поступающей в стековом формате с входа 14 устройства на регистр 1 операций, назначаются ячейки блока 12 буферной памяти, в которых находятся операнды, и ячейка, в которую будет помещен результат. Назначение ячеек в коман.ду осуществляется путем внутреннего представления команды в буферной памяти 4 команд, содержащей код операции, и адреса нат аченпых ячеек блока 12 буферной памяти. Для иллюстпаиии приведет; внутренний формат типовых команд:

Вызов операндаКОП, ЛЗ

СложениеКОП, А1, А2, A3

ОтрицаниеКОП, AI, A3

ЗанисьКОП, А1, А2

где КОП - код операции; А1 и А2--адреса ячеек операндов блока 12 буферной памяти; A3-адрес ячейки результата блока 12 буферной памяти.

Код операции передается с выхода регистра 1 операций через формирователь 3 кода

операций па первый вход буферной памяти 4 команд.

Адреса назначенных в команду ячеек операндов блока 12 буферной памяти поступают на ВТОРОЙ вход буферной памяти 4 команд из стека 5 дешнфрированных адресов через ком ;yтaтoD 9 адресов, управляемый формирователем 27 управляющих сигналов. Адрес ячейки блока 12 буферной памяти, назначенной под результат, поступает на второй вход буферной памяти 4 команд через коммутатор 9 адресов из стека 7 свободных адресов.

Иснользование под результат только свободной ячейкн блока 12 буферной памяти оказывается существенным при синхронизации логически связаиных команд, когда результат одной нспользуется в последующей как операнд. Сначала свободная ячейка блока 12 буферной памяти иазначается под результат очередной команды, и ее адрес помещается из стека 7 свободных адресов через коммутатор 9 адресов в стек 5 дещифрнрованных адресов. Затем он вычеркивается оттуда и назначается как адрес ячейки операнда в блоке 12 буферной памяти в последующую команду.

Команды, представленные во внутреннем адресном формате, с выхода буферной памяти 4 команд поступают на выход 20 устройства для их выполнения в упомянутых выще специализироваипых но своим функциям блоках, при УСЛОВИИ разрешения выдачи, постунаюшего на унравляющий вход буферной памяти 4 команд с входа 19 устройства. В момент выдачи команды с выхода буферной памяти 4 команд ИРОИЗВО.Т.ИТСЯ обращение но считыванию соответствующих ячеек операндов в блок 12 буферной иамятп через блок 11 адресации, и если ячейкн заполнены, то их содержимое с выхода блока 12 буферной памяти выдается иа выход 21 устройства. Если нет. то команда все равно выдается на выход 21 устройства в снециализированные блоки, где ожидает своих операндов. При обращении очередной команды по записи в блок 12 буферной памяти через блок 11 адресации с входа 17 устройства адрес ячейки под результат в блоке 12 буферной намяти передается также на выход 23 устройства, сопровождая, таким образом, результат очередной команды (и операнд для последующей), который, поступая с входа 18 устройства на вход блока 12 буферной памяти, одновременно передается на выход 22 устройства. С выходов 21 и 22 устройства операнды и с выхода 24 устройства соответствующие им адреса блока 12 буферной памяти поступают на входы всех нснолнительных специализированных блоков. По этим адресам команды, хранящиеся в специализированных блоках, опознают «своих операндов и начинают выполняться.

Одновременно с формированием внутреннего формата команды происходит реорганизация вершины стека или, что то же самое, стека 5 дешифрированных адресов. В счетчике 28 верхней границы блока указателей 6 стека дешифрированных адресов находится текуш,ий адрес по стеку 5, который с выхода счетчика 28 подается на адресный вход сте- 5 ка 5. Выдаваемые из стека 5 по значению счетчика 28 через коммутатор 9 в буферную память 4 адреса операндов по блоку 12, согласно стековой дисциплине обработки команд, вычеркиваются из стека 5. На их ме- ю сто по зиачению счетчика 28 записывается адрес ячейки под результат команды в блоке 12, который выдается из стека 7 через коммутатор 9 на вход стека 5. Вычеркивание операндов из стека 5 достигается изменением 15 значения счетчика 28, которым управляет формирователь 27. Таким образом, стековая дисциплина использования адресов ячеек блока 12, а следовательно, и самих операндов в этих ячейках обеспечивается соответствую- 20 щими изменениями счетчика 28 верхней граинцы, а также записью в стек 5 и считыванием из стека 5 по значению счетчика 28. Выдача адресов свободных ячеек блока 12 25 из стека 7 происходит аналогично по значению стетчика 31 верхней границы в блоке указателей 8 стека свободных адресов, выход которого соединен с первым адресным входом стека 7. Изменением ЗО значения счетчика 31 также управляет формирователь 27. Запись в стек 7 адресов по блоку 12 производится по значению счетчика 32 нижней границы, выход которого соединен с вторым ад- 35 ресным входом стека 7 и которым управляет бло-; 10 восстановления. Ячейка операнда блока 12 считывается освободившейся после выполнения команды, в которой она использовалась. Соответствующие сигналы о выпол- 40 пении команд с входа 15 устройства поступают в блок 10 восстановления, а освободившиеся адреса ячеек оиераидов с входа 16 устройства - на вход стека 7 и на вход блока 11 адресации. При этом в блоке 11 обнуляются 45 индикаторы заполненности соответствующих ячеек. С выхода регистра 1 операций очередная команда поступает в блок 2 управления. В фор.мнрователе 27 управляющих сигналов 50 вырабатывается последовательность сигналов, поступающих на его выход и управляю-щих изменениями счетчиков 28, 29 и 31. Кроме того, управляющие сигналы поступают на управляющие входы коммутатора 9 адре- 55 сов и формирователя 3 кода операции. На третью входную щину узла 26 режима поступают блокировочные сигналы с управляющего выхода буферной памяти 4 команд в случае его занятости, а также с выхода уз- 60 ла 30 сравнения в блоке указателей 6 стека дешифрированных адресов, с выхода узла 33 сравнения в блоке указателей 8 стека свободных адресов и с второго выхода блока 10 восстановления. 65 В узле 30 происходит сравнение значений счетчика 28 верхней границы и счетчика 29 нижней границы. По результату сравнения в узле 26 режима определяется наличие достаточного количества онераидов для выполнения очередной команды. Если количество операндов достаточно, то с первого выхода узла 26 выдается разрешение на выполнение команды, которое поступает на первый вход распределителя 25 тактовых сигналов. При этом ноступаюш:ие с входа 13 устройства тактовые сигналы на второй вход распределителя 25 преобразуются в соответствующую команду. Последовательность сигналов, выдаваемая с выходной шины распределителя 25, поступает в формирователь 27, узел 26 и блок 10. Происходит формирование внутреннего представления команды и реорганизация блоков указателей стеков 6 и 8, описываемые выше. Если в узле 26 определяется, что количество операндов меньше, чем требуется очередной команде, то организуется режим подкачки. С второго выхода узла 26 выдается блокировочный сигнал, запрещающий реорганизацию блоков указателей 6 и 8, запись в стек 5, прием в регистр 1 и дешифрацию последуЮП1Г1Х команд на выход 23 устройства. С первого выхода узла 26 в распределитель 25 выдается сигнал, по которому приостанавливается выдача тактовых сигиалов для очередной команды, и с выхода распределителя начинают поступать тактовые сигналы по временной диаграмме команды подкачки. По этим сигналам в формирователе 27 вырабатываются управляющие сигиалы для формировання команды подкачки в буферной памяти 4, куда поступает код операции, сформированный в формирователе 3, и адрес ячейки в блоке 12 из стека 7 через коммутатор 9. Для сохранения стековой дисциплины адрес для подкачиваемого оиеранда должен быть записан в стек 5 дешифрированных адресов ио значению счетчика 28 иижней границы, Для этого в формирователе 27 вырабатывается сигнал обмена, по которому обменивается содержимое счетчиков 28 и 29. Сформированная в буферной памяти 4 команда подкачки поступает на выход 20 устройства для выполнения. Формирование команд подкачки продолл ается до тех пор, пока количество адресов в стеке 5 дешифрированных адресов не будет соответствовать количеству требуемых для очередной команды операндов. На вход распределителя 25 в узле 26 вырабатывается сигнал о прекращении подкачки. По окончании режима подкачки производится обратный обмен содержимого счетчиков 28 и 29, причем значение счетчика 29 нижней границы будет новым по сравнению с его значением до начала подкачки. Распределитель 25 переключается на выработку тактовых сигналов по временной диаграмме очередной команды.

11

Режим откачки устанавливается аналогично режиму подкачки. Отличие в том, что нри отсутствии свободных адресов в стеке 7 и соответствующем сигнале из узла 33 сравнения в блоке указателей 8 стека свободных адресов режим откачки устанавливается лишь после того, как произойдет выполнение всех предыдущих команд. Сообщение об этом происходит с входа 15 устройства в блок 10 восстановления, откуда поступает во входную шину узла 26 режима. Это обусловлено тем. что после выполнения команды могут освободиться ячейки блока 12, использованные в качестве операндов, и их адреса могут быть записаны в стек 7 свободных адресов с входа 16 устройства.

Пока стек 7 пуст и не выполнены все предыдущие команды, узел 26 поддерживает в устройстве состояние ожидания, останавливая выработку тактовых сигналов в распределителе 25 и выдавая блокировку на второй выход. После записи адреса в стек 7 с входа 16 устройства узел 26 выдает разрешение на обработку очередной команды, в противном случае устанавливается режим откачки.

Другим отличием режима откачки является то, что в буферную память 4 команд выдается через коммутатор 9 адрес ячейки блока 12 из стека 5, в сформированной команде откачки содержится адрес ячейки блока 12, содерлсимое которой необходимо отослать в блок оперативной памяти, так как на этот адрес указывает счетчик 29 нижней границы в указателе 6 стека дешифрированных адресов.

Полностью заполненная буферная память 4 команд формирует блокировочный сигнал во входную шину узла режима. В результате устанавливается состояние ожидания до тех пор, пока буферная память 4 не сможет принять очередную команду.

Формула изобретения

Устройство для управления параллельным выполнением команд в стоховой электронной вычислительной машине, содержащее регистр операций, блок управления, блок адресации, блок буферной памяти, информационные вход и выход которого соединены соответственно с информационным входом и первым информационным выходом устройства, адресный вход - с выходом блока адресации, вход и выход регистра операций соединены соответственно с первым входом устройства и с первым управляющим входом блока управления, второй управляющий вход которого соединен с первым управляющим входом устройства, отличающееся тем, что, с целью повыщения производительности в работе, в него введены стек дешифрированных адресов, блок указателей стека дещифриро12

ванных адресов, стек свободных адресов, блок указателей стека свободных адресов, формирователь кода операции, коммутатор адресов, буферная память команд и блок восстаиовлепия, первые вход и выход которого подключены соответственно к второму управляющему входу устройства и к входу блока управления, вторые вход и выход блока восстановления подключены соответственно к

первому выходу блока управления и к первому входу блока указателей стека свободных адресов, второй выход блока управления соединен с управляющими входами регистра операций, стека дещифрированных адресов, с

управляющим выходом устройства, с первым входом блока указателей стека дещифрированных адресов и с вторым входом блока указателей стека свободных адресов, третий выход блока управления соединен с управляющими входами формирователя кода операции, коммутатора адресов, с третьим входом блока указателей стека свободных адресов, с вторым входом блока указателей стека дещифрировавиых адресов, вход блока управления соединен с управляющими выходами буферной памяти команд, блока указателей стека дешифрированных адресов, блока указателей стека свободных адресов, первый и второй выходы которого подключены соответственно к первому и второму адресным входам стека свободных адресов, вход и выход которого соединены соответственно с первым адресным входом устройства, с первым входом блока адресации и с первым входом коммутатора адресов, второй вход которого соединен с выходом стека дещифрированных адресов, выход коммутатора адресов соединен с первым входом буферной памяти команд и с входом стека дещифрированных

адресов, адресный вход которого подключен к выходу блока указателей стека дещифрированиых адресов, выход регистра операций соединен через формирователь кода операции с вторым входом буферной памяти команд, управляющий вход которого соединен с третьим управляющим входом устройства, выход буферной памяти команд соединен с выходом устройства и с вторым входом блока адресации, третий вход которого соединен с вторым

адресным входом устройства, выход блока адресации соединен с адресным выходом устройства, информационный вход устройства соединен с вторым информационным выходом устройства.

Источники информации, принятые во внимание при экспертизе:

1. Патент США № 3718912, кл. 340-172.5, 27.02.73.

2. Патент США № 3725876, кл. 340-172.5, 03.04.73.

19

20

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления параллельным выполнением команд в электронной вычислительной машине | 1982 |

|

SU1078429A1 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| Процессор микропрограмируемой ЭВМ | 1989 |

|

SU1697082A1 |

| Устройство для стековой адресации | 1979 |

|

SU783793A1 |

| Устройство для формирования команд | 1978 |

|

SU734686A1 |

| Процессор микропрограммируемой ЭВМ | 1979 |

|

SU860077A1 |

| Устройство для формирования команд с аппаратной организацией циклических программ | 1979 |

|

SU942018A1 |

| Устройство управления буферной памятью | 1978 |

|

SU737952A1 |

| Стековое запоминающее устройство | 1987 |

|

SU1737456A1 |

| Микропрограммное устройство для анализа программ | 1980 |

|

SU943729A1 |

21 22

Авторы

Даты

1977-04-30—Публикация

1976-01-21—Подача