Изобретение относится к области электросвязи и предлагает способ маршрутизации и трансляции блоков информации между системами либо приема/передачи информации, либо обработки данных. Изобретение может быть использовано при построении либо локальных, территориальных и глобальных сетей подвижной и фиксированной связи, либо распределенных вычислительных сред, а также служить основой в построении сетей связи общего пользования (FPLMTS/UMTS) или универсальной персональной связи (UPT).

2. Уровень техники

Известно [1], что методы передачи информации выполняют две функции:

I. Установление маршрута передачи;

II. Соединение тракта передачи.

Установление маршрута передачи осуществляют программными методами, реализованными в виде протоколов маршрутизации. Алгоритмы, заложенные в протоколы маршрутизации, описывают процесс вычисления наиболее предпочтительного маршрута на основании информации, содержащейся в таблицах маршрутизации и определяющей соответствие между физическими номерами канальных интерфейсов и логическими адресами отправителей/получателей. Известно, что протоколы маршрутизации разделяют на два класса по признаку наличия зависимости между пакетами передаваемого трафика. В протоколах маршрутизации первого класса, называемых маршрутно-зависимыми, присутствует зависимость между пакетами (они относятся к одному трафику), и вычисление маршрута осуществляется для первого пакета, а для второго и последующих пакетов предоставляется сквозной канал связи. При поступлении последнего пакета маршрут передачи сбрасывается. В протоколах маршрутизации другого класса, называемых маршрутно-независимыми, отсутствует зависимость между передаваемыми пакетами, и вычисление маршрута выполняется для каждого пакета независимо. Алгоритмы маршрутизации обоих классов, реализованные программными методами, состоят из последовательности команд, каждая из которых выполняется не менее чем за четыре такта (чтение, декодирование, исполнение, запись) [16].

Алгоритмы маршрутизации, реализованные аппаратным методом без использования программных методов и вычислительных процедур, на существующем уровне техники неизвестны.

Известно, что для соединения тракта передачи применяют контроллер, управляющий каналом связи по результатам, полученным от протоколов маршрутизации. При этом различают несколько способов соединения тракта передачи:

- коммутация каналов:

a) традиционная, когда паре отправитель-получатель выделяется канал связи с определенной скоростью передачи на все время вызова;

b) быстрая, когда паре отправитель-получатель выделяется канал связи с определенной скоростью передачи на время трансляции готового сообщения,

c) идеальная, то же, что и быстрая коммутация, но выделение канала связи с определенной скоростью передачи на время трансляции готового сообщения осуществляется без задержки;

- коммутация пакетов, для которой известны следующие признаки [2]:

1) с коллективной памятью, когда все входные и выходные контроллеры непосредственно соединены с общим запоминающим устройством, доступным для записи со всех входных контроллеров и чтения для всех выходных контроллеров. Данный метод использован в патентах:

[4] , в котором выходной порт определяется на основе стратегии поступления;

[5] , в котором выходной порт определяется на основе порядкового номера поступления;

2) с общей шиной, когда каждый входной порт синхронно в режиме разделения по времени передает в шину пакеты информации, и где каждый выходной порт подключен к шине адресным фильтром и принимает пакеты информации в выходной буфер. Данный метод использован в патентах:

[6], в котором выходной порт определяется системным процессором на основе стратегии доступа;

[7] , в котором выходной порт определяется системным процессором, а доступ к шине определяет центральный арбитр на основе приоритетов;

[8] , в котором выходной порт определяется системным процессором, а доступ к шине определяет распределенный арбитр на основе приоритетов;

[9] , в котором выходной порт определяется кольцевым арбитром на основе приоритетов;

[10], в котором выходной порт определяется кольцевым арбитром по стратегии поступления пакетов информации;

3) с пространственным разделением, когда каждый входной порт соединен с выходным портом через матрицу элементов переключения (ключей), среди которых различают:

a) с внешним управлением, когда сигнал управления на ключ поступает от внешнего контроллера. Данный метод использован в патентах:

[11] , в котором выходной порт определяется с помощью дельта-сети, и сигнал управления на матрицу ключей поступает от выходного контроллера;

[12] , в котором выходной порт определяется через информационную шину, и сигнал управления поступает от центрального контроллера;

b) с внутренним управлением, когда сигнал управления на ключ поступает от внутреннего контроллера. Данный метод использован в патентах:

[13] , где блок дистанционного управления последовательно вводит и выводит информацию о ключах, а контроллер включает/отключает локальную матрицу ключей;

[14], где контроллер (декодер адреса) в зависимости от адреса пакета информации, поступающего из входного буфера, подает сигнал управления на ключ;

[15], где контроллер (мультиплексор) по шине управления получает код управления.

Таким образом, известные методы передачи информации используют: коммутационное поле (в виде либо общей памяти, либо общей среды передачи, либо матрицы переключателей), входные и выходные интерфейсы, централизованный или децентрализованный управляющий контроллер, высокоскоростные шины для обмена информацией между ними, и выполняют программные методы вычисления маршрута передачи в соответствии с протоколами маршрутизации.

Аналогами, наиболее близкими к заявляемому изобретению, являются способы коммутации пакетов с пространственным разделением и внутренним управлением ключами ([13], [14], [15]).

Из [13] известно, что соединение/разъединение тракта передачи выполняет матрица переключателей, управляемая внутренним контроллером.

Соединение/разъединение тракта передачи обеспечивается передачей всем контроллерам управляющего пакета, который содержит номер внутреннего контроллера и номер переключателя. Данная схема обеспечивает включение только одного переключателя во всей матрице в единицу времени. Для установления тракта передачи, состоящего из N переключателей, требуется затратить N временных тактов для передачи N управляющих пакетов.

Из [14] известно, что соединение/разъединение тракта передачи выполняет коммутационный элемент, состоящий из ячейки памяти, блока сравнения и ключа. Из поступающего пакета информации анализируется единственный бит адреса, который определяется сигналом управления. В соответствии со значением данного бита вся последующая передача поступает из одного входа на один из двух выходов. Данная схема обеспечивает самомаршрутизацию передаваемых пакетов при соединении тракта передачи от одного входного до одного выходного канального интерфейса. Однако, данная схема для установления тракта передачи через N коммутационных элементов использует N временных тактов.

Из [15] известно, что соединение/разъединение тракта передачи выполняет 16-входовой мультиплексор, имеющий в своем составе 4-разрядный регистр для временного хранения состояния мультиплексора. Для соединения тракта передачи формируется управляющий фрейм (пакет), передаваемый от входного к выходному канальному интерфейсу через шину управления. Разъединение тракта передачи выполняется другим управляющим фреймом (пакетом). Матрица коммутации постоянно анализирует передаваемые по шине управления фреймы (пакеты), определяет моменты времени, когда требуется соединить или разъединить тракт передачи. Данная схема не позволяет реализовать соединение одного входного канального интерфейса с более чем одним выходным канальным интерфейсом за время передачи одного управляющего фрейма (пакета).

Известно, что передача информации при фиксированной связи осуществляется по адресу выходного интерфейса в виде кода идентификатора оконечной системы.

Однако, передача информации по сети связи выполняется по адресам пары отправитель-получатель, что вызывает накладные расходы на преобразование кодов идентификаторов в адреса пары отправитель-получатель.

Известно [3], что подсистема подвижной связи является дополнением системы фиксированной связи и включает: управляющий процессор с программным обеспечением (ПО) переадресации входящих или исходящих вызовов.

Известна [16] контекстно-адресуемая память (САМ) как ассоциативное запоминающее устройство, в котором признаком поиска данных является само содержание (либо часть содержания) данных.

3. Сущность изобретения

Сущность изобретения заключается в том, что способ двухтактной ассоциативной маршрутизации обеспечивает:

1. установление маршрута передачи от одного входного интерфейса до одного и более выходного интерфейса,

2. соединение тракта передачи для одновременной трансляции одного и более блока информации по установленным трактам передачи,

3. разъединение тракта передачи по окончании трансляции блока информации,

4. сбрасывание маршрута передачи по окончании трансляции потока (последовательности) блоков информации,

при фиксированной или подвижной связи,

при синхронной или асинхронной передаче,

при многоадресной передаче, соединении типа "точка-многоточие",

при этом под блоком информации понимается последовательная совокупность битов информации конечного размера, содержание которой в соответствии с указанным протоколом однозначно интерпретируется:

как сведения, идентифицирующие отправителя, - поле "Адрес источника",

как сведения, идентифицирующие получателя, - поле "Адрес приемника",

как сведения о наличии (отсутствии) смыслового содержания - поле "Длина данных",

как собственно смысловое содержание - поле "Данные",

как другая служебная информация.

Заявляемый технический результат использует

функцию входного интерфейса по программному выделению значения адреса из блока информации;

известное свойство САМ для однотактного поиска регистра соответствия ячейки САМ по значению адреса;

локальное преобразование каждого бита найденного регистра соответствия для установления соответствия между значениями адресов блока информации и физическими номерами выходных интерфейсов;

метод фиксации состояния коммутационного элемента матрицы, заключающийся в том, что один и более выходных канальных интерфейсов выдают сигнал подтверждения установления тракта передачи, а входной канальный интерфейс выдает сигнал фиксации тракта передачи на коммутационный элемент матрицы, обеспечивая установление маршрута и соединение тракта передачи;

входной канальный интерфейс начинает трансляцию блока информацию по соединенному тракту передачи после получения сигнала подтверждения установления тракта передачи из матрицы коммутационных элементов по каналу обратной связи.

Тракт передачи обеспечивает пространственную трансляцию блока информации от входного до одного и более выходных канальных интерфейсов.

По окончании передачи блока информации, используя свойство САМ, выполняется поиск выходного канального интерфейса и,

если транслированный блок информации был не последним, то входной интерфейс подает команду удаления нулевого адреса блока информации из САМ, передает сигнал на разъединение тракта передачи, и один и более выходных интерфейсов снимают сигнал подтверждения установления тракта передачи, а входной интерфейс подает сигнал фиксации тракта передачи на коммутационные элементы матрицы, разъединяя тракт передачи,

если транслированный блок информации был последним, то входной интерфейс подает команду удаления адреса блока информации из САМ, выходной интерфейс снимает сигнал подтверждения установления тракта передачи, а входной интерфейс подает сигнал фиксации тракта передачи на коммутационные элементы матрицы, разъединяя тракт передачи и сбрасывая маршрут передачи.

Таким образом, предложенный способ двухтактной ассоциативной маршрутизации не содержит вычислительных операций и устанавливает/сбрасывает маршрут и соединяет/разъединяет тракт передачи не более, чем за два такта. Способ двухтактной ассоциативной маршрутизации относится к классу зависимых методов передачи, соответствует как пакетной коммутации с пространственным разделением среды передачи, так и идеальной коммутации каналов, с внутренним управлением коммутационными элементами матрицы.

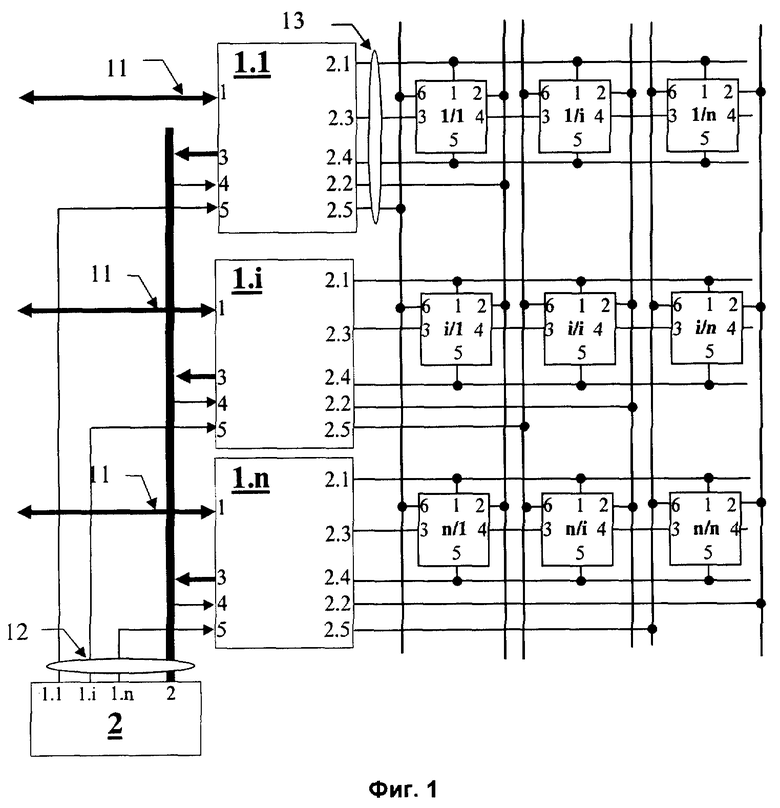

Функциональная схема реализации заявляемого технического результата представлена на фиг. 1 и основана на взаимодействии N канальных интерфейсов (1.1-1. n), ассоциативного блока 2 и матрицы коммутационных элементов (КЭ) 1/1-n/n, каждый из которых имеет каналы тракта передачи и обратной связи, при этом

каждый канальный интерфейс (см. Фиг.2) соединен с внешней сетью двунаправленным каналом передачи информации 11.i: выходом 1.1 с исходящей линией 111.i и входом 1.2 с входящей линией 112.i,

каждый канальный интерфейс (см. фиг.2) подключен к шине поиска 12: выходом 3.1 к 2k-разрядной шине адреса 125, где k находится в пределах от 3 до 8, входом 5 к линиям наличия адреса 124.1-124.n, выходом 3.2 и входом 4.3 к шине соединения/разъединения 123, а также к шине цикловой синхронизации 122 и шине тактовой синхронизации 121,

каждый канальный интерфейс 1.i (см. фиг.2) подключен к тракту передачи данных 13. i (см. фиг.3): входом 2.1 к входящей шине прямого канала 131.i, выходом 2.2 к исходящей шине прямого канала 132.i, входом 2.3 к входящей шине обратного канала 133. i, выходом 2.4 к исходящей шине обратного канала 134.i, а также выходом 2.5 к шине запроса на установление маршрута 135.i,

ассоциативный блок (см. фиг.5) подключен к шине поиска 12: входом 2.1 к шине адреса 125, входом 2.2 к шине соединения/разъединения 123, выходом 1.1 к линиям наличия адреса 124.n, выходом 1.2 к шине тактовой синхронизации 121 и выходом 1.3 к шине цикловой синхронизации 122.

Синхронизация процессов осуществляется сигналами тактовой и цикловой синхронизации:

сигнал цикловой синхронизации задает временной интервал доступа канального интерфейса с номером 1.1 к шине поиска 12, при этом скважность сигнала прямо пропорциональна числу N канальных интерфейсов,

сигнал тактовой синхронизации задает временные интервалы первого и второго тактов,

каждый канальный интерфейс 1.1-1.n последовательно получает равное время доступа к шине поиска 12.

Из внешней сети блок информации поступает по каналу 11 (линия 112.i) на вход 1.2 канального интерфейса с физическим номером 1.i (канальный интерфейс-отправитель). Последний выделяет из поступившего блока информации значения "Адрес источника", "Адрес приемника" и "Длина данных".

Для установления маршрута передачи поступившего блока информации выполняется следующая последовательность операций:

в первом такте

канальный интерфейс-отправитель 1. i, получив доступ к шине поиска 12, передает значение "Адрес источника" с выхода 3.1 по шине 125 на вход 2.1 ассоциативного блока 2 и сигнал "Запрос на соединение" с выхода 3.2 по шине 123 на вход 2.2 ассоциативного блока 2 и на входы 4.3 канальных интерфейсов 1.1-1.n,

ассоциативный блок 2, получив от канального интерфейса- отправителя 1.i "Адрес источника" и "Запрос на соединение", осуществляет контекстный поиск значения "Адрес источника" по содержимому САМ, и

в случае, если значения "Адрес источника" нет в САМ, то ассоциативный блок 2 произведет запись "Адреса источника" в САМ и установит бит соответствия между значением "Адрес источника" и номером канального интерфейса 1.i в значение логической "1", далее с выхода 1.1 на вход 5 канального интерфейса-отправителя 1.i по линии 124.i установит сигнал "Наличие адреса",

в случае, если значение "Адрес источника" присутствует в САМ и бит соответствия между значением "Адрес источника" и номером канального интерфейса 1.i равен логической "1", то ассоциативный блок 2 с выхода 1.1 на вход 5 канального интерфейса-отправителя 1.i по линии 124.i установит сигнал "Наличие адреса",

в случае, если значение "Адрес источника" присутствует в САМ, но логической "1" равен бит соответствия между значением "Адрес источника" и номером канального интерфейса 1.j, где j отличен от i, то ассоциативный блок 2 с выхода 1.1 на вход 5 канального интерфейса-отправителя 1.i по линии 124.i не установит сигнала "Наличие адреса", а канальный интерфейс-отправитель 1.i удалит блок информации, после чего перейдет в режим ожидания поступления нового блока информации из внешней сети по каналу 11 (линия 112.i):

во втором такте

канальный интерфейс-отправитель 1. i, получив доступ к шине поиска 12, передает значение "Адреса приемника" с выхода 3.1 по шине 125 на вход 2.1 ассоциативного блока 2 и "Запрос на соединение" с выхода 3.2 по шине 123 на вход 2.2 ассоциативного блока 2 и на входы 4.3 канальных интерфейсов 1.1-1. n,

ассоциативный блок 2, получив от канального интерфейса- отправителя 1.i "Адрес приемника" и "Запрос на соединение", осуществляет контекстный поиск значения "Адреса приемника" с содержимым ячеек САМ, и

в случае, если значения "Адрес приемника" нет в САМ, то ассоциативный блок 2 произведет запись "Адреса приемника" в САМ и установит бит соответствия между значением "Адрес приемника" и всеми номерами канальных интерфейсов 1.n в значение логической "1", далее с выхода 1.1 на входы 5 каждого канального интерфейса-получателя 1.1-1. n, по линии 124.i установит сигнал "Наличие адреса",

в случае, если значение "Адрес приемника" присутствует в САМ и значению "Адрес приемника" соответствует один и более номеров канальных интерфейсов 1. k (биты соответствия равны логической "1"), то ассоциативный блок 2 с выхода 1. k по линии 124.k на входы 5 только этих канальных интерфейсов-получателей 1.k установит сигнал "Наличие адреса",

канальные интерфейсы-получатели 1.j, для которых j равен k, получив на вход 4.3 "Запрос на соединение" и на вход 5 сигнал "Наличие адреса", передают с выхода 2.4 сигнал "Подтверждение установления канала" на вход j.4 канала обратной связи столбца КЭ матрицы, по тракту передачи 13 (исходящая шина обратного канала 134.j),

те канальные интерфейсы 1.j, для которых j отличен от k, вследствие чего не получившие на вход 5 сигнал "Наличие адреса", не передают с выхода 2.4 сигнал "Подтверждение установления канала" на вход j.4 канала обратной связи столбца КЭ матрицы по тракту передачи 13 (исходящая шина обратного канала 134.j),

канальный интерфейс-отправитель 1.i с выхода 2.5 подает сигнал "Фиксация тракта" на входы i.5 строки (i/1-i/n) КЭ матрицы,

каждый КЭ строки (i/1-i/n), получив на вход 5 сигнал "Фиксация тракта", запоминает значение сигнала "Подтверждение установления канала", поступившего на вход 6, передает сумму сигналов от КЭ со входа 4 (i/[n-1]) и (i/n) на выход 3, а КЭ (i/1) с выхода 3 передает сигнал "Подтверждение установления канала" на вход 2.3 канального интерфейса-отправителя 1.i, соединяя тем самым тракт передачи с выхода 2.2 канального интерфейса-отправителя 1.i до входа 2.1 одного и более канальных интерфейсов-получателей 1.k,

канальный интерфейс-отправитель 1.i, получив на вход 2.3 из канала обратной связи строки матрицы КЭ сигнал "Подтверждение установления канала", переходит в режим трансляции блока информации по установленному тракту передачи, а при отсутствии указанного сигнала - в режим ожидания нового цикла доступа к шине поиска.

Трансляция блока информации осуществляется по соединенному тракту передачи, для чего:

канальный интерфейс-отправитель 1.i сигналом "Блокировка фиксации" запрещает последующую передачу сигнала "Фиксация тракта" с выхода 2.4 и передает блок информации с выхода 2.2 на вход 1 всех КЭ строки (i/1-i/n),

КЭ строки (i/1-i/n), получив блок информации на вход 1, передает его или блокирует передачу на выход 2 по условию значения сигнала "Подтверждение установления канала",

блок информации с выхода 2 КЭ (i/j) поступает на вход 2.1 канального интерфейса-получателя 1.j,

отдельный канальный интерфейс-получатель 1.j, приняв на вход 2.1 блок информации, передает последний в канал связи 11 (исходящая линия 111.j).

Операции по сбрасыванию маршрута и тракта передачи после окончания трансляции блока информации выполняются в следующей последовательности:

в первом такте

канальный интерфейс-отправитель 1. i снимает сигнал "Блокировка фиксации",

если значение поля "Длина данных" равно нулю, то канальный интерфейс-отправитель 1. i, получив доступ к шине поиска, передает "Адрес источника" с выхода 3.1 по шине 125 на вход 2.1 ассоциативного блока, а с выхода 3.2 по шине 123 выставляет сигнал "Запрос на разъединение" на вход 2.2 ассоциативного блока 2 и на входы 4.3 канальных интерфейсов 1.1-1.n, иначе канальный интерфейс-отправитель 1.i ожидает начала второго такта,

ассоциативный блок 2, получив от канального интерфейса- отправителя 1.i "Адрес источника" и "Запрос на разъединение", удаляет "Адрес источника" из САМ

во втором такте

канальный интерфейс-отправитель 1. i, получив доступ к шине поиска 12, передает значение "Адрес приемника" с выхода 3.1 по шине 125 на вход 2.1 ассоциативного блока 2, сигнал "Запрос на разъединение" с выхода 3.2 по шине 123 на вход 2.2 ассоциативного блока 2 и на входы 4.3 канальных интерфейсов 1.1-1.n,

ассоциативный блок 2, получив от канального интерфейса- отправителя "Адрес приемника" и сигнал "Запрос на разъединение", осуществляет контекстный поиск соответствия значения "Адреса источника" одному и более физическим номерам канальных интерфейсов-получателей 1.j, где j отличен от i, передает с выхода 1.1 по линиям 124.j на входы 5 этих канальных интерфейсов-получателей 1.j сигнал "Наличие адреса",

канальные интерфейсы-получатели 1.j, получив на вход 5 сигнал "Наличие адреса" от ассоциативного блока 2 и на вход 4.3 сигнал "Запрос на разъединение" от канального интерфейса- отправителя 1.i, снимают с выхода 2.4 сигнал "Подтверждение установления канала" по входам j.4 каналов обратной связи КЭ столбцов матрицы,

канальный интерфейс-отправитель 1. i передает с выхода 2.5 сигнал "Фиксация тракта" на вход 5 каждого КЭ строки (i/1-i/n), благодаря чему все КЭ с номерами i/j, составлявшие тракт передачи, переводятся в состояние "выключено",

канальный интерфейс-отправитель 1.i после снятия сигнала "Подтверждение установления канала" со входа 2.3 переходит в режим ожидания нового блока информации.

5. Перечень фигур

Фиг. 1. Функциональная схема реализации способа двухтактной ассоциативной маршрутизации.

Фиг. 2. Схема i-го канального интерфейса.

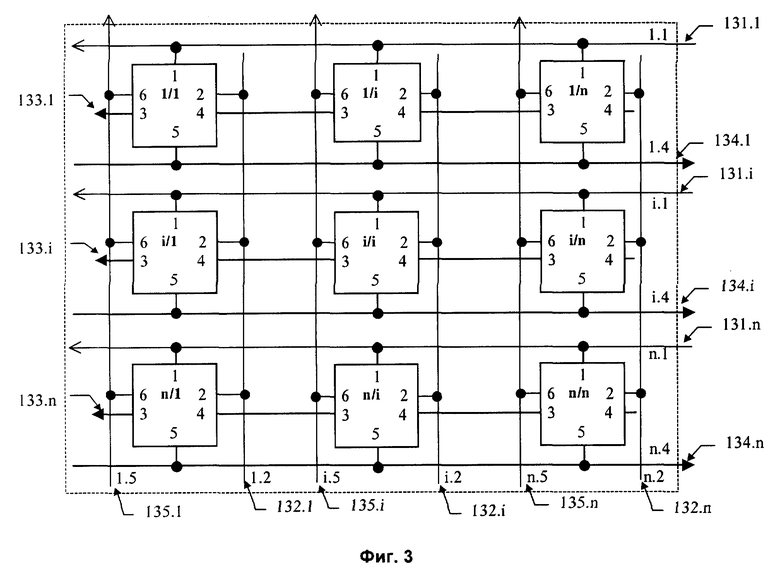

Фиг. 3. Схема матрицы коммутационных элементов.

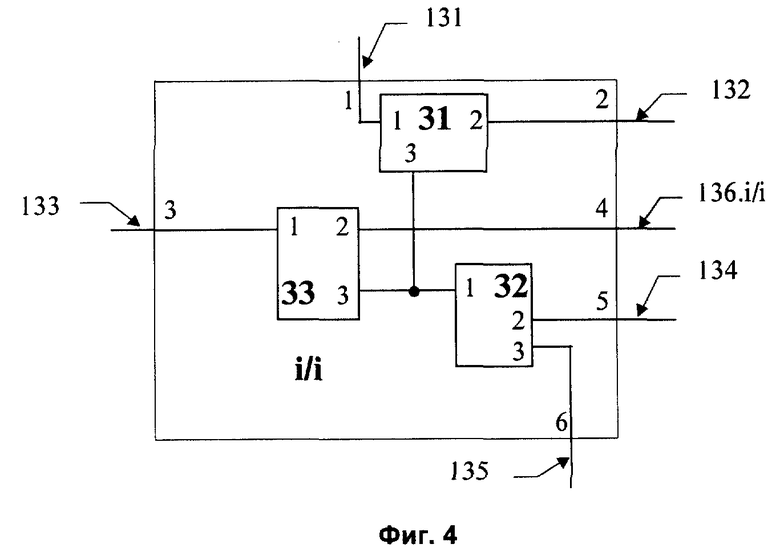

Фиг. 4. Схема коммутационного элемента.

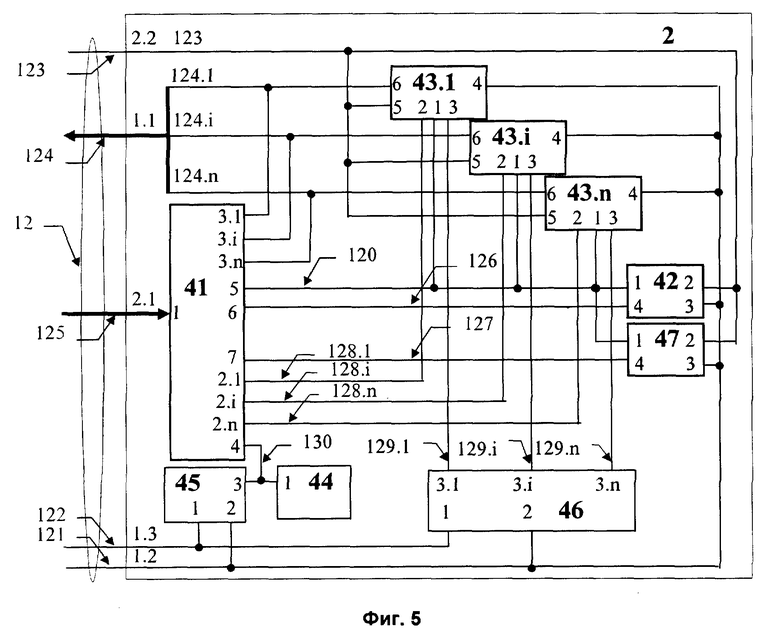

Фиг. 5. Схема ассоциативного блока.

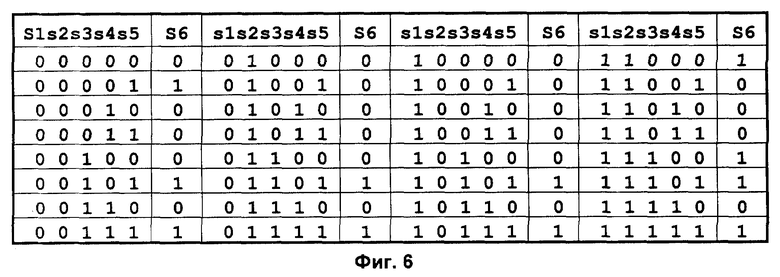

Фиг. 6. Таблица соответствия блока обработки 43.

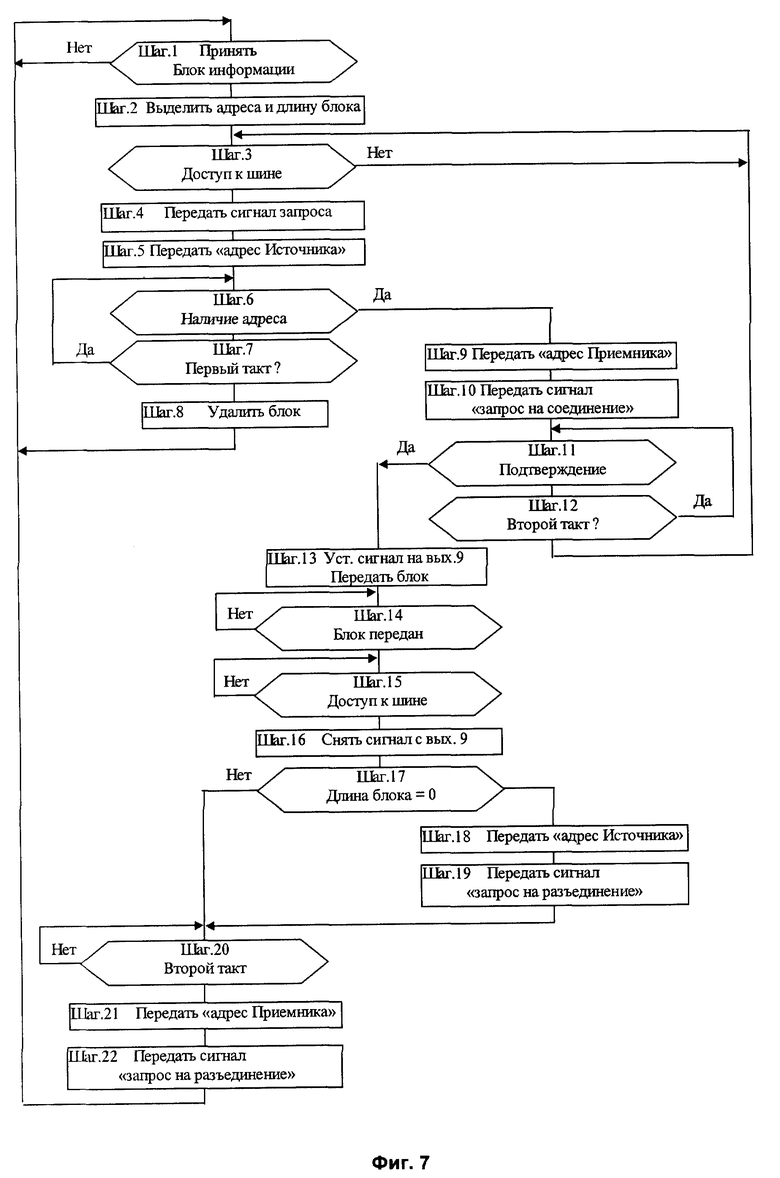

Фиг. 7. Блок-схема алгоритма канального контроллера.

6. Сведения, подтверждающие возможность осуществления изобретения

Канальный интерфейс (см. фиг. 2) выполняет функции:

1. приема и передачи блока информации;

2. выделения полей "Адрес источника", "Адрес приемника", "Длина данных";

3. установления и снятия сигнала "Запрос на установление канала";

4. установления и снятия сигнала "Подтверждение установления канала";

5. установления и снятия сигнала "Соединение/Разъединение";

6. установления и снятия сигнала "Блокировка фиксации";

7. подачи сигнала "Фиксация тракта";

8. приема сигнала "Наличие адреса";

9. вычисления временного интервала "доступ к шине",

и содержит: канальный контроллер 21, счетчик цикла 23, наборное поле 24, триггер 22 и элемент 2И 25.

При этом выход 3 счетчика цикла 23 соединен с входом 8 канального контроллера 21, входом 1 триггера 22 и входом 2 элемента 25.

При этом канальный контроллер 21 соединен: с триггером 22, входом 6 по линии наличия адреса 124.i со входом 4, выходом 5 по шине 123 со входом 3, с элементом 25, выходом 9, со входом 1.

При этом вход 7 канального контроллера 21 соединен по шине "синхронизация такта" 121 со входом 1 счетчика цикла 23.

При этом элемент 25 выходом 3 соединен шиной 135.i с матрицей коммутационных элементов.

При этом выход 3.2 каждого канального интерфейса соединен со входами 4.3 каждого из N канальных интерфейсов по шине "соединения/разъединения" 123.

Канальный контроллер 21.i, выполняет программу обработки в соответствии с алгоритмом (см. фиг. 7), при этом:

шаг 1: ждать поступления на вход 1 блока информации,

шаг 2: выделить из поступившего блока информации поля: "Адрес источника", "Адрес приемника" и "Длина данных",

шаг 3: ждать поступления на вход 8 сигнала "доступ к шине",

шаг 4: передать с выхода 5 сигнал "запрос на соединение",

шаг 5: передать с выхода 3 по шине 125 "Адрес источника",

шаг 6: если на входе 6 есть сигнал "Наличие адреса", то переход на шаг 9,

шаг 7: если на входе 7 есть сигнал "первый" такт, то переход на шаг 6,

шаг 8: удалить блок информации и переход на шаг 1,

шаг 9: передать с выхода 3 по шине 125 "Адрес приемника",

шаг 10: передать с выхода 5 сигнал "запрос на соединение",

шаг 11: если на входе 4 есть сигнал "Подтверждение установления канала", то переход на шаг 13,

шаг 12: если на входе 7 есть сигнал "второй" такт, то переход на шаг 11, иначе переход к шагу 3,

шаг 13: установить на выходе 9 сигнал "блокировка фиксации" и транслировать блок информации с выхода 2,

шаг 14: ждать окончания трансляции блока информации с выхода 2,

шаг 15: ждать появления на входе 8 сигнала "доступ к шине",

шаг 16: снять с выхода 9 сигнал "блокировка фиксации",

шаг 17: если длина блока информации равна нулю, то переход на шаг 17, иначе переход на шаг 19,

шаг 18: передать с выхода 3 "адрес источника".

шаг 19: передать с выхода 5 сигнал "запрос на разъединение",

шаг 20: ждать на входе 7 сигнал "второй" такт,

шаг 21: передать с выхода 3 "адрес приемника",

шаг 22: передать с выхода 5 сигнал "запрос на разъединение", переход на шаг 1.

С целью соединения тракта передачи канальный интерфейс с выхода 2.4 передает сигнал "Подтверждение установления канала", для чего:

принимая сигнал на вход 3 триггера 22, являющийся содержательным, и сигнал на вход 4, являющийся разрешительным, по переднему фронту сигнала на входе 1 триггера 22 фиксирует значение и передает последний на выход 2. Сигнал с выхода 2 поступает на вход 5 строки матрицы КЭ (i/1-i/n) как сигнал "Подтверждение установления канала".

Доступ канального интерфейса 1.n к шине 12 осуществляется при наличии сигнала "доступ к шине", для чего:

в счетчик цикла 23 сигналом "синхронизация цикла" с шины 122, подаваемым на вход 2, записывается значение наборного поля 24 по входу 4,

далее, принимая на вход 1 сигнал "синхронизация такта", по шине 121, счетчик цикла 23 уменьшает свое значение на 1,

наборное поле 24 устанавливает порядковый номер i-го канального интерфейса,

при появлении нулевого кода в счетчике цикла 23 с выхода 3 подается сигнал "доступ к шине" на вход 1 триггера 22, вход 8 канального контроллера 21 и вход 2 элемента 25,

задний фронт с выхода 3 элемента 25, при отсутствии с выхода 9 канального контроллера 21 сигнала "Блокировка фиксации", подается с выхода 2.5 по шине 135.i на вход 6 строки (i/1-i/n) КЭ как сигнал "Фиксация тракта".

Каждый КЭ матрицы (см. фиг. 3) выполняет функции:

1. фиксации сигнала "Подтверждение установления канала" сигналом "Фиксация тракта";

2. хранения состояния сигнала "Подтверждение установления канала";

3. включения или отключения ключа тракта передачи;

4. суммирования состояния сигналов "Подтверждение установления канала" от коммутационных элементов строки (n) и (n-1);

и состоит из матрицы размером N2 КЭ (1/1 - n/n),

при этом выход 3 КЭ 1/n соединен со входом 4 КЭ 1/(n-1),

при этом матрица КЭ формируется подключением:

входа 1 КЭ каждой строки 1/i-n/i к входящий шине прямого канала 131.i,

входа 3 КЭ первого столбца n/1 к входящий шине обратного канала 133.j,

выхода 2 КЭ каждого столбца j/1-j/n к исходящий шине прямого канала 132. j,

входа 5 КЭ каждого столбца j/1-j/n к исходящий шине обратного канала 134.j,

входа 6 каждого столбца КЭ j/1-j/n к исходящий шине 135.j.

Коммутационный элемент (см. фиг. 4), в свою очередь, является элементом коммутации с обратной связью и состоит из триггера 32, ключа тракта передачи 31 и логического элемента (ЛЭ) 2ИЛИ 33 обратного канала.

При этом выход 1 триггера 32 соединен со входом 3 ключа 31 и входом 3 ЛЭ 33.

Ключ 31 под воздействием управляющего сигнала на входе 3 обеспечивает передачу сигнала со входа 1 (шина 131) на выход 2 (шина 132), при этом ключ может иметь исполнение либо электронное, либо электромеханическое, либо оптическое в зависимости от вида сигнала на входе 1.

Триггер 32 выполняет фиксацию по входу 2 сигнала "Подтверждение установления канала", задним фронтом сигнала "Фиксация тракта" на входе 3. Хранение значения сигнала "Подтверждение установления канала" осуществляется до появления на входе 3 заднего фронта сигнала "Фиксация тракта".

Ассоциативный блок (см. фиг. 5) выполняет функции: 1. контекстного поиска значения "Адреса источника/приемника" по содержимому ячеек контекстно-адресуемой памяти (САМ),

2. записи или стирания битов соответствия в регистрах САМ,

3. передачи сигнала "Наличие адреса",

4. записи, чтения и удаления значений "Адрес источника" и "Адрес приемника" в/из ячейки САМ,

5. приема сигнала "Запрос на установление канала",

и состоит из блока (САМ) памяти 41, блока записи 42, блоков обработки 43.1-43. n, генератора тактов 44, делителя цикла 45, счетчика позиции 46 и блока удаления 47, линии удаления 126, линии записи 127, линии наличия адреса 120, линий обработки 128.1-128.n и линий позиции 129.1-129.n.

Блок памяти 41 соединен выходами 2.1-2.n по линиям 128.1 -128.n с выходами 2 блоков обработки 43.1-43. n, выходом 5 по шине 120 с входами 1 блоков обработки 43.1-43.n.

Блок записи 42 соединен входом 2 по шине 123 с входами 5 блоков обработки 43.1-43.n и входом 3 по шине 121 с входами 4 блоков обработки 43.1-43. n, входом 1 по шине 120 с выходом 5 САМ 41, выходом 4 по линии 126 со входом 6 САМ 41.

Блок удаления 47 соединен входом 2 по шине 123 с входами 5 блоков обработки 43.1-43.n и входом 3 по шине 121 с входами 4 блоков обработки 43.1-43. n, входом 1 по шине 120 с выходом 5 САМ 41, выходом 4 по линии 127 со входом 7 САМ 41.

Счетчик позиции 46 соединен выходами 3.1-3.n по линиями 129.1-129.n с входами 3 блоков обработки 43.1-43.n.

Генератор такта 44 соединен выходом 1 по линии 127 с входом 4 САМ 41 и входом 3 счетчика цикла 45.

Счетчик цикла 45 соединен выходом 1 по шине "синхронизация цикла" 122 с входом 1 счетчика позиции 46, выходом 2 по шине "синхронизация такта" 121 с входом 2 счетчика позиции 46 и входами 4 блоков обработки 43.1-43.n.

Генератор тактов 44 с выхода 1 подает сигнал синхронизации на вход 4 блока памяти 41, определяющий интервалы времени "поиск" и "запись" блока памяти 41, и на вход 3 счетчика циклов 45.

Счетчик циклов 45, получив на вход 3 сигнал синхронизации, подает на выход 1 сигнал "синхронизация тактов" ("первый" или "второй") и на выход 2 сигнал "синхронизация цикла" на шину 122 для канальных интерфейсов 1.1-1.n и счетчика позиции 46.

Блок анализа 42, получив на входы 2.1-2.n биты соответствия, выполняет операцию "ИЛИ" и выдает результат на выход 1.

САМ 41 содержит 2k контекстно адресуемых ячеек памяти с N - регистрами, где N - число канальных интерфейсов. САМ 41 в интервалы времени "поиск" и "запись", определяемые сигналом "синхронизация" на входе 4, выполняет:

в интервале времени "поиск" - чтение с входа 1 значения кода адреса,

сравнение поступившего значения с содержимым всех ячеек САМ памяти,

если адреса нет ни в одной ячейке памяти, результат сравнения отрицательный,

то полученный адрес записывается в первую свободную ячейку памяти,

чтение на выход 2 N - регистров ячейки САМ,

в интервале времени "запись" - с входа 3 значения битов соответствия записываются в N - регистров ячейки САМ.

Блок обработки 43.i является функциональным элементом и выполняет функцию, таблица соответствия которой приведена в таблице (фиг.6). При этом сигналы, поступающие на входы 1, 2, 3, 4, 5, представлены как s1, s2, s3, s4, s5, а выход 6 - s6, соответственно.

Счетчик позиции 46 является сдвиговым регистром, который, получив на вход 1 сигнал "синхронизация цикла", устанавливается в исходное состояние (логическая "1" на выходе 3.1). По сигналу "синхронизация такта", поступающего на вход 2, логическая "1" последовательно перемещается с выхода 3.1 на 3. i и далее до 3.n. В результате сигнал на выходах 3.i определяет номер активного канального интерфейса 1.1-1.n.

Ассоциативный блок 2 в начальный момент времени выполняет синхронизацию работы счетчика позиции 46 с работой канальных интерфейсов 1.1-1.n, для чего делитель цикла 45 выдает на шины 121 и 122 сигналы "синхронизация тактов" и "синхронизация циклов" соответственно. В результате счетчик позиции 46 на выходе 3.i выставляет сигнал "номер канального интерфейса" на вход 3 блоков обработки 43.1-43. n. Кроме того, блок памяти 41 устанавливается в исходное состояние, в результате чего каждая ячейка САМ содержит значение логического "0".

Ассоциативный блок 2, получив на вход 1 блока памяти 41 значение "Адрес", выполняет чтение из регистров ячейки САМ битов соответствия всех N канальных интерфейсов на выход 2.1-2.n. Блоки обработки 43.1-43.n, одновременно получив на вход 2 бит соответствия, на вход 3 бит позиции, на вход 5 сигнал "запрос на соединение/разъединение", на вход 1 результат анализа, на вход 4 сигнал "первый" или "второй" такт, выполняют обработку в соответствии с таблицей (фиг. 6) и передают результат обработки на выход 6. Биты соответствия с выхода 6 блоков обработки 43.1-43.n поступают на входы 3.1-3.n блока памяти 41 и по линиям 124.n на входы 5 канальных интерфейсов 1.1-1.n.

Блок памяти 41, получив на входы 3.1-3.n биты соответствия, выполняет их запись в регистры ячейки САМ.

В течение времени "первого" такта ассоциативный блок 2 получает от канального интерфейса 1.i "Адрес источника", а во "втором" такте - "Адрес приемника".

Библиография

1. Бюллетень ТИИЭР, том 66 за 1978 год.

2. Инженерная энциклопедия "Технологии Электронных Коммуникаций" (ТЭК) "АТМ: технология высокоскоростных сетей, А. Н.Назаров, М.В.Симонов, ЭКО- ТРЕЙНДЗ, Москва, 1998.

3. ММКТТ, том VI, выпуск VI.12, рекомендации Q1000-Q1032.

4. Патент US N 5475383 от 12.12.1995 г.

5. Патент US N 5509006 от 16.04.1996 г.

6. Патент US N 5592622 от 7.01.97 г.

7. Патент US N 5561669 от 1.10.96 г.

8. Патент US N 5459840 от 17.10.95 г.

9. Патент US N 5537403 от 16.07.96 г.

10. Патент US N 5642349 от 24.06.1997 г.

11. Патент US N Re. 34528 от 1.02.1994 г.

12. Патент US N 5307342 от 26.04.1994 г.

13. Патент EP 0488673 A2 от 27.11.1991 г.

14. Патент US N 5396491 от 7.03.1995 г.

15. Патент US N 5430442 от 4.06.1995 г.

16. Клингман Э. Проектирование микропроцессорных систем.-М.: Мир, 1980.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ СИНХРОННОЙ АССОЦИАТИВНОЙ МАРШРУТИЗАЦИИ/КОММУТАЦИИ | 2009 |

|

RU2447594C2 |

| Способ распределения информационных потоков в пакетной радиосети и управляемый модульный маршрутизатор для его осуществления | 2020 |

|

RU2748574C1 |

| СПОСОБ ПЕРЕДАЧИ БЛОКОВ ДАННЫХ С ДИНАМИЧЕСКОЙ ГРАНИЦЕЙ | 2009 |

|

RU2431234C2 |

| СПОСОБ ЗАЩИТЫ ПЕРСОНАЛЬНОГО НОМЕРА ПОЛЬЗОВАТЕЛЯ | 2010 |

|

RU2435325C1 |

| СИСТЕМА РАДИОСВЯЗИ С ПОДВИЖНЫМИ ОБЪЕКТАМИ С ПРИМЕНЕНИЕМ РАДИОФОТОННЫХ ЭЛЕМЕНТОВ | 2018 |

|

RU2686456C1 |

| МАЛОГАБАРИТНАЯ НЕОБСЛУЖИВАЕМАЯ АППАРАТУРА ПЕРЕДАЧИ ДАННЫХ | 2018 |

|

RU2684568C1 |

| Способ маршрутизации трафика, имеющего приоритетный класс в сети связи, включающий двух и более операторов | 2016 |

|

RU2631144C1 |

| БЕРЕГОВОЙ УЗЕЛ СВЯЗИ ФЛОТА | 2019 |

|

RU2718608C1 |

| СПОСОБ ПЕРЕДАЧИ ДАННЫХ С ЗАДАННЫМ КАЧЕСТВОМ В СИСТЕМЕ СВЯЗИ, НЕ ОБЕСПЕЧИВАЮЩЕЙ СКВОЗНОЙ СОСТАВНОЙ ИНФОРМАЦИОННЫЙ КАНАЛ В ЛЮБОЙ МОМЕНТ ВРЕМЕНИ | 2020 |

|

RU2734021C1 |

| СПОСОБ ДИНАМИЧЕСКОЙ МАРШРУТИЗАЦИИ ТРАФИКА В СЕТИ СВЯЗИ | 2020 |

|

RU2737702C1 |

Способ двухтактной ассоциативной маршрутизации предназначен для передачи информации от отправителя до одного и более получателей и предлагает способ маршрутизации и трансляции блоков информации между системами либо приема/передачи информации, либо обработки данных. Изобретение может быть использовано при построении либо локальных, территориальных и глобальных сетей подвижной и фиксированной связи, либо распределенных вычислительных сред, а также служить основой в построении сетей связи общего пользования (FP МТ / МТ) или универсальной персональной связи (РТ). Технический результат заключается в исключении вычислительных операций при установлении соединений. Установление/сбрасывание маршрута передачи и соединение/разъединение тракта передачи выполняют не более чем за два такта, с использованием ассоциативного поиска, локального преобразования битов соответствия логического адреса и физического номера канального интерфейса и передачи подтверждения установления тракта передачи от выходного к входному канальному интерфейсу но каналу обратной связи матрицы коммутационных элементов. 1 з.п.ф-лы, 7 ил.

| US 5450402 A, 12.09.95 | |||

| US 5568475 A, 11.07.96 | |||

| US 5436890 A, 25.07.95 | |||

| US 5392281 A, 21.02.95 | |||

| DE 3919144 C1, 05.12.90 | |||

| Устройство для секционного преимущественно эшелонированного агрегатирования | 1975 |

|

SU683657A1 |

| ВЗВЕШИВАЮЩАЯ СЕКЦИЯ ДЛЯ КОНВЕЙЕРОВ С ХОДОВЫМИ РОЛИКАМИ | 2005 |

|

RU2293292C1 |

| УСТАНОВКА ДЛЯ ПЕРЕРАБОТКИ ПТИЧЬЕГО ПОМЕТА | 2019 |

|

RU2707127C1 |

Авторы

Даты

1999-10-20—Публикация

1999-01-13—Подача