1. Область техники

Изобретение относится к области электросвязи и предлагает способ установления и изменения маршрута передачи, соединение или разъединение тракта передачи и сброс маршрута передачи с целью переноса блока информации между системами либо приема/передачи информации, либо обработки данных.

Изобретение может быть использовано при построении либо локальных, территориальных или глобальных сетей подвижной и фиксированной связи, либо распределенных вычислительных сред.

2. Уровень техники

Известно [1], что методы переноса информации выполняют две функции:

I. Установление, изменение, сброс маршрута передачи;

II. Соединение или разъединение тракта передачи.

Установление маршрута передачи осуществляют алгоритмы маршрутизации, вычисляющие соответствие между номером канального порта и адресами отправителя и получателя и сохраняющие вычисленное соответствие в таблице маршрута. Алгоритмы маршрутизации реализуют либо программным, либо аппаратным методами. Успешное вычисление маршрута передачи включает выполнение за установленное время и с заданными параметрами. Идентичность информации в таблице маршрутов заданного сегмента сети является обязательным условием успешного вычисления маршрута. Поддержку идентичности информации в таблицах маршрутов обеспечивают протоколы маршрутизации.

Известно [20], что алгоритмы маршрутизации имеют множество отличительных признаков, одним из которых является наличие зависимости между пакетами, то есть они относятся к одному трафику. При наличии зависимости между пакетами вычисление маршрута выполняют маршрутно-зависимым способом, а именно маршрут вычисляют только для первого пакета, а второй и последующие пакеты передают по удерживаемому тракту передачи. Поступление последнего пакета или отсутствие трафика, установленное время, приводит к сбрасыванию маршрута передачи. При отсутствии зависимости между пакетами маршрут вычисляют для каждого пакета, то есть маршрутно-независимым способом.

Известно [17], что реализация алгоритма маршрутизации программным методом для обработки маршрутно-зависимого и маршрутно-независимого трафика использует последовательность команд процессора, каждая из которых выполняется не менее чем за четыре такта частоты синхронизации (чтение, декодирование, исполнение, запись).

Известно [18], что реализация алгоритма маршрутизации аппаратным методом для обработки маршрутно-зависимого трафика использует две операций, исполняющиеся за два такта частоты синхронизации каждая.

Известно [2], что алгоритмы маршрутизации передают полученные результаты вычислений канальным контроллерам для соединения/разъединения тракта передачи.

При этом различают следующие способы соединения тракта передачи:

- коммутация каналов:

a) традиционная, когда паре отправитель-получатель выделяют канал связи с определенной скоростью передачи на все время вызова;

b) быстрая, когда паре отправитель-получатель выделяют канал связи с определенной полосой пропускания на время трансляции готового сообщения,

c) идеальная, то же, что и быстрая коммутация, но выделение канала связи с определенной полосой пропускания на время трансляции готового сообщения осуществляют без задержки;

- коммутация пакетов:

a) с коллективной памятью, когда все входные и выходные порты соединены с общим запоминающим устройством непосредственно, при этом для записи и чтения доступны все выходных порты. Данный метод использован в патентах, где: [3] выходной порт определяют центральным контроллером, а доступ к памяти определяют на основе правила поступления;

[4] выходной порт определяют центральным контроллером, а доступ к памяти определяют распределенным контроллером на основе правила поступления

порядкового номера поступления;

b) с общей шиной, когда каждый входной порт синхронно в режиме разделения по времени передает в шину пакеты (ячейки) и где каждый выходной порт подключен к шине адресным фильтром принимает пакеты (ячейки) в выходной буфер. Данный метод использован в патентах,

где [5] выходной порт определяют системным процессором, а доступ к шине определяют на основе правила доступа;

[6] выходной порт определяют канальным процессором, а доступ к шине определяют на основе приоритетов центральным арбитром;

[7] выходной порт определяют системным процессором, а доступ к шине определяют на основе приоритетов распределенным арбитром;

[8] выходной порт определяют кольцевым арбитром, а доступ к шине определяют на основе приоритетов;

[9] выходной порт определяют кольцевым арбитром, а доступ к шине определяют на основе правила поступления пакетов;

с) с пространственным разделением, когда каждый входной интерфейс соединен с выходным интерфейсом через матрицу элементов переключения (ключей), среди которых различают:

1) с внешним управлением, когда сигнал управления поступает на элемент памяти ключа от внешнего контроллера.

Данный метод использован в патентах, где:

[10] выходной порт определяют с помощью дельта-сети, и сигнал управления на матрицу ключей поступает с распределенного контроллера;

[11] выходной порт определяют с помощью кольцевой сети, и сигнал управления на матрицу ключей поступает от центрального контроллера;

[12] выходной порт определяют через информационную шину, и сигнал управления поступает на матрицу ключей от центрального контроллера по шине данных;

[13] выходной порт определяют через информационную шину, и сигнал управления поступает на матрицу ключей от центрального контроллера по шине адреса;

2) с внутренним управлением, когда сигнал управления поступает на элемент памяти ключ от внутреннего контроллера. Данный метод использован в патентах,

где [14] внутренний контроллер (регистр) получает информацию о состоянии ключей и включает или отключает ключи локальной матрицы;

[15] внутренний контроллер (декодер адреса) в зависимости от адреса пакета информации, поступающего из входного порта, подает сигнал управления на ключ;

[16] внутренний контроллер (мультиплексор) по шине управления получает код управления ключом;

[18] внутренний контроллер (сумматор) суммирует сигналы, поступающие от входного порта и регистра соответствия, и подает суммарный сигнал на входной порт по каналу обратной связи коммутационного элемента и на управление ключом.

Таким образом, известные методы передачи информации состоят из входных и выходных портов, централизованных или децентрализованных контроллеров и коммутационного поля (в виде общей памяти, или общей шины, или матрицы ключей) и используют программные и аппаратные методы для вычисления маршрута передачи.

Известно [19] запоминающее устройство, из которого осуществляют выборку по содержимому, именуемому как контекстно-адресуемая память (САМ). Результатом выборки является признак наличия искомого содержимого (либо его части) в памяти и адрес его хранения.

Аналоги наиболее близки к заявляемому изобретению, являются методами передачи информации с коммутацией пакетов с пространственным разделением и внешним управлением ключами ([10] [12] [13]).

Из [11] известно, что

маршрутизирующий коммутатор, содержащий множество входных и выходных портов для установления маршрута передачи, посылает данные СОСТОЯНИЕ каждому входному буферу и одновременно каждому незанятому буферу вывода, а также посылает запрос маршрутизации, идентифицируя незанятый буфер вывода, через соответствующую шину.

Однако данная схема для установления маршрута передачи использует более 5 временных тактов.

Из [12] известно, что

сетевой коммутатор для установления маршрута передачи между множеством входных и выходных портов использует не менее N*N/M+2 временных тактов, где N - размер матрицы элементов коммутации, а М число портов.

Из [13] известно, что

маршрутизирующий коммутатор, содержащий множество входных и выходных портов для установления маршрута передачи, использует вычислительное устройство.

Однако данная схема для установления маршрута передачи использует более чем N*4 временных тактов, где N - число операций в алгоритме установления маршрута передачи.

3. Сущность изобретения

Сущность изобретения заключается в том, что способ синхронной ассоциативной маршрутизации/коммутации за минимальное число тактов частоты синхронизации обеспечивает за 2 такта установление маршрута передачи, за 2 такта - соединение тракта и за 1 такт - разъединение тракта при формировании тракта передачи, для чего использует команды управления

при установлении маршрута передачи:

- «открыть» маршрут,

- «фиксировать» маршрут,

- «дополнить» маршрут,

- «закрыть» маршрут,

При формировании тракта передачи:

- «соединить» тракт,

- «разъединить» тракт,

при фиксированной и подвижной связи,

при синхронной и асинхронной передаче,

при одноадресной передаче, соединение типа «точка-точка»,

при многоадресной передаче, соединение типа «точка-многоточие»,

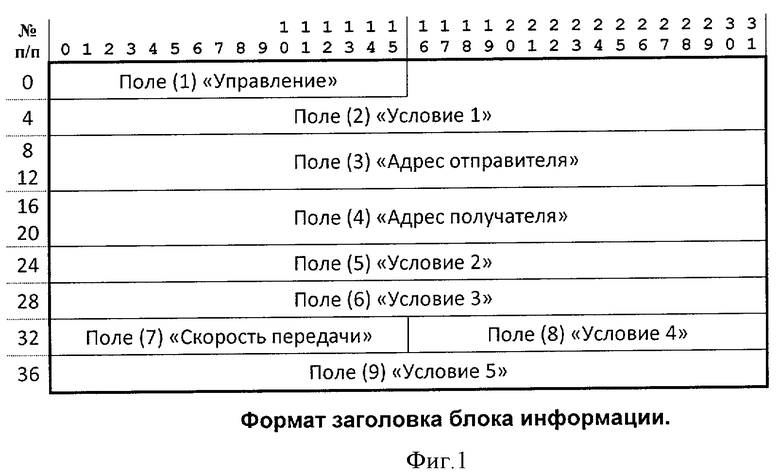

при этом под заголовком блока информации (фиг.1) принимается совокупность битов конечного размера, значение которых однозначно интерпретируются как сведения, идентифицирующие:

«Управление» - поле (1), принимающее значения «открыть», «фиксировать», «дополнить», «закрыть» маршрут передачи и «соединить» или «разъединить» тракт передачи, а также имеющее дополнительные значения,

«Адрес отправителя» - поле (3),

«Адрес получателя» - поле (4),

«Скорость передачи» - поле (7), принимающее значения от BRmin до BRmax,

«условие 1» - поле (2), «условие 2» - поле (5), «условие 3» - поле (6),

«условие 4» - поле (8), «условие 5» - поле (9).

Заявляемый технический результат включает N портов, коммутационных элементов, объединенные в матрицу коммутации размером N×N, и арбитр, используя:

функцию арбитра по последовательному предоставлению каждому порту равного времени доступа к шине;

функции коммутационных элементов по хранению состояния «включено» или «выключено» и соединению или разъединению тракта передачи;

функции порта по приему из внешней сети блока информации и выделению из заголовка блока информации значения полей «Адрес отправителя», «Адрес получателя», «Управление» и параметр условия «Скорость передачи»;

известное свойство контекстно-адресуемой памяти (САМ) [19] по поиску содержимого и выдачи признака наличия содержимого.

Заявляемый технический результат обеспечивает,

что каждый порт принимает из внешней сети блоки информации и выделяет из заголовка блока информации сведения, однозначно интерпретируемые как адреса отправителя и получателя информации, команда управления и параметр условия,

каждый порт определяет момент времени доступа к шине по коду,

получив доступ к шине, порту присваивается (i) номер порта,

каждый коммутационный элемент, объединенный в матрицу размером n×n, имеет ячейку памяти, где хранит состояние “включено” или “выключено”,

при этом в течение первого такта

порт (i) по шине передает в порты (1÷n, где n≠i) сведения, однозначно интерпретируемые как адреса отправителя и получателя информации, команда управления и параметр условия, подает сигнал «установить тракт»,

коммутационный элемент, объединенный в матрицу размером n×n, принимая сигнал «установить тракт», переходит в состояние «выключено», разъединяя тракт передачи,

каждый из портов (1÷n, где n≠i) принимает сведения, однозначно интерпретируемые как адреса отправителя и получателя информации, команда управления и параметр условия, осуществляет поиск адреса отправителя и получателя в контекстно-адресуемой памяти, проверяет условие на истинность значения,

в течение второго такта

порт (i) передает блок информации, подает сигнал «установить тракт», принимает сигнал «подтверждение»,

каждый из портов (1÷n, где n≠i) принимает сигнал из контекстно-адресуемой памяти, подает сигнал в контекстно-адресуемую память, получает результат проверки истинности условия, выполняет команду управления, передает сигнал «фиксировать тракт», принимает блок информации,

каждый коммутационный элемент, получивший сигнал «установить тракт» и сигнал «фиксировать тракт», меняет состояние на "включено", соединяя тракт передачи, и подает сигнал «подтверждение» в порт (i).

Когда команда управления, принимая значение «открыть маршрут», в течение второго такта,

порт (i) подает сигнал «установить тракт»,

каждый из портов (1÷n, где n≠i),

проверяет отсутствие в контекстно-адресуемой памяти значение адресов отправителя и получателя,

проверяет равенство параметра условия значению истина,

подает сигнал запись в контекстно-адресуемую память для записи значения адреса отправителя и получателя информации,

подает сигнал «фиксировать тракт»,

порт (i), получив сигнал «подтверждение», передает блок информации через коммутационный элемент, объединенный в матрицу n×n, в один и более портов (1÷n, где n≠i), а каждый из портов (1÷n, где n≠i), принимает блок информации.

Когда команда управления имеет значение «фиксировать маршрут», в течение второго такта,

порт (i) подает сигнал «установить тракт»,

каждый из портов (1÷n, где n≠i),

проверяет наличие в контекстно-адресуемой памяти значение адресов отправителя и получателя,

проверяет равенство параметра условия значению истина,

подает сигнал «фиксировать тракт»,

порт (i), получив сигнал «подтверждение», передает блок информации через коммутационный элемент, объединенный в матрицу n×n, в один и более портов (1÷n, где n≠i), а каждый из портов (1÷n, где n≠i) принимает блок информации.

Когда команда управления имеет значение «дополнить маршрут», в течение второго такта,

порт (i) подает сигнал «установить тракт»,

каждый из портов (1÷n, где n≠i)

проверяет наличие в контекстно-адресуемой памяти значение адресов отправителя и получателя,

проверяет равенство параметра условия значению истина,

подает сигнал запись в контекстно-адресуемую память для записи значения адреса отправителя и получателя информации,

подает сигнал «фиксировать тракт»,

порт (i), получив сигнал «подтверждение», передает блок информации через коммутационный элемент, объединенный в матрицу n×n, в один и более портов (1÷n, где n≠i), а каждый из портов (1÷n, где n≠i) принимает блок информации.

Когда команда управления имеет значение «закрыть маршрут», в течение второго такта,

порт (i) подает сигнал «установить тракт»,

каждый из портов (1÷n, где n≠i)

проверяет наличие в контекстно-адресуемой памяти значение адресов отправителя и получателя,

проверяет равенство параметра условия значению истина,

подает сигнал «фиксировать тракт»,

подает сигнал удалить в контекстно-адресуемую память для стирания значения адреса отправителя и получателя информации,

порт (i), получив сигнал «подтверждение», передает блок информации через коммутационный элемент, объединенный в матрицу n×n, в один и более портов (1÷n, где n≠i), а каждый из портов (1÷n, где n≠i) принимает блок информации.

Когда команда управления имеет значение «соединить тракт», в течение второго такта,

порт (i) подает сигнал «установить тракт»,

каждый из портов (1÷n, где n≠i)

проверяет наличие в контекстно-адресуемой памяти значение адресов отправителя и получателя,

подает сигнал «фиксировать тракт»,

порт (i), получив сигнал «подтверждение», передает блок информации через коммутационный элемент, объединенный в матрицу n×n, в один и более портов (1÷n, где n≠i), а каждый из портов (1÷n, где n≠i) принимает блок информации.

Когда команда управления имеет значение «разъединить тракт», в течение первого такта,

порт (i) подает сигнал «установить тракт»,

каждый коммутационный элемент, имеющий состояние "включено", получивший сигнал «установить тракт», переходит в состояние "выключено", разъединяя тракт передачи,

В случае, когда порт (i) не получил сигнал «подтверждение», он удаляет блок информации.

Заявляемый результат предусматривает возможность использования многоразрядных линий в коммутационном элементе, формирующих тракт передачи.

Параметром условия служит поле, однозначно интерпретируемое как скорость передачи. Условием считают, что сумма значений текущей скорости передачи порта и принятой скорости передачи меньше максимально возможного значения скорости порта.

Значение текущей скорости передачи порта увеличивается на значение принятой скорости передачи по команде «фиксировать маршрут» и «дополнить маршрут». Значение текущей скорости передачи порта уменьшается на значение принятой скорости передачи по команде «закрыть маршрут».

На фиг.1 представлен формат заголовка передаваемого блока включающий: поле (1) - «Управление», поле (2) - «Условие 1», поле (3) - «Адрес получателя», поле (4) - «Адрес отправителя», поле (5) - «Условие 2», поле (6) - «Условие 3», поле (7) - «Скорость передачи», поле (8) - «Условие 4», поле (9) - «Условие 5».

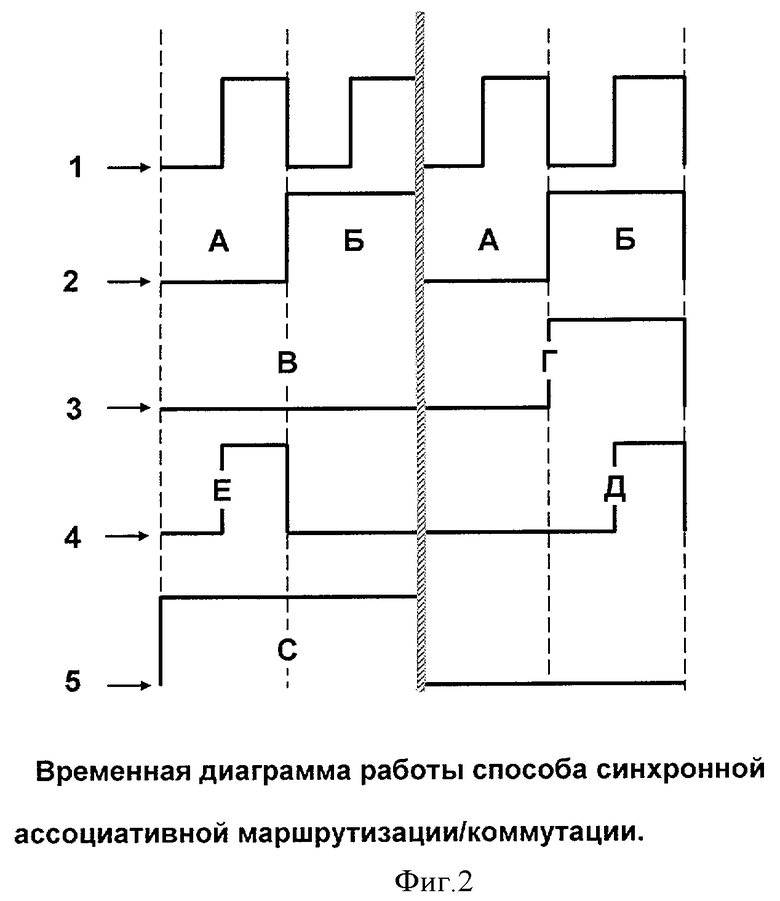

На фиг.2 представлена временная диаграмма работы заявляемого технического результата,

где диаграмма 1, сигнал частотной синхронизации,

диаграмма 2, сигнал частоты цикла работы (тактовая синхронизация), где первый цикл - поиск (позиции А), второй цикл - исполнение (позиция Б),

диаграмма 3 показывает выполнение команды "закрыть маршрут" (позиция В), "открыть маршрут", "фиксировать маршрут", "добавить маршрут" (позиция Г),

диаграмма 4 показывает выполнение команды «соединение тракта» (позиция Д), и «разъединение тракта» (позиция Е),

диаграмма 5, сигнал цикловой синхронизации i - порта (позиция С).

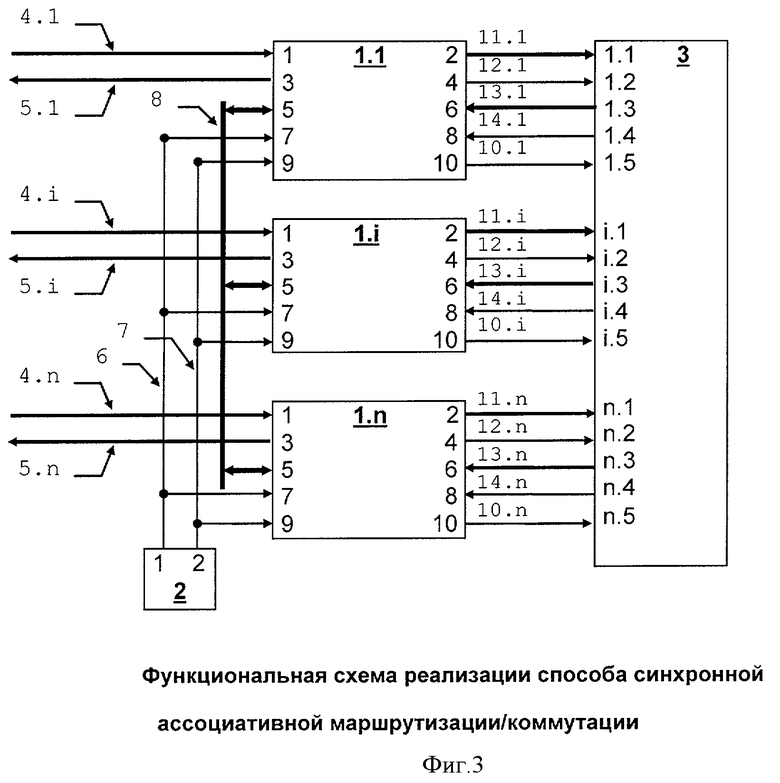

Функциональная схема заявляемого технического результата представлена на фиг.3 и основана на взаимодействии N портов (1.1÷1.n), арбитра 2 и матрицы коммутационных элементов 3,

при этом каждый порт 1.1÷1.n входом 1 линией 4.i и выходом 3 линией 5.i соединен с внешней сетью приема/передачи блоков информации соответственно,

каждый порт 1.1÷1.n выходом 2 линией 11.1÷11.n соединен с входом 1.1÷n.1 матрицы коммутационных элементов 3,

каждый порт 1.1÷1.n выходом 4 линией 12.1÷12.n соединен с входом 1.2÷n.2 матрицы коммутационных элементов 3,

каждый порт 1.1÷1.n выходом 10 линией 10.1÷10.n соединен с входом 1.5÷n.5 матрицы коммутационных элементов 3,

каждый порт 1.1÷1.n входом 6 линией 13.1÷13.n соединен с выходом 1.3÷n.3 матрицы коммутационных элементов 3,

каждый порт 1.1÷1.n входом 8 линией 14.1÷14.n соединен с выходом 1.4÷n.4 матрицы коммутационных элементов 3,

каждый порт 1.1÷1.n двунаправленным входом/выходом 5 соединен посредством (2m) - разрядной шиной 8, где m находится в пределах от 1 до 8, с двунаправленным входом/выходом 5 каждого порта 1.1÷1.n,

каждый порт 1.1÷1.n входом 7 соединен шиной 6 с выходом 1 арбитра 2,

каждый порт 1.1÷1.n входом 9 соединен шиной 7 с выходом 2 арбитра 2.

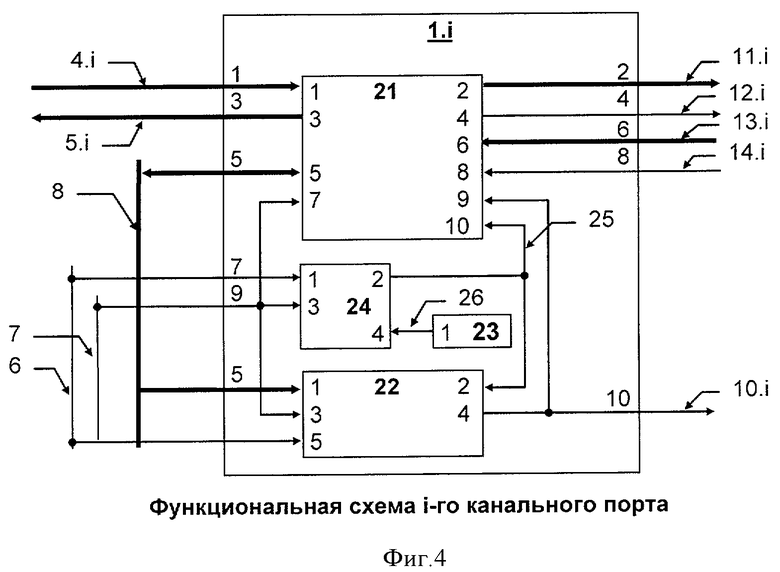

Функциональная схема порта (1.1÷1.n), представленная на фиг.4, содержит контроллеры 21 и 24, ассоциативный блок 22 и блок номер цикла 23,

при этом вход 7 контроллера 21, вход 3 контроллера 24 и вход 3 ассоциативного блок 22 соединены шиной 7,

вход 1 контроллера 24 и вход 5 ассоциативного блок 22 соединены шиной 6,

двунаправленный вход/выход 5 контроллера 21 и вход 1 ассоциативного блок 22 соединены с шиной 8,

выход 9 контроллера 21 и вход 6 ассоциативного блок 22 соединены линией 25,

выход 4 ассоциативного блок 22 и вход 10 контроллера 21 соединены линией 10.i,

выход 2 контроллер 24, вход 11 контроллера 21 и вход 2 ассоциативного блок 22 соединены линией 26,

выход 1 блока номер цикла 23 и вход 4 контроллер 24 соединены линией 27.

Синхронизацию выполнения операций осуществляют сигналы частотной (диаграмма 1) и цикловой синхронизации (диаграмма 5), которые арбитр 2 по шинам 6 и 7 передает каждому канальному порту 1.1÷1.n,

сигнал цикловой синхронизации по шине 7 синхронизирует доступ 1.1÷1.n портов к шине 8,

номер интервала времени, в течение которого каждый порт получает доступ к шине 8, определяется кодом, записанным в блок 23 каждого порта 1.1÷1.n,

скважность сигнала цикловой синхронизации прямо пропорциональна числу n портов,

каждый порт 1.1÷1.n последовательно получает равное время доступа к шине 8.

Способ синхронной ассоциативной маршрутизации/коммутации с целью передачи блока информации с одного порта на один и более портов устанавливает маршрут и формирует тракт передачи,

для чего порт 1.1÷1.n с входа 1 по линии 4. i принимает из внешней сети блок информации и выделяет из заголовка поля «Адрес отправителя», «Адрес получателя», «Команда управления» и «Скорость передачи»,

порт 1.i, где 1<=i<=n, ожидает получение сигнала «доступ к шине» 8,

получив с выхода 2 блока 24 на вход 11 по линии 26 сигнал «доступ к шине» 8,

в течение первого такта,

если команда управления соответствует операции «открыть маршрут», «фиксировать маршрут», «дополнить маршрут», «закрыть маршрут», «установить соединение»,

то порт 1.i передает с двунаправленного выхода 5 по шине 8 на вход 5 каждого порта 1.1÷1.n, где n≠i, сведения, однозначно интерпретируемые как адреса отправителя и получателя информации, команда управления и параметр условия «Скорость передачи», равный BR(i), и с выхода 4 по линии 12.i на вход i.2 матрицы коммутационных элементов (КЭ) 3 сигнал «установить тракт», каждый порт 1.1÷1.n, где n≠i, получив с шины 8 на вход 5, вход 1 блока 22 выполняет поиск в памяти САМ адреса отправителя и получателя информации и проверку условия «Скорость передачи» BR(i)+BRp<BR(max), где BR(i) - запрашиваемая скорость передачи, BRp - суммарная скорость передачи, используемая портом, BR(max) - общая скорость передачи порта,

если команда управления соответствует операции «разъединить тракт», то

порт 1.i с выхода 4 по линии 12.1÷12.n подает на вход 1.2÷n.2 матрицы КЭ 3 сигнал «установить тракт»,

КЭ матрицы 3, имеющие состояние «включено», получив на вход 1.2÷n.2 с линии 12.1÷12.n сигнал «установить тракт», переходят в состояние «выключено» и разъединяют тракт передачи,

в течение второго такта

каждый порт (1÷n, где n≠i), получив с выхода 4 блока 22 по линии 10.i на вход 10 блока 21 сигнал наличия или отсутствия значения полей "Адрес отправителя" и "Адрес получателя" в память САМ, с выхода 2 блока 24 по линии 26 на вход 11 признака порта (i), с выхода i.4 матрицы КЭ 3 по линии 14.i на вход 8 блока 21 сигнал «подтверждение», выполняет:

если команда управления равна «открыть маршрут», то принимает с выхода 4 блока 22 по линии 10.i на вход 10 блока 21 сигнал отсутствия значения полей "Адрес отправителя" и "Адрес получателя", подает с выхода 9 блока 21 по линии 25 на вход 6 блока 22 сигнал «запись в память САМ» и с выхода 4 блока 21 по линии 12.i на вход i.2 КЭ матрицы 3 сигнал «фиксировать тракт», иначе блокирует подачу сигнала «фиксировать тракт» на выходе 4 блока 21,

если команда управления равна «фиксировать маршрут», то принимает с выхода 4 блока 22 по линии 10.i на вход 10 блока 21 сигнал присутствия значения полей "Адрес отправителя" и "Адрес получателя", подает выхода 4 блока 21 по линии 12.i на вход i.2 КЭ матрицы 3 сигнал «фиксировать тракт», иначе блокирует подачу сигнала «фиксировать тракт» на выходе 4 блока 21,

если команда управления равна «дополнить маршрут», то принимает с выхода 4 блока 22 по линии 10.i на вход 10 блока 21 сигнал присутствия значения полей "Адрес отправителя" и "Адрес получателя", подает с выхода 9 блока 21 по линии 25 на вход 6 блока 22 сигнал «запись в память САМ» и с выхода 4 блока 21 по линии 12.i на вход i.2 КЭ матрицы 3 сигнал «фиксировать тракт», иначе блокирует подачу сигнала «фиксировать тракт» на выходе 4 блока 21,

если команда управления равна «закрыть маршрут», то принимает с выхода 4 блока 22 по линии 10.i на вход 10 блока 21 сигнал присутствия значения полей "Адрес отправителя" и "Адрес получателя" сигнал, подает с выхода 9 блока 21 по линии 25 на вход 6 блока 22 сигнал «удалить из памяти САМ» и с выхода 4 блока 21 по линии 12.1 на вход i.2 КЭ матрицы 3 сигнал «фиксировать тракт», иначе блокирует подачу сигнала «фиксировать тракт» на выходе 4 блока 21,

если команда управления равна «соединить тракт», то принимает с выхода 4 блока 22 по линии 10.i на вход 10 блока 21 признак присутствия значения полей "Адрес отправителя" и "Адрес получателя" сигнал, подает с выхода 4 блока 21 по линии 12.i на вход i.2 КЭ матрицы 3 сигнал «фиксировать тракт», иначе блокирует подачу сигнала «фиксировать тракт» на выходе 4 блока 21,

если на вход 8 блока 21 по линии 14.i с выхода i.4 матрицы КЭ 3 поступил сигнал «подтверждение», с выхода 2 блока 24 по линии 26 на вход 11 блока 21 поступил признак порта (i), то порт (i) начинается передачу блока информации с выхода 2 по линии 11.i на вход i.1 матрицы КЭ 3, а порты (1÷n, где n≠i) начинают прием блока информации с выхода i.3 матрицы КЭ 3 по линии 13.i на входе 6 блока 21 и далее на выход 3 блока 21 по линии 5.i во внешнюю сеть

из тракта передачи (i) блока 21 по линии 14.i, то принимает с выхода 4 блока 22 по линии 10.i на вход 10 блока 21 признак присутствия значения полей "Адрес отправителя" и "Адрес получателя" сигнал, подает с выхода 4 блока 21 по линии 12.i на вход i.2 КЭ матрицы 3 сигнал «фиксировать тракт», иначе блокирует подачу сигнала «фиксировать тракт» на выходе 4 блока 21,

КЭ матрицы 3, получив с линии 12.i на вход i.2 сигнал «установить тракт» и с линии i.5 на вход i.5 сигнал «фиксировать тракт», передают с выхода i.4 по линии 14.i сигнал «подтверждение», сохраняют состояние «Включено» в блоке 31 i/i, где 1<=I<=n, и соединяют линию i.1 с линией i.3, образуя тракт передачи.

4. Перечень фигур

Фиг.1. Формат блока передачи.

Фиг.2. Временная диаграмма работы способа синхронной ассоциативной маршрутизации/коммутации.

Фиг.3. Функциональная схема реализации способа синхронной ассоциативной маршрутизации/коммутации.

Фиг.4. Функциональная схема i-го канального порта.

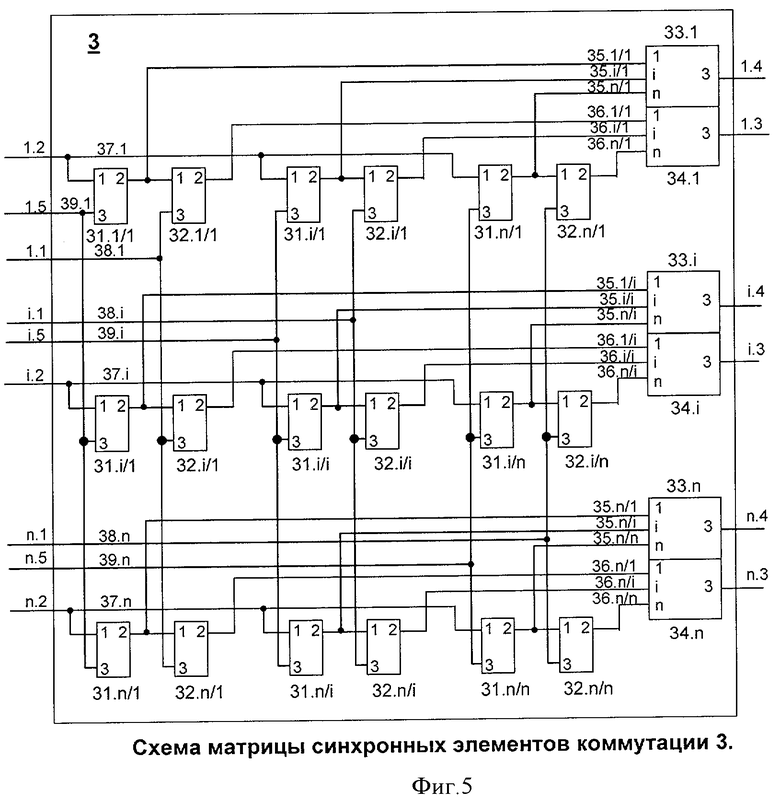

Фиг.5. Схема матрицы синхронных элементов коммутации 3.

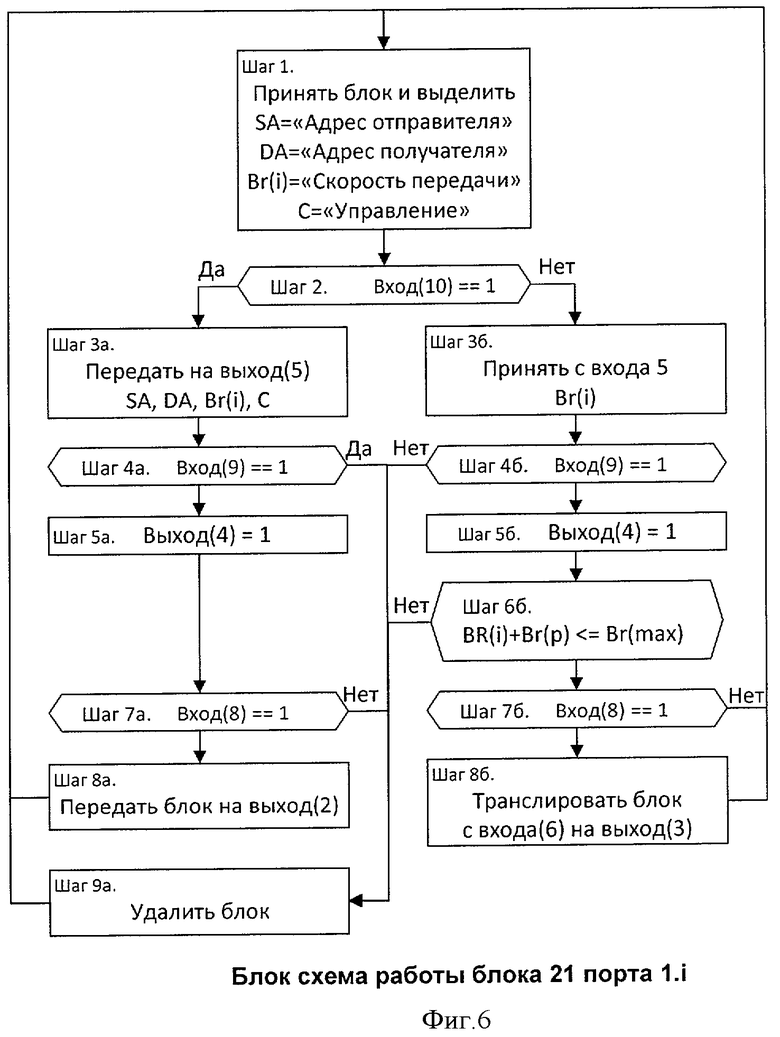

Фиг.6. Блок схема работы блока 21 порта 1.i.

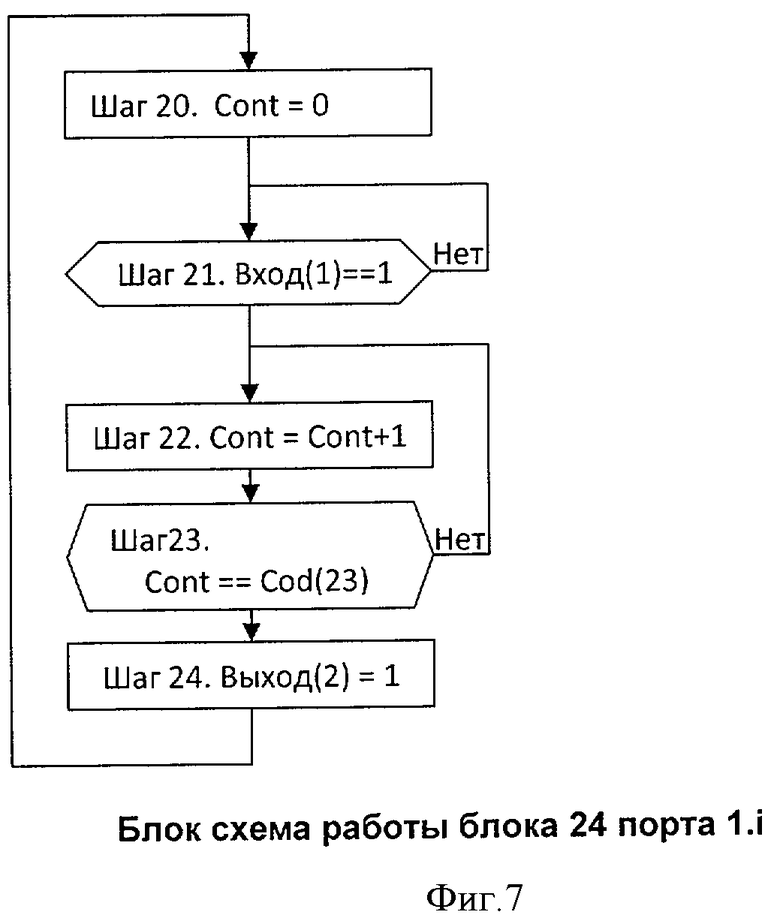

Фиг.7. Блок схема работы блока 24 порта 1.i.

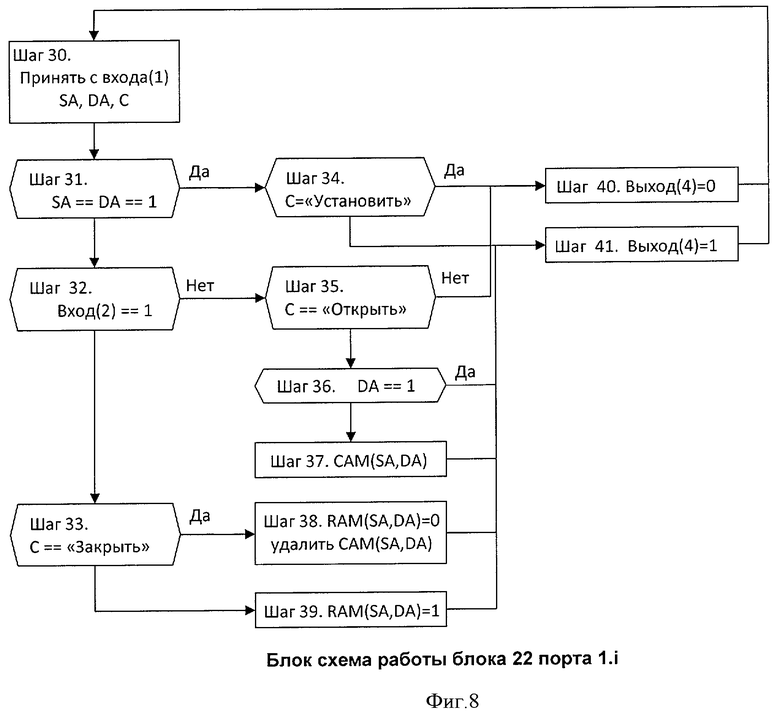

Фиг.8. Блок схема работы блока 22 порта 1.i.

5. Сведения, подтверждающие возможность осуществления изобретения

Порт 1.i (см. фиг.4) выполняет:

1. прием блока информации;

2. передачу блока информации;

3. удаление блока информации;

4. выделение полей "Адрес источника" и "Адрес приемника",

5. выделение полей "Управление" и «Скорость передачи»;

6. проверяет условие «Скорости передачи» BR(i)+BRp<BR(max);

7. команду «открыть маршрут»,

8. команду «фиксировать маршрут»,

9. команду «дополнить маршрут»,

10. команду «закрыть маршрут»,

11. команду «соединить тракт»,

12. команду «разъединить тракт»,

13. подачу сигнала «установить тракт»,

14. подачу сигнала «фиксировать тракт»,

15. прием сигнала «подтверждение»,

16. поиск значения полей "Адрес источника" и "Адрес приемника",

17. запись значений полей "Адрес источника" и "Адрес приемника" в память САМ;

18. удалить значений полей "Адрес источника" и "Адрес приемника" из памяти САМ;

19. определяет интервал времени «доступ к шине»

и содержит контроллеры 21 и 24, ассоциативный блок 22 и блок номер цикла 23.

При этом вход 7 контроллера 21, вход 3 контроллера 24, вход 3 ассоциативного блок 22 соединены шиной 7.

При этом вход 1 контроллера 24, вход 5 ассоциативного блока 22 соединены шиной 6.

При этом двунаправленный вход/выход 5 контроллера 21 и вход 1 ассоциативного блока 22 соединены с шиной 8.

При этом выход 9 контроллера 21 и вход 6 ассоциативного блока 22 соединены линией 25.

При этом вход 10 контроллера 21 и выход 4 ассоциативного блока 22 соединены линией 10.i.

При этом выход 2 контроллер 24, вход 11 контроллера 21 и вход 2 ассоциативного блок 22 соединены линией 26.

При этом вход 4 контроллера 24 соединен линией 27 с выходом 1 блока 23 номера цикла.

При этом вход 1 и выход 3 порта 1.i соединены с внешней сетью линиями 4.i и 5.i соответственно.

При этом порт 1.i выходом 2 соединен линией 11.i с входом i.1 матрицы КЭ 3.

При этом порт 1.i выходом 4 соединен линией 12.i с входом i.2 матрицы КЭ 3.

При этом порт 1.i выходом 6 соединен линией 13.i с входом i.3 матрицы КЭ 3.

При этом порт 1.i выходом 8 соединен линией 14.i с входом i.4 матрицы КЭ 3.

При этом порт 1.i выходом 10 соединен линией 15.i с входом i.5 матрицы КЭ 3.

При этом вход 7 порт 1.i соединен с выходом 1 арбитра 2 шиной 6.

При этом вход 9 порт 1.i соединен с выходом 2 арбитра 2 шиной 7.

При этом двунаправленный вход/выход 5 каждого из N порта соединен шиной 8.

Контроллер 21 1.i порта выполняет программу обработки в соответствии с алгоритмом (см. фиг.6),

при этом шаг 1: Принять блок информации и выделить из него SA («Адрес отправителя»), DA («Адрес получателя»), Br(i) («Скорость передачи») и С («Управление»),

шаг 2: если на входе 10 есть сигнал «доступ к шине», то переход на шаг 3а, иначе переход на шаг 3б,

шаг 3а: Передать на выход 5 SA, DA, Br(i), С,

шаг 4а: если на входе 9 есть сигнал «Наличие адреса», то переход на шаг 9а,

шаг 5а: передать с выхода 4 сигнал «установить/разъединить тракт»,

шаг 7а: если на входе 8 нет сигнала «подтверждение», то переход на шаг 9а.

шаг 8а: передать блок информации с выхода 2 и переход на шаг 1.

шаг 9а: удалить блок информации и переход на шаг 1,

шаг 3б: Принять с входа 5 Br(i),

шаг 4б: если на входе 9 есть сигнал «Наличие адреса», то переход на шаг 9а,

шаг 5б: передать с выхода 4 сигнал «установить/разъединить тракт»,

шаг 6б: если сумма BR(i)+Br(p) меньше Br(max), то переход на шаг 9а,

шаг 7б: если на входе 8 нет сигнал «подтверждение», то переход на шаг 9а,

шаг 8б: транслировать блок информации с входа 6 на выход 3 и переход на шаг 1.

Контроллер 24 1.i порта выполняет программу обработки в соответствии с алгоритмом (см. фиг.7),

при этом шаг 20: установить значение счетчика равным 0,

шаг 21: если на входе 1 есть сигнал "цикл", то переход на шаг 22,

шаг 22: увеличить значение счетчика на 1,

шаг 23: если значение счетчика неравно значению номера цикла 23, то переход на шаг 22,

шаг 24: установить на выходе 2 есть сигнал "доступ к шине" и переход на шаг 20.

Ассоциативный блок 22 1.i порта выполняет программу обработки в соответствии с алгоритмом (см. фиг.8),

при этом шаг 30: Принять с входа 1 SA, DA,

шаг 31: если SA и DA присутствуют в САМ (SA==DA==1), то переход на шаг 34,

шаг 32: если на входе 2 нет сигнал "доступ к шине", то переход на шаг 35,

шаг 33: если значение С равно «закрыть», то переход на шаг 38,

шаг 34: если значение С равно «Установить», то переход на шаг 40, иначе переход на шаг 41,

шаг 35: если значение С неравно «Открыть», то переход на шаг 40,

шаг 36: если DA присутствуют в САМ (DA==1), то переход на шаг 41,

шаг 37: записать в САМ SA и DA (SA=DA=1),

шаг 38: удалить из RAM и САМ SA и DA (SA=DA=0) и переход на шаг 41,

шаг 39: записать в RAM SA и DA (SA=DA=0) и переход на шаг 41,

шаг 40: сбросить на выходе 4 сигнал «Наличие адреса» и переход на шаг 30,

шаг 41: установить на выходе 4 сигнал «Наличие адреса» и переход на шаг 30.

С целью соединения тракта передачи порт (i) с выхода 4 блока 21 по линии 12.i на вход i.2 КЭ матрицы 3 передает в первом такте сигнал «установить тракт», порт (i) с выхода 10 по линии 10.i на вход i.5 КЗ матрицы 3 передает во втором такте сигнал «фиксировать тракт». Поступление на вход 8 по линии 14.i с выхода i.4 КЭ матрицы 3 сигнал «подтверждение» сигнализирует порту (i), что соединения тракта выполнено.

Доступ порта (i) к шине 8 осуществляется с выхода 2 блока 24 по линии 26 на вход 11 блока 21 сигналом «доступ к шине», для чего арбитр 2 подает с выхода 1 на шину 6 сигнала «частотная синхронизация» (диаграмма 1 фиг.2) и с выхода 2 на шину 7 сигнала «цикловая синхронизация» (диаграмма 5 фиг.2). Скважность сигнала «цикловая синхронизация» пропорциональна числу портов.

Матрица элементов коммутации ЭК размером N2 (см. фиг.5) выполняет функции:

1. прием сигнала «установление тракта»,

2. прием сигнала «фиксация тракта»,

3. выдача сигнала «подтверждение»,

4. хранения состояния сигнала «установление тракта»,

5. включения или отключения тракта передачи

и состоит из триггера 31.n, элемента 2И 32.n, элементов n-ИЛИ 33.n и 34.n с n-входами,

при этом вход 1 триггеров 31n/1 соединен с входом n.2 ЭК матрицы 3 линией 37.n,

вход 3 триггеров 31 1/n соединен с входом п.5 ЭК матрицы 3 линией 39.n,

выход 2 триггеров 31n/n соединен с входом 1-n элементы n-ИЛИ 33.n и входом 1 элемента 2И 32n/n линией 35n/n

вход 3 элемента 2И 32.n соединен с входом n.1 матрицы ЭК 3 линией 38.n,

выход 2 элемента 2И 32n/n соединен с входом 1-n элементы n-ИЛИ 34.n линией 36n/n,

выход 3 элемента n-ИЛИ 33.n соединен с выходом n.4 матрицы ЭК 3,

выход 3 элемента n-ИЛИ 34.n соединен с выходом n.3 матрицы ЭК 3,

Триггер 31 выполняет фиксацию сигнала «установление тракта», принимая сигналы «установление тракта» на вход 2 и «фиксация тракта» на вход 3 на данном входе. Хранение значение сигнала «установление тракта» осуществляется до появления на входе 2 переднего фронта сигнала «установление тракта».

Элемент 2И 32 под воздействием управляющего сигнала на входе 1 обеспечивает передачу сигнала с входа 3 (линия 38) на выход 2 (линия 36), при этом ключ может иметь исполнение либо одноразрядной линией 38 и 36, либо многоразрядной линией 38 и 36.

Элемент n-ИЛИ 33 передает с входов 1.n на выход 3 сигнал «подтверждение».

Элемент n-ИЛИ 34 передает с входов 1.n на выход 3 сигнал "тракт передачи".

Библиография

1. Бюллетень ТИИЭР, том 66 за 1978 год.

2. Инженерная энциклопедия "Технологии Электронных Коммуникаций" (ТЭК) "АТМ: технология высокоскоростных сетей, А.Н.Назаров, М.В.Симонов, ЭКО-ТРЕЙНДЗ, Москва, 1998.

3. Патент US №6021086 от 1.02.2000 г.

4. Патент US №5905725 от 18.05.1999 г.

5. Патент GB №2395860 от 2.06.2004 г.

6. Патент ЕР №2009849 от 31.12.2008 г.

7. Патент US №5459840 от 17.10.95 г.

8. Патент US №5537403 от 16.07.96 г

9. Патент US №5642349 от 24.06.1997 г.

10. Патент US № Re.34528 от 1.02.1994 г.

11. Патент US №6212194 от 3.04.2001 г.

12. Патент US №2003/0152087 A1 от 14.08.2003 г.

13. Патент US №6947415 от 20.09.2005 г.

14. Патент ЕР 0488673 А2 от 27.11.1991 г.

15. Патент US №2003/0091038 A1 от 15.05.2003 г.

16. Патент US №6625148 от 23.09.2003 г.

17. Клингман Э. Проектирование микропроцессорных систем. - М.: Мир, 1980.

18. Патент RU №2140132 от 13.01.1999 г.

19. Патент US №6717831 от 6.04.2004 г.

20. Сэм Хелеби и Денни Мак-Ферсон Принципы маршрутизации в Internet.-: Пер. с англ. - М.: Издательский дом «Вильямс», 2001.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ДВУХТАКТНОЙ АССОЦИАТИВНОЙ МАРШРУТИЗАЦИИ | 1999 |

|

RU2140132C1 |

| МАРШРУТИЗИРУЮЩИЙ КОММУТАТОР И СПОСОБ РАБОТЫ МАРШРУТИЗАТОРА | 2015 |

|

RU2580077C1 |

| МУЛЬТИСЕРВИСНЫЙ МАРШРУТИЗАТОР | 2019 |

|

RU2710980C1 |

| Способ организации автоматической балансировки потоков многопоточного соединения на коммутационных устройствах с использованием их самообучения | 2017 |

|

RU2675148C1 |

| СПОСОБ И УСТРОЙСТВО ГИБРИДНОЙ КОММУТАЦИИ РАСПРЕДЕЛЕННОЙ МНОГОУРОВНЕВОЙ ТЕЛЕКОММУНИКАЦИОННОЙ СИСТЕМЫ, БЛОК КОММУТАЦИИ И ГЕНЕРАТОР ИСКУССТВЕННОГО ТРАФИКА | 2014 |

|

RU2542906C1 |

| Способ контроля доступа между устройствами в межмашинных сетях передачи данных | 2018 |

|

RU2714853C1 |

| Способ создания защищенного L2-соединения между сетями с коммутацией пакетов | 2018 |

|

RU2694585C1 |

| КОММУТАТОР LINK-ПОРТОВ | 2009 |

|

RU2405196C1 |

| СПОСОБ МАРШРУТИЗАЦИИ ПОТОКОВ ИНФОРМАЦИИ, КРИТИЧНОЙ К ЗАДЕРЖКАМ, В СЕТИ СПУТНИКОВОЙ СВЯЗИ НА НЕГЕОСТАЦИОНАРНЫХ КОСМИЧЕСКИХ АППАРАТАХ, СВЯЗАННЫХ МЕЖСПУТНИКОВЫМИ ЛИНИЯМИ СВЯЗИ В ОДНОЙ ОРБИТАЛЬНОЙ ПЛОСКОСТИ И РАСПОЛОЖЕННЫХ НА КРУГОВЫХ ОРБИТАХ | 2022 |

|

RU2799503C1 |

| Способ распределения информационных потоков в пакетной радиосети и управляемый модульный маршрутизатор для его осуществления | 2020 |

|

RU2748574C1 |

Изобретение относится к области электросвязи и может быть использовано при построении локальных, территориальных и глобальных сетей подвижной и фиксированной связи, или распределенных вычислительных сред. Техническим результатом является расширение функциональных возможностей и увеличения быстродействия синхронизации за счет обеспечения установления маршрута передачи за 2 такта. Способ синхронной ассоциативной маршрутизации/коммутации предназначен для установления маршрута и соединения тракта передачи от одного отправителя до одного и более получателей, между системами либо приема/передачи информации, либо обработки данных, информации структурированной в блоки, включающие сведения, однозначно идентифицирующие отправителя и получателя информации, служебные сведения, однозначно определяющие действия, для установления маршрута: открыть или закрыть, фиксировать или добавить маршрут, или для соединения тракта передачи: соединить или разъединить, и однозначно определяющие условие, скорость передачи. 13 з.п. ф-лы, 8 ил.

1. Способ синхронной ассоциативной маршрутизации/коммутации, предназначенный для установления маршрута и соединения тракта передачи от отправителя до одного и более получателя информации, структурированной в блоки, включающие сведения, однозначно идентифицирующие адреса отправителя и получателя информации,

состоящий из N портов, коммутационных элементов, объединенных в матрицу коммутации размером N×N и арбитра,

соединяющий внешнюю сеть с N портами, соединенными с коммутационными элементами, объединенными в матрицу коммутации размером N×N, соединяющими тракт передачи блоков информации от одного порта до одного и более другого порта,

принимающий из внешней сети блоки информации и выделяющий из заголовка блока информации адреса отправителя и получателя информации,

выполняющий преобразование внутренних данных, определяющих соответствие между номером порта и адресами отправителя или получателя информации,

хранящий внутренние данные о соответствие между номером порта и адресами отправителя и получателя, применяющий известное ассоциативное запоминающее устройство, содержащее ячейки сравнения, используемые для поиска адреса и ячейки хранения, используемые для идентификации номера порта, отличающийся тем, что

каждый порт принимает из внешней сети блоки информации и выделяет из заголовка блока информации сведения, однозначно интерпретируемые как адреса отправителя и получателя информации, команда управления и параметр условия, каждый порт определяет момент времени доступа к шине по коду, получив доступ к шине, порту присваивается (i) номер порта,

каждый коммутационный элемент, объединенный в матрицу размером n×n, имеет ячейку памяти, где хранит состояние включено или выключено, при этом в течение первого такта

порт (i) по шине передает в порты (1÷n, где n≠i) сведения, однозначно интерпретируемые как адреса отправителя и получателя информации, команда управления и параметр условия, подает сигнал «установить тракт»,

коммутационный элемент, объединенный в матрицу размером n×n, принимая сигнал «установить тракт», переходит в состояние «выключено», разъединяя тракт передачи,

каждый из портов (1÷n, где n≠i) принимает сведения, однозначно интерпретируемые как адреса отправителя и получателя информации, команда управления и параметр условия, осуществляет поиск адреса отправителя и получателя в контекстно-адресуемой памяти, проверяет условие на истинность значения,

в течение второго такта

порт (i) передает блок информации, подает сигнал «установить тракт», принимает сигнал «подтверждение»,

каждый из портов (1÷n, где n≠i) принимает сигнал из контекстно-адресуемой памяти, подает сигнал в контекстно-адресуемую память, получает результат проверки истинности условия, выполняет команду управления, передает сигнал «фиксировать тракт», принимает блок информации,

каждый коммутационный элемент, получивший сигнал «установить тракт» и сигнал «фиксировать тракт», меняет состояние на включено, соединяя тракт передачи, и подает сигнал «подтверждение» в порт (i).

2. Способ синхронной ассоциативной маршрутизации/коммутации по п.1, отличающийся тем, что когда команда управления принимает значение «открыть маршрут», в течение второго такта

порт (i) подает сигнал «установить тракт»,

каждый из портов (1÷n, где n≠i)

проверяет отсутствие в контекстно-адресуемой памяти значение адресов отправителя и получателя,

проверяет равенство параметра условия значению истина,

подает сигнал запись в контекстно-адресуемую память для записи значения адреса отправителя и получателя информации, подает сигнал «фиксировать тракт»,

порт (i), получив сигнал «подтверждение», передает блок информации через коммутационный элемент, объединенный в матрицу n×n, в один и более портов (1÷n, где n≠i), а каждый из портов (1÷n, где n≠i) принимает блок информации.

3. Способ синхронной ассоциативной маршрутизации/коммутации по п.2, отличающийся тем, что когда команда управления имеет значение «фиксировать маршрут», в течение второго такта

порт (i) подает сигнал «установить тракт»,

каждый из портов (1÷n, где n≠i)

проверяет наличие в контекстно-адресуемой памяти значение адресов отправителя и получателя,

проверяет равенство параметра условия значению истина, подает сигнал «фиксировать тракт»,

порт (i), получив сигнал «подтверждение», передает блок информации через коммутационный элемент, объединенный в матрицу n×n, в один и более портов (1÷n, где n≠i), а каждый из портов (1÷n, где n≠i) принимает блок информации.

4. Способ синхронной ассоциативной маршрутизации/коммутации по п.2, отличающийся тем, что когда команда управления имеет значение «дополнить маршрут», в течение второго такта

порт (i) подает сигнал «установить тракт»,

каждый из портов (1÷n, где n≠i)

проверяет наличие в контекстно-адресуемой памяти значение адресов отправителя и получателя,

проверяет равенство параметра условия значению истина,

подает сигнал запись в контекстно-адресуемую память для записи значения адреса отправителя и получателя информации, подает сигнал «фиксировать тракт»,

порт (i), получив сигнал «подтверждение», передает блок информации через коммутационный элемент, объединенный в матрицу n×n, в один и более портов (1÷n, где n≠i), а каждый из портов (1÷n, где n≠i) принимает блок информации.

5. Способ синхронной ассоциативной маршрутизации/коммутации по п.2, отличающийся тем, что когда команда управления имеет значение «закрыть маршрут», в течение второго такта

порт (i) подает сигнал «установить тракт»,

каждый из портов (1÷n, где n≠i)

проверяет наличие в контекстно-адресуемой памяти значение адресов отправителя и получателя,

проверяет равенство параметра условия значению истина, подает сигнал «фиксировать тракт»,

подает сигнал удалить в контекстно-адресуемую память для стирания значения адреса отправителя и получателя информации,

порт (i), получив сигнал «подтверждение», передает блок информации через коммутационный элемент, объединенный в матрицу n×n, в один и более портов (1÷n, где n≠i), а каждый из портов (1÷n, где n≠i) принимает блок информации.

6. Способ синхронной ассоциативной маршрутизации/коммутации по п.2, отличающийся тем, что когда команда управления имеет значение «соединить тракт», в течение второго такта

порт (i) подает сигнал «установить тракт»,

каждый из портов (1÷n, где n≠i)

проверяет наличие в контекстно-адресуемой памяти значение адресов отправителя и получателя,

подает сигнал «фиксировать тракт»,

порт (i), получив сигнал «подтверждение», передает блок информации через коммутационный элемент, объединенный в матрицу n×n, в один и более портов (1÷n, где n≠i), а каждый из портов (1÷n, где n≠i) принимает блок информации.

7. Способ синхронной ассоциативной маршрутизации/коммутации по п.6, отличающийся тем, что когда команда управления имеет значение «разъединить тракт», в течение первого такта

порт (i) подает сигнал «установить тракт»,

каждый коммутационный элемент, имеющий состояние включено, получивший сигнал «установить тракт», переходит в состояние выключено, разъединяя тракт передачи.

8. Способ синхронной ассоциативной маршрутизации/коммутации по любому из пп.2-7, отличающийся тем, что порт (i), не получив сигнал «подтверждение», удаляет блок информации.

9. Способ синхронной ассоциативной маршрутизации/коммутации по любому из пп.2-7, отличающийся тем, что коммутационный элемент соединяет тракт многоразрядной линией.

10. Способ синхронной ассоциативной маршрутизации/коммутации по любому из пп.2-5, отличающийся тем, что параметром условия служит поле, однозначно интерпретируемое как скорость передачи.

11. Способ синхронной ассоциативной маршрутизации/коммутации по любому из пп.2-5, отличающийся тем, что условием считают, что сумма значений текущей скорости передачи порта и принятой скорости передачи меньше максимально возможного значения скорости порта.

12. Способ синхронной ассоциативной маршрутизации/коммутации по п.11, отличающийся тем, что значение текущей скорости передачи порта увеличивается на значение принятой скорости передачи по команде «фиксировать маршрут».

13. Способ синхронной ассоциативной маршрутизации/коммутации по п.12, отличающийся тем, что значение текущей скорости передачи порта увеличивается на значение принятой скорости передачи по команде «дополнить маршрут».

14. Способ синхронной ассоциативной маршрутизации/коммутации по п.13, отличающийся тем, что значение текущей скорости передачи порта уменьшается на значение принятой скорости передачи по команде «закрыть маршрут».

| US 6947415 B1, 20.09.2005 | |||

| WO 2005114436 A1, 01.12.2005 | |||

| СИСТЕМА ВРЕМЕННОГО ЗАПОМИНАНИЯ ИНФОРМАЦИИ | 1991 |

|

RU2138845C1 |

| СПОСОБ ОБНОВЛЕНИЯ ПАРАМЕТРА ЛИНИИ РАДИОСВЯЗИ В СИСТЕМЕ МОБИЛЬНОЙ СВЯЗИ | 2003 |

|

RU2291591C2 |

| СПОСОБ ДВУХТАКТНОЙ АССОЦИАТИВНОЙ МАРШРУТИЗАЦИИ | 1999 |

|

RU2140132C1 |

Даты

2012-04-10—Публикация

2009-11-23—Подача