Изобретение относится к автоматике и аналоговой вычислительной технике и может быть использовано для построения функциональных узлов аналоговых вычислительных машин, средств автоматического регулирования и управления, аналоговых процессоров и др.

Известны логические устройства (см., например, рис. 8 или 9 на стр. 41 в кн. : Алгоритмы и устройства обработки сигналов и автоматизация проектирования. Сб. научных трудов. Таллинн: АН Эстонии, 1991 г.), которые идентифицируют супраминимальное значение информационного аналогового сигнала.

К причинам, препятствующим достижению указанного ниже технического результата при использовании известных логических устройств, относятся ограниченные функциональные возможности, обусловленные тем, что для настройки на идентификацию субмаксимального значения информационного сигнала требуется изменение схемы устройства.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является, принятое за прототип логическое устройство для ранговой обработки аналоговых сигналов (фиг. 1 в описании изобретения к Патенту РФ 2109338, кл. G 06 G 7/25, 1998 г.), которое идентифицирует минимальное и супраминимальное значения информационного сигнала и содержит n реляторов, состоящих из компаратора и замыкающего ключа в первом и n-м реляторах и из компаратора, двух замыкающих и размыкающего ключей во всех промежуточных реляторах.

К причинам, препятствующим достижению указанного ниже технического результата при использовании прототипа, относятся ограниченные функциональные возможности, обусловленные тем, что для настройки на идентификацию максимального и субмаксимального значений информационного сигнала требуется изменение схемы устройства.

Техническим результатом изобретения является расширение функциональных возможностей за счет обеспечения идентификации минимального и супраминимального или максимального и субмаксимального значений информационного сигнала без изменения схемы устройства.

Указанный технический результат при осуществлении изобретения достигается тем, что в логическом устройстве для ранговой обработки аналоговых сигналов, содержащем n реляторов, состоящих из компаратора и замыкающего ключа в первом и n-м реляторах и из компаратора, первого ключа, выполненного замыкающим, второго ключа, выполненного размыкающим, и третьего ключа, выполненного замыкающим, во всех промежуточных реляторах, входы ключей являются соответствующими переключательными входами реляторов, а их выходы - соответствующими выходами реляторов, неинвертирующие входы компараторов реляторов являются входами соответствующих задающих напряжений, их инвертирующие входы объединены и образуют информационный вход логического устройства, идентифицирующий вход которого соединен с переключательным входом первого и с первым переключательным входом второго реляторов, выход первого релятора соединен с вторым и с третьим переключательными входами второго релятора, первый и второй выходы i-го  релятора соединены с первым переключательным входом (i+1)-го релятора, а второй и третий переключательные входы (i+1)-го релятора - с третьим выходом i-го релятора, первый и второй выходы (n-1)-го релятора соединены с переключательным входом n-го релятора, выход которого подключен к третьему выходу (n-1)-го релятора и является выходом логического устройства, особенность заключается в том, что в каждый из n реляторов введен булевый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй входы которого соединены соответственно с выходом компаратора и входом управления релятора, выход булевого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ в первом и в n-м реляторах подключен к управляющему входу замыкающего ключа, а в каждом из промежуточных реляторов - к управляющему входу первого, второго и третьего ключей, входы управления всех реляторов объединены и образуют вход управления логического устройства.

релятора соединены с первым переключательным входом (i+1)-го релятора, а второй и третий переключательные входы (i+1)-го релятора - с третьим выходом i-го релятора, первый и второй выходы (n-1)-го релятора соединены с переключательным входом n-го релятора, выход которого подключен к третьему выходу (n-1)-го релятора и является выходом логического устройства, особенность заключается в том, что в каждый из n реляторов введен булевый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй входы которого соединены соответственно с выходом компаратора и входом управления релятора, выход булевого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ в первом и в n-м реляторах подключен к управляющему входу замыкающего ключа, а в каждом из промежуточных реляторов - к управляющему входу первого, второго и третьего ключей, входы управления всех реляторов объединены и образуют вход управления логического устройства.

Проведенный заявителем анализ уровня техники, включающий поиск по патентным и научно-техническим источникам информации, и выявление источников, содержащих сведения об аналогах заявленного изобретения, позволил установить, что заявитель не обнаружил аналог, характеризующийся признаками, тождественными всем существенным признакам заявленного изобретения. Определение из перечня выявленных аналогов прототипа как наиболее близкого по совокупности существенных признаков аналога позволил выявить совокупность существенных по отношению к усматриваемому заявителем техническому результату отличительных признаков в заявленном устройстве, изложенных в формуле изобретения. Следовательно, заявляемое изобретение соответствует условию "новизна".

Для проверки соответствия заявленного изобретения условию "изобретательский уровень" заявитель провел дополнительный поиск известных решений, чтобы выявить признаки, совпадающие с отличительными от прототипа признаками заявленного устройства. Результаты поиска показали, что заявленное изобретение не вытекает для специалиста явным образом из известного уровня техники, поскольку из уровня техники, определенного заявителем, не выявлено влияние предусматриваемых существенными признаками заявленного изобретения преобразований на достижение технического результата, в частности, заявленным изобретением не предусматриваются следующие преобразования:

- дополнение известного средства какой-либо известной частью (частями), присоединяемой (присоединяемыми) к нему по известным правилам для достижения технического результата, в отношении которого установлено влияние именно таких дополнений;

- замена какой-либо части (частей) известного средства другой известной частью для достижения технического результата, в отношении которого установлено влияние именно такой замены;

- исключение какой-либо части (элемента) средства с одновременным исключением обусловленной ее наличием функции и достижением при этом обычного для такого исключения результата;

- увеличение количества однотипных элементов для усиления технического результата, обусловленного наличием в средстве именно таких элементов;

- выполнение известного средства или его части (частей) из известного материала для достижения технического результата, обусловленного известными свойствами этого материала;

- создание средства, состоящего из известных частей, выбор которых и связь между которыми осуществлены на основании известных правил, рекомендаций, и достигаемый при этом технический результат обусловлены только известными свойствами частей этого средства и связей между ними.

Описываемое изобретение не основано на изменении количественного признака (признаков), представлении таких признаков во взаимосвязи либо изменении ее вида. Имеется в виду случай, когда известен факт влияния каждого из указанных признаков на технический результат, и новые значения этих признаков или их взаимосвязь могли быть получены исходя из известных зависимостей, закономерностей. Следовательно, заявленное изобретение соответствует условию "изобретательский уровень".

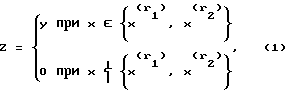

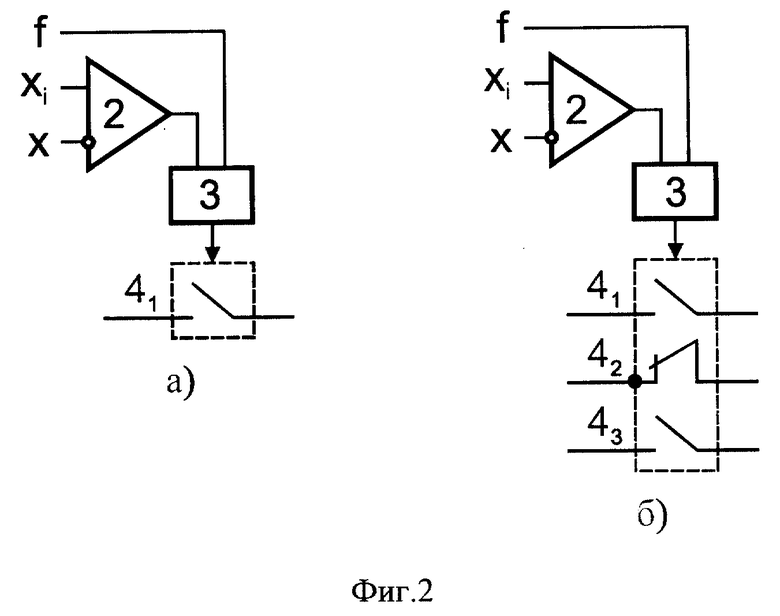

На фиг. 1 представлена схема предлагаемого логического устройства. На фиг. 2 изображены схемы одноключевого (фиг. 2,а) и трехключевого (фиг. 2,б) реляторов, которые использованы в предлагаемом устройстве.

Схема логического устройства (фиг. 1) содержит n реляторов 11,...,1n. Каждый релятор содержит компаратор 2, подключенный выходом к первому входу булевого элемента "исключающее ИЛИ" 3, второй вход которого является входом управления релятора, а выход соединен с управляющим входом замыкающего ключа 41 в одноключевом реляторе (фиг. 2,а) или с управляющим входом первого ключа 41, выполненного замыкающим, второго ключа 42, выполненного размыкающим, и третьего ключа 43, выполненного замыкающим в трехключевом реляторе (фиг. 2, б). Неинвертирующие компараторные входы реляторов 11,...,1n являются входами соответствующих задающих напряжений, их инвертирующие компараторные входы объединены и образуют информационный вход логического устройства, идентифицирующий вход которого соединен с переключательным входом релятора 11 и с первым переключательным входом релятора 12, выход релятора 11 соединен с вторым и с третьим переключательными входами релятора 12, первый и второй выходы релятора  соединены с первым переключательным входом релятора 1i+1, а второй и третий переключательные входы релятора 1i+1 - с третьим выходом релятора 1i, первый и второй выходы релятора 1n-1 соединены с переключательным входом релятора 1n, выход которого подключен к третьему выходу релятора 1n-1 и является выходом Z логического устройства, вход управления которого образуют объединенные входы управления всех реляторов.

соединены с первым переключательным входом релятора 1i+1, а второй и третий переключательные входы релятора 1i+1 - с третьим выходом релятора 1i, первый и второй выходы релятора 1n-1 соединены с переключательным входом релятора 1n, выход которого подключен к третьему выходу релятора 1n-1 и является выходом Z логического устройства, вход управления которого образуют объединенные входы управления всех реляторов.

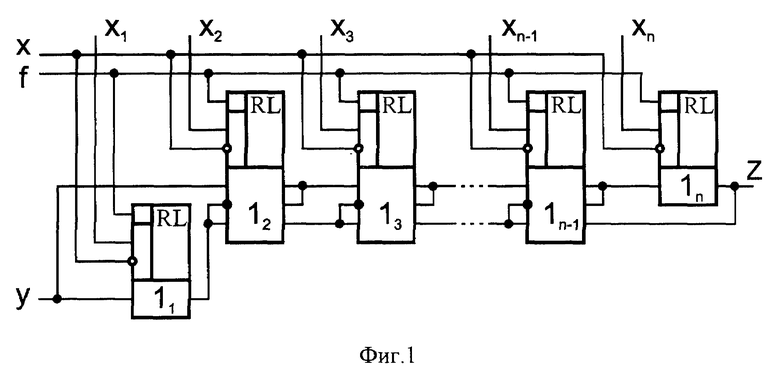

Работа предлагаемого логического устройства осуществляется следующим образом. На неинвертирующие компараторные входы реляторов 11,...,1n подаются соответственно задающие напряжения x1,...,xn∈ (xmin,xmax); на информационный и идентифицирующий входы логического устройства подаются соответственно информационный аналоговый сигнал x ∈ (xmin,xmax), значения которого подлежат идентификации, и идентифицирующий аналоговый сигнал y. При f = 0 (f ∈ {0,1} - сигнал на входе управления логического устройства) и xi > x или при f = 1 и xi < x замыкающие ключи 41, 43 замкнуты, размыкающий ключ 42 разомкнут, а при f = 1 и xi > x или при f = 0 и xi < x имеем обратную картину, то есть сигнал f изменяет логику коммутации переключательных входов реляторов. В прототипе аналогичное изменение достигается путем перестройки его схемы (заменой замыкающих и размыкающих ключей соответственно на размыкающие и замыкающие или взаимозамещением компараторных входов реляторов). Таким образом, воспроизводимая предлагаемым логическим устройством операция определяется выражением

где надстрочный индекс r ∈ {r1,r2} (r = 1, r = 2, при f = 0; r1 = n + 1, r2 = n при f = 1) есть ранг (порядковый номер) информационного сигнала x = x(r) в последовательности x(1),...,x(n+1), полученной ранжированием сигналов x1,...,xn, x в порядке их возрастания. Согласно (1) при f = 0 осуществляется идентификация (или селекция, если информационный и идентифицирующий входы устройства объединены) минимального x = x(1) и супраминимального x = x(2), а при f = 1 - максимального x = x(n+1) и субмаксимального x = x(n) значений информационного сигнала x. Логическое устройство обладает свойством обратимости, то есть идентифицирующий вход и выход этого устройства могут быть использованы соответственно в качестве его выхода и идентифицирующего входа.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемое логическое устройство обладает более широкими по сравнению с прототипом функциональными возможностями, так как обеспечивает идентификацию минимального и супраминимального или максимального и субмаксимального значений информационного сигнала без каких-либо схемных изменений.

Таким образом, вышеизложенные сведения свидетельствуют о выполнении при использовании заявленного устройства следующей совокупности условий:

- средство, воплощающее заявленное устройство при его осуществлении, предназначено для использовании в промышленности, а именно в области автоматики и аналоговой вычислительной техники в качестве функционального узла аналоговых вычислительных машин, средств автоматического регулирования и управления, аналоговых процессоров и др.;

- для заявленного устройства в том виде, как оно охарактеризовано в независимом пункте изложенной формулы изобретения, подтверждена возможность его осуществления с помощью описанных в заявке или известных до даты приоритета средств и методов;

- средство, воплощающее заявленное изобретение при его осуществлении, способно обеспечить достижение усматриваемого заявителем технического результата.

Следовательно, заявленное изобретение соответствует условию "промышленная применимость".

| название | год | авторы | номер документа |

|---|---|---|---|

| АНАЛОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ДЛЯ ИДЕНТИФИКАЦИИ И СЕЛЕКЦИИ ЭКСТРЕМАЛЬНОГО, СУПРАЭКСТРЕМАЛЬНОГО ИЛИ СУБЭКСТРЕМАЛЬНОГО ЗНАЧЕНИЙ ИНФОРМАЦИОННОГО СИГНАЛА | 1995 |

|

RU2109338C1 |

| РАНГОВЫЙ ИДЕНТИФИКАТОР | 1999 |

|

RU2149454C1 |

| РАНГОВЫЙ РАСПОЗНАВАТЕЛЬ | 1999 |

|

RU2143736C1 |

| РАНГОВЫЙ ПРЕДИКАТОР | 2001 |

|

RU2204861C1 |

| РЕЛЯТОРНЫЙ ПРОЦЕССОР ДЛЯ ИДЕНТИФИКАЦИИ И СЕЛЕКЦИИ КВАРТИЛЬНЫХ ЗНАЧЕНИЙ ИНФОРМАЦИОННОГО СИГНАЛА, ЗАДАННОГО НА ПЯТИЭЛЕМЕНТНОМ МНОЖЕСТВЕ СИГНАЛОВ | 2001 |

|

RU2178914C1 |

| АНАЛОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ "ЗАПРЕТ МИНИМАЛЬНОГО И МАКСИМАЛЬНОГО ЗНАЧЕНИЙ ИНФОРМАЦИОННОЙ ПЕРЕМЕННОЙ" | 1995 |

|

RU2130200C1 |

| РЕЛЯТОРНЫЙ МОДУЛЬ | 2001 |

|

RU2195701C1 |

| АНАЛОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ДЛЯ ИДЕНТИФИКАЦИИ РАНГОВОЙ НЕЧЕТНОСТИ ИЛИ ЧЕТНОСТИ ИНФОРМАЦИОННОГО СИГНАЛА | 1995 |

|

RU2109339C1 |

| АДРЕСНЫЙ ИДЕНТИФИКАТОР | 1999 |

|

RU2143740C1 |

| КОНЪЮНКТИВНО-ДИЗЪЮНКТИВНЫЙ РЕЛЯТОР | 1999 |

|

RU2143730C1 |

Изобретение относится к вычислительной технике и может быть использовано в аналоговых вычислительных машинах. Техническим результатом является расширение функциональных возможностей за счет обеспечения идентификации минимального и супраминимального или максимального и субмаксимального значений информационного сигнала. Устройство содержит n реляторов, первый и последний из которых состоят из компаратора и замыкающего ключа, каждый промежуточный релятор состоит из компаратора, двух замыкающих и размыкающего ключей. Каждый релятор содержит также булевый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ. 2 ил.

Логическое устройство для ранговой обработки аналоговых сигналов, содержащее n реляторов, состоящих из компаратора и замыкающего ключа в первом и n-м реляторах и из компаратора, первого ключа, выполненного замыкающим, второго ключа, выполненного размыкающим, и третьего ключа, выполненного замыкающим, во всех промежуточных реляторах входы ключей являются соответствующими переключательными входами реляторов, а их выходы - соответствующими выходами реляторов, неинвертирующие входы компараторов реляторов являются входами соответствующих задающих напряжений, их инвертирующие входы объединены и образуют информационный вход логического устройства, идентифицирующий вход которого соединен с переключательным входом первого и с первым переключательным входом второго реляторов, выход первого релятора соединен с вторым и с третьим переключательными входами второго релятора, первый и второй выходы i-го (i =  релятора соединены с первым переключательным входом (i + 1)-го релятора, а второй и третий переключательные входы (i + 1)-го релятора - с третьим выходом i-го релятора, первый и второй выходы (n - 1)-го релятора соединены с переключательным входом n-го релятора, выход которого подключен к третьему выходу (n - 1)-го релятора и является выходом логического устройства, отличающееся тем, что в каждый из n реляторов введен булевый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй входы которого соединены соответственно с выходом компаратора и входом управления релятора, выход булевого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ в первом и в n-м реляторах подключен к управляющему входу замыкающего ключа, а в каждом из промежуточных реляторов - к управляющему входу первого, второго и третьего ключей, входы управления всех реляторов объединены и образуют вход управления логического устройства.

релятора соединены с первым переключательным входом (i + 1)-го релятора, а второй и третий переключательные входы (i + 1)-го релятора - с третьим выходом i-го релятора, первый и второй выходы (n - 1)-го релятора соединены с переключательным входом n-го релятора, выход которого подключен к третьему выходу (n - 1)-го релятора и является выходом логического устройства, отличающееся тем, что в каждый из n реляторов введен булевый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй входы которого соединены соответственно с выходом компаратора и входом управления релятора, выход булевого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ в первом и в n-м реляторах подключен к управляющему входу замыкающего ключа, а в каждом из промежуточных реляторов - к управляющему входу первого, второго и третьего ключей, входы управления всех реляторов объединены и образуют вход управления логического устройства.

| АНАЛОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ДЛЯ ИДЕНТИФИКАЦИИ И СЕЛЕКЦИИ ЭКСТРЕМАЛЬНОГО, СУПРАЭКСТРЕМАЛЬНОГО ИЛИ СУБЭКСТРЕМАЛЬНОГО ЗНАЧЕНИЙ ИНФОРМАЦИОННОГО СИГНАЛА | 1995 |

|

RU2109338C1 |

| Волгин Л.И | |||

| Алгоритмы и устройства обработки сигналов и автоматизация проектирования | |||

| - Таллинн: Валгус, 1991, с.41 | |||

| РЕЛЯТОРНЫЙ КОММУТАТОР | 1996 |

|

RU2103735C1 |

| US 5157291 A, 20.10.1992. | |||

Авторы

Даты

1999-12-27—Публикация

1999-02-16—Подача