Изобретение относится к аналоговой вычислительной технике и автоматике и может быть использовано в устройствах допускового контроля, для ранговой обработки аналоговых сигналов по признаку их принадлежности к срединным сигналам, для групповой идентификации и селекции срединных значений информационного сигнала и др.

Известны реляторные коммутационно-логические преобразователи и устройства (см. , например, а.с. СССР 1693614, кл. G 06 G 7/25; Л.И.Волгин. Синтез устройств для обработки и преобразования информации в элементном базисе реляторов. - Таллинн: Валгус, 1989) для выделения медианного (срединного) сигнала из множества трех сигналов.

Известные устройства обладают ограниченными функциональными возможностями, так как осуществляют выделение срединного сигнала только из трех сигналов.

Наиболее близким к предлагаемому схемному решению является многопороговый функциональный преобразователь, построенный на реляторах - аналоговых логических элементах, воспроизводящих элементарные операции предикатной алгебры выбора (а. с. СССР 1621054, кл. G 06 G 7/25). Устройство в демультиплексорном включении воспроизводит логическую функцию "запрет максимальной и минимальной переменной (функцию идентификации и селекции срединных сигналов) при любом количестве сигналов.

Недостатком прототипа являются большие аппаратурные затраты (количество ключей в реляторах при увеличении числа сигналов возрастает по закону арифметической прогрессии).

Цель изобретения - уменьшение аппаратурных затрат за счет уменьшения количества ключей.

Поставленная цель достигается тем, в аналоговом логическом элементе, содержащим входной и выходной двухключевые реляторы и n-2 срединных четырехключевых реляторов, во входном двухключевом реляторе первый и второй переключательные входы соединены и образуют переключательный вход аналогового логического элемента, выход которого образуют соединенные первый и второй переключательные выходы выходного двухключевого релятора, каждый неинвертирующий компараторный вход реляторов предназначен для задающих сигналов, инвертирующие компараторные входы предназначены для информационного сигнала, отличающийся тем, что в каждом срединном четырехключевом реляторе соединены первый и второй переключательные входы и соединены третий и четвертый переключательные входы, второй и третий переключательные выходы объединены и соединены с выходом аналогового логического элемента, первый и второй переключательные выходы входного двухключевого релятора соединены с первым и четвертым переключательными входами второго четырехключевого релятора, первый и второй переключательные входы выходного двухключевого релятора соединены с четвертым и первым переключательными выходами предпоследнего четырехключевого релятора, первый и четвертый переключательные выходы каждого срединного четырехключевого релятора до (n-2)-го соединены соответственно с первым и четвертым переключательными входами последующего релятора.

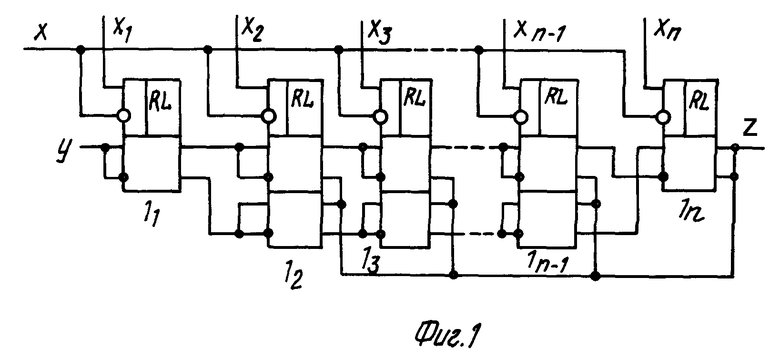

Электрическая схема аналогового логического элемента представлена на фиг. 1. На фиг. 2 представлены электрические схемы использованных в аналоговом логическом элементе четырехключевых 12oC 1n-1 (фиг. 2а) и двухключевых 11, 1n (фиг.2б) реляторов.

Положение ключей на фиг. 2 соответствует ситуации, когда xi>x, где xi (i= 1,2,..., n) есть задающие аналоговые сигналы, x - аналоговый информационный сигнал. На фиг. 1 и 2 зачерненными кружками отмечены переключательные входы ключей, состоянием которых управляют компараторы реляторов, передающие входные сигналы на размыкающие ключи 4, 6 (фиг.2а) и 4 (фиг. 2б) реляторов 11oC 1n. На фиг. 2 ключи 3, 5 (фиг. 2а) и 3 (фиг. 2б) являются замыкающими. На фиг. 1, 2 хi и xj есть аналоговые задающие сигналы (i-1,2,.., n; j = 1,2, . . . , n; i ≠j ), x -информационный (идентифицируемый) аналоговый сигнал (напряжение). На фиг. 1 y -идентифицирующий сигнал, z - выходной сигнал.

Работа аналогового логического элемента осуществляется следующим образом. Аналоговый логических элемент содержит входной 11 и выходной 1n двухключевые реляторы и n-2 срединных четырехключевых реляторов 12oC 1n-1, включенных между входным 11 и выходным 1n двухключевыми реляторами. На все неинвертирующие компараторные входы реляторов 11oC 1n в произвольном порядке от внешних источников напряжения подаются задающие сигналы x, x2,... xn. На инвертирующие компараторные входы реляторов 11oC 1n подается информационный (идентифицируемый) сигнал x (напряжение).

Первый и второй переключательные входы (входного двухключевого релятора 11 соединены и образуют вход аналогового логического элемента. Первый и второй переключательные выходы выходного двухключевого релятора 1n соединены и образуют выход аналогового логического элемента. В каждом срединном четырехключевом реляторе соединены первый и второй переключательные входы и соединены третий и четвертый переключательные входы. Второй и третий переключательные выходы в каждом срединном реляторе объединены и соединены с выходом аналогового логического элемента, а первый и четвертый переключательные выходы каждого срединного четырехключевого релятора до (n-2)-го соединены соответственно с первым и четвертым переключательными входами последующего релятора. Первый и второй переключательные выходы двухключевого входного релятора 11 соединены соответственно со вторым и четвертым переключательными входами второго четырехключевого релятора 12, а первый и второй входы выходного двухключевого релятора 1n соединены соответственно с четвертым и первым переключательными выходами предпоследнего четырехключевого релятора 1n-1.

Аналоговый логический элемент при y ≠ x воспроизводит операцию идентификации заданной ситуации:

Здесь r есть ранг (порядковый номер) информационной переменной x = x(r) в последовательности x(1), x(2),... x(n+1), полученной ранжированием задающих переменных x(1), x(2),...xn, x в порядке их возрастания.

Следовательно, идентифицирующий сигнал y появится на выходе логического элемента (z=y ≠ 0) при x ∈ {x(1),...x(n)}. Если x ∈ {x(1), x(n+1)}, то выходной сигнал z равен нулю (z=0).

При отождествлении идентифицирующей y и информационной x переменных (при y = x, т.е. переключательный выход логического элемента соединен с его информационным входом) воспроизводится операция групповой ранговой селекции информационного сигнала x= x(r) по признаку его принадлежности к заданному множеству ранговых переменных {x(2),...x(n)} выделенных из полного множества ранговых переменных x(1), x(2),..., x(n), x(n+1). Отсюда следует, что логический элемент воспроизводит операцию "запрет минимального и максимального ранговых значений информационной переменной x":

где x(1)=min(x1, x2,...,xn, x), x(n+1)=max (x1, x2,...xn, x).

Число ключей в предложенном схемном решении равно 4 (n-1), а в прототипе равно 21 +22 +... +2n. Например, если n=6, то в прототипе используется 126 ключей, а в предложенном схемном решении 20 ключей, т.е. имеем выигрыш в количестве ключей примерно в 6 раз.

Изобретение относится к вычислительной технике и автоматике и может быть использовано для ранговой обработки аналоговых сигналов. Техническим результатом является уменьшение аппаратурных затрат. Изобретение содержит входной и выходной двухключевые реляторы и срединные четырехключевые реляторы. Каждый релятор содержит компаратор, замыкающие и размыкающие ключи. 2 ил.

Аналоговый логический элемент "запрет минимального и максимального значений информационной переменной", содержащий n задающих сигналов, входной и выходной двухключевые реляторы и n - 2 срединных четырехключевых реляторов, каждый релятор содержит компаратор, который управляет состоянием замыкающих и размыкающих ключей, во входном двухключевом реляторе первый и второй переключательные входы соединены и образуют переключательный вход аналогового логического элемента, выход которого образуют соединенные первый и второй переключательные выходы выходного двухключевого релятора, каждый неинвертирующий компараторный вход реляторов предназначен для задающих сигналов, инвертирующие компараторные входы реляторов предназначены для информационного сигнала, отличающийся тем, что в каждом срединном четырехключевом реляторе соединены первый и второй переключательные входы и соединены третий и четвертый переключательные входы, второй и третий переключательные выходы объединены и соединены с выходом аналогового логического элемента, первый и второй переключательные выходы входного двухключевого релятора соединены с первым и четвертым переключательными входами второго четырехключевого релятора, первый и второй переключательные входы выходного двухключевого релятора соединены с четвертым и первым переключательными выходами предпоследнего четырехключевого релятора, первый и четвертый переключательные выходы каждого срединного четырехключевого релятора до (n - 2)-го соединены соответственно с первым и четвертым переключательными входами последующего релятора.

| Многопороговый функциональный преобразователь | 1988 |

|

SU1621054A2 |

| Медианный мультиплексор-демультиплексор | 1989 |

|

SU1693614A1 |

Авторы

Даты

1999-05-10—Публикация

1995-06-06—Подача