Изобретение относится к области аналоговой вычислительной техники и автоматики и может быть использовано для ранговой идентификации и селекции заданного на пятиэлементном множестве аналоговых сигналов информационного (выбранного) сигнала по квартильно-ранговому признаку, для допускового контроля, для сортировки сигналов и пр.

Известны аналоговые процессоры, воспроизводящие операции ранговой селекции информационного сигнала, заданного на n-элементном задающем множестве аналоговых сигналов { x1, x2, . . . , xi, . . . , xn} , которые при n= 5 по второму и четвертому выходам воспроизводят операции селекции квартильных значений х(2) и х(4), где n - число элементов задающего множества сигналов (см. а. с. 1621054, БИ 2, 1991г. , фиг. 3).

При использовании таких процессоров для квартильной селекции они обладают аппаратурной избыточностью за счет незадействованных ключей реляторов.

Наиболее близким к предлагаемому схемному решению является реляторный коммутационно-логический преобразователь для идентификации и селекции минимального и супраминимального или максимального и субмаксимального значений информационного сигнала, который при n= 5 на задающем множестве аналоговых сигналов хi = xri (i= 1, 2, 3, 4, 5) воспроизводит операции групповой идентификации минимального х(1) и первого квартального х(2) значений или максимального х(5) и второго квартильного x(2) значений информационного сигнала, так как при n= 5 супраминимальное x(2) и первое квартильное х(2) значения или субмаксимальное x(4) и второе квартильное х(4) значения совпадают, где ri есть ранг информационного сигнала хi (см. патент 2109338, БИ 11,1998г. , фиг. 1).

Недостатком прототипа являются ограниченные функциональные возможности, так как при групповой идентификации минимальное х(1) и первое квартильное х(2) значения, максимальное х(5) и субмаксимальное х(5) значения совпадают.

В предлагаемом схемном решении указанный недостаток (неразличимость) устранен, что расширяет его функциональные возможности по сравнению с прототипом.

Указанный технический эффект достигается тем, что в процессор с одним информационным и одним идентифицирующим входами, содержащий первый одноканальный, второй двухканальный, третий трехканальный демультиплексорные реляторы, для которых первый и второй выходы первого релятора соединены соответственно с первым и вторым переключательными входами второго релятора, первый, второй и третий выходы которого соединены соответственно с первым, вторым и третьим переключательными входами третьего релятора, введен четвертый мультиплексорный двухканальный релятор, первым и вторым выходами которого являются объединенные выходные выводы размыкающего и замыкающего ключей первого и второго каналов релятора, первым, вторым, третьим и четвертым переключательными входами введенного релятора являются входные выводы размыкающих и замыкающих ключей первого и второго каналов введенного релятора, которые присоединены соответственно к первому, второму, третьему и четвертому выходам третьего релятора, а инвертирующий вход компаратора введенного релятора присоединен к информационному входу реляторного процессора, при этом свободные сигналы задающего кортежа в произвольном порядке подаются на неинвертирующие входы всех четырех компараторов реляторов.

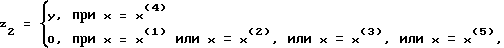

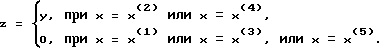

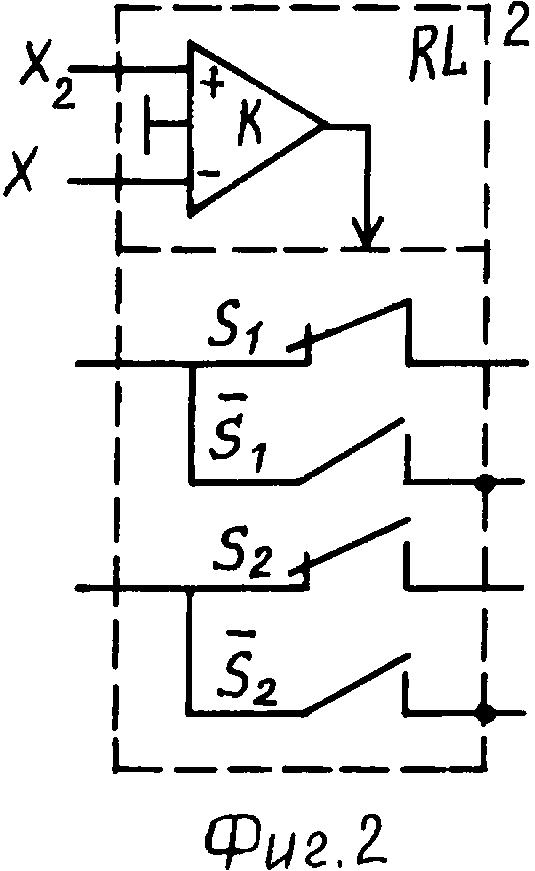

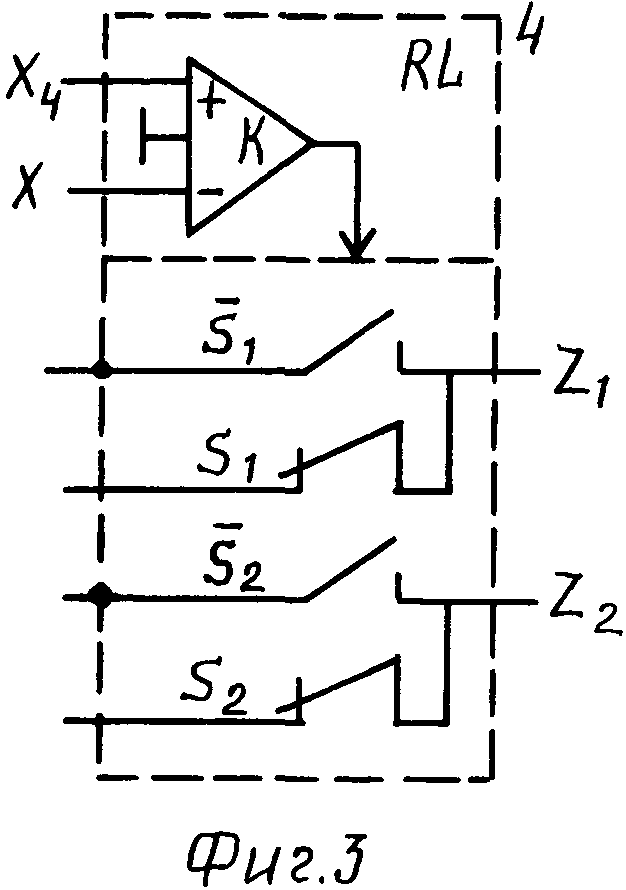

На фиг. 1 представлена схема реляторного процессора; на фиг. 2 и 3 изображены схемы соответственно демультиплексорного и мультиплексорного двухканальных реляторов.

Реляторный процессор (фиг. 1) содержит первый одноканальный 1, второй двухканальный 2, третий трехканальный 3 демультиплексорные реляторы (схема демультиплексорного двухканального релятора 2 изображена на фиг. 2) и четвертый мультиплексорный релятор 4, изображенный на фиг. 3. Каждый релятор состоит из компаратора К, выход которого соединен с управляющим входом его переключательных каналов, состоящих из размыкающего Sj замыкающего  ключей (на фиг. 1, 2, 3 выводы размыкающих ключей отмечены зачерненными кружками). Положение ключей на фиг. 2,3 соответствует ситуации, когда сигнал хk (напряжение) на неинвертирующем компараторном входе релятора больше напряжения х на его инвертирующем входе (отмечен незачерненным кружком). При xk<х (k= 1, 2, 3, 4, 5) имеем обратную картину. Для фиг. 1 на информационный вход реляторного процессора подается сигнал х= x5. принадлежащий задающему множеству сигналов x1, х2, х3, x4, x5. В общем случае в качестве информационной переменной хi может быть выбран любой сигнал, принадлежащий задающему множеству сигналов. Остальные свободные сигналы x1, х2, . . . , хi-1, xi+1, . . . , хn-1, xn в произвольном порядке подаются на компараторные (задающие) неинвертирующие входы компараторов реляторов 1, 2, 3, 4, 5, где n - число элементов задающего множества сигналов (в нашем случае n= 5).

ключей (на фиг. 1, 2, 3 выводы размыкающих ключей отмечены зачерненными кружками). Положение ключей на фиг. 2,3 соответствует ситуации, когда сигнал хk (напряжение) на неинвертирующем компараторном входе релятора больше напряжения х на его инвертирующем входе (отмечен незачерненным кружком). При xk<х (k= 1, 2, 3, 4, 5) имеем обратную картину. Для фиг. 1 на информационный вход реляторного процессора подается сигнал х= x5. принадлежащий задающему множеству сигналов x1, х2, х3, x4, x5. В общем случае в качестве информационной переменной хi может быть выбран любой сигнал, принадлежащий задающему множеству сигналов. Остальные свободные сигналы x1, х2, . . . , хi-1, xi+1, . . . , хn-1, xn в произвольном порядке подаются на компараторные (задающие) неинвертирующие входы компараторов реляторов 1, 2, 3, 4, 5, где n - число элементов задающего множества сигналов (в нашем случае n= 5).

Объединенные входные выводы ключей первого релятора 1 являются идентифицирующим входом реляторного процессора, на который подается идентифицирующий сигнал у (режим идентификации). Если в качестве идентифицирующего сигнала использовать информационный сигнал (при у= х), реляторный процессор работает в режиме селекции (выделения) информационного сигнала.

Каждый переключательный канал реляторов имеет один замыкающий и один размыкающий ключ, входные выводы которых объединены и образуют переключательные входы демультиплексорных реляторов 1, 2, 3. В мультиплексорном двухканальном реляторе 4, первым и вторым выходами которого являются объединенные выходные выводы размыкающего и замыкающего ключей первого и второго каналов, образующих первый (z1) и второй (z2) выходы реляторного процессора. Первым, вторым, третьим и четвертым переключательными входами мультиплексорного релятора 4 являются входные выводы размыкающих и замыкающих ключей соответственно первого и второго переключательных каналов.

В первом реляторе выходные выводы замыкающего и размыкающего ключей  являются его выходами. Второй двухканальный релятор 2 имеет первый, второй и третий выходы, в качестве которых соответственно используются выходной вывод замыкающего ключа первого канала 21, объединенные выходные выводы размыкающего ключа первого канала 21 и замыкающего ключа второго канала 22, выходной вывод размыкающего ключа второго канала 22. Третий релятор 3 имеет первый, второй, третий и четвертый выходы, в качестве которых соответственно используются выходной вывод замыкающего ключа первого канала 31, объединенные выходные выводы размыкающего ключа первого канала 31 и замыкающего ключа второго канала 32, объединенные выходные выводы размыкающего ключа второго канала 32; и выходной вывод замыкающего ключа третьего канала 33, выходной вывод размыкающего ключа третьего канала 33.

являются его выходами. Второй двухканальный релятор 2 имеет первый, второй и третий выходы, в качестве которых соответственно используются выходной вывод замыкающего ключа первого канала 21, объединенные выходные выводы размыкающего ключа первого канала 21 и замыкающего ключа второго канала 22, выходной вывод размыкающего ключа второго канала 22. Третий релятор 3 имеет первый, второй, третий и четвертый выходы, в качестве которых соответственно используются выходной вывод замыкающего ключа первого канала 31, объединенные выходные выводы размыкающего ключа первого канала 31 и замыкающего ключа второго канала 32, объединенные выходные выводы размыкающего ключа второго канала 32; и выходной вывод замыкающего ключа третьего канала 33, выходной вывод размыкающего ключа третьего канала 33.

Первый и второй выходы первого релятора 1 соединены соответственно с первым и вторым переключательными входами второго релятора 2. Первый, второй и третий выходы второго релятора 2 соединены соответственно с первым, вторым и третьим переключательными входами третьего релятора 3. Первый, второй, третий и четвертый выходы третьего релятора 3 соединены соответственно с первым, вторым, третьим и четвертым переключательными входами четвертого мультиплексорного релятора 4.

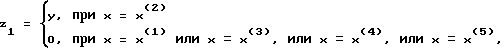

Реляторный процессор воспроизводит логические операции индивидуальной рангово-квартильной идентификации и селекции (при у= х) заданной на пятиэлементном множестве сигналов информационного сигнала х:

где  = xi (i= 1, 2, 3, 4, 5) есть ранговые переменные, ri - ранг информационного сигнала xi =

= xi (i= 1, 2, 3, 4, 5) есть ранговые переменные, ri - ранг информационного сигнала xi =  , т. е. порядковый помер информационного сигнала х= хi= var в последовательности x(1)= min (x1, . . . , х5), х(2), х(3), х(4), х(5)= max (x1, . . . , x5), полученной ранжированием задающего множества сигналов { x1, х2, x3, x4, x5} в порядке их возрастания.

, т. е. порядковый помер информационного сигнала х= хi= var в последовательности x(1)= min (x1, . . . , х5), х(2), х(3), х(4), х(5)= max (x1, . . . , x5), полученной ранжированием задающего множества сигналов { x1, х2, x3, x4, x5} в порядке их возрастания.

Отсюда следует, что при х= х(2), т. е. когда информационный сигнал имеет первое квартильное значение, идентифицирующий сигнал у проходит на первый выход z1= у, а на втором выходе z2 сигнал отсутствует.

Аналогично, когда информационный сигнал х= х(4) принимает второе квартильное значение х= х(4), идентифицирующий сигнал у проходит на второй выход z2= у, а z1= 0.

При работе в режиме селекции приведенные выражения для z1 и z2 остаются в силе при замене в них "у" на "х".

При объединении первого и второго выходов (z1= z2= z) реляторный процессор воспроизводит логическую операцию групповой идентификации первого и второго квартильных значений информационного сигнала х= var:

В отличие от прототипа ранговый процессор (фиг. 1) осуществляет индивидуальную идентификацию и селекцию информационного сигнала, а также возможна и групповая идентификация квартильных значений информационного сигнала.

Изобретение относится к аналоговой вычислительной технике и может быть использовано для ранговой идентификации и селекции заданного на пятиэлементном множестве аналоговых сигналов информационного (выбранного) сигнала по квартильно-ранговому признаку, для допускового контроля, для сортировки сигналов. Техническим результатом является расширение функциональных возможностей. Устройство содержит одноканальный, двухканальный, трехканальный демультиплексорные реляторы, двухканальный мультиплексорный релятор, состоящие из компаратора, замыкающих и размыкающих ключей. 3 ил.

Реляторный процессор для идентификации и селекции квартильных значений информационного сигнала, заданного на пятиэлементном множестве сигналов, содержащий первый одноканальный, второй двухканальный, третий трехканальный демультиплексорные реляторы, каждый релятор содержит компаратор, выходное напряжение которого управляет состоянием замыкающих и размыкающих ключей переключательных каналов, каждый переключательный канал реляторов имеет один замыкающий и один размыкающий ключ, входные выводы которых объединены и образуют переключательные входы реляторов, в первом одноканальном реляторе выходные выводы ключей являются его выходами, второй двухканальный релятор имеет первый, второй и третий выходы, в качестве которых соответственно используются выходной вывод замыкающего ключа первого канала, объединенные выходные выводы размыкающего ключа первого канала и замыкающего ключа второго канала, выходной вывод размыкающего ключа второго канала, третий релятор имеет первый, второй третий и четвертый выходы, в качестве которых соответственно используются выходной вывод замыкающего ключа первого канала, объединенные выходные выводы размыкающего ключа первого канала и замыкающего ключа второго канала, объединенные выходные выводы размыкающего ключа второго канала и выходной вывод замыкающего ключа третьего канала, выходной вывод размыкающего ключа третьего канала, все инвертирующие входы компараторов реляторов присоединены к информационному входу реляторного процессора, на который подается один из сигналов задающего множества сигналов, на переключательный вход первого релятора подается идентифицирующий сигнал реляторного процессора, первый и второй выходы первого релятора соединены соответственно с первым и вторым переключательными входами второго релятора, первый, второй и третий выходы которого соединены соответственно с первым, вторым и третьим переключательными входами третьего релятора, отличающийся тем, что в схему реляторного процессора введен четвертый мультиплексорный двухканальный релятор, первым и вторым выходами которого являются объединенные выходные выводы размыкающего и замыкающего ключей первого и второго каналов введенного релятора, первым, вторым, третьим и четвертым переключательными входами являются входные выводы размыкающих и замыкающих ключей первого и второго каналов введенного релятора и присоединены соответственно к первому, второму, третьему и четвертому выходам третьего релятора, а инвертирующий вход компаратора введенного релятора присоединен к информационному входу реляторного процессора, при этом свободные сигналы задающего кортежа сигналов в произвольном порядке подаются на неинвертирующие входы всех четырех компараторов реляторов.

| АНАЛОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ДЛЯ ИДЕНТИФИКАЦИИ И СЕЛЕКЦИИ ЭКСТРЕМАЛЬНОГО, СУПРАЭКСТРЕМАЛЬНОГО ИЛИ СУБЭКСТРЕМАЛЬНОГО ЗНАЧЕНИЙ ИНФОРМАЦИОННОГО СИГНАЛА | 1995 |

|

RU2109338C1 |

| Многопороговый функциональный преобразователь | 1988 |

|

SU1621054A2 |

| РАНГОВЫЙ ПРОЦЕССОР ДЛЯ ИДЕНТИФИКАЦИИ И СЕЛЕКЦИИ СУБМЕДИАННОГО, МЕДИАННОГО И СУПРАМЕДИАННОГО ЗНАЧЕНИЯ ИНФОРМАЦИОННОГО СИГНАЛА | 1998 |

|

RU2154299C1 |

| Многопороговый функциональный преобразователь | 1989 |

|

SU1679507A1 |

| SU 1568061 A1, 30.05.1990 | |||

| US 5642070 A, 24.06.1997 ВОЛГИН Л.И | |||

| Синтез устройств для обработки и преобразования информации в элементном базисе реляторов | |||

| - Таллинн: Валгус, 1989, с | |||

| Автоматический огнетушитель | 0 |

|

SU92A1 |

Авторы

Даты

2002-01-27—Публикация

2001-01-30—Подача