Устройство относится к области вычислительной техники, а именно к системам встроенного контроля, и может найти применение в аппаратуре, где используется цифровая обработка информации.

Известно устройство контроля мультиплексора канала ввода-вывода информации [Машина бортовая цифровая вычислительная ЦВМ20-700 ТО.6Ф3.031.055 ТО. Часть 1. Общие сведения, 1981 г.; Машина бортовая цифровая вычислительная БЦВМ20-700 6Ф3. 031.055. Т01. Приложение. Альбом иллюстраций, 1981 г.], в котором в передаваемых кодах отведены контрольные биты и в контрольном канале проведено соединение выходных бит с входными.

При правильной передаче информации ЦВМ работает обычным образом. В случае обнаружения ошибки в контрольном канале при бите формируется сигнал "Отказ ЦВМ" и машина отключается, недостатком данного устройства является невозможность автоматического устранения ошибок, выявленных в процессе контроля в работающей машине.

В качестве прототипа принято устройство контроля, реализованное в процессоре ввода-вывода ЦВМ-100 [Изделие Ц100-2. Руководство по технической эксплуатации ОЯ. 700.048-02 РЭ. - Июль 10/87, стр. 42; Коротков Е.И. и др. ЦВМ - 100. Архитектура и основы математического обеспечения - М.: ВВИА, 1991, стр. 48. ] , которое является наиболее близким по технической сущности. Оно состоит из устройства ввода информации (УВИ1...УВИ9), регистров приема информации (РПИ1. . .РПИ9), схемы приоритета, мультиплексора (Ms), устройства ввода информации (УВИ1...УВИ9), по сигналам из центрального процессора (ЦП) управляет приемом информации от датчиков в регистры приема информации (РП1.. . РП9). Эти же устройства после приема кодов в РПИ выдают "сигнал - заявку" ввода в схему приоритета. Если заявка ввода сформирована одновременно несколькими УВИ, то схема приоритета, управляя мультиплексором, определяет очередность записи информации в буферную память (ПБ). Каждый поступающий последовательный код содержит контрольный разряд четности - нечетности информации, правильность которого также проверяется в УВИ, при обнаружении ошибки приема информации вырабатывается сигнал прерывания. Контроль правильности передачи информации в схеме "РПИ - М3 - ПБ" в стандартном процессоре ввода - вывода отсутствует. При появлении сбоев в работе мультиплексора в буферную память записывается искаженная информация.

Недостатком прототипа является то, что при передаче информации через мультиплексор ошибка не обнаруживается, т.к. на этом этапе контроль правильности передачи информации не производится.

Техническим результатом изобретения является обнаружение ошибок в передаваемой информации через мультиплексор и их автоматическая коррекция.

Сущность изобретения состоит в том, что устройство самоконтролирующегося мультиплексора процессора ввода-вывода ЦВМ, содержащее мультиплексор, схему приоритета, устройства ввода информации и регистры приема информации РПИ1 .. . РПИ9, входы которых соединены с выходами соответствующих датчиков, а выходы регистров приема информации РПИ2 ... РПИ9 соединены со 2-м и 9-м входами мультиплексора, 10-й вход которого соединен с выходом схемы приоритета, и ее вход соединен с соответствующими выходами устройств ввода информации УПИ1 . .. УПИ9, входы которых соединены с выходами центрального процессора, дополнительно содержит регистр контроля, схему адаптации и схему "ИЛИ", вход которой соединен с выходами устройств ввода информации УВИ1 ... УВИ9, а выходы схемы "ИЛИ" соединен с 1-ми входами схемы адаптации и регистра контроля, 2-й вход которого соединен с выходом регистра приема информации РПИ1, а выход регистра контроля соединен с 2-м входом схемы адаптации и 1-м входом мультиплексора, выход которого соединен с соответствующим входом буферной памяти через 3-й вход схемы адаптации 7.

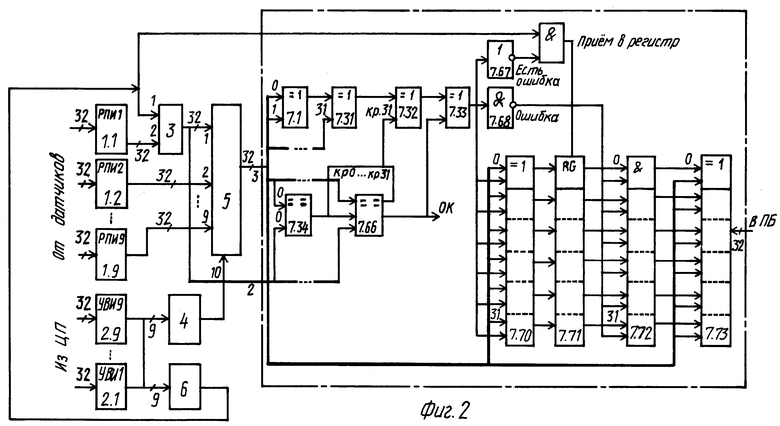

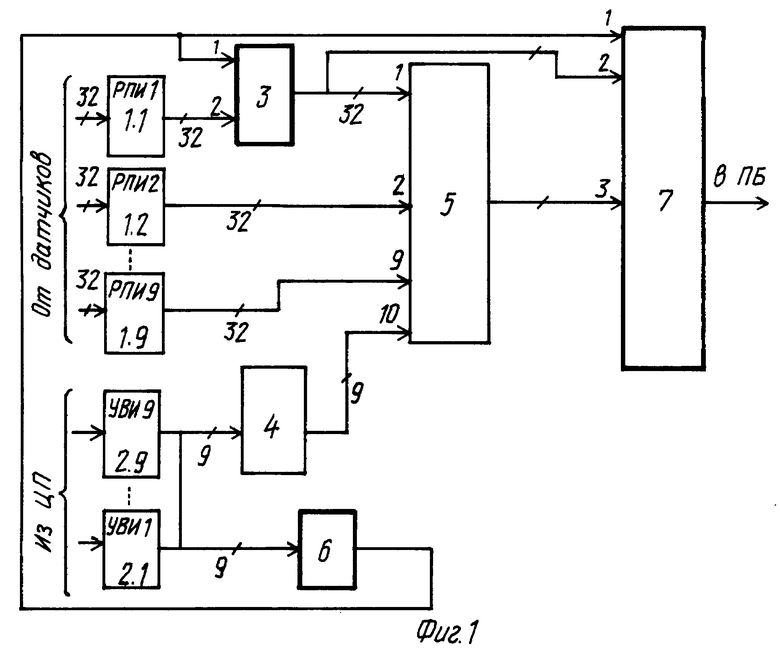

На фиг. 1 показана структурная схема устройства самоконтролирующегося мультиплексора процессора ввода - вывода ЦВМ. На фиг. 2 приведен пример технической реализации данного устройства.

Структурная схема устройства (фиг. 1) состоит из регистров приема информации (РПИ1 . .. РПИ9) 1.1 ... 1.9 устройств ввода информации (УВИ1 ... УВИ9) 2.1 ... 2.10, регистра контроля 3, схемы приоритета 4, мультиплексора 5, схемы "ИЛИ", схемы адаптации 7.

Работа устройства состоит в следующем. При отсутствии заявок ввода информации по всем девяти каналам, поступающим от устройства ввода информации 2.1 ... 2.9, на выходе схемы 6 формируется сигнал, обнуляющий через 1-е входы регистр контроля 3 и схему адаптации 7, подготавливая их к работе. Контрольное число (нулевой код) из регистра контроля 3 подается на 1-й вход мультиплексора 5. По разрешающему сигналу от схемы приоритета 4, поступающему на 10-й вход мультиплексора 5, контрольный код передается из регистра контроля 3 на 1-й вход мультиплексора 5 и с его выхода на 3-й вход схемы адаптации 7. На второй вход схемы адаптации 7 контрольный код подается непосредственно из регистра контроля 3. В схеме адаптации 7 коды поразрядно сравниваются и при обнаружении ошибки схема адаптации 7 настраивается на коррекцию сбойных разрядов, поступающих из мультиплексора 5 в очередном сеансе ввода информации, который начинает при поступлении заявок ввода от устройств ввода информации 2.1 ... 2.9. При отсутствии ошибки схема адаптации 7 пропускает поступающую информацию без изменений в буферную память (ПБ).

Устройство самоконтролирующегося мультиплексора процесса ввода - вывода может быть выполнено, например, как показано на фиг. 2. Здесь в режиме контроля неисправности мультиплексора 5 контрольный (нулевой) код из регистра контроля через мультиплексор 5 поступает на 2-ой вход схемы адаптации 7 на сборки элементов "Исключающее ИЛИ" 7.70 и 7.73, а также на схемы сравнения на элементах: 7.1 ... 7.32 и 7.34 ... 7.66 на 32-х элементах каждая. Через 3-й вход схемы адаптации 7 контрольный код подается на схему сравнения 7.34 . .. 7.66 непосредственно из регистра контроля. Коды поразрядно сравниваются в схеме сравнения 7.34 ... 7.66, в результате чего формируются контрольные разряды КР0 ... КР31 и сигнал интегральной исправности ОК = 1. При КР = 0 (i = 0 ... 31) сигнал ОК = 1, что соответствует исправному состоянию мультиплексора 5, а при КР = 1 (i = 0 ... 51) сигнал ОК = 0 - мультиплексор неисправен. В схеме 7.70 выполняется логическая операция "Исключающее ИЛИ" над кодом, поступающим с выхода мультиплексора 5, и сигналом ОК с выхода схемы сравнения 7.34 . .. 7.66. В результате формируется 32-х разрядный код, содержащий информацию о сбойных разрядах, который параллельно подается на вход регистра хранения ошибки 7.71.

Схема сравнения, выполненная на элементах 7.1 ... 7.32 анализирует поступающую информацию на четность-нечетность и через элемент 7.68 управляет сборкой 7.22. При отсутствии ошибок (сбойных разрядов) в передаваемой информации через мультиплексор 5 содержимое регистра хранения ошибки 7.71 равно нулю. В противном случае в схеме 7.69 формируется разрешение записи в регистры хранения ошибки 7.71 кода и схемы 7.70 и в соответствующих разрядах регистра 7.71 запишутся единицы. В результате в схеме адаптации 7 имеется информация о неисправности мультиплексора.

При реализации очередного сеанса ввода информации, в соответствии с реализованным в схеме приоритетов 4 алгоритме приоритета, по ее разрешающему сигналу, поступающему на 10-й вход мультиплексора 5, определяется очередность записи информации в буферную память. Регистр контроля 3 в этом случае только пропускает информацию по первому каналу. С выхода мультиплексора 5 передаваемый числовой код подается на вход схемы 7.73. Одновременно на эту же схему подается хранимый в регистре 7.71 код коррекции ошибок. В схеме 7.73 в соответствии с логикой "Исключающее ИЛИ" происходит исправление сбойных разрядов в передаваемом коде. В результате на выходе адаптации 7 появится 32-х разрядный код с устраненными ошибками.

В очередном случае отсутствия заявок ввода по всем девяти каналам описанные выше процессы повторяются, что ведет к постоянному в процессе работы ЦВМ контролю состояния мультиплексора и адаптации его к возникающим ошибкам.

Конструктивно схема адаптации 7 может быть выполнена на микросхемах 153 и 555 серий.

Экспериментальные исследования заявляемого устройства показали, что по сравнению с прототипом обеспечивает 100% передачу достоверной информации и позволяет автоматизировать процесс обнаружения и корректировку ошибок во время работы, что расширяет функциональные возможности ЦВМ. Использование данного устройства, например, в бортовой ЦВМ, где в случае обнаружения сбойного блока происходит отказ самой ЦВМ, позволяет продолжить работу ЦВМ и выполнить поставленную задачу.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ И УСТРОЙСТВО СЕЛЕКЦИИ ДВИЖУЩИХСЯ НАЗЕМНЫХ ЦЕЛЕЙ В ТРЕХКАНАЛЬНОЙ ЦИФРОВОЙ РСА | 1998 |

|

RU2205423C2 |

| УСТРОЙСТВО ДЛЯ РЕАЛИЗАЦИИ ПРОСТРАНСТВЕННО-ВРЕМЕННОЙ ОБРАБОТКИ ИЗОБРАЖЕНИЙ НА ОСНОВЕ МАТРИЦ ФОТОЧУВСТВИТЕЛЬНЫХ ПРИБОРОВ С ЗАРЯДОВОЙ СВЯЗЬЮ | 2007 |

|

RU2358408C2 |

| Устройство для преобразования телевизионных стандартов | 1990 |

|

SU1811644A3 |

| УСТРОЙСТВО ДЛЯ МНОГОКАНАЛЬНОЙ ОБРАБОТКИ ИНФОРМАЦИИ | 1992 |

|

RU2060602C1 |

| СПОСОБ ОПРЕДЕЛЕНИЯ ДИЭЛЕКТРИЧЕСКИХ ХАРАКТЕРИСТИК ПОЛИМЕРОВ | 1998 |

|

RU2166768C2 |

| ЦИФРОВОЙ КОМПЕНСАТОР ПОМЕХ | 1998 |

|

RU2154838C2 |

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ КАЧЕСТВА ПИЛОТИРОВАНИЯ САМОЛЕТА ЛЕТЧИКОМ | 1998 |

|

RU2136046C1 |

| Устройство для преобразования телевизионных стандартов | 1990 |

|

SU1811643A3 |

| Устройство для умножения частоты | 1991 |

|

SU1836681A3 |

| СПОСОБ АДАПТАЦИИ СИСТЕМЫ СОПРОВОЖДЕНИЯ МАНЕВРЕННОЙ ВОЗДУШНОЙ ЦЕЛИ ПО ДАЛЬНОСТИ НА ОСНОВЕ ИНФОРМАЦИИ ОТ ИЗМЕРИТЕЛЕЙ РАЗЛИЧНОЙ ФИЗИЧЕСКОЙ ПРИРОДЫ | 2005 |

|

RU2303797C2 |

Изобретение относится к вычислительной технике, в частности к устройствам контроля цифровой аппаратуры. Технический результат заключается в обнаружении ошибок в передаваемой информации через мультиплексор и их автоматической коррекции. Технический результат достигается за счет того, что в штатное устройство ввода-вывода дополнительно вводятся регистр контроля, логический элемент и схема адаптации, которая осуществляет прием и анализ поступающих кодов на предмет сбойных разрядов. В случае их обнаружения вырабатывается сигнал на их коррекцию. 2 ил.

Устройство самоконтролирующегося мультиплексора процессора ввода-вывода ЦВМ, содержащее мультиплексор, схему приоритета, устройства ввода информации УВИ1...УВИ9 и регистры приема информации РПИ1...РПИ9, входы которых соединены с выходами соответствующих датчиков, а выходы регистров приема информации РПИ2...РПИ9 соединены с входами мультиплексора, десятый вход которого соединен с выходом схемы приоритета, а ее вход соединен с соответствующими выходами устройств ввода информации УВИ1...УВИ9, входы которых предназначены для соединения с выходами центрального процессора, отличающееся тем, что оно дополнительно содержит регистр контроля, схему адаптации и схему ИЛИ, вход которой соединен с выходами устройств ввода информации УВИ1...УВИ9, выход схемы ИЛИ соединен с первыми входами схемы адаптации и регистра контроля, второй вход которого соединен с выходом регистра приема информации РПИ1, а выход регистра контроля соединен со вторым входом схемы адаптации и первым входом мультиплексора, выход которого соединен с третьим входом схемы адаптации, предназначенной для передачи поступающей информации в буферную память.

| Коротков Е.И | |||

| и др., ЦВМ-100 | |||

| Архитектура и основы математического обеспечения | |||

| - М.: ВВИА, 1991, с | |||

| Приспособление для автоматической односторонней разгрузки железнодорожных платформ | 1921 |

|

SU48A1 |

| Самоконтролируемый мультиплексор | 1985 |

|

SU1302270A1 |

| Универсальный логический модуль | 1987 |

|

SU1476457A1 |

| JP 03041541 A, 22.02.91 | |||

| Прибор для промывания газов | 1922 |

|

SU20A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Общие сведения | |||

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

Авторы

Даты

2000-01-20—Публикация

1998-06-02—Подача