Изобретение относится к области обработки цифровых сигналов. В частности, изобретение относится к системе, предназначенной для облегчения работы транспортного процессора при обработке потока структурированных в виде полей данных, пригодного для передачи информации в системе телевидения высокого разрешения.

Недавние разработки в области обработки видеосигнала привели к созданию систем для обработки и передачи сигналов цифрового телевидения высокого разрешения (высокой четкости). Одна такая система описана в патенте США N 5168356. В этой системе на транспортный процессор подается поток данных, который состоит из кодовых слов в стандарте, совместимом с известным стандартом сжатия MPEG. Основной функцией транспортного процессора является упаковка данных, состоящих из кодовых слов переменной длины, с получением упакованных слов данных. Совокупности упакованных слов данных, которую называют пакетом данных или ячейкой данных, предшествует заголовок, содержащий, помимо прочей информации, информацию, идентифицирующую соответствующие слова данных. Таким образом, на выходе транспортного процессора создается поток пакетированных данных, состоящий из последовательности транспортных пакетов. Использование транспортных пакетов повышает возможность восстановления синхронизации и восстановления сигнала в приемнике, например, после пропадания сигнала, которое может произойти из-за нарушения в канале передачи. Это достигается благодаря заголовку данных, с помощью которого приемник при потере или нарушении передаваемых данных может определить точки повторного входа в поток данных.

Система наземного телевизионного вещания высокого разрешения, недавно предложенная в качестве системы телевидения высокого разрешения Большого Альянса в США, использует для передачи пакетированного потока данных с заранее заданной структурой поля данных формат цифровой передачи с частично подавленной боковой полосой. Система телевидения высокого разрешения Большого Альянса представляет собой предлагаемый стандарт передачи, который сейчас рассматривается в США Федеральной комиссией связи в ее Консультативном комитете по перспективному телевидению. Описание системы телевидения высокого разрешения Большого Альянса в том виде, как оно было направлено в Техническую подгруппу Консультативного комитета по перспективному телевидению 22 февраля 1994 года (проект документа), опубликовано в Трудах Национальной ассоциации вещательных организаций за 1994 год, 48th Annual Broadcast Engineering Conference Proceedings, March 20-24, 1994.

В системе Большого Альянса данные организованы в последовательность полей данных. Каждая структура поля включает 313 сегментов: сегмент синхронизации поля (который не содержит полезной информации), за которым следуют 312 сегментов данных. Каждый сегмент данных включает компоненту данных и компоненту прямой коррекции ошибок (ПКО). Каждый сегмент данных предваряется компонентой синхронизации. Транспортный процессор выдает пакеты с фиксированной длиной в 188 байтов в процессор передачи, который осуществляет различные функции кодирования для каждого пакета с формированием выходных символьных сегментов для их подачи в выходной канал передачи. Каждый байт содержит заранее заданное количество символов, например 4 символа. Пакеты данных содержат данные в соответствии со стандартом сжатия MPEG-2, разработанным Международной организацией по стандартизации (Группой экспертов по движущимся изображениям). Транспортный процессор вырабатывает только пакеты данных для процессора передачи, который добавляет вспомогательную компоненту обнаружения и коррекции ошибки для прямой коррекции ошибок в каждый сегмент, и вспомогательный сегмент синхронизации поля в начало каждого поля данных, т. е. между каждой группой сегментов полей данных. Для осуществления этих операций скорость потока данных должна регулироваться, поскольку, как будет видно в дальнейшем, вспомогательные компоненты прямой коррекции ошибок и вспомогательный сегмент синхронизации поля имеют место в разное время и имеют разную длительность.

Пакеты разделяются интервалами, которые позволяют транспортному процессору вставить в поток данных вспомогательные данные, необходимые для каждого сегмента (например, данные прямой коррекции ошибок). Однако, когда нужно вставить в поток данных сегмент синхронизации поля большей длины, который не содержит полезных данных, как другие пакеты, поток упакованных данных необходимо прервать и задержать на время, равное интервалу сегмента. Поток данных, созданный с учетом необходимости его прерывания и вставки в него вспомогательной информации различной длительности (данных прямой коррекция ошибок или синхронизации поля), иллюстрируется на фиг. 3. Этот поток данных содержит между интервалами синхронизации поля пакеты длиной 312 байтов плюс интервалы прямой коррекции ошибок, как будет обсуждаться в дальнейшем.

Авторы установили, что прерываемый поток данных, как описано выше, не только нежелательно уменьшает скорость прохождения данных, но и приводит к образованию между пакетами данных неодинаковых интервалов. Существование таких неодинаковых интервалов между пакетами значительно усложняет обработку сигнала.

В частности, авторы установили, что прерываемый поток данных нежелательно повышает требования к интерфейсу между транспортным процессором и процессором передачи в передатчике, особенно в отношении синхронизации данных, а также между любыми системами для записи пакетированного потока данных. Весьма вероятно, что поток данных телевидения высокого разрешения будет записываться на студийной аппаратуре или аппаратуре потребителя. Чтобы удовлетворить требованиям к синхронизации стандарта MPEG, любая система записи должна без искажений воспроизводить синхронизацию пакетов, включая любые неодинаковые промежутки между пакетами, которые, если они имеются, должны вставляться между пакетами. Эти требования значительно увеличивают сложность схем, необходимых в качестве интерфейса для системы записи. Кроме того, любой такой промежуток, сформированный средствами обработки для передачи, должен быть выдержан в демодуляторе приемника.

Предпочтительно настоящее изобретение используется в системе, предназначенной для обработки пакетированного потока данных, представляющего заранее заданные последовательные структуры полей данных. Система согласно изобретению избавляет от необходимости выравнивания структур полей данных, которые могут относиться к типу, характеризующемуся неодинаковой скоростью следования данных из-за различия типа вспомогательной (служебной), т.е. не содержащей данных, информации разной длительности, например такой, какая используется в описанной выше системе телевидения высокого разрешения Большого Альянса.

В передатчике транспортный процессор (например, для формирования пакетов данных с соответствующими заголовками) работает с постоянной равномерной скоростью следования данных без прерывания в системе, которая вставляет вспомогательную информацию, не содержащую данные различной длительности в поток данных с формированием заранее заданной последовательной структуры полей данных. Предпочтительно, транспортный процессор работает с такой постоянной равномерной скоростью поступления данных без необходимости модификации заранее заданной первоначальной структуры поля данных. Этот процесс осуществляется за счет передачи данных из транспортного процессора в связанную с ним схему интерфейса/буфера в ответ на заранее заданный тактовый сигнал.

Согласно изобретению, в передатчике в тракте потока данных, идущих с постоянной скоростью с выхода транспортного процессора, установлено устройство видеозаписи/воспроизведения.

Соответствующий транспортный процессор/декодер в приемнике аналогично осуществляет непрерывную обработку с постоянной равномерной скоростью данных.

В описанном варианте выполнения передатчика согласно настоящему изобретению для обеспечения подачи байтов данных в схему буферного интерфейса с равномерной скоростью данных транспортный процессор работает с постоянной равномерной скоростью поступления данных без прерывания, реагируя на сигнал синхронизации 3/8 СТ, где СТ - системный тактовый сигнал. Реагируя на сигнал синхронизации 3/8 СТ, буфер записывает данные и считывает данные с неравномерной скоростью с выдачей их в схему формирования поля данных. Схема формирования поля работает с неравномерной скоростью следования данных и, реагируя на данные, содержащие байты, и на вспомогательную информацию, не содержащую данных, выдает последовательность выходных структур символьных полей. Схема формирования поля данных запрашивает данные с неравномерной скоростью. Схема интерфейса преобразует этот запрос в запрос с постоянной скоростью следования данных для транспортного процессора.

В описанном варианте выполнения приемника согласно настоящему изобретению принятый поток символов характеризуется последовательной структурой полей данных. Устройство обработки поля данных обрабатывает принятую структуру поля символьных данных с неравномерной скоростью и формирует выходные данные, идущие с неравномерной скоростью. Схема интерфейсного буфера реагирует на тактовый сигнал 3/8 СТ считывания и преобразует эти данные в выходной поток байтов данных в формате MPEG, характеризующийся постоянной равномерной скоростью следования данных. Этот поток данных обрабатывается транспортным декодером, который, реагируя на тактовый сигнал 3/8 СТ, осуществляет непрерывную обработку с постоянной равномерной скоростью следования данных.

На чертежах:

на фиг.1 иллюстрируется последовательная структура полей данных, включающая сегменты синхронизации и данных,

на фиг. 2 изображена блок-схема, иллюстрирующая в общих чертах устройство для обработки пакетированного потока данных,

на фиг.3 изображен пакетированный поток данных, в котором между пакетами данных имеются неравномерные вспомогательные интервалы,

на фиг. 4 изображена блок-схема устройства кодирования в передатчике, которое включает схему буфера/интерфейса и схему структурирования полей данных согласно изобретению, которые реагируют на входные пакетированные байтовые данные с выдачей в канал передачи выходных символов,

на фиг. 5 иллюстрируется спектр телевизионного сигнала, который может быть использован для передачи выходных данных, сформированных системой, показанной на фиг. 4; он показан в сравнении со спектром обычного телевизионного сигнала в системе NTSC,

на фиг. 6-16 изображены сигналы, характеризующие работу системы передатчика, показанной на фиг.4,

на фиг. 17 изображена блок-схема расположенного в приемнике декодера, который включает устройство обработки поля данных в основной полосе частот и схему буфера/интерфейса согласно изобретению, которые реагируют на входные пакетированные символьные данные с выдачей в транспортный процессор выходных байтовых данных,

на фиг. 18-27 изображены сигналы, характеризующие работу системы приемника, показанной на фиг. 17,

на фиг. 28 и 29 более подробно показаны узлы систем, изображенных на фиг. 4 и 17 соответственно,

на фиг. 30-32 изображены сигналы, которые полезны для понимания работы системы, выполненной согласно изобретению,

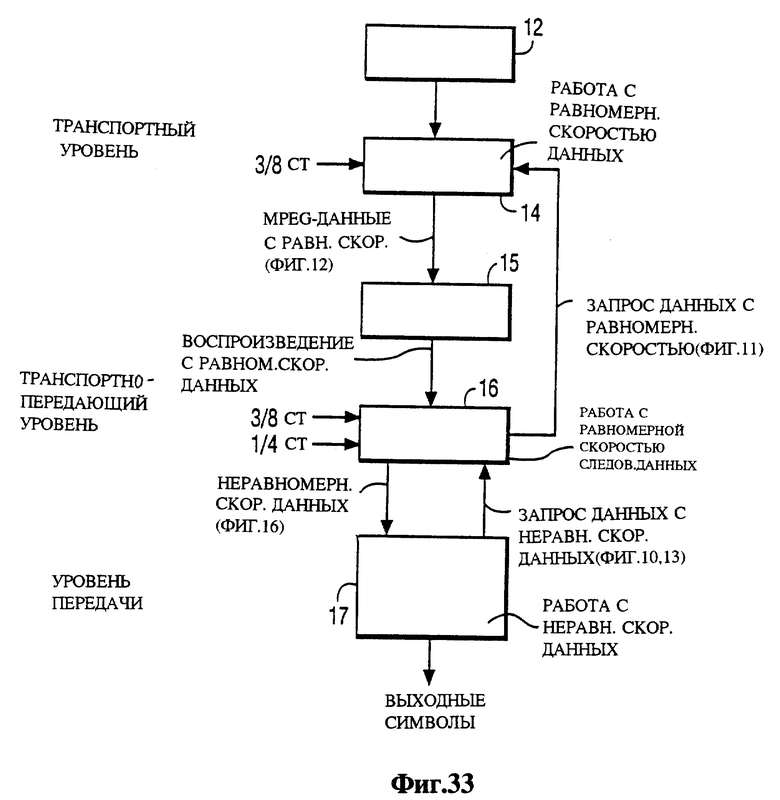

на фиг. 33 и 34 иллюстрируются устройства, изображенные на фиг. 4 и 17 соответственно, применительно к системе видеозаписи/воспроизведения.

На фиг. 1 изображена структура полей данных системы телевидения высокого разрешения Большого Альянса в США для использования в системе обработки пакетированного потока данных. Выходной поток символьных данных, представляющий структуру полей данных, формируется процессором передачи в ответ на пакеты входных данных из предыдущего транспортного процессора. Процессор передачи и транспортный процессор будут описаны в связи с фиг. 4. Каждая структура полей данных включает вспомогательный сегмент синхронизации поля (который не содержит полезных данных), предшествующий группе сегментов данных поля, каждый из которых имеет соответствующую компоненту синхронизации. Каждый сегмент данных поля включает компоненту пакета данных из 187 байтов, компоненту синхронизации из одного байта перед каждым сегментом данных и компоненту прямой коррекции ошибок после данных. Каждому сегменту соответствует интервал "Y", определяющий интервал запрета данных между каждым пакетом данных. Транспортный процессор выдает пакеты входных данных по 188 байтов плюс сегмент синхронизации в процессор передачи. Процессор передачи добавляет вспомогательную информацию, касающуюся кодирования для прямой коррекции ошибок и синхронизации поля, и выдает выходные сегменты в символьной форме для передачи их в выходной канал передачи.

Компонента синхронизации, соответствующая каждому сегменту, и компонента синхронизации поля облегчают установление синхронизации символов и пакетов и фазовую автоподстройку в приемнике в условиях избыточного шума и помех. Четырехсимвольная компонента синхронизации является бинарной (2-уровневой) для того, чтобы повысить надежность восстановления пакетов и импульсов синхронизации, и представляет собой сигнал, который периодически повторяется с уникальной частотой, чтобы обеспечить надежное обнаружение в приемнике в условиях шума и помех. Символы синхронизации не кодируются по методу Рида-Соломона или с использованием решетчатого кода и не подвергаются перемежению. Компонента синхронизации поля может содержать псевдослучайные последовательности и служит для нескольких целей. Она обеспечивает средство для определения начала каждого поля данных, а также может быть использована адаптивным выравнивателем в приемнике как опорная обучающая последовательность для удаления межсимвольных и других искажений. Кроме того, она обеспечивает средство, с помощью которого приемник может определить, использовать или нет фильтр подавления помех, и может применяться для диагностических целей, например для измерения отношения сигнал-шум и частотной характеристики канала. Кроме того, компонента синхронизации может использоваться в схемах слежения за фазой в приемнике для определения параметров в контуре управления фазой. Как и компонента синхронизации, компонента синхронизации поля не кодируется кодом коррекции ошибок или решетчатым кодом и не перемежается. В этом примере поля данных не обязательно соответствуют чередующимся полям изображения, которые составляют кадр изображения в телевизионном сигнале в стандарте NTSC.

На фиг. 2 иллюстрируется в общих чертах обработка сегмента 22 поля данных одного типа блоками процессора передачи и выходного процессора, изображенными на фиг. 4. Этот сегмент представляет собой один из 312 сегментов данных заданного поля данных, состоящий из 832 символов. Сегмент, иллюстрируемый на фиг. 2, содержит 187 байтов пакета транспортных данных в формате MPEG-2, перед которыми следует компонента синхронизации, содержащая один байт, а после следует соответствующая компонента прямой коррекции ошибок, содержащая 20 байтов контроля по четности кода Рида-Соломона. Каждый транспортный пакет при использовании в системе телевидения высокого разрешения Большого Альянса включает 4-байтовый заголовок связи, первый байт которого является байтом синхронизации для облегчения синхронизации пакетов. За ним может следовать необязательный заголовок адаптации, а оставшуюся часть пакета составляют полезные данные формата MPEG. Однобайтовая компонента синхронизации перед тем, как подвергнуться двухпозиционной модуляции с частичным подавлением боковой полосы, преобразуется в 4 символа. 187-байтовый сегмент пакета в формате MPEG и компонента кодирования прямой коррекции ошибок перед тем, как подвергнуться 8-позиционной модуляции с частичным подавлением боковой полосы, кодируются решетчатым кодом со скоростью кода 2/3 и преобразуются в 828 символов. Способы осуществления такой 2-позиционной и 8- позиционной модуляции с частичным подавлением боковой полосы хорошо известны. Полученный в результате выходной сегмент 24 поля, который передается в выходной канал, содержит 4-символьную компоненту синхронизации, за которой следует 828-символьная компонента поля данных, содержащая данные формата MPEG и данные прямой коррекции ошибок.

На фиг. 3 представлен поток пакетов данных в соответствии со структурой полей данных, изображенной на фиг. 1. Каждое поле данных имеет 312 сегментов, каждый из которых включает компоненты синхронизации, данных и прямой коррекции ошибок. Более конкретно, каждый сегмент поля данных содержит интервал, который охватывает 188 байтов данных, включая сигнал синхронизации ("пакетные байты"), и интервал, который охватывает 20 байтов кода прямой коррекции ошибок. В каждом сегменте 188 байтов данных соответствуют 188 интервалам (периодам) тактового сигнала, а каждые 20 байтов кодов прямой коррекции ошибок соответствуют 20 интервалам (периодам) тактового сигнала. Когда наступает время вставки сегмента синхронизации поля, передача сегментов данных/прямой коррекции ошибок должна быть задержана на 228 периодов тактового сигнала, что соответствует интервалу синхронизации сегмента (т.е. 20+188+20 периодов тактового сигнала). Сегмент синхронизации поля не содержит полезных данных, которые содержатся в каждом сегменте пакетных данных. Этот разрыв в потоке данных вызывает нежелательные неравные интервалы или промежутки между пакетами, как показано на фиг. 3. Такой прерываемый поток данных и неодинаковые промежутки между пакетами очень усложняют управление данными и повышают требования к оборудованию, относящемуся к интерфейсу между транспортным процессором и процессором передачи как в приемнике, так и в передатчике, а также уменьшают скорость следования данных. Более того, при воспроизведении записанных материалов трудно осуществить синхронизацию структуры полей данных. Неодинаковые промежутки между пакетами очень осложняют задачу записи потока пакетных данных на студийном оборудовании или оборудовании потребителя, поскольку неравные промежутки между пакетами должны быть сохранены там, где они находятся, т.е. записывающее оборудование должно верно воспроизводить синхронизацию пакета MPEG. Кроме того, неравные промежутки должны быть сохранены в выходном сигнале, производимом демодулятором в приемнике.

Описанные проблемы, вызванные неравными промежутками между пакетами и связанные с нерегулярностью вспомогательных данных, рассматриваются и решаются системой, выполненной согласно настоящему изобретению. В описываемой системе транспортный процессор обрабатывает пакеты данных с постоянной равномерной скоростью следования данных в ответ на тактовый сигнал, который зависит от используемой схемы модуляции данных. Этот сигнал синхронизации управляет также работой блока буфера/интерфейса, расположенного между транспортным процессором и устройствами уровня передачи, который обрабатывает данные в соответствии с заранее заданной структурой поля данных. Преимущество описываемой системы заключается в том, что для достижения желаемой работы с постоянной равномерной скоростью следования данных нет необходимости модифицировать первоначальную структуру поля данных. Кроме того, не оказывается воздействия на такие параметры, как скорость следования символов, перемежение сегментов, а также на компоненты синхронизации и кодирования с коррекцией ошибок по методу Рида-Соломона.

В системе передатчика (фиг. 4) согласно настоящему изобретению транспортный процессор 14 работает с постоянной равномерной скоростью следования данных без прерывания и выдает байтовые данные в стандарте MPEG с равномерной скоростью следования данных в блок 16 буферного интерфейса. Интерфейс 16 выдает байтовые данные с неравномерной скоростью в блок 17 формирования поля данных и кодирования. Блок 17 работает при неравномерной скорости следования данных и в ответ на байтовые данные и вспомогательную информацию, не содержащую данные (данные синхронизации поля и прямой коррекции ошибок), выдает последовательность структур выходных полей символов. Блок 17 запрашивает данные с неравномерной скоростью посредством сигнала Запрос Пакета Поля Данных. Блок 16 интерфейса преобразует этот запрос в сигнал запроса с равномерной скоростью следования данных (Запрос Пакета Для Транспортировки), который подается в транспортный процессор 14.

Более конкретно, транспортный процессор 14 относится к системному транспортному уровню, а блок 17 относится к системному уровню передачи (куда входит также выходной процессор 18), который отделен от транспортного уровня интерфейсом 16. Источник 12 данных содержит схему сжатия данных, совместимую со стандартом MPEG, и выдает байтовые данные в формате MPEG-2 в транспортный процессор 14. Транспортный процессор 14 упаковывает байты формата MPEG в слова данных фиксированной длины, которые в конце концов группируются в пакеты данных фиксированной длины (188 байтов). Каждый пакет предваряется заголовком, содержащим пояснительную информацию об источнике программы, типе службы и другую информацию, описывающую полезные данные в соответствующем пакете и относящуюся к ним. Кроме того, в начало каждого пакета транспортный процессор 14 вставляет 1-байтовый сигнал синхронизации пакета формата MPEG. Процессор 10 передачи осуществляет операции, которые включают входную буферизацию, кодирование для прямого обнаружения/коррекции ошибок, вставку сигнала синхронизации поля, решетчатое кодирование для улучшения отношения сигнал-шум, перемежение для уменьшения влияния групп ошибок, возникающих при передаче пакета данных, и символьное преобразование.

Блок 17 осуществляет функцию формирования поля данных, в то время как входные пакеты данных формируются в структуру полей данных, включающую данные, а также компоненты синхронизации поля и прямой коррекции ошибок, как описано ранее. Пакеты данных из блока 16 интерфейса в блок 17 следуют с постоянными равномерными промежутками между пакетами так, что поля данных формируются блоком 17 "без стыков" и без прерывания потока данных. Система передачи на фиг. 4 работает, реагируя на символьные тактовые импульсы (СТ) и тактовые импульсы, полученные на их основе, как будет описано ниже. Подходящая частота символьных тактовых импульсов равна 10,762237 МГц.

Описанная система согласно настоящему изобретению позволяет транспортному процессору работать при равномерной скорости следования данных без модификации первоначальной структуры поля данных, содержащей, например, один сегмент синхронизации поля на каждые 312 сегментов данных, с формированием равномерного потока данных с 313-сегментным полем. Более того, нет необходимости прерывать поток данных для вставки между полями данных вспомогательной информации о синхронизации поля.

Система передатчика, изображенного на фиг. 4, использует тактовые импульсы 1/4 СТ и 3/8 СТ, где СТ - символьный тактовый сигнал системы. Выбор для обработки сигнала тактового сигнала 1/4 СТ, как будет показано ниже, обусловлен тем, что один байт (8 битов) содержит 4 символа при 2 битах на символ. Тактовый сигнал 3/8 СТ предпочтителен для систем с 8-позиционной модуляцией с частичным подавлением боковой полосы, в то время как тактовый сигнал 3/4 СТ, также находящийся в рамках настоящего изобретения, предпочтителен для более быстрых систем с 16-позиционной модуляцией с частичным подавлением боковой полосы. В системе, которая будет описана ниже, блок 16 содержит между выходом транспортного процессора 14 и входом блока 17 формирования поля данных буфер 46 обратного магазинного типа. Пакеты байтовых данных считываются из транспортного процессора 14 и записываются в буфер 46 в ответ на тактовые импульсы 3/8 СТ, а из буфера 46 пакеты данных считываются и подаются в кодер 17 в ответ на тактовые импульсы 1/4 СТ. Оба этих тактовых импульса предпочтительно вырабатываются цифровым устройством, а не более дорогой схемой с фазовой автоподстройкой. Тактовые импульсы 3/8 СТ синхронизируют работу как транспортного процессора 14, так и буфера 46 так, что данные между транспортным процессором и буфером передаются синхронно. Как будет описано ниже, аналогичные требования предъявляются к приемнику.

На фиг. 6-9 символьные тактовые импульсы СТ (фиг. 6) и полученные из них синхронные тактовые импульсы 1/4 СТ (фиг. 7) генерируются схемой 40 управления синхронизацией, например микропроцессором, в блоке 17. Схема 40 генерирует также сигнал Запрос Пакета Поля Данных (фиг. 10), который синхронизирован с символьным тактовым импульсом СТ, так как для генерации сигнала Запрос Пакета Поля Данных используются тактовые импульсы 1/4 СТ. Генератор 42 тактового сигнала в блоке 16 генерирует тактовые импульсы 3/8 СТ (фиг. 8), которые синхронизированы с тактовыми импульсами СТ и тактовыми импульсами 1/4 СТ из схемы 40 синхронизации. На фиг. 9 (приведенной только для ссылки) изображен импульс длиной в 1 байт, связанный с появлением однобайтового импульса синхронизации в качестве первого байта в начале каждого пакета данных.

Тактовые импульсы 3/8 СТ генерируются путем подсчета тактовых импульсов СТ. Блок 42 генерирует три выходных импульса на каждые восемь тактовых импульсов СТ. На фиг. 7 и 8 иллюстрируется одно возможное соотношение между тактовыми импульсами 1/4 СТ и тактовыми импульсами 3/8 СТ. Для выработки тактовых импульсов 3/8 СТ подходит любая комбинация из 3 тактовых импульсов в пределах интервала из 8 тактовых импульсов, однако между этими тремя импульсами и тактовыми импульсами 1/4 СТ должно существовать фиксированное фазовое соотношение, и точно такое же соотношение должно поддерживаться между тактовыми импульсами 1/4 СТ и тактовыми импульсами 3/8 СТ в приемнике и передатчике. Иллюстрируемая на фиг.8 структура тактовых импульсов 3/8 СТ является предпочтительной, поскольку этот сигнал легко преобразовать и выровнять с байтом синхронизации (который легко обнаружить в начале каждого пакета), а также легко повторить в приемнике. Аналогичные замечания относятся к использованию любых шести из восьми тактовых символьных импульсов для генерации тактовых импульсов 3/4 СТ для сигнала с 16-позиционной модуляцией с частичным подавлением боковой полосы. Иллюстрируемое соотношение между показанными тактовыми импульсами осуществляется в схеме 40 контроля синхронизации путем сброса счетчика передним фронтом тактовых импульсов 1/4 СТ, в результате чего из буфера 46 выдается байт синхронизации пакета. Счетчик символов считает от 0 до 7, причем 0 синхронизируется с байтом синхронизации пакета, который выдается из буфера 46. Могут быть использованы любые три из восьми отсчетов счетчика тактовых импульсов СТ, однако в приемнике/декодере должны быть использованы такие же три отсчета.

Схема 40 управления синхронизацией обеспечивает возможность генерации структуры поля данных, содержащей 312 сегментов данных и один сегмент синхронизации поля. В ответ на тактовые импульсы 1/4 СТ сигнал Запрос Пакета Поля Данных (фиг. 10, 13) из схемы 40 имеет высокий логический уровень в течение 188 байтов и низкий логический уровень в течение 20 байтов. Сигнал Запрос Пакета Поля Данных из контроллера 40 (фиг. 10) имеет неравномерные промежутки между пакетами. Изображена часть поля данных, в частности два последних сегмента 311 и 312 данных одного поля данных, сегмент 313 синхронизации поля перед началом следующего поля данных и первый сегмент данных следующего поля данных. Этот сигнал содержит интервалы "разрешения" данных, когда данные запрашиваются (каждый содержит 188 байтов данных, синхронизированных со 188 тактовыми импульсами 1/4 СТ), интервалы "запрещения" данных (каждый содержит 20 тактовых импульсов 1/4 СТ), когда в поток данных должна быть добавлена информация прямой коррекции ошибок, или интервалы длиной 228 тактовых импульсов 1/4 СТ, когда между полями данных должна быть добавлена информация, касающаяся синхронизации поля. Этот сигнал является автономным входным сигналом для схемы 44 управления системой в блоке 16.

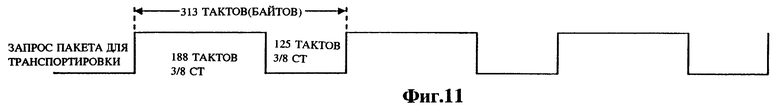

Схема 44 управления реагирует на тактовые импульсы 3/8 СТ и тактовые импульсы 1/4 СТ и генерирует на своем выходе сигнал Запрос Пакета Для Транспортировки, как показано на фиг. 11. Этот сигнал запрашивает 188-байтовый пакет данных из транспортного процессора 14 при каждом 313-ом тактовом импульсе 1/4 СТ. Для формирования равномерной скорости следования данных и потока данных без прерывания этот сигнал Запрос Пакета имеет постоянные равномерные промежутки между запросами пакета. Постоянные равномерные промежутки длиной в 125 тактовых импульсов 3/8 СТ между запросами пакета облегчают вставку блоком 17 вспомогательных данных, например информации о прямой коррекции ошибок и синхронизации поля, между полями данных в поток данных "без стыков" и прерывания для создания структуры полей данных, как будет объяснено впоследствии.

Описываемое изобретение касается обработки потока данных, имеющего структуру поля с 313 сегментами на поле, включающего сегмент синхронизации поля, за которым следуют 312 сегментов поля данных. В этом контексте описываемая система будет работать с тактовыми импульсами, частота следования которых кратна тактовым импульсам 3/8 СТ, например с более быстрыми тактовыми импульсами, включая тактовые импульсы 3/4 СТ, 3/2 СТ и 3 СТ, в схемах, например, 8-позиционной модуляции с частичным подавлением боковой полосы или 16-позиционной модуляции с частичным подавлением боковой полосы. Эти опции будут лучше поняты из последующего обсуждения фиг.10, 11-30, 31 и 32. Из этого обсуждения станет ясно также, что принципы настоящего изобретения применимы и к другим типам структур полей данных.

Форма сигнала, показанного на фиг. 10, является постоянной для описываемого варианта со структурой полей данных, включающих 313 сегментов. Структура сигнала, изображенного на фиг. 11, может меняться в зависимости от некоторых факторов следующим образом. Фиг. 30 соответствует фиг. 11, на которой изображен сигнал Запрос Пакета, имеющий равномерную скорость следования данных и посылаемый из схемы 44 в транспортный процессор 14 в ответ на тактовые импульсы 3/8 СТ для 8-позиционной модуляции с частичным подавлением боковой полосы. Если для 8-позиционной модуляции с частичным подавлением боковой полосы используются тактовые импульсы 3/4 СТ, идущие с вдвое большей частотой, то форма сигнала Запрос Пакета, направляемого в транспортный процессор 14, будет такой, как показано на фиг. 31. Поскольку размер каждого пакета данных фиксирован и равен 188 байтам, интервал пакета данных остается неизменным и равным 188 тактовым импульсам 3/4 СТ. Однако интервалы запрета данных между пакетами значительно возрастают и достигают 438 тактовых импульсов 3/4 СТ. В этом примере число тактовых импульсов в каждом сегменте возросло до 626 (вдвое больше, чем в предыдущем примере) благодаря возрастанию в два раза частоты байтовых тактовых импульсов 3/4 СТ. Другими словами:

626 тактовых импульсов в сегменте - 188 тактовых импульсов (фиксированная величина) = 438 тактовых импульсов.

Хотя число байтов на сегмент возросло, структура пакета данных не изменилась. Структура поля данных также не изменилась, поскольку каждое поле данных по-прежнему содержит 312 сегментов, каждый из которых содержит 188-байтовый пакет данных, перед которым находится сегмент синхронизации поля. Аналогичные замечания относятся и к импульсам синхронизации большей кратной частоты, например 3/2 СТ или 3 СТ, при которых количество тактовых импульсов в интервале между пакетами данных возрастает пропорционально. Было определено, что частота тактовых импульсов 3/8 СТ является минимальной частотой для синхронизации 313 байтов на сегмент в поле данных из 313 сегментов.

На фиг. 32 иллюстрируется использование тактовых импульсов 3/8 СТ, которые имеют большую частоту следования, в системе с 16-позиционной модуляцией с частичным подавлением боковой полосы. В случае 16-позиционной модуляции с частичным подавлением боковой полосы частота тактовых импульсов увеличивается вдвое, при этом, по сравнению с системой с 8-позиционной модуляцией с частичным подавлением боковой полосы, в единицу времени проходит в два раза больше пакетов. Интервал данных длиной в 188 тактовых импульсов и интервал запрета данных между данными длиной в 125 тактовых импульсов такие же, как в случае с 8-позиционной модуляцией с частичным подавлением боковой полосы, из-за связи между частотой тактовых импульсов и скоростью данных при соответствующем типе модуляции. Более низкая частота тактовых импульсов 3/8 СТ при более низкой скорости данных для 8-позиционной модуляции с частичным подавлением боковой полосы - это то же самое, что более высокая частота тактовых импульсов 3/4 СТ при более высокой скорости данных для 16-позиционной модуляции с частичным подавлением боковой полосы. Можно показать, что желаемое соотношение (например, 3/8 СТ, 3/4 СТ и т.д.) тактовых импульсов может быть получено в соответствии со следующим выражением, которое определяет число символов на поле:

NX(188 + Y) = S(X + 1),

где X(188 +Y) и S(X+ 1) - число символов на поле;

188 + Y - число символов на сегмент данных;

X+1 - число сегментов в поле (например, 313);

S - число символов на сегмент (например, 832);

X - число сегментов данных в поле (например, 312);

Y - интервал между данными;

N - множитель, который требуется определить.

N равно 8/3 в случае тактовых импульсов 3/8 СТ при 8-позиционной модуляции с частичным подавлением боковой полосы, и N равно 4/3 в случае тактовых импульсов 3/4 СТ.

При считывании данных транспортный процессор синхронизирован тактовыми импульсами 3/8 СТ, а реагируя на сигнал Запрос Пакета из блока 44, он в течение 188 периодов тактовых импульсов 3/8 СТ выдает пакет данных длиной 188 байтов в формате MPEG, как представлено на фиг. 12. В действительности на фиг. 12 изображен сигнал Данные Истинны, который выдается транспортным процессором 14 одновременно с выдачей 188-байтовых пакетов данных. Сигнал Данные Истинны имеет форму сигнала Запрос Пакета Для Транспортировки (фиг. 11). Сигнал Запрос Пакета Поля Данных из схемы 40 синхронизации блока 17 (фиг. 10) не синхронизирован с сигналом Запрос Пакета Для Транспортировки из схемы 44 (фиг. 11).

Пакеты данных из транспортного процессора 14 (Данные) подаются в буфер 46 блока 16. Этот буфер относительно мал, он рассчитан на несколько пакетов. Чтобы разрешить запись пакетов данных в буфер 46 в ответ на тактовые импульсы записи 3/8 СТ (WCK), буфер 46 также получает на свой вход разрешения записи (WEN) сигнал Данные Истинны. Кроме того, из транспортного процессора 14 в буфер 46 подается флаг Начало Пакета (SOP). Этот флаг генерируется в начале каждого пакета данных одновременно с байтом синхронизации, который предваряет каждый пакет. Запросы в транспортный процессор 14 на посылку пакета данных в блок 17 через блок 16 интерфейса не обслуживаются до тех пор, пока буфер 46 не достигнет заранее заданного уровня заполнения, например половины всего объема. Индикация уровня заполнения буфера 46 осуществляется с помощью флага Заполнение, который подается на управляющий вход контроллера 44.

188-байтовый пакет данных помещается в буфер 46 каждые 188/313 периодов тактовых импульсов 3/8 СТ (фиг.11 и 12). В течение оставшихся 125 периодов тактовых импульсов 3/8 СТ в буфер 46 обратного магазинного типа запись данных не производится. Скорость поступления данных на вход буфера 46 равномерна и в точности равна скорости выдачи данных из буфера 46. Скорость выдачи данных управляется сигналом Запрос Пакета Кадра Данных из схемы 40. Сигнал Запрос Пакета Кадра Данных и сигнал Запрос Пакета Для Транспортировки не синхронизированы, но связаны между собой за счет соотношения между тактовыми импульсами 3/8 СТ и тактовыми импульсами 1/4 СТ.

Контроллер 44 содержит логические схемы, реагирующие на тактовые импульсы 3/8 СТ, сигнал Запрос Пакета Поля Данных, флаг Заполнение Буфера (фиг. 15) из буфера 46 и флаг Начало Пакета (SOP), получаемый из схемы 45 выравнивания через буфер 46. Чтобы разрешить считывание данных транспортного пакета из буфера в блок 17 в соответствующие моменты времени, контроллер 44 выдает сигнал управления (фиг. 14) на вход разрешения считывания (REN) буфера 46. Это происходит так, как изображено на фиг. 13-16. Сигнал, изображенный на фиг. 13, аналогичен сигналу, изображенному на фиг. 10 и описанному выше.

В норме сигнал разрешения считывания (фиг. 14) синхронизирован с сигналом Запрос Пакета Данных Поля (фиг. 13). Флаг Начало Пакета, который в норме появляется в начале каждого пакета данных, заставляет контроллер 44 выдать сигнал на вход разрешения считывания буфера 46, чтобы запретить буферу считывание данных. Конкретно, контроллер 44 запрограммирован так, что, реагируя на флаг Начало Пакета, он считывает из буфера 46 188 байтов, затем прекращает считывание в течение интервала сигнала прямой коррекции ошибок длиной 20 байтов. Это позволяет схеме 50 прямой коррекции ошибок в кодере 17 передачи вычислить информацию, касающуюся прямой коррекции ошибок, для пакета, который непосредственно предшествует текущему пакету, хранимому в буфере 46. Эта информация, касающаяся коррекции ошибок, вставляется в поток данных в течение 20-байтового вспомогательного интервала прямой коррекции ошибок в конце предшествующего пакета. Как сигнал Запрос Пакета Поля Данных (фиг. 13), так и сигнал разрешения считывания, когда он присутствует (фиг. 14), имеют структуру, характеризующуюся неравномерными промежутками между пакетами, необходимыми для вставки 20-байтовой вспомогательной информации схемой 50 блока 17 и для вставки блоком 58 вспомогательной информации о синхронизации поля большей длительности. Эта вставка вспомогательной информации осуществляется без прерывания потока данных.

Возвратимся к описанию фиг. 4. Вставка сегмента синхронизации поля без остановки и прерывания потока облегчается путем синхронизации считывания/записи в буфере 46 в сочетании с заранее заданным уровнем заполнения буфера. По мере запроса пакетов они непрерывно записываются в буфер 46 из транспортного процессора. В течение одного периода поля данных точное количество байтов данных, необходимое для формирования поля данных, будет передано из транспортного процессора 14 в буфер 46. Буфер 46 относительно мал, в этом примере он вмещает лишь 4 пакета данных. Заранее заданный уровень заполнения буфера составляет 2 пакета данных, но этот уровень может изменяться в соответствии с требованиями конкретной системы. На практике этот уровень следует определить так, чтобы для известных интервалов данных и интервалов запрета данных в данной системе буфер не переполнился, когда считывание из него будет остановлено для вставки в поток данных вспомогательной информации, и не опустел в остальное время. Когда считывание из буфера временно остановлено для вставки в поток данных вспомогательной информации (например, сигнала синхронизации поля), пакеты данных продолжают записываться в буфер 46 с постоянной равномерной скоростью (фиг.11). В течение этого времени буфер 46 не заполняется до конца. Постоянные равномерные промежутки между пакетами данных (фиг. 11) предоставляют буферу 46 достаточно времени, чтобы вновь заполниться, пока считывание данных из него временно запрещено для вставки вспомогательной информации. После того, как в течение интервала запрета считывания вспомогательные данные вставлены, данные вновь считываются из буфера 46. В течение всего этого времени транспортный процессор 14 непрерывно посылал пакеты данных в буфер 46, в результате чего, в то время как транспортный процессор 14 обрабатывает данные без прерывания, поток данных течет без прерывания.

При использовании более высокой частоты синхронизации, например 3/4 СТ, 3/2 СТ, буфер 46 не опустеет, поскольку интервалы между пакетами в режиме 8-позиционной модуляции с частичным подавлением боковой полосы длиннее. Это дает буферу дополнительное время для повторного заполнения из транспортного процессора.

Если флаг Заполнение Буфера имеет низкий логический уровень, указывая, что буфер 46 содержит меньше заранее заданного количества пакетов, то контроллер 44 также отменяет сигнал разрешения считывания для буфера 46. В это время сигнал Данные Истинны из схемы 44 (фиг. 16) является "низким" (отсутствует), поскольку считывание из буфера 46 запрещено. Эта ситуация может возникнуть, например, при запуске системы или после системного сброса, например в момент Т1. Обычно структура поля данных инициируется в начале дня передачи и с этого момента передача пакетов данных продолжается без перерыва до выхода станции из работы в конце дня передачи. В течение этого времени, в те промежутки, когда считывание из буфера 46 запрещено, транспортный процессор в ответ на сигнал Запрос Пакета Для Транспортировки из контроллера 44 продолжает посылать пакеты данных в буфер 46. После того, как заранее заданное число пакетов будет записано и условие заполнения буфера будет удовлетворено, состояние флага Заполнение (фиг. 15) изменится на высокий логический уровень. В буфер 46 опять будет подан сигнал разрешения считывания, что разрешит ему выдачу пакетов данных. Операция разрешения считывания для буфера инициируется передним фронтом первого интервала разрешения данных, который появится после того, как, в ответ на выполнение условия заполнения, флаг Заполнение будет установлен равным высокому логическому уровню. Следовательно, в момент Т2 первый байт (синхронизации) пакета данных выравнивается с началом запроса пакета из сигнала Запрос Пакета Поля Данных (фиг. 13) и с началом сигнала Данные Истинны (фиг. 16).

Схема 45 выравнивания на фиг. 4 облегчает вышеупомянутую операцию, которая иллюстрируется фиг. 13 - 16. Схема 45 показана на фиг. 28 совместно с блоками 17, 42, 44 и 46, изображенными на фиг. 4. Схема 45 выравнивания содержит включенные каскадно D-триггеры (регистры) 102 и 104, которые синхронизируются тактовыми импульсами считывания 1/4 СТ из буфера 46 и которые разблокируются подачей на вход буфера 46 сигнала разрешения считывания (REN) из системного контроллера 44. Данные из буфера 46 через триггеры 102 и 104 подаются в кодер 17 передачи. Реагируя на флаг Начало Пакета (SOP) (задержанная регистром копия входного сигнала Начало Пакета) с выхода триггера 102, контроллер 44 вырабатывает сигнал разрешения считывания для буфера. Сигнал Начало Пакета представляет собой задержанную копию сигнала Начало Пакета на входе буфера 46.

Вернемся к фиг. 4. С выхода блока 45 байтовые данные в параллельном коде по 8 битов и сигнал Данные Истинны (фиг. 16) подаются на соответствующие входы блока 50 прямой коррекции ошибок в кодере 17 передачи. Блок 50 прямой коррекции ошибок добавляет 20 байтов данных прямой коррекции ошибок в поток данных в течение вспомогательных интервалов "данные неистинны" между каждыми интервалами пакета данных в соответствии с формой сигнала, показанной на фиг. 16. Поток данных из блока 50 прямой коррекции ошибок подается в преобразователь 52 параллельных данных в последовательные. Блок 52 преобразует каждый байт из 8 параллельных битов в группу из четырех двухбитовых слов, которые подаются на выход последовательно. Используя хорошо известные способы, данные из блока 52 кодируют в блоке 54 решетчатыми кодами со скоростью кода 2/3 с формированием на выходе трех битов (два информационных бита и один вычисленный избыточный бит) для каждых двух битов на входе для улучшения характеристики сигнал-шум. Эти биты вычисляются согласно заранее заданному алгоритму, примеры которого хорошо известны специалистам в данной области. Кодер 54 работает совместно с блоком 56 генерации битов, который формирует третий бит в соответствии с заранее заданным алгоритмом.

На выходе кодера 54 решетчатого кода формируется последовательность из 3-битовых слов решетчатого кода, причем четыре 3-битовых слова составляют байт. Преобразователь 58 символов преобразует каждое 3-битовое слово, поступающее на его вход из кодера 54, в один выходной символ и осуществляет временное мультиплексирование этих выходных символов с поступающей из блока 60 компонентой синхронизации поля, значение которой задано заранее, с формированием выходного символьного потока данных. Согласно функции преобразования блока 58, восемь последовательно возрастающих двоичных значений, полученных из блока 54, от 000, 001, 010,... до 111, преобразуются в следующие восемь символьных уровней соответственно: -7 -5 -3 -1 +1 +3 +5 +7.

Сигналы управления для генератора 60 синхронизации поля и преобразователя 58 формируются схемой 40 управления синхронизацией, например микропроцессором. Схема 40 управляет работой генератора 60 так, что блоку 60 разрешено выдавать информацию, касающуюся сегмента синхронизации поля, в течение интервала заранее заданной длительности между соседними полями данных, то есть после каждых 312 сегментов данных, как описано выше. Каждый сегмент синхронизации поля мультиплексирован предсказуемым путем в поток данных между группами данных поля без прерывания потока данных, как отмечено выше при описании буфера 46. Мультиплексор 58 также заменяет компоненту синхронизации формата MPEG в начале каждого пакета на сигнал синхронизации сегмента перед окончательной обработкой в блоке 18.

8-уровневый символьный сигнал данных из блока 58 подается в выходной процессор 18, где к подавленной высокочастотной несущей может быть добавлен малый пилот-сигнал для обеспечения устойчивого восстановления несущей в приемнике в сложных условиях приема. Используя известные способы обработки сигнала, модулятор 8-позиционной модуляции с частичным подавлением боковой полосы в процессоре 18 принимает составной сигнал, содержащий решетчатые коды, фильтрует его и формирует спектр сигнала для передачи его через стандартный телевизионный канал с полосой частот 6 МГц, модулирует (преобразует с повышением частоты) сигнал данных в несущую промежуточной частоты (ПЧ) и переносит сигнал на несущую высокой частоты. На фиг. 5 на верхней диаграмме для этого примера изображен спектр модулирующего сигнала с частичным подавлением боковой полосы в сравнении со спектром сигнала с полосой 6 МГц в стандарте NTSC, который показан на нижней диаграмме.

На фиг. 17 изображен приемник сигналов с частичным подавлением боковой полосы, выполненный согласно изобретению. Демодулированный поток символьных данных из препроцессора 72 имеет структуру полей данных, которая была описана выше, при неравномерной скорости следования данных. Процессор 75 поля данных, относящийся к уровню системы передачи, обрабатывает структуру поля данных, идущих с неравномерной скоростью данных, и выдает данные с неравномерной скоростью следования данных. Схема 84 буферного интерфейса преобразовывает эти данные в поток байтовых данных в стандарте MPEG, идущих с постоянной равномерной скоростью. Этот поток обрабатывается в транспортном декодере 86, который работает без прерывания с постоянной равномерной скоростью данных и выдает декодированные байтовые данные в выходной процессор 88. Транспортный декодер 88 относится к системному транспортному уровню.

Более конкретно, сигнал, принятый из канала передачи, обрабатывается радиочастотным тюнером 70, включающим схемы селекции и смесители для преобразования сигнала с понижением частоты. Этот сигнал подается для ПЧ-фильтрации и синхронного детектирования на препроцессор 72, использующий известные способы для формирования сигнала в полосе модулирующего сигнала. Блок 72 включает также выравниватель для компенсации амплитудных и фазовых искажений, вносимых каналом передачи. Сигнал символьных данных с выхода блока 72 затем подвергается декодированию решетчатого кода, прямому обнаружению/коррекции ошибок и другой обработке сигнала, которая является обратной по отношению к обработке, выполненной в системе передачи, изображенной на фиг. 4.

Тактовые импульсы СТ и производные тактовые импульсы 1/4 СТ и 3/8 СТ идентичны соответствующим тактовым импульсам в передатчике. Таким образом, выходной поток данных (байтовые данные в стандарте MPEG), который подается в транспортный процессор/декодер 86, соответствует потоку данных (байтовые данные в стандарте MPEG), выдаваемому процессором 14 в системе передатчика, изображенной на фиг. 4. Входные символьные данные, подаваемые в блок символьного преобразователя и демультиплексора 74, соответствуют сигналу Выходные Символьные Данные, выдаваемому блоком 17 на фиг. 4. Входной поток символьных данных содержит компоненту синхронизации поля относительно большой длительности, которая соответственно определяет соседние поля данных (фиг. 1 и 3), между группами пакетов относительно меньшей длительности. Таким образом, входной поток символьных данных в приемнике имеет неравномерную скорость следования данных. Перед тем, как поступить в транспортный процессор 86 приемника, этот входной поток символьных данных с неравномерной скоростью следования данных преобразуется в выходной сигнал байтовых данных в стандарте MPEG (из схемы 84), который содержит пакеты данных, идущих с равномерной скоростью, разделенные равномерными промежутками между пакетами. Такой поток данных, следующих с постоянной равномерной скоростью, облегчает обработку и демультиплексирование данных транспортным декодером 86, который работает без прерывания потока данных.

Более конкретно, входной поток символьных данных в полосе частот модулирующего сигнала с неравномерной скоростью следования данных, полученный после демодуляции и выравнивания, подается в символьный преобразователь и демультиплексор 74, который осуществляет операции, обратные тем, которые выполняет преобразователь 58, изображенный на фиг. 4. Блок 74 преобразует каждый символ в 3-битовое слово, которое с помощью декодера 76 решетчатого кода, работающего совместно с блоком 78, декодируется в 2-битовое слово. Кроме того, блок 74 заменяет сигнал синхронизации сегмента в начале каждого пакета сегмента на сигнал синхронизации пакета MPEG. Поток символьных данных, обработанный блоком 74, контролируется блоком 90 для обнаружения появления управляющей информации, присутствующей в течение интервалов синхронизации поля, например так называемой "обучающей последовательности" для использования в предшествующем выравнивателе в блоке 72, информации о выборе режима и другой информации. Эта информация извлекается блоком 90 и подается в предыдущие схемы в соответствии с требованиями конкретной системы.

Группы 2-битовых слов данных с выхода декодера 76 решетчатого кода с помощью преобразователя 80 последовательных данных в параллельные преобразуются из последовательной формы в 8-битовую (однобайтовую) параллельную форму. Последовательные слова из преобразователя 80 подаются в блок 82 обнаружения и коррекции ошибок, например декодер Рида-Соломона. После коррекции ошибок данные из блока 82 подаются в блок 84 буфера/интерфейса приемника совместно с сигналом Данные Истинны, тактовыми импульсами СТ и 1/4 СТ, а также сигналом Начало Пакета из контроллера 92. Тактовые импульсы СТ и 1/4 СТ синхронизированы и вырабатываются местным генератором в контроллере 92. Сигнал Начало Пакета генерируется в ответ на появление в начале каждого пакета байта синхронизации. В ответ на сигнал Начало Пакета блок 82 прямой коррекции ошибок генерирует сигнал Данные Истинны.

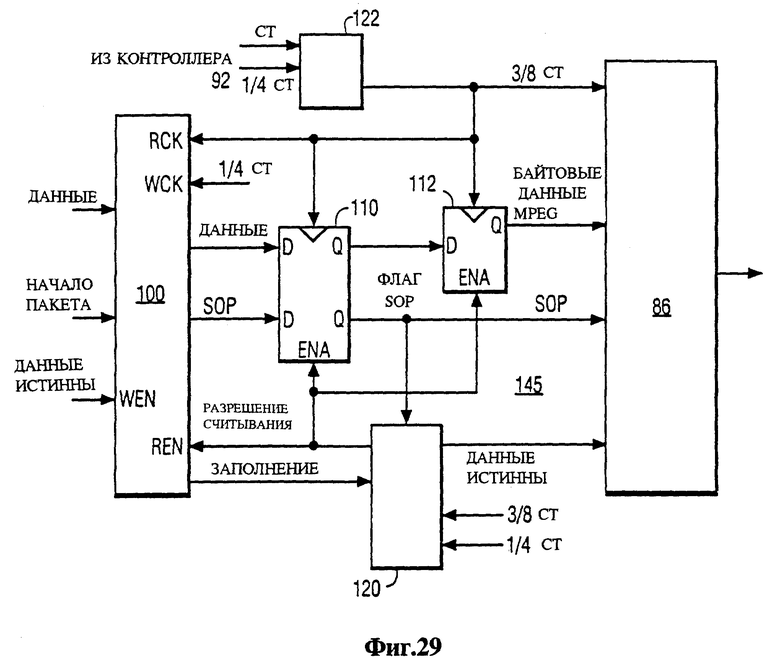

Блок 84 буфера/интерфейса аналогичен блоку 16 передатчика и изображен на фиг. 29. Схема интерфейса на фиг. 29 включает буфер 100 обратного магазинного типа, системный контроллер 120, генератор 122 тактовых импульсов 3/8 СТ и схему 145 выравнивания, характеристики каждого из перечисленных устройств аналогичны характеристикам таких же устройств в блоке 16 передатчика, изображенном на фиг. 28. Буфер 100, изображенный на фиг. 29, по существу такой же, как буфер 46 обратного магазинного типа в блоке 16 буфера передатчика на фиг. 4, за исключением того, что тактовые импульсы считывания и записи поменялись местами. Конкретнее, на тактовый вход записи в буфере 100 поданы тактовые импульсы 1/4 СТ, а на тактовый вход считывания в буфере 100 поданы тактовые импульсы 3/8 СТ. На фиг. 29 сигнал Начало Пакета на входе регистра 110 представляет собой буферизованную версию сигнала Начало Пакета, а сигнал Начало Пакета на входе транспортного процессора 86 представляет собой задержанную версию сигнала Начало Пакета на входе регистра 110.

Вернемся к фиг.17. Байтовый поток данных в полосе частот модулирующего сигнала в стандарте MPEG из блока 84 обрабатывается транспортным процессором/декодером 86, который по существу производит операции, обратные тем, которые выполняет транспортный процессор 14 в передатчике (фиг. 4). Транспортный процессор 86 декодирует данные с разделением их на составляющие компоненты. Процессор 86 содержит различные схемы обработки данных и демультиплексирования, включая анализаторы заголовков, маршрутизаторы сигнала в соответствии с информацией, содержащейся в заголовке, схемы декомпрессии сигнала стандарта MPEG и другие устройства обработки данных изображения и звука, которые формируют сигналы, сформатированные так, как это требуется для видео/аудио процессора 88, изображенного на фиг. 17. Видео- и аудиоданные, восстановленные транспортным декодером 86, обрабатываются соответственно видео- и аудиосхемами в блоке 88 с формированием сигналов изображения и звука, пригодных для воспроизведения.

Детектор 90 в блоке 75 также выдает сигнал Маркер Поля в блок 92 управления. Сигнал Маркер Поля запрещает контроллеру 92 запись сегмента синхронизации поля в блок 84 буфера, в результате чего выходной поток данных лишается компоненты синхронизации поля. Пакеты выходных данных из блока 84 буфера формируют единый поток, который не содержит компоненты синхронизации поля, в результате чего поток байтовых данных в стандарте MPEG из блока 84 характеризуется постоянной равномерной скоростью следования данных и постоянными равномерными промежутками между пакетами. Удаление вспомогательного сегмента синхронизации поля без остановки или разрыва потока данных осуществляется путем синхронизации считывания/записи в буфере 84 с учетом заранее заданного уровня заполнения буфера. При наличии пакетов они непрерывно считываются из буфера 46 в транспортный процессор. В течение одного периода, соответствующего полю данных, из буфера 84 в транспортный процессор 86 будет передано точно такое же количество байтов, какое необходимо, чтобы составить поле данных. Буфер 84 характеризуется тем же объемом и требованиями, касающимися его заполнения, что и буфер 46 в передатчике. Когда запись в буфер 84 временно запрещена для удаления из потока данных вспомогательной информации (например, сигнала синхронизации поля), пакеты данных продолжают считываться в транспортный процессор 86 с постоянной равномерной скоростью. За это время буфер 84 не опустошается полностью. Постоянный равномерный промежуток между пакетами данных предоставляет буферу 84 достаточно времени, чтобы частично опустошиться в течение того интервала, когда запись в него временно запрещена для удаления из потока данных вспомогательной информации. После того, как в течение интервала, когда запись была запрещена, вспомогательная информация удалена, данные опять записываются в буфер 84. В течение всего этого времени транспортный процессор 86 непрерывно получал пакеты данных из буфера 84, в результате чего поток данных тек без прерывания, а транспортный процессор 86 обрабатывал данные без прерывания.

Форма сигнала, изображенного на фиг. 18-27, соответствует работе приемника. Синхронизация в приемнике достигается за счет использования байта синхронизации пакета, который, как объяснялось ранее, является первым байтом каждого пакета данных. Как и в случае передатчика, после того как в начале пакета обнаружен байт синхронизации (фиг. 21), генерируются тактовые импульсы СТ (фиг. 18) и синхронизированные с ними тактовые импульсы 1/4 СТ (фиг. 19). Также, как и в передатчике, для выработки в приемнике тактовых импульсов 3/8 СТ (фиг. 20) используется счетчик для

подсчета тактовых импульсов 1/4 СТ. Синхронно с каждым байтом синхронизации пакета этот счетчик сбрасывается в ноль. Замечания, сделанные выше в отношении структуры и характеристик тактовых импульсов 3/8 СТ в передатчике, также справедливы в отношении тактовых импульсов 3/8 СТ в приемнике. Тактовые импульсы 1/4 СТ и тактовые импульсы 3/8 СТ в приемнике и передатчике должны быть идентичны.

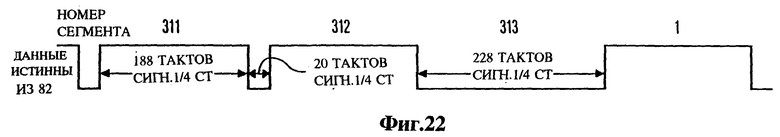

На фиг. 22 иллюстрируется сигнал синхронизации Данные Истинны, вырабатываемый схемой 82 блока 75 одновременно с сигналом данных из процессора 75. Форма сигнала Данные Истинны соответствует форме сигнала данных из процессора 75. Сигнал синхронизации Данные Истинны имеет неравномерную структуру с неравномерными промежутками между пакетами, включая промежуток в 20 тактов, соответствующий данным прямой коррекции ошибок, вставленным в сигнал данных, и значительно более широкий промежуток в 228 тактов, соответствующий вставленному в сигнал данных сигналу синхронизации поля. Пакеты данных в сигнале данных появляются в течение 188 тактов, во время которых сигнал Данные Истинны положителен. Таким образом, сигнал данных из схемы 82 характеризуется неравномерным потоком данных по сравнению с пакетными данными. Аналог показанного на фиг. 22 сигнала Данные Истинны в передатчике изображен на фиг.3 и 10.

В противоположность этому, сигнал Данные Истинны, подаваемый из блока 84 буфера в транспортный процессор/декодер 86 (фиг. 23), имеет равномерную структуру с равномерными промежутками между пакетами. Форма этого сигнала свидетельствует, что поток данных из блока 84 буфера имеет постоянные равномерные межпакетные промежутки (интервалы "запрещения данных" длиной в 125 периодов тактовых импульсов 3/8 СТ) между постоянными равномерными пакетами данных (интервалы "разрешения данных" длиной в 188 периодов тактовых импульсов 3/8 СТ). Таким образом, для работы транспортного процессора 86 без прерывания поток байтовых данных в стандарте MPEG является постоянным равномерным потоком данных. Реагируя на сигнал Данные Истинны, изображенный на фиг. 23, транспортный процессор 86 в течение каждого интервала длиной 188 тактовых импульсов получает пакеты данных для обработки из непрерывного потока данных. Для передатчика аналоги сигнала Данные Истинны, изображенного на фиг. 23, показаны на фиг. 11 и 12.

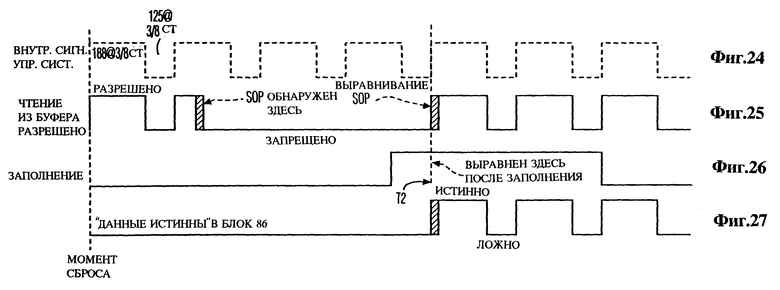

Блок 84 буфера/интерфейса в приемнике работает аналогично такому же блоку в передатчике, изображенному на фиг. 28. Как отмечено выше, соответствующие буферы обратного магазинного типа различаются в отношении входных тактовых импульсов Считывание и Запись. Кроме того, тогда как системный контроллер 44 передатчика на фиг. 28, реагируя на Запрос Пакета Поля Данных, вырабатывает сигнал Запрос Пакета Для Транспортировки, соответствующий блок в приемнике, изображенный на фиг. 29, для индикации начала нового пакета посылает в транспортный процессор 86 флаг Начало Пакета. Как и в случае буфера 46 в передатчике, буфер 100 в приемнике на фиг. 29 каждый раз при перезагрузке системы очищается и загружается до заранее заданного уровня. До того как данные разрешено считывать, буфер 100 должен достичь заранее заданного уровня "заполнения". Эта операция иллюстрируется на фиг. 24-27 и аналогична соответствующей операции в передатчике, рассмотренной выше в связи с фиг. 13-16.

Контроллер 120 автономно генерирует временные интервалы, изображенные на фиг. 24 штриховой линией. Этот сигнал имеет однородную структуру. Более конкретно, этот сигнал состоит из постоянных равномерных интервалов длиной в 125 периодов тактовых импульсов 3/8 СТ (соответствующих интервалам запрещения данных между пакетами) между постоянными равномерными интервалами длиной в 188 периодов тактовых импульсов 3/8 СТ (соответствующих интервалам разрешения данных в пакете данных). Из этого сигнала контроллер 120 вырабатывает сигнал разрешения считывания из буфера обратного магазинного типа (фиг. 25) для буфера 100 и сигнал Данные Истинны (фиг.27) для транспортного процессора 86, причем оба сигнала имеют постоянную равномерную структуру. Эти сигналы вырабатываются в ответ на сигнал Заполнение Буфера (фиг. 26) и флаг Начало Пакета, поданные на вход регистра 110. Этот флаг представляет собой буферизованную и задержанную версию сигнала Начало Пакета. Сигнал Начало Пакета (задержанный в регистре) с выхода регистра 110 подается на управляющий вход блока 120 и в транспортный процессор 86. Сигнал Заполнение Буфера вырабатывается, когда буфер 100 достигает заранее заданного заполнения. Операция разрешения считывания инициируется передним фронтом первого (положительного) интервала разрешения данных, который появляется после того, как сигнал Заполнение, в результате удовлетворения условия заполнения буфера, установится в высокий уровень. Следовательно, в момент времени Т2 первый байт (байт синхронизации) пакета данных выровняется с началом интервала истинности данных сигнала Данные Истинны (фиг. 27).

Как триггер, так и тактовый вход считывания буфера 84, синхронизируется тактовыми импульсами 3/8 СТ, генерируемыми в этом же блоке схемой 122 на основе тактовых импульсов СТ и тактовых импульсов 3/8 СТ, как описано выше. Тактовые импульсы 3/8 СТ поступают также в контроллер 120. Через триггеры 110 и 112 сигнал байтовых данных в стандарте MPEG поступает на вход данных транспортного процессора 86, когда эти триггеры разблокированы сигналом разрешения считывания, вырабатываемым контроллером 120. Одновременно из контроллера 120 флаг Начало Пакета вместе с сигналом Данные Истинны (фиг. 27) подается в транспортный процессор 86. Сигнал Данные Истинны подается в транспортный процессор 86 для того, чтобы разрешить ему принять данные в течение тех интервалов, когда присутствуют пакеты данных.

Интерфейс между транспортным процессором и процессором передачи, содержащий блок 17, важен для многих применений. Например, в телевизионном вещании, когда передача начата, требуется, чтобы процессор передачи генерировал и выдавал поля данных без прерываний. Работа телевизионных приемников основана на этом непрерывном потоке полей данных, включающих сегменты синхронизации поля для обеспечения синхронизации. Любое изменение в скорости следования полей данных или их структуры в процессе вещания приведет к срыву синхронизации в приемнике. Обычно студия вещания имеет несколько наборов видеомагнитофонов, запрограммированных для автоматического включения подходящего материала в различные моменты времени. Эти видеомагнитофоны выдают транспортные пакеты, содержащие информацию транспортного потока. Каждый видеомагнитофон синхронизирует свой выходной сигнал с потоком данных в процессор передачи, который не может изменять скорость следования полей данных или структуру полей. Неравномерные промежутки в потоке пакетов из транспортного процессора в процессор передачи приведут к тому, что структура поля передаваемых в интерфейс данных исказит поток данных, который будет содержать как пакет, так и структуру поля данных. Каждому студийному видеомагнитофону потребуются сложные интерфейсы, которые смогли бы синхронизировать сигналы на выходе магнитофона с границами как пакета, так и поля. Потребуется передавать через интерфейс дополнительную информацию о структуре поля или осуществлять контроль потока данных в интерфейсе. Интерфейс магнитофона должен будет содержать средства для обнаружения сигнала синхронизации пакета, средства обнаружения поля и память достаточного объема для хранения в буфере структуры поля данных. Дополнительные сложности возникают в случае предварительно сделанных записей и вставки местных программ и рекламы. Эти и другие трудности успешно устраняются с помощью системы записи/воспроизведения, использующей принципы настоящего изобретения, как показано на фиг.33 и 34.

На фиг. 33 и 34 представлены системы передатчика и приемника, изображенные на фиг. 4 и 17 соответственно, с тем отличием, что системы на фиг. 33 и 34 включают устройство видеозаписи. На фиг. 33 ленточное устройство 15 видеозаписи/воспроизведения принимает поток данных с равномерной скоростью следования данных из транспортного процессора 14, а через буфер/интерфейс 16 выдает с равномерной скоростью данные воспроизведения в кодер и блок 17 формирования поля данных. Как и в случае системы, изображенной на фиг. 4, система на фиг. 33 характеризуется равномерным потоком данных в интерфейсе между транспортным уровнем и уровнем передачи. В этом примере источник 12 данных содержит студийную видеокамеру и кодер MPEG для кодирования выходного сигнала камеры до его пакетирования транспортным процессором 14.

Устройство 15 может быть устройством для побайтовой записи на ленту, имеющимся в продаже, например видеомагнитофоном типа PanasonicTM D3. В конструкции некоторых устройств для видеозаписи может быть включен интерфейс 16. Устройство 15 может представлять собой один из наборов, состоящих из нескольких устройств для видеозаписи и широко используемых, как известно, в студиях вещания для облегчения передачи из студии материалов различного типа.

На фиг. 34 устройство 85 видеозаписи/воспроизведения на магнитной ленте принимает и обрабатывает поток данных, идущих с равномерной скоростью (с удаленной вспомогательной информацией) из интерфейса/буфера 84, и выдает данные воспроизведения с равномерной скоростью следования в транспортный процессор/декодер 86. Система, показанная на фиг. 34, также характеризуется равномерной скоростью потока в интерфейсе между уровнем передачи и транспортным уровнем. В этой системе устройство 85 записи представляет собой кассетный видеомагнитофон пользователя, способный осуществлять запись из эфира или воспроизводить материал, например, заранее записанный с помощью устройства, имеющего характеристики, подобные блоку 15 на фиг. 33. Блок 85 может быть отдельным блоком в системе, где элементы 72, 75, 84 и 86 встроены в телевизионный приемник. Альтернативно, элементы 72, 75, 84 и 86 могут быть включены в устройство 85 записи.

Изобретение относится к области обработки цифровых сигналов. Передаваемый сигнал телевидения высокой четкости представлен потоком данных в пакетной форме в виде последовательности полей данных с неравномерной скоростью следования данных вследствие того, что различные типы интервалов с вспомогательной информацией, не содержащей полезных данных, имеют разную длительность. Каждому полю данных предшествует вспомогательный сегмент синхронизации поля, за которым следуют 312 сегментов данных в пакетной форме, каждый из которых содержит соответствующую информацию прямой коррекции ошибок. В передатчике транспортный процессор формирует пакеты данных с соответствующими заголовками и осуществляет непрерывную обработку с постоянной равномерной скоростью следования данных, в то же время подавая поток данных в пакетной форме в блок, который формирует последовательные поля данных путем вставки в поток данных вспомогательной информации, не содержащей данные. Преимуществом является то, что транспортный процессор работает с постоянной равномерной скоростью следования данных без необходимости преобразования первоначальной структуры поля данных для удовлетворения требований блока формирования поля данных. Это осуществляется за счет передачи данных из транспортного процессора в соответствующий блок интерфейса/буфера в ответ на символьный тактовый сигнал (СТ) 3/8 СТ, а также за счет заранее заданного уровня заполнения буфера. Соответствующий транспортный процессор/декодер в приемнике работает совместно с процессором поля данных и также осуществляет непрерывную обработку с постоянной равномерной скоростью данных. Технический результат изобретения - создан транспортный процессор, в котором данные записываются с равномерной скоростью, а описываются с неравномерной скоростью. 3 с. и 15 з. п.ф-лы, 34 ил.

| ВСЕСОЮЗНАЯ НАТЕ»' О fi::4ECKAf jt_^ библиотека МБА | 0 |

|

SU353757A1 |

| Электрический кабель | 1971 |

|

SU562221A3 |

| Устройство предсказания сигнала изображения при дифференциальном кодировании | 1986 |

|

SU1396293A1 |

| Устройство кодирования телевизионного сигнала | 1986 |

|

SU1381730A1 |

| Домовый номерной фонарь, служащий одновременно для указания названия улицы и номера дома и для освещения прилежащего участка улицы | 1917 |

|

SU93A1 |

Авторы

Даты

2000-01-20—Публикация

1995-06-13—Подача