схемы сравнения адреса, второй вход которой и второй вход схемы сравнения соединены с восьмым входом машины, выходы схемы сравнения и схемы сравнения адреса подключены к входу блока памяти, четвертому входу блока управления обменом системной магистрали и к второму -входу блока сопряжения с периферийными устройствами.

2.Машина по п.1,- отличающаяся тем, что, арбитр системной магистрали содержит узлы распределенного и сосредоточенного арбитража, элементы И, ИЛИ, НЕ, причем первый выход узла распределенного арбитража соединен с первым входом первогр элемента ИЛИ, второй вход которого подклчен, к выходу первого элемента И, .первый вход которого соединен с первым выходом узла сосредоточенного арбитража, второй вход - с выходом первого элемента НЕ, первые входы узлов сос редоточенного и распределенного арбитража и первый вход второго элемента И соединены с первым входом арбитра, выход первого элемента ШШ является первым выходом арбитра, четвертьй вход которого соединен с входом первого элемента НЕ и со вторым входом второго элемента И, выход которого соединен с вторым входом узла расггределенного арбитража, второй выход которого является вторым выходом арбитра, второй вход которого соединен с первым входом третьего элемента И, третий вход арбитра соединен с вторым входом узла сосредоточенного арбитража,, третий выход - с третьим выходом узла рапределенного арбитража и с входом второго элемента НЕ, выходы первого

и второго элементов НЕ соединены соответственно с вторым и третьим входами третьего элемента И, выход которого подключен к третьему.входу узла сосредоточенного арбитража, второй выход которого и четвертый выход узла распределенного арбитража соединены соответственно с входами второго элемента ИЛИ, выход которого является четвертым выходом арбитра, пятый вход которого соединен с третьим входом узла распределенного арбитража и с четвертым входом узла сосредоточенного арбитража.

3.Машина поп.1, отличающаяся тем, что арбитр внутренней магистрали содержит узел вьщеле- ния левой единицы, элементы И, элемент ИЛИ-НЕ, выход которого соединен

.с первыми входами элементов И, вторые входы которых соединены соответсвенно с выходами узла вьщеления левой единицы, первый вход которого и первый вход элемента ИЛИ-НЕ подключены к первому входу арбитра, выход первого элемента И является первым выходом арбитра, второй вход которого соединен с вторыми входами узла вьщеления левой единицы и элемента ИЛИ-НЕ, выход второго элемента И является вторым выходом арбитра.

4.Машина поп.1, отличающаяся тем, что блок управления обменом в процессоре содержит триггеры, элементы И,НЕ, причем выход первого триггера соединен с первым входом первого элемента И, выход котрого соединен с первым входом второго триггера, выходы первого и второго триггеров подключены к второму выходу блока, второй вход первого элемента И соединен с первым входом блока, выход второго триггера подключен к первым входам второго и третьего элементов И и первому входу первого триггера, второй вход второго элемента И соединен с вькодйм элемента НЕ, второй вход первого триггера, второй вход третьего элемента И третий вход второго элемента И и вхо элемента НЕ подключены к второму входу блока, выход второго элемента

И соединен с первым входом третьего триггера, вькоды второго и третьего триггеров и выход третьего элемента И подключены к первому выходу блока вторые входы второго и третьего триггеров соединены с входом блока, выход которого соединен с выходами второго и третьего триггеров и выходом третьего элемента И.

5.Машина по пп.1 и 2, отличающаяся тем, что узел распределенного арбитража содержит два

.триггера, элемент задержки и элемент И, выход которого является четвертым ВЫХОДОМ узла, входы элемента И соединены соответственно с первым выходом первого триггера и выходом элемента задержки, второй выхсд первого триггера подключен к первому и третьему выходам узла и к первому входу второго триггера, второй вход которого является вторым входом узла, а выход подключен к второму выходу узла и к первому входу второго триггера, третш 1 вход узла соединен с входом элемента задержки и вторым входом второго триггера, третий вход которого является первым входом узла. 6. Машина по пп.1 и 2, отличающаяся тем, что узел сосредоточенного арбитража содержит три триггера, элемент ИЛИ-НЕ и элемент И, выход которого является вторьп выходом узла, первьй вход первого триггера является вторым входом узла, первьй вход которого подключен к первым входам второго триггера и элемента ИЛИ-НЕ, второй вход которого и второй вход первого триггера соединены с выходом третьего триггера, выход элемента ИЛИ-НЕ является первым выхо- дом узла, первый вход третьего триггера является третьим входом узла, четвертый вход которого соединен с вторым входом третьего триггера и с первым входом элемента И, второй вход которого соединен с выходом рторого триггера, второй вход которого соединен с выходом первого триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОМАШИННАЯ СИСТЕМА УПРАВЛЕНИЯ | 2006 |

|

RU2320003C2 |

| Устройство связи многопроцессорной вычислительной системы | 1988 |

|

SU1529243A1 |

| Устройство для согласования системных магистралей | 1989 |

|

SU1674143A1 |

| Многоканальная система управления распределением ресурсов в вычислительном комплексе | 1987 |

|

SU1432580A1 |

| Мультиплексное устройство для обмена информацией | 1983 |

|

SU1157546A1 |

| Устройство связи кольцевой оптоволоконной сети | 1988 |

|

SU1689963A1 |

| Устройство межмодульной связи для системы коммутации сообщений | 1986 |

|

SU1388883A1 |

| УСТРОЙСТВО МЕЖМАШИННОГО ОБМЕНА | 1989 |

|

SU1635782A1 |

| Устройство сопряжения многопроцессорной системы | 1987 |

|

SU1575195A1 |

| Распределенная система управления | 1989 |

|

SU1732345A1 |

1. МИКРОЭЛЕКТРОННАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА, содержащая процессор, включающий блок дешифрации команд, первьй выход которого подключен к первому входу блока выполнения операций, блок памяти, блок сопряжения с периферийными устройствами, буферный запоминающий узел и блок управления обменом системной магистрали, соединенные двусторонними связями, первьй выход блока управления обменом системной магистрали соединен с управляющим входом буферного запоминающего узла, первые вход и выход которого являются соответственно первыми входом и выходом микроЭВМ, первьй вход и второй выход блока управления обменом системной магистрали являются соответственно вторым входом и вторым выходом машины, первые вход и выход блока сопряжения с периферийными устройствами являются соответственно третьим входом и выходом машины, отличающая с я тем, что, с целью повьшюния коэффициента использования оборудования, в нее введены схема сравнения адреса, арбитр внутренней магистрали, арбитр системной магистрали, а в процессор введены блок управления обменом и буферный запоминающий элемент, соединенные двусторонними связями, и схема сравнения, причем первые вход и выход буферного запоминающего элемента -соединены соответственно с выходом и вторым входом блока выполнения операций, второй вход подключен к первому выходу блока управления обменом, второй выход соединен с первым входом схемы сравнения, первый вход и второй выход блока управления обменом соединены соответственно с первым выходом и с первым входом арбитра внутренней магистрали, второй вход подключен к второму выходу блока дешифрации команд, буферньй запоминающ1 й элемент и блок уп(Л равления обменом соединены двусторонними связями с блоком памяти, блоком с сопряжения с периферийными устройствами, блоком управления обменом систем- S ной магистрали и с буферным запоминающим узлом, вторые вход и выход о o:i арбитра внутренней магистрали соединены соответственно с третьим выходом и вторым входом -блока управления обменом системной магистрали, третий о: вход и четвертый выход которого соеО О5 динены соответственно с первым выходом и с первым входом арбитра системной магистрали, вторые входи вь1ход которого являются соответственно четвертыми входом и выходом машины, третий вход и выход арбитра системной магистрали являются соответственно пятым входом и выходом машины, четвертые вход и выход являются соответственно шестым входом и выходом машины, пятый вход является седьмым входом машины, второй выход буферного запоминающего узла подключен к первому входу

1

Изобретение относится к вычислительной технике.

Известна микроэлектронная вычислительная машина (ЭВМ), содержащая программный счетчик, рабочие регистры, 5 арифметико-логический узел, сумматор, таймер, управляющую логику, дешифратор команд, адресную шину, разделенную с помощью коммутатора на две секции 1

Конструктивно ЭВМ выполнена в ий- 10 де нескольких больших интегральных схем (БИС), расположенных на платах ЭВМ, построенная таким образом, имеет относительно большие габариты, большие потребляемую мощность и стой- 15 мость. Дальнейшее.повышение интеграции прпивело к появлению сверхбольших интегральньк схем - СБИС.

Однокристальные ЭВМ имеют меньшую стоимость, большую надежность, меньшу1о20 потребляемую мощность, более гибки в применении.

Из известных ЭВМ наиболее близкой по технической сзшщости к изобретению является ЭВМ, содержащая процессор, 25 включающий связанные между собой операционньш блок и блок управления, блок памяти, блок сопряжения с периферийными устройствами,двунаправленный буферный элемент системной магистрали и - зо блок управления обменном системной магистрали соединенные между собой внутренней магистралью.Выход блока управления системой магистрали соединен с входом двунаправленного буферного элемента системной магистрали, вход-выход которого и первый вход - выход блока управления системной магистрали соединены с первыми внешними выходами однокристальной ЭВМ, а входвыход блока сопряжения с периферийными устройствами подключен ко вторьм внешн выводам однокристальной ЭВМ .

Недостатком известной однокристальной ЭВМ является невозможность объединения однокристальных микроЭВМ в многопроцессорную систему с общим полем памяти.

Целью изобретения является повышение коэффициента использования оборудования ЭВМ.

Поставленная цель достигается тем, что в микроэвм, содержащую процессор, включающий блок дешифрации команд, первьй выход которого подключен к первому входу блока выполнения операций, блок памяти, блок сопряжения с периферийными устройствами, буферный запоминающий узел и блок управления обменом системной магистрали, соединенные двусторонним связями, первый выход блока управления обменом системной магистрали соединен с управляющим входом буферного запоминающего узла, первые .вход и выход которого являются соответственно первыми входом и выходом машины, первый вход и второй выход блока управления обменом системной магистрали являются соответственно вторым входом и вторым выходом машины, первые вход и выход блока сопряжения :С периферийными устройствами являются соответственно третьим входом и выходом машины, введены схема сравнения адреса, арбитр внутренней ма--- гистрали, арбитр системной магистрали, а в процессор введены блок управ ления обменом и буферный запоминающий элемент, соединенные двусторонними связями, и схема сравнения. Первые вход и выход буферного запоминающего элемента соединены соответственно с выходом и вторым входом блока выполнения операций, второй вход подключен к первому выхо- ду блока управления обменом, второй выход соединен с первым входом схемы сравнения. Первый вход и второй выход блока управления обменом соединены соответственно с первым выходом и с первым входом арбитра внутренней магистрали, второй вход подключен к второму выходу блока . дешифрации команд. Буферный запоминающий элемент и блок управления обменом соединены двусторонними связями с блоком памяти, блоком сопряжения с периферийными устройствами, блоком управления обменом системной магистрали и с буферным запоминающим узлом. Вторые вход и выход арбитра внутренней магистрали соединены соответственно с третьим выходом и вторым входом блока управления обменом системной магистрали, третий вход и. четвертый выход которого соединены соответст- венно с первым выходом и-с первым входом арбитра системной магистрали, вторые вход и выход которого являются соответственно четвертыми входом и выходом машины. Третьи вход и выход арбитра системной магистрали яв.ляются соответственно пятыми входом и выходом машины, четвертые; вход и выход - шестыми входом и вьгходом машины, пятый ёход - седьмым входом микроэвм. Второй выход буферного запоминающего узла подршючен к перво му входу схемы сравнения адреса, вто рой вход кото-рой и второй вход схемьг сравнения соединены с восьмым Входом машины. Выходы схемы сравнения и схе мы сравнения адреса подключены к вхо ду блока памяти, четвертому входу бл ка управления обменом системной магист рали и к -второму входу блока сопряже ния с периферийными устройствами. Ар битр системной магистрали в машине с держит узлы распределенного и сосред точенного арбитража, элементы И, ИЛИ НЕ. Первый выход узла распределенног арбитража соединен с первым входом первого элемента ИЛИ, второй вход которого подключен к выходу первого элемента И, первьш вход которого соединен с первым выходом Узла сосредоточенного арбитража, второй вход - с выходом первого элемента НЕ. Первые входы узлов сосредоточенного и распределенного арбитража и первый вход второго элемента И соединены с первым входом арбитра. Выход первого элемента ИЛИ является первым выходом арбитра, четвертый вход которого соединен с входом первого элемента НЕ и с вторым входом второго элемента И, выход которого соединен с вторым входом узла распределенного арбитража, второй выход крторого .является вторым выходом арбитра, второй вход которого соединен с первым входом третьего элемента И. Третий вход арбитра соединен с вторым входом узла сосредоточенного арбитража, третий выход - с третьим выходом узла распределенного арбитража и с входом второго элемента НЕ. Выходы первого ивторого элементов НЕ соединены соответственно с вторым и третьим входами третьего элемента И, выход которого подключен к третьему входу узла сосредоточенного арбитража, второй выход которого и четвертый выход узла распределенного арбитража соединены соответственно с входами второго элемента ИЛИ, выход которого является четвертым выходом арбитра, пятый вход которого соединен с третьим входом узла распределенного арбитража и с четвертым входом узла сосредоточенного арбитража. Арбитр внутренней магистрали в машине содержит узел вьзделения левой единищ Ь элементы И, элемент ИЛЙ-НЕ, выход которого соединен с первыми входами элементов И, вторые входы которых соединены соответственно с выходами узла выделения левой единицы, первый вход которого и первый вход элемента ИЛИ-НЕ подключены к первому входу арбитра. Выход первого элемента И является первым выходом арбитра, второй вход которого соединен с вторыми входами узла вьщеления левой единицы и элемента ИЛИ-НЕ, выход второго элемента И является вторым выходом арбитра. Блок управления обменом в процессоре содержит триггеры, элементы И,НЕ, причем выход первого триггера соединей с первым входом первого элемента И, выход которого соединен с первым входом второго триггера. Выходы первого и второго триггеров подключены к второму выходу блока. Второй вход первого элемента И соединен с первь1М входом блока, выход второго триггера подключен к первым входам второго и третьего элементов Инк первому входу первого триггера. Второй вход второго элемента И соединен с выходом элемента НЕ. Второй вход первого триггера,второй вход третьего элемента И, третий вход второго элемента И и вход элемента НЕ подключены к второму входу блока. Выход второго элемента И соединен с первым входом тре тьего триггера. Выходы второго и третьего триггеров и вьрсод третьего элемента И подключены к первому выходу блока. Вторые входы второго и третьего триггеров соединены.с входом блока, выход которого соединен с выходами второго и .третьего триггеров и выходом третьего элемента И. В арбитре системной магистрали узел распределенного арбитража содержит два триггера, элемент задержки и элемент И, выход которого является четвертым выходом узла. Входы элемента И соединены соответственно с первым выходом первого триггера и выходом элемента задержки, второй выход первого триггера подключен к первому и третьему выходам узла и к первому входу второго триггера, второй вход которого является вторым входом узла, а выход под.ключей к второму выходу узла и к перво му ВХОДУ второго триггера. Третий вхрй узла соединен с входом элемента задержки и вторым входом второго триггера, третий .вход которого является первым входом узла.В арбитре системной магистрали узел сосредоточенного арбитража содержит три триггера, эле- . мент ШШ-НЕ и элемен-г И, выход кото- рого является вторым выходом узла.Первый вход первого триггера является вторым входом узла, первый вход которого подключен к первым входам второго триргера и элемента ИЛИ-НЕ, второй вход которого и второй вход первого триггера соединены с выходом третьего триггера. п Выход элемента ИЛИ-НЕ является первым выходом узла, первый вход третьего триггера - третьим входом узла, четвертый вход которого соединен с вторым Входом третьего триггера и с первым входом элемента И, второй вход которого соединен с выходом второго триггера второй вход которого соединен с выходом первого вриггера.

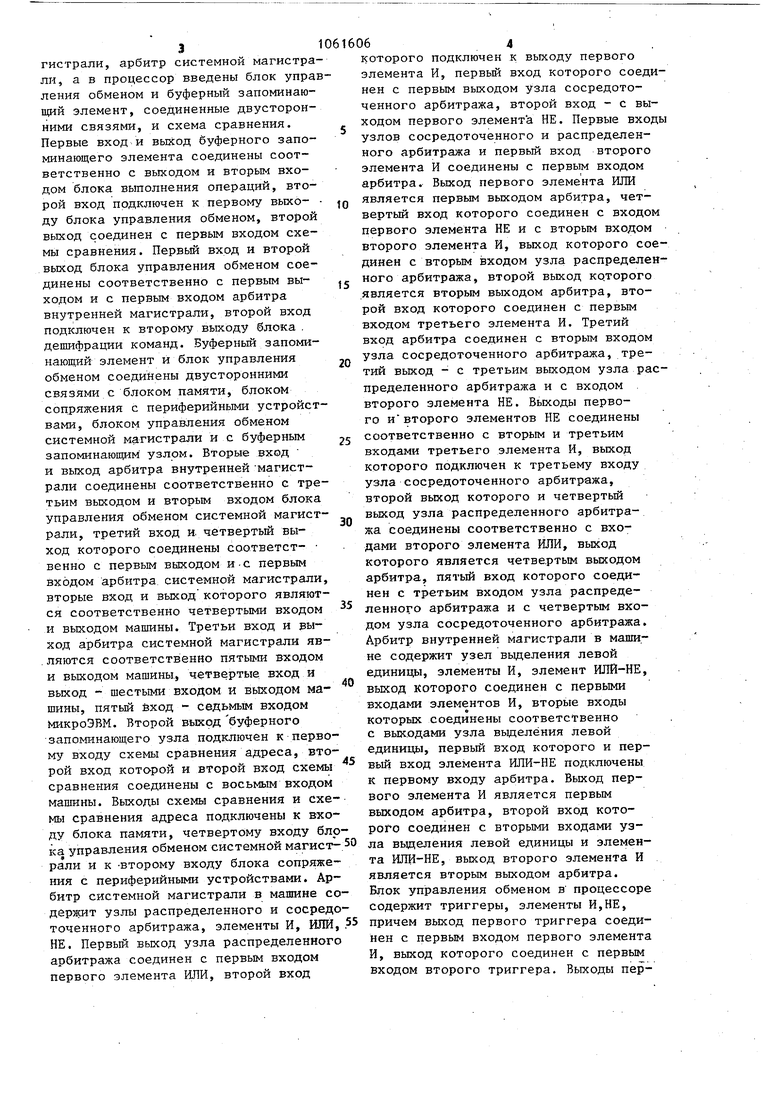

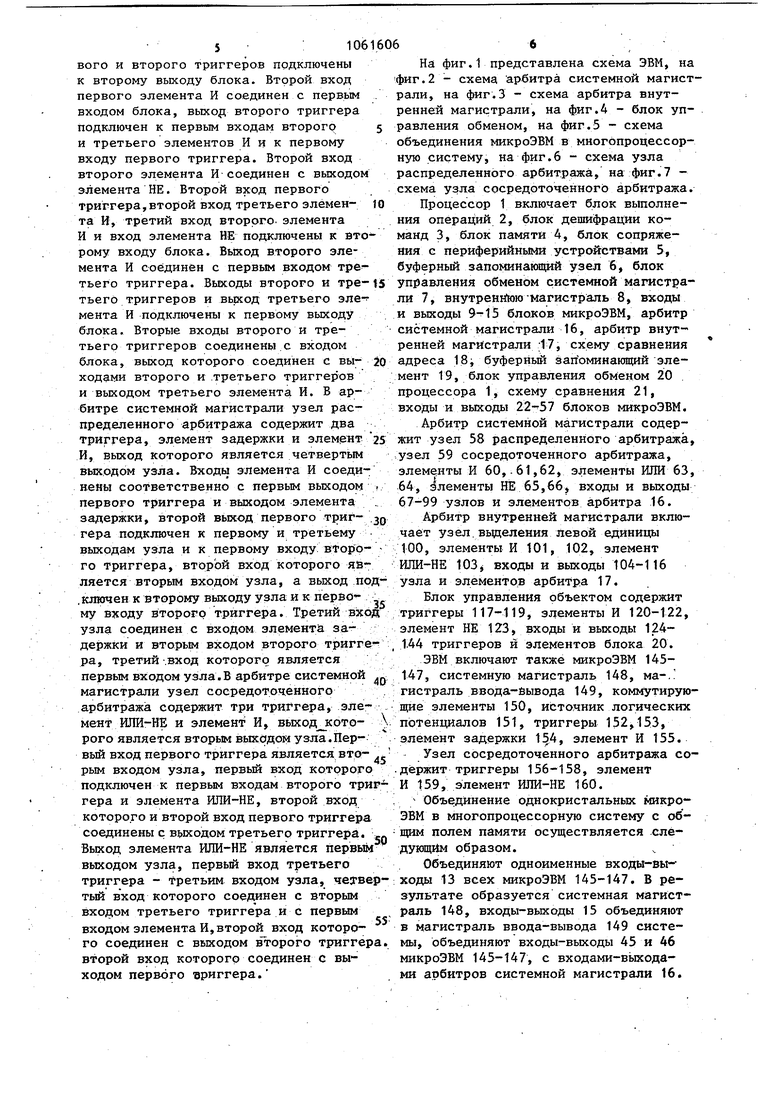

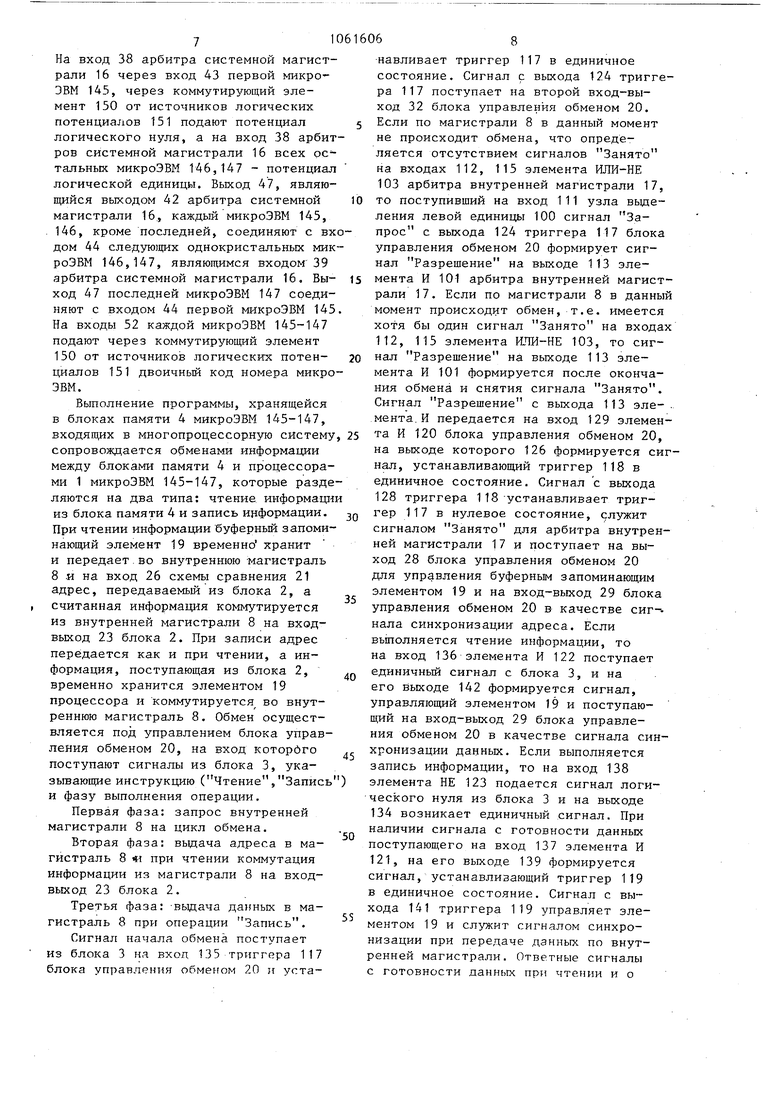

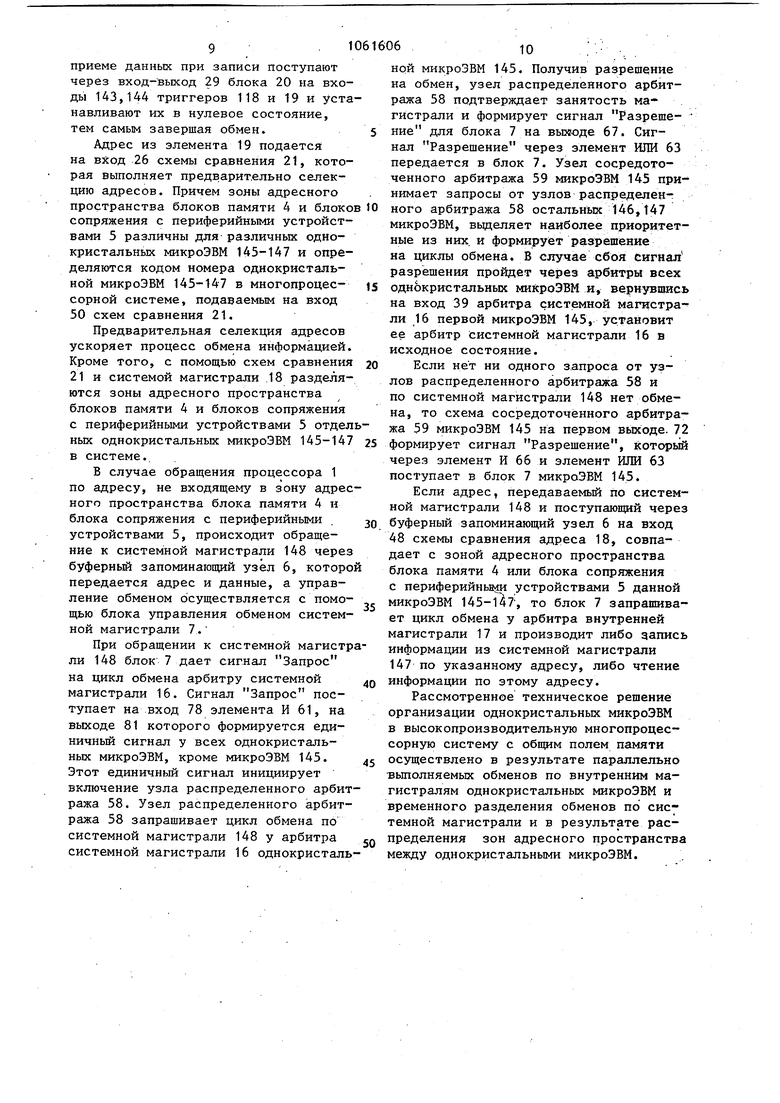

На фиг.1 представлена схема ЭВМ, на фиг.2 - схема арбитра системной магистрали, на фиг.З - схема арбитра внутренней магистрали, на фиг.4 - блок управления обменом, на фиг.З - схема объединения микроЭВМ в многопроцессорную систему, на фиг.6 - схема узла распределенного арбитража, на фиг.7 схема узла сосредоточенного арбитража.

Процессор 1 включает блок выполнения операций 2, блок дешифрации команд 3, блок памяти 4, блок сопряжения с периферийными устройствами 5, буферный запоминающий узел 6, блок управления обменом системной магистраля 7, внутреннею-магистраль 8, входы и выходы блоков микроЭВМ, арбитр системной магистрали 16, арбитр внутренней магистрали -IT, схему сравнения адреса 18; буферньй запоминающий элемент 19, блок управления обменом 20 процессора 1, схему сравнения 21, входы и выходы блоков микроЭВМ.

Арбитр системной магистрали содержит узел 58 распределенного арбитража, узел 59 сосредоточенного арбитража, элементы И 60,.61,62, элементы ИЛИ 63, 64, Элементы НЕ 65,66, входы и выходы 67-99 узлов и элементов арбитра 16.

Арбитр внутренней магистрали включает узел.вьщеления левой единицы 100, элементы И 101, 102, элемент ИЛИ-НЕ 103 входы и выходы 104-116

Блок управления объектом содержит триггеры 117-119, элементы И 120-122, элемент НЕ 123, входы и выходы 1241.44 триггеров и элементов блока 20.

ЭВМ включают также микроЭВМ 145узла и элементов арбитра 17. 147, системную магистраль 148, ма-. гистраль ввода-вывода 149, коммутирующие элементы 150, источник логических потенциалов 131, триггеры 132,133, элемент задержки 154, элемент И 155. Узел сосредоточенного арбитража содержит триггеры 156-158, элемент И 139, элемент ИЛИ-НЕ 160. Объединение однокристальных микроЭВМ в многопроцессорную систему с общим полем памяти осуществляется .следующим образом. Объединяют одноименные входы-вы-ходы 13 всех микроЭВМ 145-147. В результате образуется системная магистраль 148, входы-выходы 15 объединяют в магистраль ввода-вывода 149 системы, объединяют входы-выходы 43 и 46 микроэвм 145-147, с входами-вькодами арбитров системной магистрали 16. На вход 38 арбитра системной магистрали 16 через вход 43 первой микроЭВМ 145, через коммутирующий элемент 150 от источников логических потенциалов 151 подают потенциал логического нуля, а на вход 38 арбит ров системной магистрали 16 всех остальных микроэвм 146,147 - потенциал логической единицы. Выход 47, являющийся выходом 42 арбитра системной магистрали 16, каждьш микроЭВМ 145, 146, кроме последней, соединяют с вх дом 44 следующих однокристальных мик роЭВМ 146,147, являющимся входом 39 арбитра системной магистрали 16. Выход 47 последней микроЭВМ 147 соединяют с входом 44 первой микроЭВМ 145 На входы 52 каждой микроЭВМ 145-147 подают через коммутирующий элемент 150 от источников логических потенциалов 151 двоичный код номера микро ЭВМ. Выполнение программы, хранящейся в блоках памяти 4 микроЭВМ 145-147, входящих в многопроцессорную систему сопровождается обменами информации между блоками памяти 4 и процессорами 1 микроэвм 145-147, которые разде ляются на два типа: чтение информаци из блока памяти 4 и запись информации. При чтении информации буферный запоми нающий элемент 19 временно хранит и передает.во внутреннюю -магистраль 8 и на вход 26 схемы сравнения 21 адрес, передаваемьш из блока 2, а считанная информация коммутируется из внутренней магистрали 8 на входвыход 23 блока 2. При записи адрес передается как и при чтении, а информация, поступающая из блока 2, временно хранится элементом 19 процессора и коммутируется во внутреннюю магистраль 8. Обмен осуществляется под управлением блока управления обменом 20, на вход которого поступают сигналы из блока 3, указывающие инструкцию (Чтение,Запись и фазу выполнения операции. Первая фаза: запрос внутренней магистрали 8 на цикл обмена. Вторая фаза: выдача адреса в магистраль 8 1 при чтении коммутация информации из магистрали 8 на входвыход 23 блока 2. Третья фаза: -вьщача данных в магистраль 8 при операции Запись. Сигнал начала обмена поступает из блока 3 на вход 135 трт1ггера 117 блока управления обменом 20 и устанавливает триггер 117 в единичное состояние. Сигнал с выхода 124 триггера 117 поступает на второй вход-выход 32 блока управления обменом 20. Если по магистрали 8 в данный момент не происходит обмена, что определяется отсутствием сигналов Занято на входах 112, 115 элемента ИЛИ-НЕ 103 арбитра внутренней магистрали 17, то поступивший на вход 111 узла вьщеления левой единицы 100 сигнал Запрос с выхода 124 триггера 117 блока управления обменом 20 формирует сигнал Разрешение на выходе 113 элемента И 101 арбитра внутренней магистрали 17. Если по магистрали В в данный момент происходит обмен, т.е. имеется хотя бы один сигнал Занято на входах 112, 115 элемента ИЛИ-НЕ 103, то сигнал Разрешение на выходе 113 элемента И 101 формируется после окончания обмена и снятия сигнала Занято. Сигнал Разрешение с выхода 113 эле-, мента. И передается на вход 129 элемента И 120 блока управления обменом 20, на выходе которого 126 формируется сигнал, устанавливающий триггер 118 в единичное состояние. Сигнал с выхода 128 триггера 118-устанавливает триггер 117 в нулевое состояние, длужит сигналом Занято для арбитра внутренней магистрали 17 и поступает на выход 28 блока управления обменом 20 для управления буферным запоминающим элементом 19 и на вход-выход 29 блока управления обменом 20 в качестве сиг-нала синхронизации адреса. Если вьтолняется чтение информации, то на вход 136 элемента И 122 поступает единичный сигнал с блока 3, и на его выходе 142 формируется сигнал, управляющий элементом 19 и поступающий на вход-выход 29 блока управления обменом 20 в качестве сигнала синхронизации данных. Если выполняется запись информации, то на вход 138 элемента НЕ 123 подается сигнал логического нуля из блока 3 и на выходе 134 возникает единичный сигнал. При наличии сигнала с готовности данньк поступающего на вход 137 элемента И 121, на его выходе 139 формируется сигнал, устанавливающий триггер 119 в единичное состояние. Сигнал с выхода 141 триггера 119 управляет элементом 19 и служит сигналом синхронизации при передаче данных по внутренней магистрали. Ответные сигналы с готовности данных при чтении и о

приеме данных при записи поступают через вход-выход 29 блока 20 на входы 143,144 триггеров 118 и 19 и устанавливают их в нулевое состояние, тем самым завершая обмен.

Адрес из элемента 19 подается на 26 схемы сравнения 21, которая выполняет предварительно селекцию адресов. Причем зоны адресного пространства блоков памяти 4 и блоко сопряжения с периферийными устройствами 5 различны для различных однокристальных микроэвм 145-147 и определяются кодом номера однокристальной микроэвм 145-147 в многопроцессорной системе, подаваемым на вход 50 схем сравнения 21. Предварительная селекция адресов ускоряет процесс обмена информацией. Кроме того, с помощью схем сравнения 21 и системой магистрали .18 разделяются зоны адресного пространства блоков памяти 4 и блоков сопряжения с периферийными устройствами 5 отдел ных однокристальных микроЭВМ 145-147 в системе., В случае обращения процессора 1 по адресу, не входящему в зону адрес ного пространства блока памяти 4 и блока сопряжения с периферийными устройствами 5, происходит обращение к системной магистрали 148 через буферньй запоминающий узел 6, которо передается адрес и данные, а управление обменом осуществляется с помощью блока управления обменом системной магистрали 7. При обращении к системной магистр ли 148 блок 7 дает сигнал Запрос на цикл обмена арбитру системной магистрали 16. Сигнал Запрос поступает на вход 78 элемента И 61, на выходе 81 которого формируется единичный сигнал у всех однокристальных микроэвм, кроме микроЭВМ 145. Этот единичный сигнал инициирует включение узла распределенного арбит ража 58. Узел распределенного арбитража 58 запрашивает цикл обмена по системной магистрали 148 у арбитра системной магистрали 16 однокристаль

ной микроэвм 145. Получив разрешение на обмен, узел распределенного арбитража 58 подтверждает занятость магистрали и формирует сигнал Разреюе- ние для блока 7 на выжоде 67. Сигнал Разрешение через элемент ИЛИ 63 передается в блок 7. Узел сосредоточенного арбитража 59 микроЭВМ 145 принимает запросы от узлов распределенного арбитража 58 остальных 146,147 микроЭВМ, вьщеляет наиболее приоритетные из них, и формирует разрешение на циклы обмена. В случае сбоя сигнал разрешения пройдет через арбитры всех однокристальных микроЭВМ и, вернувщись на вход 39 арбитра системной магистрали 16 первой микроэвм 145, установит ее арбитр системной магистрали 16 в исходное состояние. Если нет ни одного запроса от узлов распределенного арбитража 58 и по системной магистрали 148 нет обмена, то схема сосредоточенного арбитража 59 микроэвм 145 на первом выходе. 72 формирует сигнал Разрешение, который через элемент И 66 и элемент ИЛИ 63 поступает в блок 7 микроЭВМ 145. Если адрес, передаваемьй по системной магистрали 148 и поступающий через буферный запоминающий узел 6 на вход 48 схемы сравнения адреса 18, совпадает с зоной адресного пространства блока памяти 4 или блока сопряжения с периферийньнет устройствами 5 данной микроэвм 145-14/, то блок 7 запрашивает цикл обмена у арбитра внутренней магистрали 17 и производит либо запись информации из системной магистрали 147 по указанному адресу, либо чтение информации по этому адресу. Рассмотренное техническое решение организации однокристальных микроЭВМ в высокопроизводительную многопроцессорную систему с общим полем памяти осуществлено в результате параллельно вьтолняемых обменов по внутренним магистралям однокристальных микроЭВМ и временного разделения обменов по системной магистрали и в результате распределения зон адресного пространства между однокристальными микроЭВМ.

Vuz. 1

Риг. г

. ff

Vuz.6

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США №4016546, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| СПОСОБ ПЕРЕМЕЩЕНИЯ КЛАПАНА (ВАРИАНТЫ), УСТРОЙСТВО ДЛЯ СНИЖЕНИЯ ТРЕНИЯ ВО ВРЕМЯ ПЕРЕМЕЩЕНИЯ КЛАПАНА (ВАРИАНТЫ) И УСТАНОВКА, СОДЕРЖАЩАЯ ТАКОЙ КЛАПАН | 2003 |

|

RU2334150C2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-06-30—Публикация

1979-09-05—Подача