рователк сигнапов Чтение-запись, о первым и вторым выходами формивыходы которых являются соответствен- рователя сигналов Чтение-запись.

1172455

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропроцессорная система | 1989 |

|

SU1675898A2 |

| Запоминающее устройство | 1986 |

|

SU1437916A1 |

| Запоминающее устройство | 1984 |

|

SU1243033A1 |

| Устройство для проверки выполнения последовательности команд микропроцессора | 1984 |

|

SU1247874A1 |

| Устройство для управления роботом | 1983 |

|

SU1228074A1 |

| Приоритетное устройство доступа к общей памяти | 1987 |

|

SU1529239A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1987 |

|

SU1451768A1 |

| Устройство для ввода и вывода динамически изменяющейся информации | 1982 |

|

SU1115043A1 |

| Устройство для сопряжения источника и приемника информации | 1985 |

|

SU1309032A1 |

| Процессор для мультипроцессорной системы | 1987 |

|

SU1517035A1 |

МИКРОПРОЦЕССОРНАЯ СИСТЕМА, содержащая микропроцессор, запоминающее устройство и периферийное устройство, причем информационные входы-выходы запоминающего и периферийного устройств через информационную шину соединены с информационным входом-выходом микрокомпрессора, адресный выход которого соединен через адресную .шину с адресными входами запоминающего и перифериГжого устройств, отличающаяся тем, что, с целью упрощения, она содержит первый и второй формирователи сигналов Чтениезапись, к первым входам которых поключер; в1)Гход разряда адресного выхода микр(.1Т1ро1де(.:сора, управляющие выходы считьтанием и записью периферийН(П I запоминающего устройств которого гт1.1Лк:1Юк:11Ы соответственно к BTopbw 1 тр(-|ч,и--1 входам первого и второго формирователей ст гналон Чтение-запись, управляю1иие выходы считыванием и записью тапомиткчющего устройства микропроцессора подключены соответственно к четвер-л/ч-гхи пятому вxoдa i первого формирователя сигналов Чтение-запись, первый и второй ВЫХОДЬ которого ПОДКЛЮЧ1:(М соответственно к управляющим вхолам считыванием п записью периферийН.::го устройства, первь й и второй выхгЛы второго формирователя сигналов Чтение-запись подключоны соответственно к управляюши входам считывание:-; и записью запоминающего устройства, первый формирователь ситналов Чтение-запись содержит два элемента И и два элемента iUD-l, причем первый вход первого формтфовате.ля сиг KasiEbj налов Чте;Ие-зап сь подключен к первым входам первого и второго элементов И, выходы которых подключены соответствечно к вторым входам первого и второго элементов ИЛИ, вторые входы которых н: вторые входы первого и второго элементов И подключены соответст1 енно к второму, третьему, четвертому и пятому входам первого формирователя сигналов Чте, первый и второй выходы ние-запись которого являются выходами первого и второго элементов ИЛ1-} соответственно, второй формирователь сигналов Чтение-запись содержит элемент И-НЕ и два элемента И, первьш вход второго формирователя сигналов Чтение-запись через элемент И-НЕ подключен к первым входам первого и второго элементов И, к вторым входам которых подключены соответственно второй и третий входы второгс борми

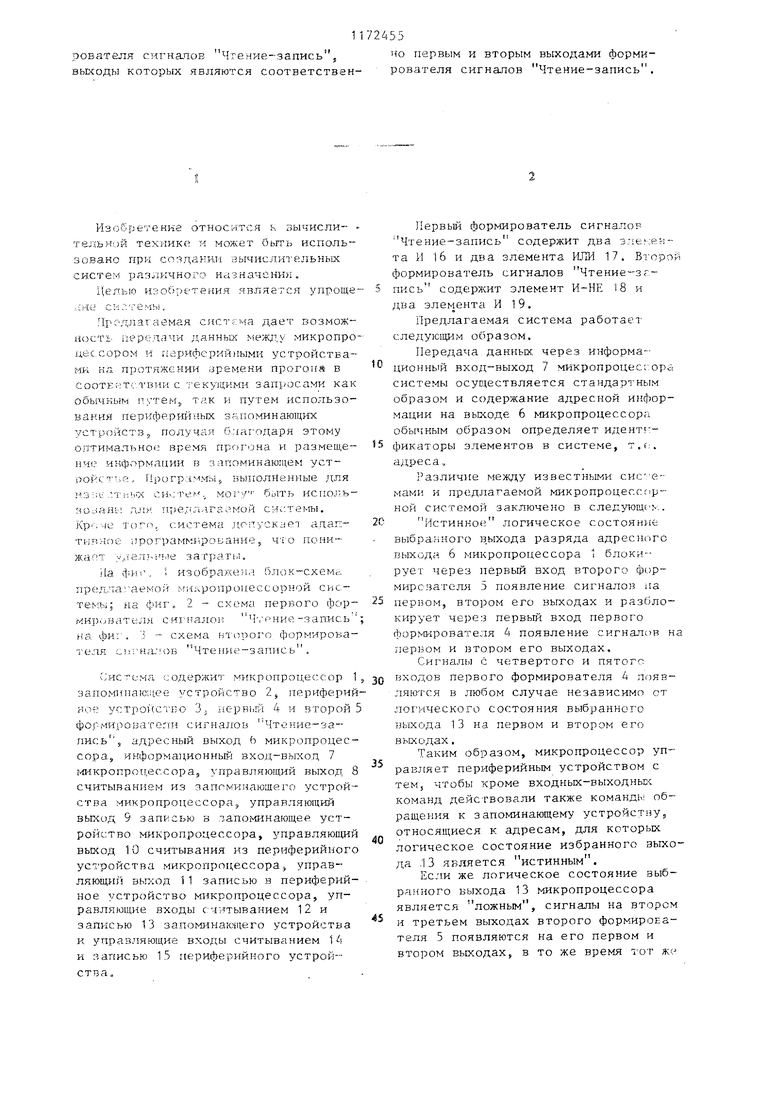

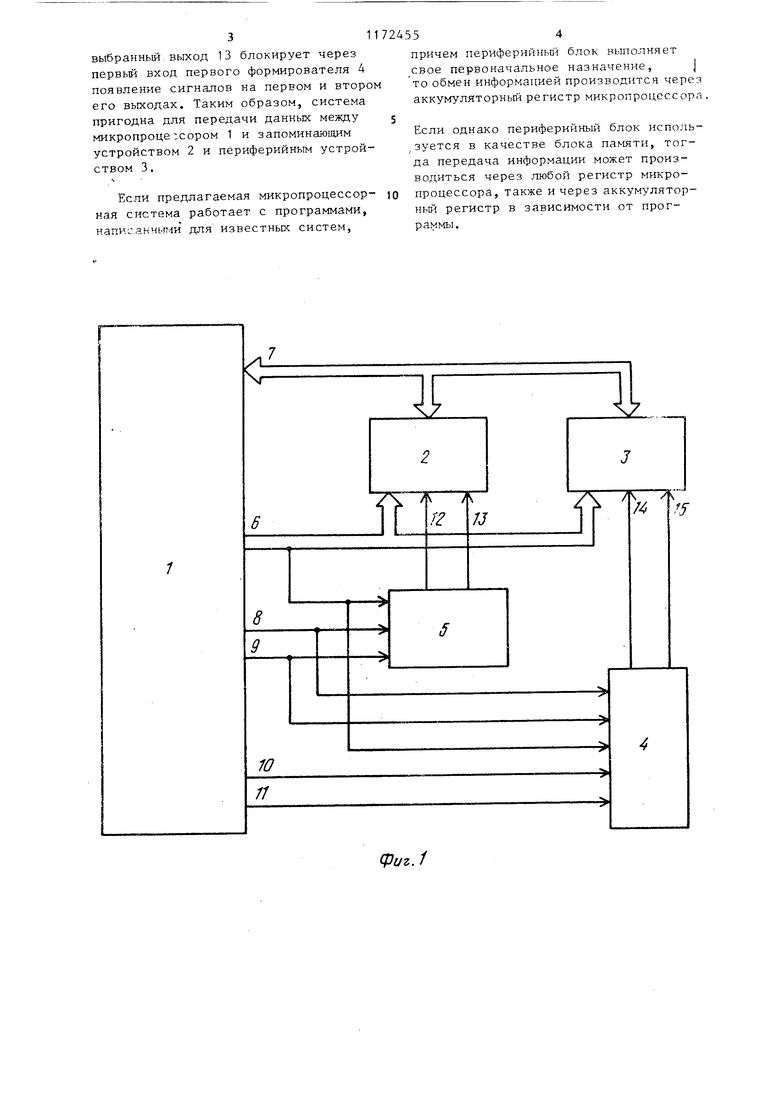

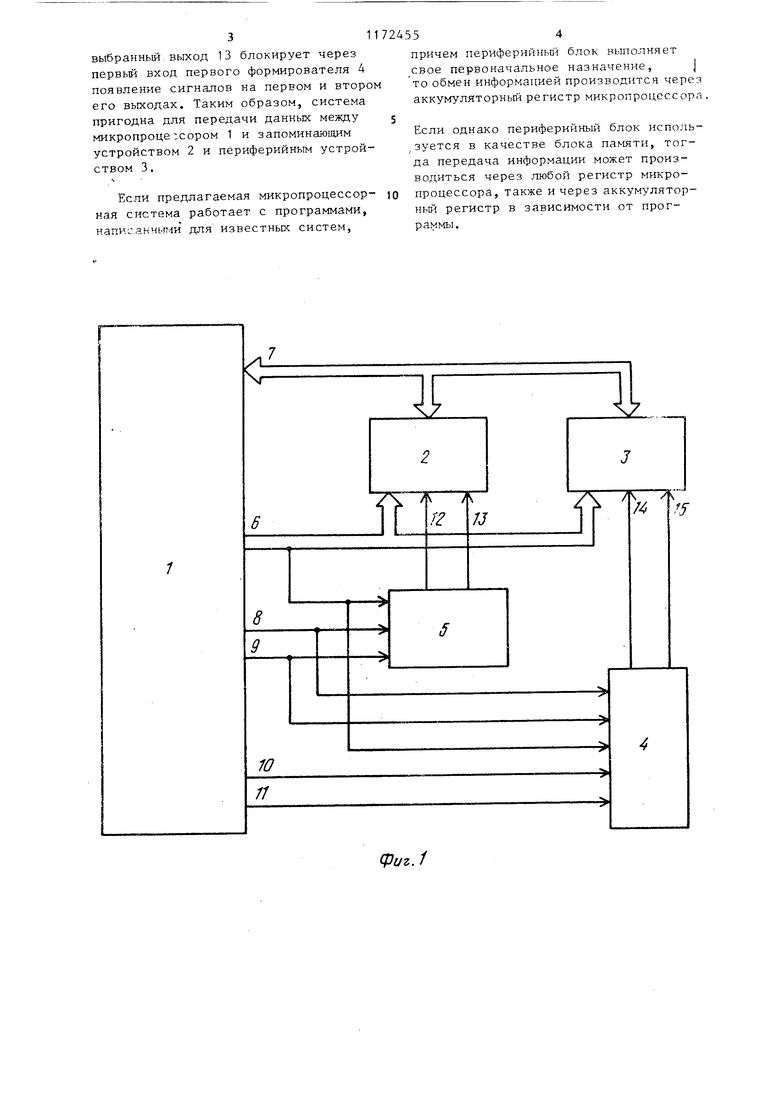

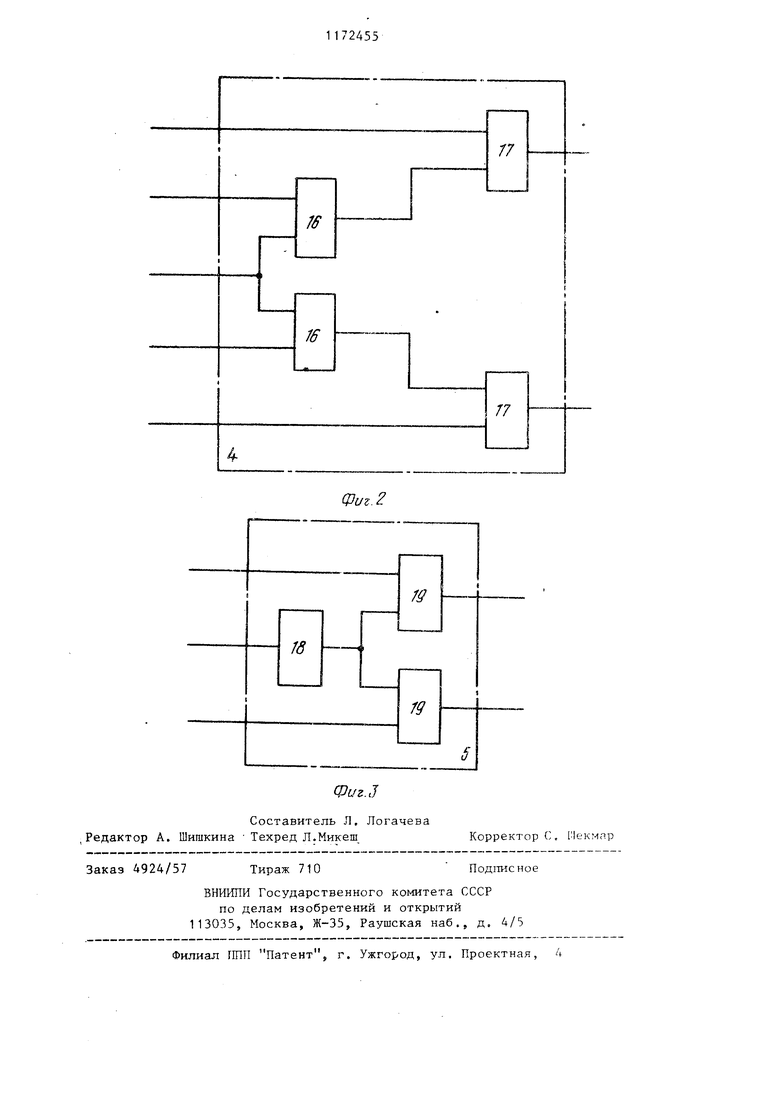

Изобретение относится к вычислительн;)й техмике и бьггь использовано при соядакрл вычислительных систег 5 раз 1ичного назначсни ;. Целью изоб:)етения является упроще л; ИИ с к л те мы, .ЧГГ-длагаемая система дает возможHocTi- передачи данных межд,у микропро цессором и периферийными устройства мк кя. протяжении зремени прогон в cooTE.-jTfTBHH с текущими запросами как обьикым путем. т.;;к и путем использования периферийных запоминающих устройств получая благодаря этому оптимальное время npfirijHa и размеш,ени информапии в запоминающем устDOKC e, fli)oграммы5 вьпголНенпые для из :;v .Ti-ibo систем могу быть ncnojtb3o iaHt; лля У1ре;гл.ггаемой системы, Кр, че тс)Г1- с;истема дОТускает адаптиг ;- Г)е программп.рование, что понижапт ,ribH; ie затраты. На I изображена Гхпок-схемс. предлагаемой г.-и ропропессорной сисTeMTii: на фиг. 2 - схема первого формир.:лзателя сигналон Чтение -запись tis. фиг, 3 схема нторото формироват-еля с)на:ов Чтение-запись . (:истсма содержит микропроцессор запоми:на с;: ее устройство 2, периферий ycTpoitcTEo 3, иервг.й 4 и второй фор миро ватегти с иг налов Чте ние-запись, адресный вьгход Ь микропроцессора, информационный вход-выход 7 г-яикропроцессора, управляющий выход считыванием из запоминающего устройства микропроцессора, управляющий вьгход 9 записью в лапоминающее устройство микропроцессора, управляющий выход 10 считывания из периферийного усЗройства микропроцессора, управляющю вьгход 1 1 записью в периферийное устройство микропроцессора, управляющие входы с-1 ттыванием 12 и записью 13 запоминаю1цего устройства и управляющие входы считыванием 14 и записью 15 периферийного устройства. Первьй формирователь сигналов Чтение-запись содержит два И 16 и два элемента ИЛИ 17. Второй формирователь сигналов Чтение--згпись содержит элемент И-НЕ 18 и два элемента И 19, Предлагаемая система работает следу1с-1цим образом. Передача данных через информационный вход-выход 7 микропроцес;:орй системы осуществляется стандартным образом и содержание адресной информации на вьсходе 6 микропроцессора обычным образом определяет идентт-фикаторы элементов в системе, T,f;. адреса, Различие между известными сис емами и предлагаемой микропроцесссфной системой заключено в ... истинное логическое состояние выбра.нного цыхода разряда адресного выхода 6 микропроцессора 1 блокирует через первый вход второго формирователя 5 появление сигнало) па первом, втором его выходах и разблокирует че)ез первый вход первого формирователя 4 появление сигналов на первом и jBTopoM его выходах. Сигналы с че;твертого и пятого входов первого формирователя 4 появляются в любом случае независимо от логического состояния выбранного выхода 13 на первом и втором его выходах. Таким образом, микропроцессор управляет периферийным устройством с тем, чтобы кроме БХОдных-выходньЕ-i команд действовали также команды обращения к запоминающему устройству относящиеся к адресам, для которых логическое состояние избранного выхода -13 является истинным. Если же логическое состояние выбранного выхода 13 микропроцессора является ложным, сигналы на втором и третьем выходах второго формирователя 5 появляются на его первом и втором выходах, в то же время тот же

311

выбранный, выход 13 блокирует через первый вход первого формирователя 4 появление сигналов на первом и втором его выходах. Таким образом, система пригодна для передачи данных между микропроцессором 1 и запоминающим устройством 2 и периферийным устройством 3.

Если предлагаемая микропроцессорная система работает с программами, написанньп-ш для известных систем,

И. г

Ю П

724554

причем периферийный блок выполняет свое первоначальное назначение, j то обмен информацией производится череэ аккумуляторньй регистр микропроцессора,

Если однако периферийный блок исполь, зуется в качестве блока памяти, тогда передача информации может производиться через любой регистр микро10 процессора, также и через аккумуляторньй регистр в зависимости от программы.

Ж

2

J

I

Л

/ /4

/У

/J

-

(риг.1

Фиг,2

| Прангишвили И | |||

| В | |||

| Микропроцессоры и микро-ЭВМ | |||

| М., Энергия, 1979, с | |||

| Способ сопряжения брусьев в срубах | 1921 |

|

SU33A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Сплав для отливки колец для сальниковых набивок | 1922 |

|

SU1975A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-08-07—Публикация

1981-09-16—Подача