Изобретения объединены единым изобретательским замыслом и относятся к области радиотехники, а именно к области передачи сигналов в оптическом диапазоне волн, и, в частности, заявляемые устройства могут быть использованы для безопасной передачи информации по волоконно-оптическим линиям связи.

Известно устройство (см. патент Франции N 2568431, МПК6 H 04 B 9/00, 1984 г.), которое обеспечивает периодическое выделение амплитуды принимаемого оптического сигнала и сравнение ее с предшествующими значениями. Данное устройство состоит из фотодетектора, усилителя, формирователя информационных сигналов, блока автоматической регулировки усиления, аналого-цифрового преобразователя, блока памяти, компаратора и блока сигнализации. Благодаря данному устройству можно обнаружить быстрое изменение амплитуды принимаемого сигнала, превышающее определенное пороговое значение. Такое изменение свидетельствует о нарушении работы ВОЛС.

Известно и другое устройство (см. патент Швеция N 438396, МПК6 H 04 B 9/00, 1985 г., заявлено 15.04.85 г. N 8304733-2), которое предназначено для обнаружения утечки энергии из световодов оптического кабеля (ОК), соединяющего два приемопередатчика волоконно-оптической линии. Собственно блок контроля состоит из дифференциатора, низкочастотного фильтра и компаратора. По крайней мере на одном из концов волоконно-оптической линии предусмотрено волоконно-оптическое реле, которое в случае исчезновения света, передаваемого передатчиком, обеспечивает передачу света к приемнику противоположного конца линии.

Однако указанные аналоги имеют недостатки. Известные схемы настроены на обнаружение значительного изменения оптической энергии, передаваемой в ВОЛС, причем предполагается, что такие изменения могут происходить на коротком интервале времени, т.е. схемы устройств настроены на регистрацию быстрых флуктуаций оптической энергии или же обрыва ВОЛС. Медленные флуктуации, приводящие к плавному изменению значения оптической энергии в допустимых пределах в каждом отдельном импульсе, могут привести к необнаруженной утечке энергии, передаваемой в ВОЛС. Таким образом, указанные аналоги подвержены ложным тревогам и в некоторых случаях (медленные флуктуации) могут не обнаружить утечку оптической энергии.

Наиболее близким аналогом (прототипом) по технической сущности к заявляемому является устройство контроля оптических линий связи по А.с. SU N 1711341 A1, МПК6 H 04 B 10/08, заявл. 03.07.89, опубл. 07.02.92 (см. журнал "Описание изобретений" N 15, 1991-1992 г.г., стр. 116-117). Известное устройство контроля оптических линий связи состоит из оптического световода, фотодетектора, усилителя фототока, формирователя информационных сигналов, аналого-цифрового устройства, блока памяти, блока сравнения, счетчика, элемента совпадения, умножителя, амплитудного селектора, сигнального блока, тактового генератора, входа установки контрольного уровня и усилителя формирователя. В известном устройстве фотодетектор, усилитель фототока и формирователь информационных сигналов соединены последовательно. Вход фотодетектора является входом устройства, а выход формирователя информационных сигналов является информационным выходом устройства. Также последовательно соединены аналого-цифровой преобразователь, блок памяти, блок сравнения и сигнальный блок. Выход усилителя фототока соединен с входом усилителя формирователя, выход которого соединен с входом аналого-цифрового преобразователя. Выход тактового генератора соединен с тактовыми входами аналого-цифрового преобразователя и блока памяти. Выход аналого-цифрового преобразователя соединен с входом счетчика и с первым входом амплитудного селектора, выход которого соединен с первым входом элемента совпадения. Выход счетчика соединен со вторым входом элемента совпадения, выход которого соединен со стробирующим входом умножителя. Первый вход умножителя является входом установки контрольного уровня устройства. Выход блока памяти соединен с вторым входом амплитудного селектора, первым входом блока сравнения и вторым входом умножителя, выход которого соединен с вторым входом блока сравнения.

При такой схеме в прототипе обеспечивается возможность регистрации механических нарушений волоконно-оптической линии связи в течение долей единицы секунд за счет быстродействующего аналого-цифрового преобразователя, блока сравнения и совокупности блоков для формирования и корректирования контрольного уровня. При этом, в прототипе обеспечена возможность установления более высокого контрольного уровня по сравнению с аналогами за счет нечувствительности фотоприемного устройства к медленным изменениям параметров канала.

Однако устройство прототип имеет недостатки: относительно высокие вероятность пропуска, вероятность ложной тревоги и время обнаружения недопустимого снижения значения оптической энергии, передаваемой по ВОЛС. Первый недостаток объясняется возможностью занижения значения порогового контрольного уровня в процессе функционирования. Это следует из того факта, что, во-первых, устройство не реагирует на медленные изменения параметров канала, в результате которых происходит непрерывное уменьшение значения оптической энергии на допустимую величину за каждый период обновления порогового контрольного уровня. Это будет приводить к периодическому обновлению значения порогового контрольного уровня в меньшую сторону и, в конечном итоге, может привести к значительному занижению его значения. Во-вторых, занижение значения порогового контрольного уровня может произойти также из-за того, что оно формируется на основе анализа амплитуды только одного контрольного импульса на интервале единиц-десятков минут. Принятие решения на основе анализа амплитуды только одного контрольного импульса является одновременно и причиной второго недостатка - относительно высокой вероятности ложной тревоги. Это объясняется тем, что амплитуда конкретного контрольного импульса может быть по различным причинам занижена в момент обновления порогового контрольного уровня или в момент принятия решения (сравнения амплитуды текущего контрольного импульса с пороговым контрольным уровнем). Третий недостаток объясняется использованием в целях обнаружения контрольных импульсов, период следования которых значительно больше периода следования информационных.

Целью изобретений является построение устройств контроля, обеспечивающих уменьшение вероятности пропуска, вероятности ложного срабатывания и времени обнаружения недопустимого уменьшения оптической энергии, передаваемой по ВОЛС. В обоих вариантах относительное уменьшение времени обнаружения достигается использованием для обнаружения информационных импульсов. Уменьшение вероятностей пропуска обнаружения и ложного срабатывания в первом варианте достигается, во-первых, за счет вычисления значения порогового контрольного уровня на основе статистических данных об амплитуде импульсов за длительный интервал времени. Во-вторых, поддержанием значения порогового контрольного уровня в разрешенном интервале, за счет непрерывного контроля за величиной суммарного снижения порогового контрольного уровня при его обновлении. В-третьих, принятием решения на основе анализа амплитуды последовательности импульсов в течение интервала времени, необходимого для достоверного обнаружения недопустимого уменьшения оптической энергии. Уменьшение вероятностей пропуска обнаружения и ложного срабатывания во втором варианте заявляемого устройства достигается за счет его функционирования по алгоритму последовательного обнаружения, т.е. непрерывного накопления значений амплитуд всех импульсов меньше некоторого значения до достижения значения суммы порогового контрольного уровня.

Поставленная цель в первом варианте заявляемого устройства достигается тем, что в известное устройство контроля энергии, передаваемой по волоконно-оптическим линиям связи, содержащее фотодетектор, вход которого является информационным входом устройства, выход фотодетектора присоединен ко входу усилителя, аналого-цифровой преобразователь, формирователь информационных сигналов, выход которого является информационным выходом устройства, счетчик, блок памяти, блок сигнализации, первый выход которого является первым управляющим выходом устройства, дополнительно введены выделитель тактовой частоты, информационный вход которого подключен к выходу усилителя, к которому также подключен информационный вход аналого-цифрового преобразователя, тактовый вход которого соединен с выходом выделителя тактовой частоты. Информационный выход аналого-цифрового преобразователя подсоединен к первому информационному входу первого блока вычета, ко второму информационному входу которого подключен четвертый информационный выход блока памяти. Знаковый выход первого блока вычета подключен к информационным входам формирователя информационных сигналов, счетчика и счетчика с изменяемым коэффициентом счета, а также к тактовым входам блока оценки параметров сигнала и сумматора, а информационный выход первого блока вычета подключен к первым информационным входам блока оценки параметров сигнала и сумматора, ко вторым информационным входам которых подсоединены соответственно пятый информационный выход блока памяти и выход сумматора, который кроме этого соединен с информационным входом переключателя. К управляющему входу блока оценки параметров сигнала подключен информационный выход счетчика, который кроме этого также соединен с первым управляющим входом блока расчета и с управляющим входом формирователя управляющих сигналов. К сбрасывающему входу сумматора подсоединен выход счетчика с изменяемым коэффициентом счета, который кроме этого также подключен к управляющему входу переключателя. Первый информационный выход блока оценки параметров сигнала присоединен к первому информационному входу блока расчета, второй информационный выход блока оценки параметров сигнала подключен к информационному входу блока памяти и к первому информационному входу формирователя управляющих сигналов, ко второму и третьему информационным входам которого подключены соответственно второй и третий информационные выходы блока памяти. Первый информационный выход блока памяти соединен с вторым информационным входом блока расчета, второй управляющий вход которого соединен с первым управляющим выходом формирователя управляющих) сигналов, а третий информационный вход блока расчета соединен с информационным выходом формирователя управляющих сигналов, второй и третий управляющие выходы которого соединены соответственно с вторым и третьим управляющими входами блока сигнализации, четвертый управляющий выход формирователя управляющих сигналов соединен с управляющим входом блока памяти. Первый информационный выход блока расчета соединен с первым информационным входом второго блока вычета, а второй информационный выход блока расчета подключен к управляющему входу счетчика с изменяемым коэффициентом счета. Второй информационный вход второго блока вычета присоединен к выходу переключателя, знаковый выход второго блока вычета соединен с первым управляющим входом блока сигнализации, второй управляющий выход блока сигнализации является вторым управляющим выходом устройства.

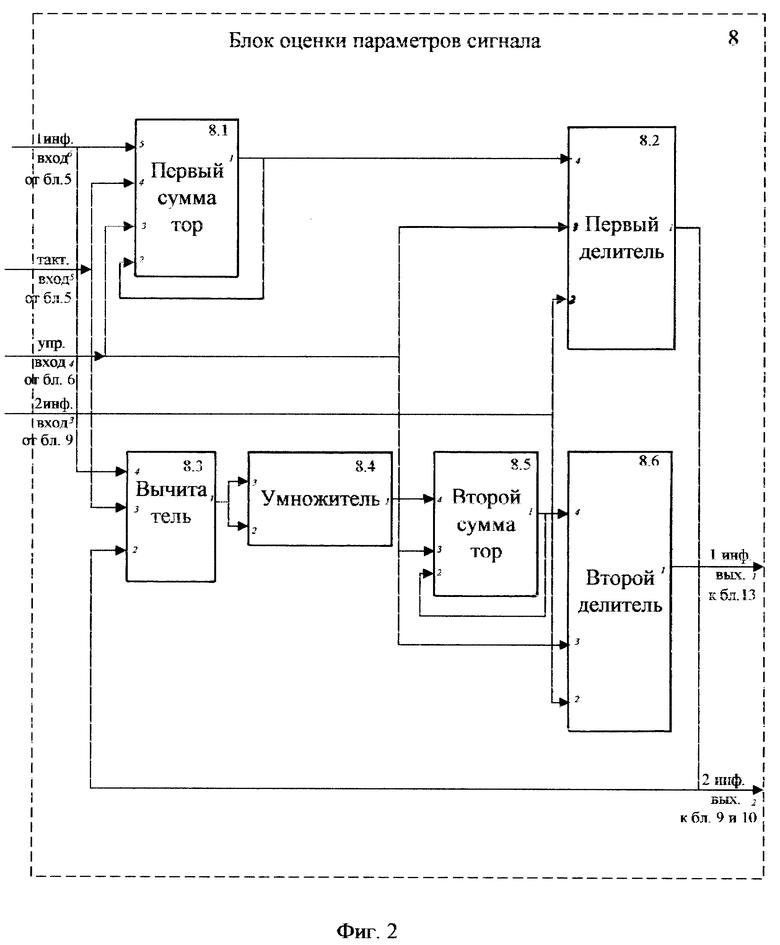

Блок оценки параметров сигнала состоит из первого сумматора, первый информационный вход которого подключен к первому информационному входу блока оценки параметров сигнала, к которому также подключен первый информационный вход вычитателя. Ко второму информационному входу первого сумматора подключен его выход, который кроме этого также подключен к первому информационному входу первого делителя, управляющий вход которого подключен к управляющему входу блока оценки параметров сигнала, к которому также подключены сбрасывающие входы первого и второго сумматоров, и управляющий вход второго делителя. Вторые информационные входы первого и второго делителей подсоединены к второму информационному входу блока оценки параметров сигнала, тактовый вход которого соединен с тактовыми входами первого сумматора и вычитателя. Ко второму информационному входу вычитателя подключен выход первого делителя, который является вторым информационным выходом блока оценки параметров сигнала. Выход вычитателя соединен с первым и вторым информационными входами умножителя, выход которого подключен к первому информационному входу второго сумматора, второй информационный вход которого соединен с выходом второго сумматора. К выходу второго сумматора подключен первый информационный вход второго делителя, выход которого является первым информационным выходом блока оценки параметров сигнала.

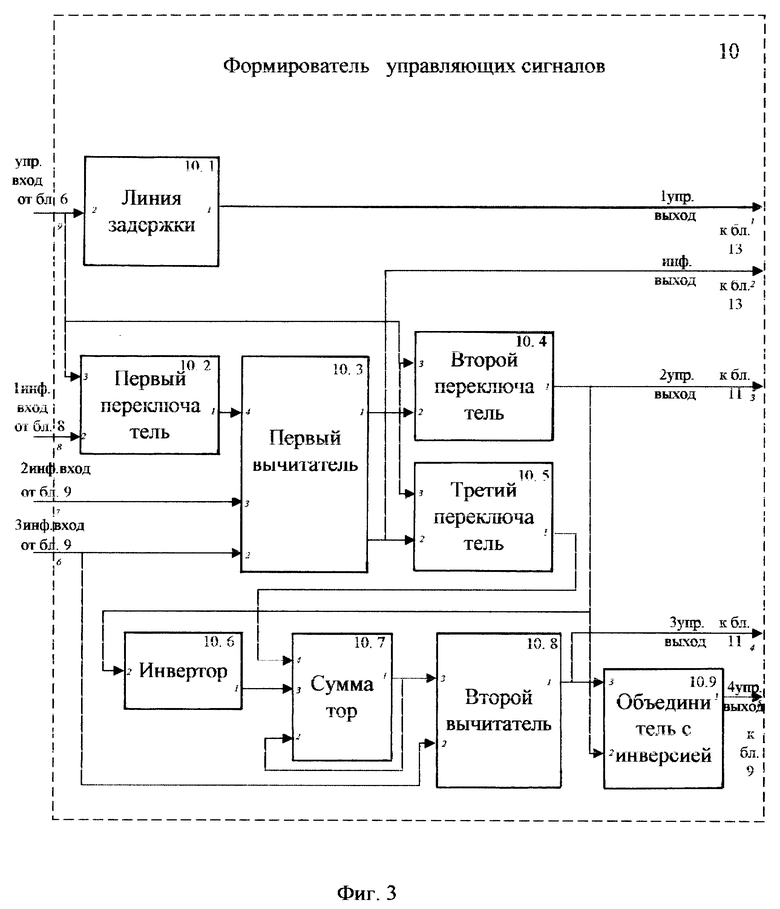

Формирователь управляющих сигналов состоит из линии задержки, вход которой подключен к управляющему входу формирователя управляющих сигналов, к которому также подключены управляющие входы соответственно первого, второго и третьего переключателей, выход линии задержки является первым управляющим выходом формирователя управляющих сигналов. Информационный вход первого переключателя соединен с первым информационным входом формирователя управляющих сигналов. Выход первого переключателя соединен с первым информационным входом первого вычитателя, второй и третий информационные входы которого подключены соответственно к второму и третьему информационным входам формирователя управляющих сигналов. Причем к третьему информационному входу также подключен второй информационный вход второго вычитателя. Знаковый выход первого вычитателя подсоединен к информационному входу второго переключателя, а информационный выход первого вычитателя подсоединен к информационному входу третьего переключателя и одновременно является информационным выходом формирователя управляющих сигналов. Выход второго переключателя соединен с информационным входом инвертора и с вторым входом объединителя с инверсией и одновременно является вторым управляющим выходом формирователя управляющих сигналов. Выход третьего переключателя соединен с первым информационным входом сумматора, к тактовому входу которого подключен выход инвертора. Ко второму информационному входу сумматора подсоединен его выход, к которому кроме этого также подключен первый информационный вход второго вычитателя. Знаковый выход второго вычитателя является третьим управляющим выходом формирователя управляющих сигналов и одновременно подключен к первому информационному входу объединителя с инверсией, выход которого является четвертым управляющим выходом формирователя управляющих сигналов.

Блок расчета состоит из первого переключателя, управляющий вход которого подключен к первому управляющему входу блока расчета. Информационный вход первого переключателя подсоединен к третьему информационному входу блока расчета, к которому также подключен информационный вход второго переключателя, управляющий вход которого присоединен к второму управляющему входу блока расчета. Выход первого переключателя соединен с вторым информационным входом делителя, первый информационный вход которого подключен к второму информационному входу блока расчета. Выход делителя соединен с первым и вторым информационными входами первого умножителя, выход которого присоединен к первому информационному входу второго умножителя, второй информационный вход которого подключен к первому информационному входу блока расчета. Выход второго умножителя является вторым информационным выходом блока расчета и одновременно подключен к первому информационному входу третьего умножителя, второй информационный вход которого подсоединен к выходу второго переключателя. Выход третьего умножителя является первым информационным выходом блока расчета.

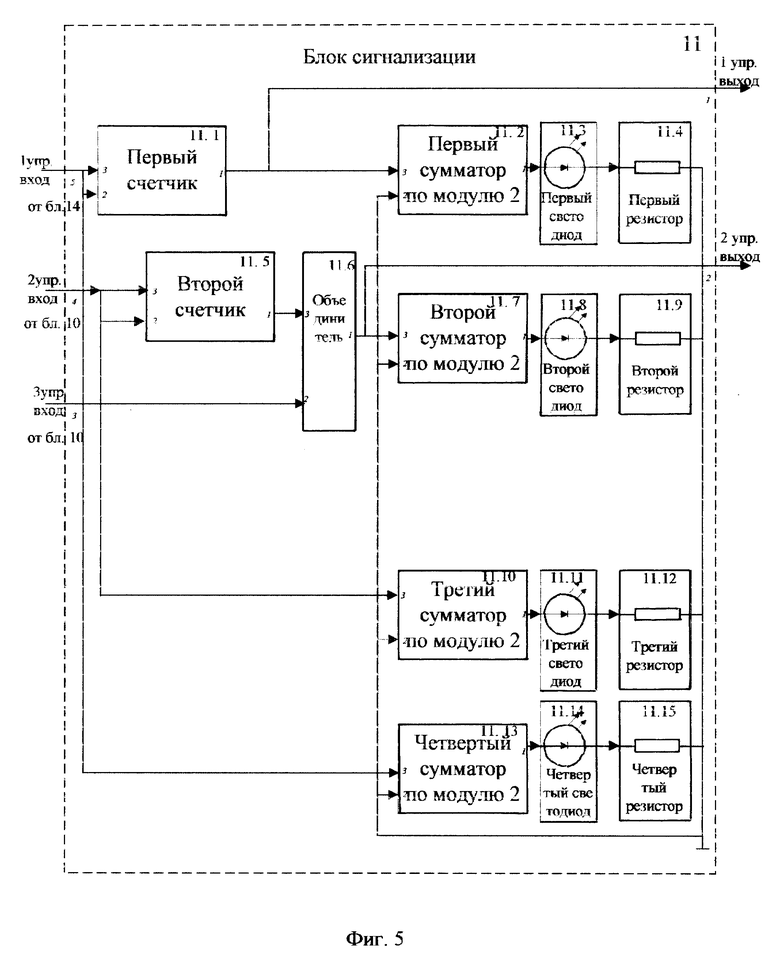

Блок сигнализации состоит из первого счетчика, информационный и сбрасывающие входы которого подключены к первому управляющему входу блока сигнализации, к которому также подключен первый информационный вход четвертого сумматора по модулю два. Выход первого счетчика является первым управляющим выходом блока сигнализации и одновременно соединен с первым информационным входом первого сумматора по модулю два. Второй информационный вход первого сумматора по модулю два запараллелен с вторыми информационными входами соответственно второго, третьего и четвертого сумматоров по модулю два и присоединен к корпусу питания. Выход первого сумматора по модулю два соединен с входом первого светодиода, выход которого подключен ко входу первого резистора. Информационный и сбрасывающий входы второго счетчика подключены к второму управляющему входу блока сигнализации, к которому также подключен первый информационный вход третьего сумматора по модулю два. Выход второго счетчика соединен с первым информационным входом объединителя, второй информационный вход которого подключен к третьему управляющему входу блока сигнализации. Выход объединителя является вторым управляющим выходом блока сигнализации и также подключен к первому информационному входу второго сумматора по модулю два. Выходы второго, третьего и четвертого сумматоров по модулю два соединены соответственно с входами второго, третьего и четвертого светодиодов, чьи выходы присоединены соответственно ко входам второго, третьего и четвертого резисторов. Выходы четырех резисторов запараллелены между собой и подключены к корпусу питания.

Поставленная цель во втором варианте заявляемого устройства достигается тем, что в известное устройство контроля энергии, передаваемой по волоконно-оптическим линиям связи, содержащее фотодетектор, вход которого является информационным входом устройства, выход фотодетектора присоединен ко входу усилителя, аналого-цифровой преобразователь, формирователь информационных сигналов, выход которого является информационным выходом устройства, счетчик, блок памяти, блок сигнализации, первый выход которого является первым управляющим выходом устройства, дополнительно введены выделитель тактовой частоты, аналого-цифровой преобразователь и блок принятия решения, информационные входы которых подключены к выходу усилителя. Тактовые входы аналого-цифрового преобразователя и блока принятия решения подсоединены к выходу выделителя тактовой частоты. Информационный выход аналого-цифрового преобразователя присоединен ко второму информационному входу блока вычета. К тактовому входу блока вычета подключен выход блока принятия решения, который также соединен со входом формирователя информационных сигналов. К первому информационному входу блока вычета подсоединен второй информационный выход блока памяти. Знаковый выход блока вычета соединен со сбрасывающим и информационным входом счетчика и тактовыми входами сумматора и блока взвешивания и управления. Информационный выход блока вычета соединен с первым информационным входом сумматора, второй информационный вход которого соединен с выходом сумматора. К сбрасывающему входу сумматора подключен выход счетчика. Выход сумматора также подсоединен к первому информационному входу блока взвешивания и управления, ко второму входу которого подключена шина из трех проводов от первого выхода блока памяти. Первый, второй и третий управляющие выходы блока взвешивания и управления подключены соответственно к первому, второму и третьему управляющим входам блока сигнализации.

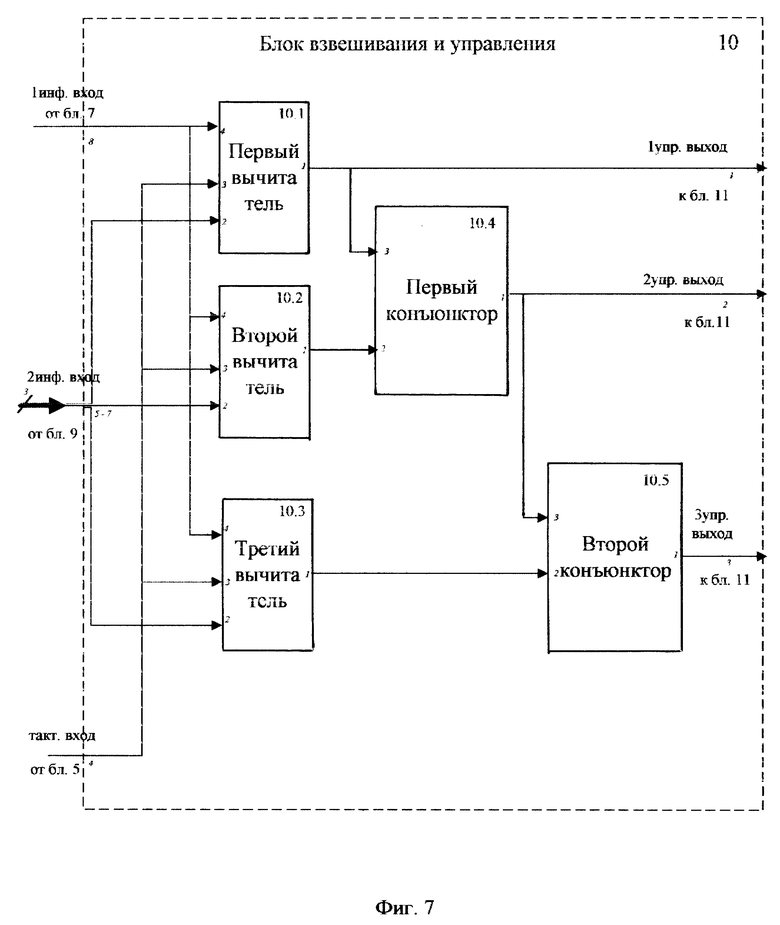

Блок взвешивания и управления состоит из первого, второго и третьего вычитателей, первые информационные входы которых запараллелены и подключены к первому информационному входу блока взвешивания и управления. Вторые информационные входы первого, второго и третьего вычитателей подключены ко второму информационному входу блока взвешивания и управления. Тактовые входы всех трех вычитателей запараллелены и подсоединены к тактовому входу блока взвешивания и управления. Выход первого вычитателя является первым управляющим выходом блока взвешивания и управления и одновременно соединен с первым информационным входом первого конъюнктора. Второй информационный вход первого конъюнктора подсоединен к выходу второго вычитателя. Выход первого конъюнктора является вторым управляющим выходом блока взвешивания и управления и одновременно соединен с первым информационным входом второго конъюнктора. Второй информационный вход второго конъюнктора подключен к выходу третьего вычитателя. Выход второго конъюнктора является третьим управляющим выходом блока взвешивания и управления.

Благодаря новой совокупности существенных признаков за счет введения в первом варианте заявляемого устройства таких блоков, как выделитель тактовой частоты, первый и второй блоки вычета, сумматор, переключатель, счетчик с изменяемым коэффициентом счета, блок оценки параметров сигнала, блок расчета и формирователь управляющих сигналов - заявляемое устройство позволяет дополнительно, кроме всех функциональных возможностей прототипа, непрерывно контролировать суммарное отклонение контрольного уровня от первоначального и реагировать в случае отклонения его значения от допустимых пределов, формировать значение контрольного уровня на основе статистических данных, принимать решение о полной тревоге по истечении некоторого рационального интервала анализа последовательности информационных импульсов.

Благодаря новой совокупности существенных признаков за счет введения во втором варианте заявляемого устройства таких блоков, как выделитель тактовой частоты, блок принятия решения, блок вычета, сумматор, блок взвешивания и управления - заявляемое устройство позволяет дополнительно, кроме всех функциональных возможностей прототипа, учитывать все уменьшения значения оптической энергии независимо от причин изменения параметров канала; использовать три различных значения пороговых уровней, вычисленных на основе накопленных статистических данных об амплитуде импульсов (на этапе доэксплуатационных исследований ВОЛС) для отображения состояния ВОЛС в процессе функционирования; проводить обнаружение снижения энергии, передаваемой в ВОЛС, по информационным импульсам.

Проведенный анализ уровня техники позволил установить, что аналоги, характеризующиеся совокупностью признаков, тождественных всем признакам заявленных технических решений, отсутствуют, что указывает на их соответствие условию патентноспособности "новизна". Результаты поиска известных решений в данной и смежных областях техники с целью выявления признаков, совпадающих с отличительными от прототипа признаками заявленных устройств, показали, что они не следуют явным образом из уровня техники. Из уровня техники также не выявлена известность влияния предусматриваемых существенными признаками заявленных изобретений преобразований на достижение указанного технического результата. Следовательно, заявленные изобретения соответствуют условию патентноспособности "изобретательский уровень".

Заявленные устройства поясняется схемами:

фиг. 1 - структурная схема устройства контроля энергии, передаваемой по волоконно-оптическим линиям связи (варианты), вариант I;

фиг. 2 - структурная схема блока оценки параметров сигнала;

фиг. 3 - структурная схема формирователя управляющих сигналов;

фиг. 4 - структурная схема блока расчета;

фиг. 5 - структурная схема блока сигнализации;

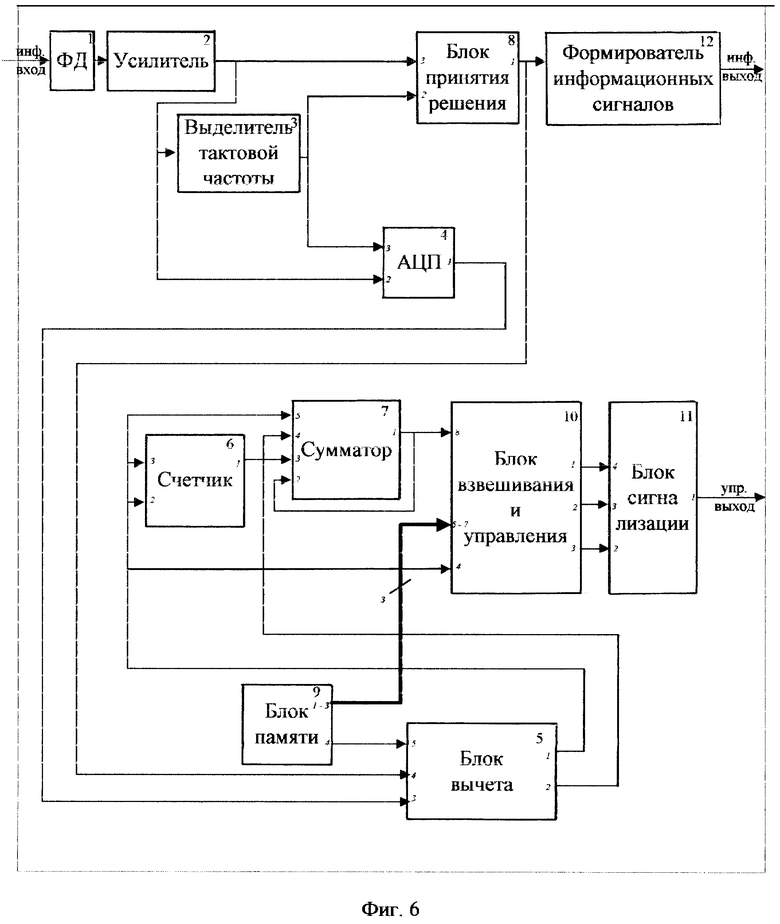

фиг. 6 - структурная схема устройства контроля энергии, передаваемой по волоконно-оптическим линиям связи (варианты), вариант II;

фиг. 7 - структурная схема блока взвешивания и управления.

Устройство контроля энергии, передаваемой по волоконно-оптическим линиям связи (вариант I), показанное на фиг. 1, состоит из фотодетектора 1, усилителя 2, выделителя тактовой частоты 3, аналого-цифрового преобразователя 4, первого блока вычета 5, счетчика 6, сумматора 7, блока оценки параметров сигнала 8, блока памяти 9, формирователя управляющих сигналов 10, блока сигнализации 11, формирователя информационных сигналов 12, блока расчета 13, второго блока вычета 14, переключателя 15, счетчика с изменяемым коэффициентом счета 16. При этом вход фотодетектора 1 является информационным входом устройства, выход фотодетектора 1 подключен ко входу усилителя 2. К выходу усилителя 2 подключены информационные входы выделителя тактовой частоты 3 и аналого-цифрового преобразователя 4, тактовый вход которого соединен с выходом выделителя тактовой частоты 3. Информационный выход аналого-цифрового преобразователя 4 подсоединен к первому информационному входу первого блока вычета 5, ко второму информационному входу которого подключен четвертый информационный выход блока памяти 9. Знаковый выход первого блока вычета 5 подключен к информационным входам формирователя информационных сигналов 12, счетчика 6 и счетчика с изменяемым коэффициентом счета 16, а также к тактовым входам блока оценки параметров сигнала 8 и сумматора 7. Выход формирователя информационных сигналов 12 является информационным выходом устройства. Информационный выход первого блока вычета 5 подключен к первым информационным входам блока оценки параметров сигнала 8 и сумматора 7, ко вторым информационным входам которых подсоединены соответственно пятый информационный выход блока памяти 9 и выход сумматора 7, который кроме этого соединен с информационным входом переключателя 15. К управляющему входу блока оценки параметров сигнала 8 подключен информационный выход счетчика 6, который кроме этого также соединен с первым управляющим входом блока расчета 13 и с управляющим входом формирователя управляющих сигналов 10. К сбрасывающему входу сумматора 7 подсоединен выход счетчика с изменяемым коэффициентом счета 16, который кроме этого также подключен к управляющему входу переключателя 15. Первый информационный выход блока оценки параметров сигнала 8 присоединен к первому информационному входу блока расчета 13, второй информационный выход блока оценки параметров сигнала 8 подключен к информационному входу блока памяти 9 и к первому информационному входу формирователя управляющих сигналов 10, ко второму и третьему информационным входам которого подключены соответственно второй и третий информационные выходы блока памяти 9. Первый информационный выход блока памяти 9 соединен с вторым информационным входом блока расчета 13, второй управляющий вход которого соединен с первым управляющим выходом формирователя управляющих сигналов 10, а третий информационный вход блока расчета 13 соединен с информационным выходом формирователя управляющих сигналов 10, второй и третий управляющие выходы которого соединены соответственно с вторым и третьим управляющими входами блока сигнализации 11, четвертый управляющий выход формирователя управляющих сигналов 10 соединен с управляющим входом блока памяти 9. Первый информационный выход блока расчета 13 соединен с первым информационным входом второго блока вычета 14, а второй информационный выход блока расчета 13 подключен к управляющему входу счетчика с изменяемым коэффициентом счета 16. Второй информационный вход второго блока вычета 14 присоединен к выходу переключателя 15, знаковый выход второго блока вычета 14 соединен с первым управляющим входом блока сигнализации 11, первый и второй управляющие выходы блока сигнализации 11 является соответственно первым и вторым управляющим выходом устройства.

Блок оценки параметров сигнала 8, показанный на фиг. 2, предназначенный для накопления статистических данных об амплитуде импульсов высокого уровня и на ее основе вычисления средней величины и дисперсии значения амплитуды импульсов. Блок оценки параметров сигнала 8 состоит из первого сумматора 8.1, первого делителя 8.2, вычитателя 8.3, умножителя 8.4, второго сумматора 8.5, второго делителя 8.6. Первый информационный вход первого сумматора 8.1 подключен к первому информационному входу блока оценки параметров сигнала 8, к которому также подключен первый информационный вход вычитателя 8.3. Ко второму информационному входу первого сумматора 8.1 подключен его выход, который кроме этого также подключен к первому информационному входу первого делителя 8.2, управляющий вход которого подключен к управляющему входу блока оценки параметров сигнала 8, к которому также подключены сбрасывающие входы первого 8.1 и второго сумматоров 8.2, и управляющий вход второго делителя 8.6. Вторые информационные входы первого 8.2 и второго делителей 8.6 подсоединены к второму информационному входу блока оценки параметров сигнала 8, тактовый вход которого соединен с тактовыми входами первого сумматора 8.1 и вычитателя 8.3. Ко второму информационному входу вычитателя 8.3 подключен выход первого делителя, который является вторым информационным выходом блока оценки параметров сигнала 8. Выход вычитателя 8.3 соединен с первым и вторым информационными входами умножителя 8.4, выход которого подключен к первому информационному входу второго сумматора 8.5, второй информационный вход которого соединен с выходом второго сумматора 8.5. К выходу второго сумматора 8.5 подключен первый информационный вход второго делителя 8.6, выход которого является первым информационным выходом блока оценки параметров сигнала 8.

Цифровые схемы сумматора, делителя, вычитателя и умножителя известны и описаны, например, в книге П.Хоровиц, У.Хилл "Искусство схемотехники", М.: Мир. 1983, в 2-х томах, т. 1, стр. 533-534, а также Гусев В.И. и др., С.-Пб. : СПбВВИУС. 1995, стр. 10. В частности, сумматор можно реализовать на микросхеме К155ИМ7, см. В.М.Шило "Популярные цифровые микросхемы". М.: Радио и связь, 1987, стр. 160; умножитель на микросхеме К555ИП9, см. там же стр. 162; вычитатель можно реализовать на микросхеме К155ИМ7, см. там же, стр. 159, делитель можно реализовать на микросхемах К555ИП9 и К155ИМ7.

Формирователь управляющих сигналов 10, показанный на фиг. 3, предназначен для формирования управляющих сигналов непрерывного контроля за значением контрольного уровня, вычисления двух информационных параметров, необходимых для принятия решения. Формирователь управляющих сигналов 10 состоит из линии задержки 10.1, первого переключателя 10.2, первого вычитателя 10.3, второго переключателя 10.4, третьего переключателя 10.5, инвертора 10.6, сумматора 10.7, второго вычитателя 10.8, объединителя с инверсией 10.9. Вход линии задержки 10.1 подключен к управляющему входу формирователя управляющих сигналов 10, к которому также подключены управляющие входы соответственно первого 10.2, второго 10.4 и третьего переключателей 10.5. Выход линии задержки 10.1 является первым управляющим выходом формирователя управляющих сигналов 10. Информационный вход первого переключателя 10.2 соединен с первым информационным входом формирователя управляющих сигналов 10. Выход первого переключателя 10.2 соединен с первым информационным входом первого вычитателя 10.3, второй и третий информационные входы которого подключены соответственно к второму и третьему информационным входам формирователя управляющих сигналов 10. Причем к третьему информационному входу также подключен второй информационный вход второго вычитателя 10.8. Знаковый выход первого вычитателя 10.3 подсоединен к информационному входу второго переключателя 10.4, а информационный выход первого вычитателя 10.3 подсоединен к информационному входу третьего переключателя 10.5 и одновременно является информационным выходом формирователя управляющих сигналов 10. Выход второго переключателя 10.4 соединен с информационным входом инвертора 10.6 и с вторым входом объединителя с инверсией 10.9 и одновременно является вторым управляющим выходом формирователя управляющих сигналов 10. Выход третьего переключателя 10.5 соединен с первым информационным входом сумматора 10.7, к тактовому входу которого подключен выход инвертора 10.6. Ко второму информационному входу сумматора 10.7 подсоединен его выход, к которому кроме этого также подключен первый информационный вход второго вычитателя 10.8. Знаковый выход второго вычитателя 10.8 является третьим управляющим выходом формирователя управляющих сигналов 10 и одновременно подключен к первому информационному входу объединителя с инверсией 10.9, выход которого является четвертым управляющим выходом формирователя управляющих сигналов 10.

Схемы линий задержек известны и описаны, например, в книге В.П. Авраменко и А.А. Ланнэ "Электрические линии задержки и фазовращатели". М.: Связь, 1973 г. В качестве линии задержки планируется использовать D-триггеры, схемы которых описаны, например, в книге Гусев В.И. и др., С.-Пб.: СПбВВИУС. 1995, стр. 89-94. В частности, такая схема может быть реализована на микросхеме К155ТМ2. В качестве переключателя планируется использовать коммутатор цифровых сигналов, схемы построения которых известны и описаны, например, в книге В. М. Шило "Популярные цифровые микросхемы". М.: Радио и связь. 1987, стр. 224-225. В частности, такие схемы можно реализовать на микросхеме К176КТ1 или К561КТ3. Схемы инверторов известны и описаны, например, в книге П.Хоровиц, У.Хилл "Искусство схемотехники", М.: Мир. 1983, в 2-х томах, т. 1, стр. 510. В частности, такую схему можно реализовать на микросхеме К555ЛН2 или К531ЛН2. В качестве объединителя с инверсией планируется использовать логический элемент "ИЛИ-НЕ", схема построения которого известна и описана, например, в книге П.Хоровиц, У.Хилл "Искусство схемотехники", М.: Мир. 1983, в 2-х томах, т. 1, стр. 510. В частности, такую схему можно реализовать на микросхеме К555ЛЕ или К531ЛЕ. Схемы вычитателя и сумматора известны и описаны, например, П.Хоровиц, У.Хилл "Искусство схемотехники", М.: Мир. 1983, в 2-х томах, т. 1, стр. 533-534, а также Гусев В.И. др., С.-Пб: СПбВВИУС. 1995, стр. 10. В частности, сумматор и вычитатель можно реализовать на микросхеме К155ИМ7.

Блок расчета 13, показанный на фиг. 4, предназначен для вычисления значений порогового контрольного уровня и коэффициента для счетчика с изменяемым коэффициентом счета. Блок расчета 13 состоит из первого переключателя 13.1, делителя 13.2, первого умножителя 13.3, второго умножителя 13.4, второго переключателя 13.5, третьего умножителя 13.6. Управляющий вход первого переключателя 13.1 подключен к первому управляющему входу блока расчета 13. Информационный вход первого переключателя 13.1 подсоединен к третьему информационному входу блока расчета 13, к которому также подключен информационный вход второго переключателя 13.5, управляющий вход которого присоединен к второму управляющему входу блока расчета 13. Выход первого переключателя 13.1 соединен с вторым информационным входом делителя 13.2, первый информационный вход которого подключен к второму информационному входу блока расчета 13. Выход делителя 13.2 соединен с первым и вторым информационными входами первого умножителя 13.3, выход которого присоединен к первому информационному входу второго умножителя 13.4, второй информационный вход которого подключен к первому информационному входу блока расчета 13. Выход второго умножителя 13.4 является вторым информационным выходом блока расчета 13 и одновременно подключен к первому информационному входу третьего умножителя 13.6, второй информационный вход которого подсоединен к выходу второго переключателя 13.5. Выход третьего умножителя является первым информационным выходом блока расчета 13.

В качестве переключателя планируется использовать коммутатор цифровых сигналов, схемы построения которых известны и описаны, например, в книге В. М. Шило "Популярные цифровые микросхемы". М. : Радио и связь, 1987, стр. 224-225. В частности, такие схемы можно реализовать на микросхеме К176КТ1 или К561КТ3. Цифровые схемы делителя и умножителя известны и описаны, например, в книге П.Хоровиц, У.Хилл "Искусство схемотехники", М.: Мир. 1983, в 2-х томах, т. 1, стр. 533-534, а также Гусев В.И. и др., С.-Пб.: СПбВВИУС. 1995, стр. 10. В частности, умножитель можно реализовать на микросхеме К555ИП9, делитель можно реализовать на микросхемах К555ИП9 и К155ИМ7.

Блок сигнализации 11, показанный на фиг. 5, предназначен для отображения состояния ВОЛС по энергетическому параметру и регистрации полной тревоги при гарантированном обнаружении (с низкими вероятностями пропуска и ложной тревоги) уменьшения энергии, передаваемой в ВОЛС. Блок сигнализации 11 состоит из первого счетчика 11.1, первого сумматора по модулю два 11.2, первого светодиода 11.3, первого резистора 11.4, второго счетчика 11.5, объединителя 11.6, второго сумматора по модулю два 11.7, второго светодиода 11.8, второго резистора 11.9, третьего сумматора по модулю два 11.10, третьего светодиода 11.11, третьего резистора 11.12, четвертого сумматора по модулю два 11.13, четвертого светодиода 11.14, четвертого резистора 11.15. Информационный и сбрасывающие входы первого счетчика 11.1 подключены к первому управляющему входу блока сигнализации 11, к которому также подключен первый информационный вход четвертого сумматора по модулю два 11.13. Выход первого счетчика 11.1 является первым управляющим выходом блока сигнализации 11 и одновременно соединен с первым информационным входом первого сумматора по модулю два 11.2. Второй информационный вход первого сумматора по модулю два 11.2 запараллелен с вторыми информационными входами соответственно второго 11.7, третьего 11.10 и четвертого сумматоров по модулю два 11.13 и присоединен к корпусу питания. Выход первого сумматора по модулю два 11.2 соединен с входом первого светодиода 11.3, выход которого подключен ко входу первого резистора 11.4. Информационный и сбрасывающий входы второго счетчика 11.5 подключены к второму управляющему входу блока сигнализации 11, к которому также подключен первый информационный вход третьего сумматора по модулю два 11.10. Выход второго счетчика 11.5 соединен с первым информационным входом объединителя 11.6, второй информационный вход которого подключен к третьему управляющему входу блока сигнализации 11. Выход объединителя 11.6 является вторым управляющим выходом блока сигнализации 11 и также подключен к первому информационному входу второго сумматора по модулю два 11.7. Выходы второго 11.7, третьего 11.10 и четвертого сумматоров по модулю два 11.13 соединены соответственно с входами второго 11.8, третьего 11.11 и четвертого светодиодов 11.14, чьи выходы присоединены соответственно ко входам второго 11.9, третьего 11.12 и четвертого резисторов 11.15. Выходы четырех резисторов запараллелены между собой и подключены к корпусу питания.

Схемы счетчиков известны и описаны, например, в книге Гусев В.И. и др., С. -Пб. : СПбВВИУС. 1995, стр. 168-183, а также в книге Л.М. Мальцева и др. "Основы цифровой техники". М.: Радио и связь. 1986, стр. 40-47. В частности, схема счетчика может быть реализована на микросхеме 155ИЕ9 или К555ИЕ10. Схемы сумматоров по модулю два известны и описаны, например, в книге Л.М. Мальцева и др. "Основы цифровой техники". М.: Радио и связь. 1986, стр. 21-22. В частности, схема счетчика может быть реализована на микросхеме К555ЛП5 или К531ЛП5. В качестве объединителя планируется использование логического элемента "ИЛИ", схемы построения которых известны и описаны, например, в книге Гусев В. И. и др., С.-Пб.: СПбВВИУС. 1995, стр. 40. В частности, такую схему можно реализовать на микросхеме К555ЛЕ или К531ЛЕ. Схемы светодиодов известны и описаны, например, в книге Л.М. Мальцева и др. "Основы цифровой техники". М.: Радио и связь. 1986, стр. 95-98. В частности, в качестве светодиода можно использовать ЗЛ341Б.

Устройство контроля энергии, предаваемой по волоконно-оптическим линиям связи (вариант II), показанное на фиг. 6, состоит из фотодетектора 1, усилителя 2, выделителя тактовой частоты 3, аналого-цифрового преобразователя 4, блока вычета 5, счетчика 6, сумматора 7, блока принятия решения 8, блока памяти 9, блока взвешивания и управления 10, блока сигнализации 11. При этом вход фотодетектора 1 является информационным входом устройства, выход фотодетектора 1 подключен ко входу усилителя 2. К выходу усилителя 2 подключены информационные входы выделителя тактовой частоты 3, аналого-цифрового преобразователя 4, блока принятия решения 8. Тактовые входы аналого-цифрового преобразователя 4 и блока принятия решения 8 подсоединены к выходу выделителя тактовой частоты 3. Выход аналого-цифрового преобразователя 4 присоединен ко второму информационному входу блока вычета 5. К тактовому входу блока вычета 5 подключен выход блока принятия решения 8, который также соединен со входом формирователя информационных сигналов 12. Выход формирователя информационных сигналов 12 является информационным выходом устройства. К первому информационному входу блока вычета 5 подсоединен второй информационный выход блока памяти 9. Знаковый выход блока вычета 5 соединен со сбрасывающим и информационным входом счетчика 6 и тактовыми входами сумматора 7 и блока взвешивания и управления 10. Информационный выход блока вычета 5 соединен с первым информационным входом сумматора 7, второй информационный вход которого соединен с выходом сумматора 7. К сбрасывающему входу сумматора 7 подключен выход счетчика 6. Выход сумматора 7 также подсоединен к первому информационному входу блока взвешивания и управления 10, ко второму входу которого подключена шина из трех проводов от первого выхода блока памяти 9. Первый, второй и третий управляющие выходы блока взвешивания и управления 10 подключены соответственно к первому, второму и третьему управляющим входам блока сигнализации 11. Выход блока сигнализации 11 является управляющим выходом устройства.

Блок взвешивания и управления 10, показанный на фиг. 7, предназначен для взвешивания накопленной суммы амплитуд импульсов при использовании трех различных пороговых значений и на этой основе формирования соответствующего управляющего сигнала. Блок взвешивания и управления 10 состоит из первого 10.1, второго 10.2 и третьего 10.3 вычитателей, первого 10.4 и второго конъюнктора 10.5. Первые информационные входы первого 10.1, второго 10.2 и третьего 10.3 вычитателей запараллелены и подключены к первому информационному входу блока взвешивания и управления 10. Вторые информационные входы первого 10.1, второго 10.2 и третьего 10.3 вычитателей подключены ко второму информационному входу блока взвешивания и управления 10. Тактовые входы всех трех вычитателей запараллелены и подсоединены к тактовому входу блока взвешивания и управления 10. Выход первого вычитателя 10.1 является первым управляющим выходом блока взвешивания и управления 10 и одновременно соединен с первым информационным входом первого конъюнктора 10.4. Второй информационный вход первого конъюнктора 10.4 подсоединен к выходу второго вычитателя 10.2. Выход первого конъюнктора 10.4 является вторым управляющим выходом блока взвешивания и управления 10 и одновременно соединен с первым информационным входом второго конъюнктора 10.5. Второй информационный вход второго конъюнктора 10.5 подключен к выходу третьего вычитателя 10.3. Выход второго конъюнктора 10.5 является третьим управляющим выходом блока взвешивания и управления 10.

В качестве конъюнктора может быть использован логический элемент И, схемы построения которого известны и описаны, например, в книге Гусев В.И. и др. , С. -Пб.: СПбВВИУС. 1995, стр. 40. В частности, такую схему можно реализовать на микросхеме К555ЛИ или К531ЛИ. Схемы вычитателя известны и описаны, например, П. Хоровиц, У. Хилл "Искусство схемотехники", М.: Мир. 1983, в 2-х томах, т. 1, стр. 533-534, а также Гусев В.И. и др., С.- Пб.: СПбВВИУС. 1995, стр. 10. В частности, вычитатель можно реализовать на микросхеме К155ИМ7.

Входящие в первый и второй варианты схемы фотодетектора, усилителя, выделителя тактовой частоты, аналого-цифрового преобразователя, блока вычета, формирователя информационных сигналов, сумматора, счетчика, блока памяти идентичны.

Схемы реализации фотодетектора и усилителя известны и описаны, например, в книге Е.А. Зак "Волоконно-оптические преобразователи с внешней модуляцией", М.: Энергоатомиздат, 1989 г., стр. 101, рис. 3.4. Серия Электроника, т. 24, М.: 1989 г., ВИНИТИ, стр. 96. В частности, фотодетектор может быть реализован на фотодиоде ФД-252 или ФД-271 АДБ, усилитель может быть реализован на микросхеме 140УД5 или 140 УД6. Схемы аналого-цифровых преобразователей известны и описаны, например, в книге Гусев В.И. и др., С.-Пб.: СПбВВИУС. 1995, стр. 229-235. В частности, такую схему можно реализовать на микросхеме К1107ПВ2 или К1107ПВ4. Схемы выделителя тактовых частот известны и описаны, например, в книге Бутусов, Верник, Галкин и др. "Волоконно-оптические системы передачи". М.: Радио и связь, 1992 г., 416 с., стр. 35, рис. 1.12. В частности, основной узел такой схемы - узкополосный фильтр может быть реализован на основе акустически связанных кварцевых резонаторов или кварцевых фильтров на поверхностных акустических волнах. Остальные субблоки выделителя тактовых частот можно выполнить, например, на микросхемах К555АГ3 и К589ХЛ4. Схемы счетчиков известны и описаны, например, в книге Гусев В.И. и др., С. -Пб. : СПбВВИУС. 1995, стр. 168-183, а также в книге Л.М. Мальцева и др. "Основы цифровой техники". М.: Радио и связь. 1986, стр. 40-47. В частности, схема счетчика может быть реализована на микросхеме 155ИЕ9 или К555ИЕ10. Схемы формирователя информационных сигналов известны и описаны, например, в книгах "Основы волоконно-оптической связи" под ред. Е.М. Дианова. М.: Советское радио. 1980, 232 с., стр. 162-165, А.Г. Мурадян, С.А. Гинзбург "Системы передачи информации по оптическому кабелю". М.: Связь. 1980, 160 с., стр. 84-113, Д. Гауэр "Оптические системы связи". М.: Радио и связь. 1989, 502 с. , стр. 369-371. В частности, схема формирователя информационных сигналов может быть реализована на микросхемах 155АГ3. Схемы блока памяти предполагается строить на элементах запоминающих устройств: ОЗУ и ППЗУ, схемы построения которых известны и описаны, например, в книге Гусев В.И. и др., С.- Пб. : СПбВВИУС. 1995, стр. 188-205. В частности, схему ОЗУ на 1024 бит можно реализовать на микросхеме К155РУ7, а схему ППЗУ на 1024 бит можно реализовать на микросхеме 530РТ1. В качестве блока вычета предполагается использование вычитателя, схема построения которого известна и описана, например, в книге П. Хоровиц, У. Хилл "Искусство схемотехники", М.: Мир. 1983, в 2-х томах, т. 1, стр. 533-534, а также Гусев В.И. и др., С.-Пб.: СПбВВИУС. 1995, стр. 10. Там же описаны схемы построения сумматоров, а также в книге Л.М. Мальцева и др. "Основы цифровой техники". М.: Радио и связь. 1986, стр. 53-55. В частности, вычитатель можно реализовать на микросхеме К500ИМ180 (см. С.В. Якубовский и др. "Цифровые и аналоговые интегральные микросхемы". Справочник. М.: Радио и связь, 1989 г., стр. 91, рис. 39 на стр. 96), а сумматор на микросхеме К155ИМ7.

Схемы остальных блоков для первого варианта заявляемого устройства известны и описаны. Схемы счетчиков известны и описаны, например, в книге В.М. Шило "Популярные цифровые микросхемы". М.: Радио и связь, 1987, стр. 94. В частности, схема счетчика с изменяемым коэффициентом счета может быть реализована на микросхеме К155ИЕ8. В качестве переключателя планируется использовать коммутатор цифровых сигналов, схемы построения которого известны и описаны, например, в книге В.М.Шило "Популярные цифровые микросхемы". М.: Радио и связь, 1987, стр. 224-225. В частности, такие схемы можно реализовать на микросхеме К176КТ1 или К561КТ3.

Схемы остальных блоков для второго варианта заявляемого устройства известны и описаны. Схемы построения блока принятия решения известны и описаны, например, в книге Бутусов, Верник, Галкин и др. "Волоконно-оптические системы передачи". М.: Радио и связь, 1992 г., 416 с., стр. 34. В частности, схема решающего устройства может быть реализована на микросхеме 521СА4. Блок сигнализации предполагается выполнить на светодиодах, схемы использования которых известны и описаны, например, в книге Л.М. Мальцева и др. "Основы цифровой техники". М.: Радио и связь. 1986, стр. 95-98. В частности, в качестве светодиода можно использовать ЗЛ341Б.

Общим в принципе работы первого и второго вариантов заявленных устройств является накопление в сумматорах значений амплитуды информационных импульсов высокого уровня и сравнение значения суммы с пороговым значением контрольного уровня, вычисленным на основе статистических данных. В первом варианте реализуется накопление значений амплитуды всех импульсов высокого уровня за фиксированный интервал времени, определяемый счетчиком с изменяемым коэффициентом счета. Во втором варианте реализуется непрерывное накопление (последовательно) значений амплитуды только тех импульсов высокого уровня, чья амплитуда оказалась меньше определенного значения.

Устройство (вариант I) работает следующим образом. Энергия оптического сигнала из оптического волокна (OB) волоконно-оптической линии связи (ВОЛС) поступает на информационный вход устройства контроля энергии, передаваемой по ВОЛС, который соединен с входом фотодетектора 1. В фотодетекторе 1 происходит детектирование поля оптической энергии (потока фотонов). С выхода фотодетектора 1 продетектированный сигнал в виде импульсов электрического тока поступает на усилитель 2, где усиливается до необходимого уровня. С выхода усилителя усиленные по амплитуде импульсы поступают на информационные входы аналого-цифрового преобразователя 4 и выделителя тактовой частоты 3.

В выделителе тактовой частоты 3 из принимаемой последовательности электрических импульсов выделяется тактовая частота. Фаза импульсов тактовой частоты на длительности периода будет определяться формой принимаемых импульсов. Поэтому тактовые импульсы с выхода выделителя 3 поступает на тактовый вход аналого-цифрового преобразователя 4 в момент наибольшего значения мгновенной амплитуды принятого импульса. Это наибольшее значение мгновенной амплитуды принятого импульса будет преобразовываться в АЦП 4 из аналогового значения в цифровой код.

Цифровой код мгновенного значения амплитуды импульса с информационного выхода аналого-цифрового преобразователя 4 поступает на первый информационный вход первого блока вычета 5, на второй информационный вход которого поступает цифровой код порогового значения амплитуды импульса, относительно которого может быть принято решение об уровне принятого импульса. Цифровой код порогового значения поступает с четвертого информационного выхода блока памяти 9. Вычисленный в первом блоке вычета 5 результат представляется знаковым разрядом и цифровым кодом разности. Знаковый бит поступает на знаковый выход первого блока вычета 5 и далее на информационные входы формирователя информационных сигналов 12, счетчика 6 и счетчика с изменяемым коэффициентом счета 16, а также на тактовые входы блока оценки параметров сигнала 8 и сумматора 7. Счетчик с изменяемым коэффициентом счета 16 и счетчик 6, реагирующие только на знаковые импульсы высокого уровня, отличаются друг от друга коэффициентами счета. Значение знакового бита отражает уровень принятого импульса. Цифровой код разности с информационного выхода первого блока вычета 5 в параллельном виде поступает на первые информационные входы блока оценки параметров сигнала 8 и сумматора 7. Этот код содержит в себе информацию о мгновенном значении xt амплитуды принятого импульса относительно порога.

В формирователе информационных сигналов 12 из поступившего знакового бита формируется информационный импульс, уровень которого соответствует уровню знакового бита. Формирование информационного импульса предполагает нормирование импульса по амплитуде, форме и временному положению.

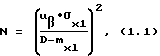

В сумматоре 7 за определенный интервал времени tN осуществляется накопление суммы относительных значений амплитуд приходящих импульсов благодаря соединению второго информационного входа сумматора с его выходом. Причем суммирование происходит только при наличии на тактовом входе сумматора 7 знакового бита высокого уровня. Это означает, что в сумматоре 7 происходит накопление значений относительных амплитуд только импульсов высокого уровня  Длительность интервала времени накопления tN зависит от значения коэффициента счета счетчика с изменяемым коэффициентом счета 16 Kсч, т.е. tN = f(Kсч). После того как счетчик с изменяемым коэффициентом 16 насчитает N знаковых импульсов высокого уровня, на его выходе появляется управляющий импульс высокого уровня, а сам счетчик 16 обнуляется. Значение N рассчитывается в блоке расчета 13 заявляемого устройства в соответствии с соотношением:

Длительность интервала времени накопления tN зависит от значения коэффициента счета счетчика с изменяемым коэффициентом счета 16 Kсч, т.е. tN = f(Kсч). После того как счетчик с изменяемым коэффициентом 16 насчитает N знаковых импульсов высокого уровня, на его выходе появляется управляющий импульс высокого уровня, а сам счетчик 16 обнуляется. Значение N рассчитывается в блоке расчета 13 заявляемого устройства в соответствии с соотношением:

где N - число импульсов, которое должен насчитать счетчик с изменяемым коэффициентом счета для появления на его выходе импульса высокого уровня, uβ - аргумент интеграла вероятностей: F(u) = β (где F(.) - интеграл вероятностей) или процентилья точки β (где β - вероятность ложного срабатывания системы контроля), D - пороговое значение системы контроля, mxl - среднее значение мгновенной амплитуды принимаемых импульсов высокого уровня xl, σxl - среднеквадратическое отклонение xl.

Для установления коэффициента счета в соответствии с поступившим из блока расчета 13 значением N в счетчике с изменяемым коэффициентом счета 16 предусмотрено изменение характера внутренних связей. С выхода этого счетчика 16 управляющий импульс поступает на сбрасывающий вход сумматора 7 и на управляющий вход переключателя 15. Поступив на управляющий вход переключателя 15, управляющий импульс разрешает прохождение через него, т.е. со входа на выход, информационного сигнала. В результате, цифровой код накопленной суммы относительных мгновенных амплитуд N импульсов высокого уровня проходит через переключатель 15. С выхода переключателя 15 цифровой код суммы поступает на второй информационный вход второго блока вычета 14. Кроме этого, по управляющему сигналу с выхода счетчика с изменяемым коэффициентом счета 16 происходит обнуление сумматора 7.

Цифровой код относительного мгновенного значения амплитуды импульса высокого уровня кроме сумматора 7 поступает на информационный вход блока оценки параметров сигнала 8. В этом блоке при наличии на его тактовом входе знакового импульса высокого уровня накапливается статистика за некоторый интервал времени T. На ее основе рассчитываются статистические характеристики относительной амплитуды принимаемого сигнала xl: средняя величина мгновенной относительной амплитуды импульсов высокого уровня - mxl T и ее дисперсия - σ

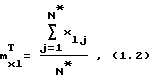

В блоке оценки параметров сигнала 8 вычисление текущего значения средней величины относительной амплитуды принимаемых импульсов высокого уровня mxl T происходит следующим образом. Цифровой код мгновенной относительной амплитуды импульсов с информационного выхода первого блока вычета 5 поступает через первый информационный вход блока оценки 8 на первый информационный вход первого сумматора 8.1, где при наличии на тактовом входе знакового импульса высокого уровня происходит накопление суммы относительных мгновенных амплитуд  импульсов высокого уровня. Это происходит благодаря наличию связи выхода первого сумматора 8.1 с его вторым информационным входом. Значение суммы с выхода первого сумматора 8.1 поступает на первый информационный вход первого делителя блока 8.2. Поступление от счетчика 6 импульса высокого уровня на управляющий вход первого делителя 8.2 разрешает в нем осуществить операцию деления цифрового кода суммы относительных амплитуд N* импульсов на цифровой код значения N*, который поступает на второй информационный вход первого делителя 8.2 с пятого выхода блока памяти 9 через второй информационный вход блока оценки параметров сигнала 8. Таким образом, вычисляется текущее среднее значение

импульсов высокого уровня. Это происходит благодаря наличию связи выхода первого сумматора 8.1 с его вторым информационным входом. Значение суммы с выхода первого сумматора 8.1 поступает на первый информационный вход первого делителя блока 8.2. Поступление от счетчика 6 импульса высокого уровня на управляющий вход первого делителя 8.2 разрешает в нем осуществить операцию деления цифрового кода суммы относительных амплитуд N* импульсов на цифровой код значения N*, который поступает на второй информационный вход первого делителя 8.2 с пятого выхода блока памяти 9 через второй информационный вход блока оценки параметров сигнала 8. Таким образом, вычисляется текущее среднее значение

цифровой код которого с выхода первого делителя 8.2 блока поступает на второй информационный выход блока оценки параметров сигнала 8 и на второй информационный вход вычитателя 8.3. Так как управляющий импульс также поступает на сбрасывающий вход первого сумматора 8.1, то происходит его обнуление.

Одновременно с началом процесса суммирования в первом сумматоре 8.1, в вычитателе 8.3 начинается процесс вычисления второй статистической характеристики - дисперсии мгновенных относительных значений амплитуд принимаемых импульсов высокого уровня σ

(xl-mxl T-1). (1.3)

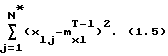

Цифровой код вычисленной разности поступает одновременно на первый и второй входы умножителя 8.4, т.е. в нем осуществляется операция возведения в квадрат:

(xl-mxl T-1)2. (1.4)

С выхода умножителя 8.4 цифровой код квадрата разности поступает на первый информационный вход второго сумматора 8.5, второй информационный вход которого подключен к его выходу. Таким образом, во втором сумматоре 8.5 происходит процесс накопления текущих значений квадрата разности, т.е.

Цифровой код результата накопленной суммы квадратов разности с выхода второго сумматора 8.5 поступает на первый информационный вход второго делителя 8.6. Приход управляющего импульса от счетчика 6 через управляющий вход блока оценки параметров сигнала 8 разрешает во втором делителе 8.6 операцию деления цифрового кода  на цифровой код значения N*, поступающий на второй информационный вход второго делителя 8.6. В этот же момент времени второй сумматор 8.5 (также как и первый сумматор 8.1) обнуляется, т. к. управляющий импульс поступает на его сбрасывающий вход. В результате операции деления на выходе второго делителя 8.6 появляется цифровой код дисперсии σ

на цифровой код значения N*, поступающий на второй информационный вход второго делителя 8.6. В этот же момент времени второй сумматор 8.5 (также как и первый сумматор 8.1) обнуляется, т. к. управляющий импульс поступает на его сбрасывающий вход. В результате операции деления на выходе второго делителя 8.6 появляется цифровой код дисперсии σ

Это цифровое значение дисперсии поступает на первый информационный выход блока оценки параметров сигнала 8. Таким образом, в конце каждого периода (T) работы блока оценки параметров сигнала на его первом и втором выходах появляются текущие оценки соответственно дисперсии и средней величины мгновенных значений относительной амплитуды принимаемых импульсов высокого уровня.

Цифровой код текущей оценки средней величины амплитуды импульсов mxl T со второго информационного выхода блока оценки поступает на информационный вход блока памяти 9 и на первый информационный вход формирователя управляющих сигналов 10 (ФУС), а цифровой код дисперсии амплитуды принимаемых импульсов σ

В формирователе управляющих сигналов 10 цифровой код средней величины амплитуды принимаемых импульсов поступает через его первый информационный вход на информационный вход первого переключателя 10.2. На управляющий вход первого переключателя 10.2 поступает через управляющий вход ФУС 10 управляющий импульс от счетчика 6, который одновременно поступает на вход линии задержки 10.1 ФУС 10 и на управляющие входы соответственно второго 10.4 и третьего 10.5 переключателей ФУС 10. В момент присутствия управляющего импульса на управляющих входах переключателей (10.2, 10.4, 10.5) разрешается прохождение информационного сигнала через них. Так цифровой код текущего значения средней величины амплитуды импульсов mxl T проключается со входа на выход первого переключателя 10.2 и поступает на первый информационный вход первого вычитателя 10.3. На второй вход первого вычитателя 10.3 от второго выхода блока памяти 9 приходит цифровой код эталонной величины среднего значения относительной амплитуды принимаемых импульсов высокого уровня mxl ЭТ, а на третий вход первого вычитателя 10.3 с третьего выхода блока памяти 9 поступает цифровой код величины максимально допустимого отклонения амплитуды импульса высокого уровня ε. Кроме того этот цифровой код (ε) также поступает на второй вход второго вычитателя 10.8 ФУС 10. В первом вычитателе 10.3 осуществляется вычисление результата разности трех сигналов - mxl ЭТ, mxl Т и ε:

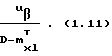

m

Таким образом, в первом вычитателе 10.3 в течение длительности управляющего импульса вычисляется значение знаменателя выражения (1.1). Со знакового выхода первого вычитателя 10.3 знаковый бит вычисленной разности поступает на информационный вход второго переключателя 10.4, а цифровой код результата разности (1.7) с информационного выхода первого вычитателя 10.3 поступает на информационный выход ФУС 10 и на информационный вход третьего переключателя 10.5. Присутствие управляющего импульса на управляющих входах второго 10.4 и третьего 10.5 переключателей обеспечивает проключение входных сигналов на выход. С выхода второго переключателя 10.4 знаковый бит цифрового кода разности поступает на второй управляющий выход ФУС 10, а также на второй информационный вход объединителя с инверсией 10.9 и на информационный вход инвертора 10.6. Если в результате вычисления в первом вычитателе 10.3 получено отрицательное значение разности (1.7), т.е. текущая величина среднего значения амплитуды отличается от эталонной на величину менее чем допустимая -ε:(m

Цифровой код разности (1.7) с выхода третьего переключателя 10.5 поступает на первый информационный вход сумматора 10.7, второй информационный вход которого соединен с его выходом. Сумматор 10.7 обеспечивает накопление цифровых значений разности (1.7) при наличии на его тактовом входе импульсов высокого уровня, поступающих с выхода инвертора 10.6. Это происходит, когда знаковый бит с выхода второго переключателя 10.4 поступает на вход инвертора 10.6 в виде импульса низкого уровня, что свидетельствует об изменении энергии, передаваемой в ВОЛС, в допустимых пределах. Таким образом, в сумматоре 10.7 происходит постоянное накопление только отрицательных результатов разницы (1.7):

Цифровой код суммы с первого выхода сумматора 10.7 поступает на первый вход второго вычитателя 10.8, где осуществляется вычисление разности двух цифровых кодов, присутствующих на его входах:

([∑(m

Таким образом, осуществляется проверка, изменилась ли эталонная величина среднего значения амплитуды импульсов mxl ЭТ на величину, большую чем допустимое значение ε. Допустимое (Δm≪ε) на каждом периоде T изменение оценки среднего значения амплитуды импульсов mxl ЭТ связано с медленными флуктуациями сигнала. Это допустимое изменение влечет за собой необходимость обновления (корректировки) эталонной оценки среднего в конце каждого периода оценки параметров сигнала. Если процесс медленных флуктуаций происходит длительное время, то число разрешенных операций обновления эталонного значения среднего может оказаться значительным. В результате может получиться, что эталонное значение mxl ЭТ изменится в итоге по отношению к первоначальному (до возникновения флуктуаций) на величину больше допустимой (>ε). Это может привести к неправильному принятию решения о величине энергии, передаваемой в ВОЛС, т. к. решения будут приниматься относительно смещенной оценки эталонного среднего. Для избежания этого сумматор 10.7 и второй вычитатель 10.8 осуществляют контроль за величиной отклонения mxl ЭТ на каждом периоде.

С выхода второго вычитателя 10.8 выходит только знаковый бит, который обозначается импульсом высокого уровня, когда значение накопленной в сумматоре 10.7 суммы превысит величину допустимого отклонения ε. Этот знаковый бит поступает на третий управляющий выход ФУС 10 и на второй вход объединителя с инверсией 10.9. Только когда на обоих входах объединителя с инверсией 10.9 присутствуют импульсы низкого уровня - "нули", на его выходе появляется управляющий импульс высокого уровня. Он поступает через четвертый управляющий выход ФУС 10 на управляющий вход блока памяти 9 и разрешает обновление эталонной оценки средней величины амплитуды принимаемых импульсов. То есть, в блоке памяти в ячейку, содержащую эталонную оценку среднего mxl ЭТ, будет записана текущая оценка mxl Т, поступившая на информационный вход блока памяти 9. Если хотя бы на одном из входов объединителя с инверсией 10.9 присутствует импульс высокого уровня, то на его выходе управляющий импульс будет обозначаться низким уровнем. Это равносильно его отсутствию. Отсутствие управляющего импульса на управляющем входе блока памяти 9 не разрешает обновление эталонной оценки средней величины амплитуды принимаемых импульсов.

По истечении времени τупр присутствия на управляющем входе ФУС 10 управляющего импульса, все три переключателя (10.2, 10.4, 10.5) ФУС оказываются закрытыми, поэтому на втором, третьем и четвертых управляющих выходах ФУС 10 будут присутствовать только импульсы низкого уровня. С этого момента времени на первый вычитатель 10.3 приходят импульсы только со второго и третьего информационных входов ФУС 10, т.е. в первом вычитателе 10.3 теперь осуществляется вычисление разности двух величин:

m

На втором выходе первого вычитателя 10.3 образуется уже цифровой код пороговой величины D, который направляется на информационный выход ФУС 10. Синхронно с ним на первый управляющий выход ФУС поступает задержанный в линии задержки 10.1 управляющий импульс.

Таким образом, в течение длительности управляющего импульса τупр, начиная с момента его прихода на управляющий вход ФУС 10, задействуются второй, третий и четвертый управляющие и информационный выход, а после окончания длительности управляющего импульса используются только первый управляющий и информационный выход. Причем, в течение τупр на информационный выход ФУС 10 поступает цифровой код разности трех сигналов m

Управляющий сигнал от счетчика 6 одновременно с приходом в ФУС 10 поступает и на первый управляющий вход блока расчета 13, с которым соединен управляющий вход первого переключателя 13.1 этого блока. В течение длительности управляющего импульса цифровой код разности трех сигналов m

Цифровой код результата деления поступает одновременно на первый и второй входы первого умножителя 13.3, где осуществляется перемножение (операция возведения в квадрат):

Цифровой код с выхода первого умножителя 13.3 поступает на первый информационный вход второго умножителя 13.4. На второй информационный вход второго умножителя 13.4 поступает цифровой код дисперсии амплитуды принимаемых импульсов σ

Таким образом, на выходе второго умножителя 13.4 появляется цифровой код числа импульсов N (см. (1.1)). Цифровой код значения N с выхода второго умножителя 13.4 поступает на второй информационный выход блока расчета 13 и на первый информационный вход третьего умножителя 13.6. На второй информационный вход третьего умножителя 13.6 поступает цифровой код значения пороговой величины амплитуды принимаемого импульса высокого уровня - D. Это значение поступает с выхода второго переключателя 13.5, когда управляющий импульс присутствует на его управляющем входе, куда он поступает с первого управляющего выхода формирователя управляющих сигналов 10 через второй управляющий вход блока расчета 13. В третьем умножителе 13.6 осуществляется вычисление результата произведения: D•N, т.е. формируется пороговое значение суммы амплитуд N принятых импульсов высокого уровня. Вычисленный цифровой код порога суммы амплитуд N импульсов поступает на первый информационный выход блока расчета 13, откуда поступает на первый информационный вход второго блока вычета 14. Со второго информационного выхода блока расчета 13 цифровой код значения N поступает на управляющий вход счетчика с изменяемым коэффициентом счета 16.

Во втором блоке вычета 14 происходит вычисление цифрового значения разности двух кодов: 1) порогового значения суммы амплитуд N импульсов и 2) суммы амплитуд N импульсов, цифровой код которой поступает на второй информационный вход второго блока вычета 14 с выхода переключателя 15. С выхода второго блока вычета 14 выходит только знаковый бит вычисленной разности:  Если значение световой энергии, передаваемой в ВОЛС, на интервале времени tN приема N импульсов высокого уровня было по какой-либо причине занижено, что выразилось в преобладании порогового значения над значением суммы амплитуд N импульсов, то на выходе второго блока вычета 14 знаковый бит появится в виде импульса высокого уровня.

Если значение световой энергии, передаваемой в ВОЛС, на интервале времени tN приема N импульсов высокого уровня было по какой-либо причине занижено, что выразилось в преобладании порогового значения над значением суммы амплитуд N импульсов, то на выходе второго блока вычета 14 знаковый бит появится в виде импульса высокого уровня.

Этот импульс поступает на первый управляющий вход блока сигнализации 11 и далее на информационный и сбрасывающий входы первого счетчика 11.1, а также на первый вход четвертого сумматора по модулю два 11.13. Так как на вторых входах всех сумматоров по модулю два блока сигнализации 11 присутствуют импульсы низкого уровня - "нули", то в данный момент на выходе четвертого сумматора по модулю два 11.13 появится импульс высокого уровня, в результате чего образуется электрическая цепь протекания тока через четвертый светодиод 11.14, четвертый резистор 11.15 и на корпус питания. Таким образом, четвертый светодиод 11.14 будет "светиться", что сигнализирует регистрацию первоначального снижения световой энергии, передаваемой в ВОЛС, на недопустимую величину. Кроме этого первый счетчик 11.1 изменит свое внутреннее состояние на единицу.

Если на первый управляющий вход блока сигнализации 11 будут приходить последовательно друг за другом M импульсов высокого уровня, причем число M определяется коэффициентом счета первого счетчика 11.1, то на выходе первого счетчика 11.1 появится импульс высокого уровня, который поступит на первый вход первого сумматора по модулю два 11.2. В результате на выходе этого сумматора 11.2 появляется импульс высокого уровня и образуется электрическая цепь протекания тока через первый светодиод 11.3. Первый светодиод 11.3 начинает светиться, что свидетельствует о регистрации недопустимого уменьшения световой энергии, передаваемой в ВОЛС, на интервале M•tN (или на интервале M•N импульсов высокого уровня). В этом случае формируется сигнал полной тревоги.

Кроме этого, импульс высокого уровня с выхода первого счетчика 11.1 поступит на первый управляющий выход блока сигнализации 11, к которому может быть подключен блок блокирования (прекращения) передачи или блок переключения передаваемого излучения информационной оптической несущей на резервное оптическое волокно.

Если на первый управляющий вход блока сигнализации будут приходить чередуясь импульсы высокого и низкого уровня, то последние будут обнулять содержимое первого счетчика 11.1. В результате на первом управляющем выходе ничего не появится и первый светодиод 11.3 светиться не будет.

Если на второй управляющий вход блока сигнализации 11 поступит от формирователя управляющих сигналов 10 импульс высокого уровня, то загорается третий светодиод 11.11, что будет свидетельствовать о снижении энергии, передаваемой в ВОЛС, на интервале оценки параметров сигнала Т на недопустимую величину. Это будет расцениваться как приближение тревоги. Кроме этого, второй счетчик 11.5 изменит свое внутреннее состояние на единицу. Если же на второй управляющий вход будут приходить последовательно друг за другом S импульсов высокого уровня, причем число S определяется коэффициентом счета второго счетчика 11.5 блока сигнализации 11, то на выходе счетчика 11.5 появится импульс высокого уровня, который поступит на первый вход объединителя 11.6. В результате чего на его выходе появится импульс высокого уровня. Такой же результат на выходе объединителя 11.6 получится, если на третий управляющий вход блока сигнализации поступит управляющий импульс высокого уровня от формирователя управляющих сигналов 10. В том и в другом случае, импульс высокого уровня с выхода объединителя 11.6 поступит на первый вход второго сумматора по модулю два 11.7 и на его выходе появится импульс высокого уровня. В результате создается электрическая цепь протекания тока через второй светодиод 11.8. При протекании тока через второй светодиод 11.8, он начинает светиться, что свидетельствует о медленном приближении тревоги (результат снижения световой энергии, передаваемой в ВОЛС, на S-интервалах оценки параметров принимаемого сигнала Т). Кроме этого, импульс высокого уровня с выхода объединителя 11.6 поступает на второй управляющий выход блока сигнализации 11, к которому может быть подключен блок блокирования передачи совместно (или нет) с блоком проверки и испытания ВОЛС.

Если на второй управляющий вход блока сигнализации 11 будут приходить чередуясь с импульсами высокого уровня и импульсы низкого уровня, то последние будут обнулять содержимое второго счетчика 11.5, т.к. его информационный вход запараллелен со сбрасывающим. Поэтому на втором управляющем выходе ничего не появится и второй светодиод 11.8 светиться не будет.

Устройство (вариант II) работает следующим образом. Энергия оптического сигнала из оптического волокна (OB) волоконно-оптической линии связи (ВОЛС) поступает на информационный вход устройства контроля энергии, передаваемой по ВОЛС, который соединен с входом фотодетектора 1. С выхода фотодетектора 1 продетектированный сигнал в виде импульсов электрического тока поступает на усилитель 2, где усиливается до необходимого уровня. С выхода усилителя 2 усиленные по амплитуде импульсы поступают на информационные входы выделителя тактовой частоты 3, аналого-цифрового преобразователя 4 и блока принятия решения 8.

В выделителе тактовой частоты 3 из принимаемой последовательности электрических импульсов выделяется тактовая частота. Фаза импульсов тактовой частоты на длительности периода будет определяться формой принимаемых импульсов. Поэтому тактовые импульсы с выхода выделителя 3 поступает на тактовый вход аналого-цифрового преобразователя 4 и блока принятия решения 8 в момент наибольшего значения мгновенной амплитуды принятого импульса. Это наибольшее значение мгновенной амплитуды принятого импульса будет преобразовываться в АЦП 4 из аналогового значения в цифровой код. С выхода АЦП 4 цифровой код мгновенного значения наибольшей амплитуды принятого импульса xt поступает на второй информационный вход блока вычета 5.

В блоке принятия решения 8 в моменты стробирования происходит сравнивание значения мгновенной амплитуды принятого электрического импульса с пороговым уровнем блока принятия решения 8. Если мгновенная амплитуда принятого импульса больше порогового уровня, принимается решение, что принят импульс высокого уровня. Поэтому на выходе блока принятия решения 8 в данном случае будет присутствовать логическая единица. Если мгновенная амплитуда принятого импульса меньше порогового уровня, принимается решение, что принят импульс высокого уровня и на выходе блока принятия решения 8 появляется логический ноль. Импульс с выхода блока принятия решения 8 поступает на информационный вход формирователя информационных сигналов 12 и на тактовый вход блока вычета 5.

В формирователе информационных сигналов 12 импульсы восстанавливаются (нормируются) по амплитуде, форме и временному положению и поступают на выход, который является информационным выходом заявляемого устройства.

На первый информационный вход блока вычета 5 поступает цифровой код эталонного среднего значения амплитуды принимаемых импульсов высокого уровня mЭТ со второго информационного выхода блока памяти 9. Эта величина, известная после доэксплуатационных измерений характеристик ВОЛС, записывается в перепрограммируемое запоминающее устройство (ППЗУ) блока памяти 9. С поступлением на тактовый вход блока вычета 5 логической единицы, что свидетельствует о приеме импульса высокого уровня, в нем разрешается операция вычитания. Поэтому из значения цифрового кода эталонного среднего значения амплитуды принимаемых импульсов высокого уровня вычитается значение цифрового кода импульсов только высокого уровня:

Δt= mэт-xlt. (2.1)

Результат вычисленной разности оформляется знаковым разрядом, который поступает на знаковый выход блока вычета 5, и собственно результатом разности, поступающим на информационный выход блока вычета 5. Уровень знакового импульса зависит от знака вычисленной разности. Если результат (2.1) отрицателен, т.е. xlt > mЭТ, то знаковый бит обозначается импульсом низкого уровня. Знаковый импульс поступает на информационный и сбрасывающий входы счетчика 6 и на тактовый вход сумматора 7. Приход знакового импульса низкого уровня изменяет внутреннее состояние счетчика 6, т.е. он подсчитывает логические нули (является счетчиком нулей). В случае прихода некоторого числа Y подряд следующих импульсов низкого уровня (Y определяется коэффициентом счета Kсч счетчика 6), на его выходе появляется импульс высокого уровня, который поступает на сбрасывающий вход сумматора 7. Таким образом, если в течение некоторого промежутка времени tсч = f(Kсч) значение оптической энергии, передаваемой в ВОЛС, больше допустимой (т.е. ВОЛС функционирует без потерь энергии), сумматор 7 будет периодически обнуляться.

Если на счетчик 6 поступает последовательность, содержащая знаковые импульсы обоих уровней, то импульсы высокого уровня будут сбрасывать содержимое счетчика 6 и возвращать его в исходное состояние. Именно знаковые импульсы высокого уровня будут тактировать работу сумматора 7 и блока взвешивания и управления 10.

На первый информационный вход сумматора 7 поступает цифровой код значения вычисленной разности (2.1) Δt с информационного выхода блока вычета 5. Сумматор 7 предназначен для накапливания значения суммы относительных значений мгновенных амплитуд импульсов, уровень которых оказался меньше эталонного xlt < mЭТ, т.е.  Накопление происходит благодаря сложению значения цифрового кода Δt в данный момент времени, поступившего на первый информационный вход сумматора 7, и значения цифрового кода суммы

Накопление происходит благодаря сложению значения цифрового кода Δt в данный момент времени, поступившего на первый информационный вход сумматора 7, и значения цифрового кода суммы  , накопленной за предыдущее время в нем же. Цифровой код

, накопленной за предыдущее время в нем же. Цифровой код  поступает с выхода сумматора 7 на его второй информационный вход. Сумматор 7, как уже было отмечено, работает только во время снижения значения оптической энергии, передаваемой в ВОЛС, т.е. при тактировании его высокоуровневыми знаковыми импульсами.

поступает с выхода сумматора 7 на его второй информационный вход. Сумматор 7, как уже было отмечено, работает только во время снижения значения оптической энергии, передаваемой в ВОЛС, т.е. при тактировании его высокоуровневыми знаковыми импульсами.

В условиях понижения оптической энергии, передаваемой по ВОЛС (по различным причинам), энергия оптического сигнала уменьшается на недопустимую величину. При этом на вход заявляемого устройства будут поступать импульсы, мгновенное значение амплитуды которых меньше эталонного среднего значения амплитуды импульсов высокого уровня: xt < mЭТ. В данном случае на знаковом выходе блока вычета 5 появляется высокоуровневый сигнал логической единицы - "1". Он сбрасывает состояние счетчика нулей 6 в исходное и осуществляет тактирование сумматора 7. Тем самым в сумматоре 7 начинается процесс суммирования относительного значения мгновенной амплитуды принятого импульса Δ Таким образом, сумматор 7 будет основным информативным блоком, отслеживающим значение оптической энергии, передаваемой в ВОЛС. Причем, сумматор 7 будет накапливать информацию независимо от причин, вызвавших недопустимое понижение оптической энергии в ВОЛС, будь то кратковременные или долговременные флуктуации.

Таким образом, сумматор 7 будет основным информативным блоком, отслеживающим значение оптической энергии, передаваемой в ВОЛС. Причем, сумматор 7 будет накапливать информацию независимо от причин, вызвавших недопустимое понижение оптической энергии в ВОЛС, будь то кратковременные или долговременные флуктуации.