Изобретение относится к электросвязи и может быть использовано для контроля качества дискретных каналов связи, подверженных воздействию помех, приводящих к появлению ошибок группового характера, с изменяющейся степенью группирования.

Заявленное техническое решение расширяет арсенал средств данного назначения.

Известно устройство контроля качества дискретного канала связи, подверженного воздействию помех, приводящих к возникновению ошибок группового характера (патент SU 1702533 А1, МПК6 Н 04 В 3/46 от 30.12.91 г.), содержащее блок выделения смежных ошибок, блок деления, дешифратор, блок вычисления оценки вероятности правильного приема, блок умножения, блок суммирования, триггер, обеспечивающее оперативную оценку вероятности правильного приема кодовых блоков одинарной и двойной длины и идентификацию на этой основе состояния канала.

Недостатком данного аналога является относительная невысокая точность (точность - степень приближения истинного значения рассматриваемого параметра к его теоретически номинальному значению. Политехнический словарь. Гл. ред. акад. А.Ю. Ишлинский. 2-е изд. - М.: Советская энциклопедия, 1980, с. 534) оценки качества контролируемого канала связи.

Известно также устройство контроля дискретных каналов (патент SU 1704284 А1, МПК6 Н 04 В 3/46 от 07.01.92 г.), содержащее анализатор, два счетчика, блок сравнения, делитель, блок задания чисел, реверсивный счетчик, дешифратор, два регистра и блок сравнения.

Недостатком данного устройства является относительно низкая точность оценки качества контролируемого дискретного канала в условиях воздействия помех, приводящих к изменению степени группирования ошибок.

Наиболее близким к заявленному устройству по принципу действия и технической реализации является устройство для контроля качества канала связи по авторскому свидетельству SU 1830186 A3, МПК6 Н 04 В 3/46, заявлено 11.11.90 г., опубликовано 23.06.93 г. Известное устройство состоит из последовательно соединенных делителя тактовой частоты, первого регистра сдвига, тактовый вход которого подсоединен к тактовым входам второго, третьего, четвертого регистров сдвига и тактовому входу первого элемента "И", первого реверсивного счетчика, делителя и компаратора (в описании прототипа элемент, выполняющий функции компаратора, назван дешифратором), выходы которого являются выходами устройства для контроля качества канала связи, входами сигналов "Тактовая частота" и "Ошибка" которого являются соответственно вход делителя тактовой частоты и суммирующий вход первого реверсивного счетчика, подключенного к информационным входам первого регистра сдвига, элемента "НЕ", выход которого подключен к установочному входу триггера и информационному входу первого элемента "И", инверсный выход которого подсоединен к входу сброса триггера, выход которого подключен к информационным входам второго регистра сдвига и второго реверсивного счетчика, второй вход которого подсоединен к выходу второго регистра сдвига, а выход к первому входу вычитателя, и четвертого регистра сдвига, первый и третий выходы которого подсоединены к входу второго элемента "И", второй вход которого подсоединен к инверсному выходу четвертого регистра сдвига, а выход к информационным входам третьего регистра сдвига и третьего реверсивного счетчика, второй вход которого подсоединен к выходу третьего регистра сдвига, а выход к второму входу вычитателя, выход которого подключен к второму входу делителя.

При таком построении устройства, в сравнении с раннее рассмотренными аналогами, достигается некоторое повышение точности оценки качества контролируемого канала связи с изменяющейся степенью группирования ошибок, за счет повышения точности определения средней длины пакета ошибок.

Однако устройство-прототип все же не обеспечивает требуемую точность оценки качества канала связи, необходимую в современных системах передачи. Это объясняется тем, что качество канала идентифицируется на основании, только последней оценки средней длины пакета ошибок, без учета предыдущих оценок состояния канала связи, при этом, в случае воздействия внутрисистемных кратковременных помех, непосредственно не влияющих на качество канала связи, возможно неверное оценивание качества канала связи. Кроме того, кратковременно флуктуирующие помехи будут вызывать высокочастотный колебательный процесс индикации состояния канала связи, что делает практически невозможным использование этой информации в контуре управления его качеством.

Целью изобретения является разработка устройства для контроля качества канала связи, подверженного воздействию помех, обеспечивающего более высокую точность оценки его состояния, а также расширение функциональных возможностей устройства, а именно формирование на его выходе сигналов, пригодных как для контроля состояния канала связи, так и для управления его качеством.

Поставленная цель достигается тем, что в известном устройстве для контроля качества канала связи, содержащем делитель тактовой частоты, вход которого является входом "Тактовая частота" устройства, а выход подключен к тактовым входам первого, второго, третьего, четвертого регистров сдвига и второго элемента "И", суммирующий вход первого реверсивного счетчика подсоединен к информационным входам первого и второго регистров сдвига, элемента "НЕ" и являются входом "Ошибка" устройства, выход элемента "НЕ" подключен к установочному входу триггера и информационному входу второго элемента "И", инверсный выход которого подключен к входу сброса триггера, выход которого подключен к информационному входу третьего регистра сдвига и суммирующему входу второго реверсивного счетчика, первый и третий выходы первого регистра сдвига подключены соответственно к первому и третьему входам первого элемента "И", второй вход которого подключен к второму инверсному выходу первого регистра, а выход подключен к суммирующему входу третьего реверсивного счетчика и информационному входу четвертого регистра сдвига, выход второго регистра сдвига подключен к вычитающему входу первого реверсивного счетчика, выход которого подключен к первому входу делителя, второй вход которого подключен к выходу вычитателя, выход третьего регистра сдвига подключен к вычитающему входу второго реверсивного счетчика, выход которого подключен к первому входу вычитателя, второй вход которого подключен выходу третьего реверсивного счетчика, вычитающий вход которого подключен к выходу четвертого регистра сдвига, и компаратор, первый, второй, третий выходы которого являются соответственно выходами "Высокая", "Средняя", "Низкая" устройства, дополнительно введены формирователь множителей, вход "Код множителя" которого является первыми установочным входом устройства, а его первый и второй устанавливающие выходы подключены к установочным входам соответственно первого и второго перемножителя, информационные входы которых подключены соответственно к входу и к выходу элемента задержки, информационный вход которого подключен к выходу делителя, а его тактовый вход подключен к выходу делителя тактовой частоты, выходы первого и второго перемножителя подключены соответственно к первому и к второму входам сумматора, выход которого подключен к входу компаратора, причем компаратор снабжен дополнительным входом "Установка порога", являющимся вторым установочным входом устройства.

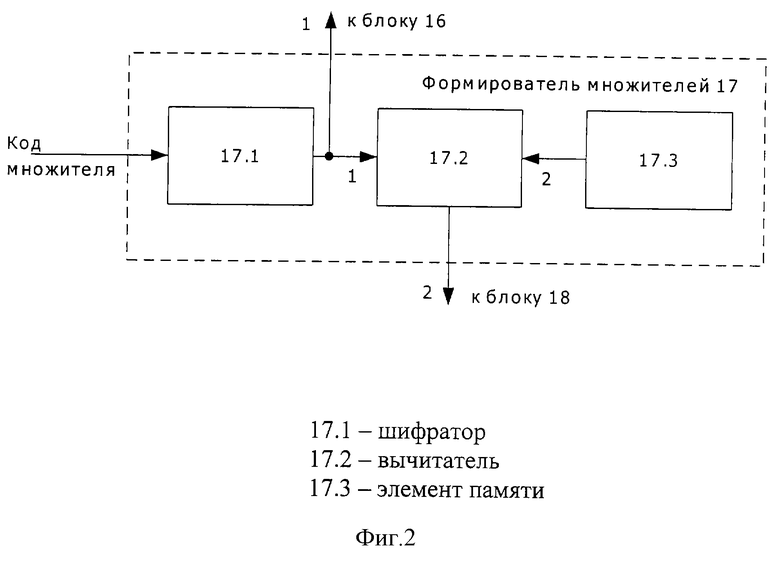

Формирователь множителей состоит из шифратора, вычитателя и элемента памяти, выход которого подключен к второму входу вычитателя, выход которого является вторым выходом формирователя, а его первый вход подключен к выходу шифратора и является первым выходом формирователя, вход "Код множителя" шифратора является первыми установочным входом устройства.

Благодаря новой совокупности существенных признаков, за счет введения вышеуказанных элементов и связей между ними, осуществляется процедура экспоненциального сглаживания оценочного значения средней длины пакета ошибок.

Этим достигается повышение точности оценки состояния канала связи в условиях воздействия помех, а также сглаживание частоты переключении выходного информационного сигнала между выходами устройства и, как следствие, уменьшение неоправданных временных потерь на перестройку аппаратуры. Таким образом, заявляемое устройство может применяться не только для контроля и индикации состояния канала связи, но и для формирования сигналов управления его качеством, что расширяет его функциональное назначение.

Проведенный анализ уровня техники позволил установить, что аналоги, характеризующиеся совокупностью признаков, тождественным всем признакам заявленного технического решения, отсутствуют, что указывает на соответствие заявленного устройства условию патентоспособности "новизна". Результаты поиска известных решений в данной и смежных областях техники с целью выявления признаков, совпадающих с отличительными от прототипа признаками заявленного объекта, показали, что они не следуют явным образом из уровня техники. Из уровня техники также не выявлена известность влияния предусматриваемых существенными признаками заявленного изобретения преобразований на достижение указанного технического результата. Следовательно, заявленное изобретение соответствует условию патентоспособности "изобретательский уровень".

Заявленное устройство поясняется чертежами, на которых показаны:

на фиг.1 - функциональная схема устройства;

на фиг.2 - функциональная схема формирователя множителей.

Устройство для контроля качества канала связи, показанное на фиг.1, состоит из делителя тактовой частоты 1, вход которого является входом "Тактовая частота" устройства, а выход подключен к тактовым входам первого, второго, третьего, четвертого регистров сдвига 3, 7, 9, 13 и второго элемента "И" 4. Суммирующий вход первого реверсивного счетчика 8 подсоединен к информационным входам первого и второго регистров сдвига 3, 7, элемента "НЕ" 5, и являются входом "Ошибка" устройства. Выход элемента "НЕ" 5 подключен к установочному входу триггера 6 и информационному входу второго элемента "И" 4. Инверсный выход второго элемента "И" 4 подключен к входу сброса триггера 6, выход которого подключен к информационному входу третьего регистра сдвига 9 и суммирующему входу второго реверсивного счетчика 10. Первый и третий выходы первого регистра сдвига 3 подключены соответственно к первому и третьему входам первого элемента "И" 2. Второй вход первого элемента "И" 2 подключен к второму инверсному выходу первого регистра сдвига 3, а выход подключен к информационному входу третьего реверсивного счетчика 12 и суммирующему входу четвертого регистра сдвига 13. Выход второго регистра сдвига 7 подключен к вычитающему входу первого реверсивного счетчика 8. Выход первого реверсивного счетчика 8 подключен к первому входу делителя 14, второй вход которого подключен к выходу вычитателя 11. Выход третьего регистра сдвига 9 подключен к вычитающему входу второго реверсивного счетчика 10, выход которого подключен к первому входу вычитателя 11, второй вход которого подключен выходу третьего реверсивного счетчика 8. Вычитающий вход третьего реверсивного счетчика 8 подключен к выходу четвертого регистра сдвига 13. Первый, второй, третий выходы компаратора 20 являются соответственно выходами "Высокая", "Средняя", "Низкая" устройства, а его вход "Установка порога" является вторым установочным входом устройства. Первый и второй устанавливающие выходы формирователя множителей 17 подключены к установочным входам соответственно первого и второго перемножителя 16, 18, а его вход "Код множителя" является первым установочным входом устройства. Информационные входы первого и второго перемножителя 16, 18 подключены, соответственно, к информационному входу и к выходу элемента задержки 15, а выходы - к первому и второму входам сумматора 19. Информационный вход элемента задержки 15 подключен к выходу делителя 14, а его тактовый вход подключен к выходу делителя тактовой частоты 1. Выход сумматора 19 подключен к входу компаратора 20.

Формирователь множителей 17 состоит из шифратора 17.1, вычитателя 17.2 и элемента памяти 17.3. Выход элемента памяти 17.3 подключен к второму входу вычитателя 17.2. Выход вычитателя 17.2 является вторым выходом формирователя 17. Первый вход вычитателя 17.1 подключен к выходу шифратора 17.1 и является первым выходом формирователя 17. Вход "Код множителя" шифратора 17 является первыми установочным входом устройства.

Делитель тактовой частоты 1 предназначен для формирования тактирующих импульсов, синхронизирующих работу первого, второго, третьего, четвертого регистров сдвига 3, 7, 9, 13, элемента "НЕ" 5 и элемента задержки 15. Схема построения его известна и описана, например, в книге Цифровые интегральные микросхемы: Справ./ М.И.Богданович, И.Н.Грель, В.А.Прохоренко, В.А.Шалимо. - Мн.: Беларусь, 1991. - 493 с.: ил., с.139-142.

Первый регистр сдвига 3 служит для формирования на входе первого элемента "И" 2 сигнала вида "010", соответствующего ситуации, когда в статистической выборке фиксированного объема, записанной в этот регистр, имеет место комбинация "101". Устройство его известно и описано, например, в указанной выше книге М.И.Богданович и др. на с.174-227.

Второй регистр сдвига 7 предназначен для последовательной записи поступающих на информационный вход устройства признаков правильного и искаженного приема, формирования из них статистической выборки фиксированного объема, обновления ее в момент поступления на его тактирующий вход синхронизирующих импульсов. Устройство его известно и описано, например, в указанной выше книге М.И.Богданович и др. с.174-227.

Третий регистр сдвига 9 предназначен для последовательной записи поступающих на его информационный вход логических единиц, соответствующих группированию признаков искаженного приема, формирования из них статистической выборки фиксированного объема, обновления ее в момент поступления на тактирующий вход синхронизирующих импульсов. Устройство его известно и описано, например, в указанной выше книге М.И.Богданович и др. на с.174-227.

Четвертый регистр сдвига 13 предназначен для последовательной записи поступающих на его информационный вход логических единиц, соответствующих сочетаниям признаков приема вида "101", формирования из них статистической выборки фиксированного объема, обновления ее в момент поступления на его тактирующий вход синхронизирующих импульсов. Устройство его известно и описано, например, в указанной выше книге М.И.Богданович и др. на с.174-227.

Триггер 6, совместно с элементом "НЕ" 4 и вторым элементом "И", предназначен для формирования на информационных входах третьего регистра сдвига 9 и второго реверсивного счетчика 10 случайной последовательности логических единиц, соответствующих ситуации группирования признаков искаженного приема в канале связи. Устройство его известно и описано, например, в указанной выше книге М.И.Богданович и др. на с.91-104.

Первый реверсивный счетчик 8 предназначен для подсчета числа признаков искаженного приема, имеющих место в выборке, сформированной регистром сдвига 7. Устройство его известно и описано, например, в указанной выше книге М.И. Богданович и др. на с.150-157.

Второй реверсивный счетчик 10 предназначен для подсчета числа признаков группирования искаженных кодовых блоков приема, имеющих место в выборке, сформированной регистром сдвига 9. Устройство его известно и описано, например, в указанной выше книге М.И.Богданович и др. на с.150-157.

Третий реверсивный счетчик 12 предназначен для подсчета числа признаков вида "101", имеющих место в выборке, сформированной регистром сдвига 13. Устройство его известно и описано, например, в указанной выше книге М.И.Богданович и др. на с.150-157.

Первый перемножитель 16 предназначен для перемножения кодового слова средней длины пакета ошибок в предыдущей выборке, на кодовое слово множителя, поступающего с первого выхода формирователя множителей 17. Устройство его известно и описано, например, в указанной выше книге М.И.Богданович и др. на с.276.

Второй перемножитель 18 предназначен для перемножения кодового слова средней длины пакета ошибок в текущей выборке на кодовое слово множителя, поступающего с второго выхода формирователя множителей 17. Устройство его известно и описано, например, в указанной выше книге М.И.Богданович и др. на с.276.

Первый элемент "И" 2, совместно с первым регистром сдвига 3, предназначен для формирования случайной последовательности логических единиц, соответствующих появлению в выборке сочетаний признаков приема вида "101". Устройство его известно и описано, например, в книге Шило В.А. Полупроводниковые цифровые микросхемы: Справочник. - М.: Радио и связь, 1987, с.34-50.

Второй элемент "И" 4, совместно с элементом "НЕ" 5, предназначен для формирования случайной последовательности логических нулей на входе "Сброс" триггера 6. Устройство его известно и описано, например, в указанной выше книге Шило В.А. на с.34-50.

Компаратор 20 предназначен для сравнения кодового слова, поступающего с выхода сумматора 19, с заранее установленным кодовым словом порогового значения средней длины пакета ошибок. Устройство его известно и описано, например, в указанной выше книге Шило В.А. на с.270-273.

Элемент "НЕ" 5 предназначен для инвертирования последовательности признаков приема, поступающих на вход триггера 6 и второго элемента "И" 4. Устройство его известно и описано, например, в книге Справочник по полупроводниковым диодам, транзисторам и интегральным схемам. / Под общ. ред. Н.Н. Гончарова. Изд. 4-е, перераб. и доп. - М.: Энергия, 1972, с.41-43.

Вычитатель 11 предназначен для формирования кода разности между числом группирований признаков искаженного приема и числом сочетаний вида "101" в одной и той же выборке. Устройство его известно и описано, например, в указанной выше книге Шило В.А. на с.159-162.

Делитель 14 предназначен для формирования кода средней длины пакета ошибок на текущем интервале наблюдения. Устройство его известно и описано, например, в указанной выше книге Шило В.А. на с.275-277.

Сумматор 19 предназначен для формирования кода суммы взвешенных оценок средней длины пакета ошибок на текущем и предыдущем интервалах наблюдения. Устройство его известно и описано, например, в указанной выше книге Шило В. А. на с.158-159.

Элемент задержки 15 предназначен для оперативной записи кодового слова средней длины пакета ошибок в текущей выборке, и считывания кодового слова средней длины пакета ошибок в предыдущей выборке. Устройство его известно и описано, например, в указанной выше книге Шило В.А. на с.164-165.

Формирователь множителей 17 предназначен для формирования кодов множителей, поступающих соответственно на установочные входы первого и второго перемножителей 16, 18. Он может быть реализован в соответствии со схемой, представленной на фиг.2.

Шифратор 17.1 предназначен для преобразования входного сигнала "Код множителя" в выходной двоичный код множителя. Устройство его известно и описано, например, в указанной выше книге Шило В.А. на с.139-142.

Вычитатель 17.2 предназначен для формирования кода множителя на входе второго перемножителя 18. Устройство его известно и описано, например, в указанной выше книге Шило В.А. на с.159-162.

Элемент памяти 17.3 предназначен для постоянного хранения двоичного кодового слова, соответствующего десятичному числу 1 с необходимым фиксированным числом разрядов после запятой. Устройство его известно и описано, например, в указанной выше книге Шило В.А. на с.171-174.

Заявленное устройство работает следующим образом.

В исходном состоянии реверсивные счетчики 8, 10, 12 и триггер 6 обнулены. Процесс контроля состояния канала связи сводится к вычислению оценки средней длины пакета ошибок, получаемой на выходе делителя 14, экспоненциальному сглаживанию результатов текущего и предыдущего оценивания на выходе сумматора 19 и сравнению уточненной оценки с предварительно установленными пороговыми значениями в компараторе 20.

На вход "Ошибка" устройства поступают признаки искаженного и правильного приема кодовых блоков в виде последовательности логических единиц и нулей, которые подаются на суммирующий вход первого реверсивного счетчика 8 и на информационный вход регистра сдвига 7, разрядность которого выбирается равной длине контролируемой выборки. Одновременно на тактовый вход регистра сдвига 7 поступают импульсы тактовой частоты, период повторения которых равен периоду следования признаков приема кодовых блоков. С помощью этих импульсов осуществляется запись и сдвиг поступающих в регистр сдвига 7 признаков приема. По истечении числа тактов, равного длине выборки после начала работы, в регистре сдвига записывается последовательность (статистика) ошибок на текущем i-ом интервале наблюдения, а в реверсивном счетчике 8 фиксируется значение кода Si, соответствующее числу признаков искаженного приема (числу логических единиц), имевших место i-ой выборке.

Одновременно, с помощью элемента "НЕ" 5, второго элемента "И" 4 и триггера 6 из входной последовательности признаков приема формируется случайная последовательность признаков, элементы которой принимают значение логической единицы в случае искаженного приема при условии неискаженного предыдущего приема и логического нуля - в противном случае. Эта последовательность поступает на суммирующий вход второго реверсивного счетчика 10 и информационный вход второго регистра сдвига 9, на тактовый вход которого с выхода делителя тактовой частоты 1 подаются тактовые импульсы, следующие синхронно и синфазно с элементами случайной последовательности признаков приема. Разрядность второго регистра сдвига 9 при этом должна быть такой же, как у второго регистра сдвига 7. По истечении i-го интервала наблюдения во втором реверсивном счетчике 10 устанавливается значение кода Di, соответствующее числу серий искаженного приема (серий логических единиц), имевших место в i-ой выборке, а в третьем регистре сдвига 9 запишется статистика серий искаженного приема на этом же интервале наблюдения.

Параллельно с рассматриваемым процессом из входной последовательности признаков приема с помощью первого регистра сдвига 3 и первого элемента "И" 2 формируется случайная последовательность признаков, элементы которой принимают значение логической единицы, когда в первом регистре сдвига 3 устанавливается последовательность признаков приема вида "101". В остальных ситуациях случаях формируется логический нуль. Эта последовательность поступает на суммирующий вход третьего реверсивного счетчика 12, который подсчитывает число логических единиц в последовательности признаков приема в i-ой выборке, и вводится через информационный вход в четвертый регистр сдвига 13 с помощью тактовых импульсов, поступающих с выхода делителя тактовой частоты 1. На последнем такте i-го интервала наблюдения в третьем реверсивном счетчике 12 устанавливается значение кода Сi числа ситуаций вида "101", а в четвертом регистре сдвига записывается их последовательность (статистика).

В результате последовательно проводимых во втором регистре сдвига 7 продвижений признаков приема в нем происходит обновление контролируемой выборки, а в первом реверсивном счетчике 8, за счет поступления на его суммирующий и вычитающий входы признаков приема, образуется код, соответствующий числу искаженно принятых блоков на текущем интервале наблюдения (в текущей выборке).

Аналогичным образом формируются коды во втором и в третьем реверсных счетчиках 10 и 12.

Формирование последовательности на входе третьего регистра сдвига 9 из принимаемой последовательности признаков приема осуществляется следующим образом. При отсутствии искаженных кодовых блоков на входе элемента "НЕ" 5 действует логический нуль, а на выходе - логическая единица, открывающая элемент "И" 4. При этом на инверсном выходе элемента "И" 4 в момент поступления тактовых импульсов с выхода делителя тактовой частоты образуется логический нуль, поступающий на сбрасывающий вход триггера 6 и устанавливающий на его выходе логический нуль. С появлением на входе признака искаженного кодового блока (логической единицы) на входе элемента "НЕ" 5 на его выходе формируется логический нуль, который поступает на устанавливающий вход триггера 6, в результате чего на его выходе формируется логический нуль, одновременно поступающий на вход второго элемента "И" 4 логический нуль запирает его, тем самым препятствуя осуществить сброс триггера 6 в нулевое состояние в момент поступления на тактовый вход второго элемента "И" 4 тактовых импульсов. Сигнал логической единицы с выхода триггера 6 поступает на суммирующий вход второго реверсивного счетчика 10, который подсчитывает число переключении триггера 6 из состояния логического нуля в состояние логической единицы, соответствующее числу серий признаков искаженного приема (серий логических единиц) в контролируемой входной последовательности признаков приема. В случае искаженного последующего приема триггер 6 сохраняет свое состояние, однако добавление логической единицы во второй реверсивный счетчик 10 не происходит, так как он срабатывает только при переходе триггера 6 из состояния логического нуля в состояние логической единицы. Таким образом, если предыдущий кодовый блок не искаженный, то логический нуль с выхода элемента "НЕ" 5 открывает второй элемент "И" 4, а на его выходе в момент действия импульсов тактовой частоты с выхода делителя тактовой частоты 1 образуется логический нуль, сбрасывающий триггер 6 в нулевое состояние.

В результате осуществления рассмотренных операций на выходах первого, второго, третьего реверсивных счетчиков 8, 10, 12 формируются коды соответственно Si, Di, Сi, которые используются на каждом i-ом такте оценки для расчета среднего числа подряд искаженных блоков, определяемого как

Вычитание из кода Di кода Сi, снимаемых соответственно с выходов второго и третьего реверсивных счетчиков 10 и 12, осуществляется в вычитателе 11, при их поступлении соответственно на его первый и второй вход. В результате этого на его выходе вычитателя 11 формируется код разности Di-Ci, поступающий на второй вход делителя 14. На первый вход делителя 14 поступает код Si, а на его выходе формируется код  , соответствующий среднему числу подряд искаженных блоков

, соответствующий среднему числу подряд искаженных блоков  , содержащихся в i-ой выборке. С выхода делителя 1 кодовое слово

, содержащихся в i-ой выборке. С выхода делителя 1 кодовое слово  поступает на вход элемента задержки 15, где происходит его запись и запоминание до следующего (i+1)-го момента оценивания, и на информационный вход второго перемножителя 18. Под воздействием тактирующих импульсов, поступающих выхода с делителя тактовой частоты 1 на тактовый вход элемента задержки 15, на информационный вход которого поступает код

поступает на вход элемента задержки 15, где происходит его запись и запоминание до следующего (i+1)-го момента оценивания, и на информационный вход второго перемножителя 18. Под воздействием тактирующих импульсов, поступающих выхода с делителя тактовой частоты 1 на тактовый вход элемента задержки 15, на информационный вход которого поступает код  , на его выходе появляется кодовое слово, записанное в предыдущий момент времени. На первом и втором выходах формирователя множителей формируются соответственно кодовые слова (1-a) и a, где a=0,1; 0,2;...0,9, в виде параллельного двоичного кода. Формирование (1-a) и a поясняется функциональной схемой, представленной на фиг.2. В элементе памяти 17.3 хранится значение десятичного числа 1, представленного в виде двоичного кодового слова с необходимой фиксированной разрядностью дробной части, которое постоянно подается на вход вычитателя 17.2. На вход шифратора 17.1 поступает кодовая комбинация одного из чисел a=0,1; 0,2;...0,9, в результате чего на его на его выходе формируется соответствующий двоичный код множителя a. Код множителя a поступает на управляемый вход второго перемножителя 18 и первый вход вычитателя 17.2. На выходе вычитателя 17.2 образуется код множителя (1-a), который поступает на управляемый вход первого перемножителя 16. На выходе первого и второго перемножителей 16 и 18 соответственно формируются коды произведений

, на его выходе появляется кодовое слово, записанное в предыдущий момент времени. На первом и втором выходах формирователя множителей формируются соответственно кодовые слова (1-a) и a, где a=0,1; 0,2;...0,9, в виде параллельного двоичного кода. Формирование (1-a) и a поясняется функциональной схемой, представленной на фиг.2. В элементе памяти 17.3 хранится значение десятичного числа 1, представленного в виде двоичного кодового слова с необходимой фиксированной разрядностью дробной части, которое постоянно подается на вход вычитателя 17.2. На вход шифратора 17.1 поступает кодовая комбинация одного из чисел a=0,1; 0,2;...0,9, в результате чего на его на его выходе формируется соответствующий двоичный код множителя a. Код множителя a поступает на управляемый вход второго перемножителя 18 и первый вход вычитателя 17.2. На выходе вычитателя 17.2 образуется код множителя (1-a), который поступает на управляемый вход первого перемножителя 16. На выходе первого и второго перемножителей 16 и 18 соответственно формируются коды произведений  .

.

Полученные кодовые комбинации поступают соответственно на первый и второй входы сумматора 19, в результате чего на его выходе образуется закодированное экспоненциально сглаженное значение среднего числа подряд искаженных битов  , поступающее затем на вход компаратора, где осуществляется сравнивание полученного значения с некоторыми заданными заранее пороговыми значениями, соответствующими высокой, средней и низкой степени группирования признаков искаженного приема.

, поступающее затем на вход компаратора, где осуществляется сравнивание полученного значения с некоторыми заданными заранее пороговыми значениями, соответствующими высокой, средней и низкой степени группирования признаков искаженного приема.

Таким образом, достигается повышение точности оценки качества канала связи, в условиях воздействия помех и сокращение времени перестройки аппаратуры, за счет сглаживания частоты переключений выходного информационного сигнала устройства, что обуславливает возможность использования его в контуре управления качеством контролируемого канала связи.

Изобретение относится к электросвязи и может быть использовано для контроля состояния дискретных каналов связи, подверженных воздействию помех, приводящих к появлению ошибок группового характера, с изменяющейся степенью группирования. Технический результат заключается в расширении функциональных возможностей устройства, а именно в формировании на его выходе сигналов, пригодных как для контроля состояния канала связи, так и для управления его качеством. Устройство состоит из делителя тактовой частоты, первого и второго элементов И, первого, второго, третьего и четвертого регистров сдвига, элементов НЕ, триггера, первого, второго и третьего реверсивных счетчиков, вычитателя, делителя. В устройство также введены элемент задержки, первый и второй перемножители, формирователь множителей, сумматор и компаратор, благодаря которым осуществляется процедура экспоненциального сглаживания оценочного значения средней длины пакета ошибок, в результате которой достигается повышение точности оценки состояния канала связи в условиях воздействия помех, а также сглаживание частоты переключений выходного информационного сигнала между выходами устройства и уменьшение неоправданных временных потерь на перестройку аппаратуры. 1 з.п. ф-лы, 2 ил.

| Устройство для контроля качества канала связи | 1990 |

|

SU1830186A3 |

| Устройство контроля дискретных каналов | 1990 |

|

SU1704284A1 |

| УСТРОЙСТВО КОНТРОЛЯ ВОСПРИИМЧИВОСТИ РАДИОПРИЕМНИКА К ПОМЕХАМ | 1991 |

|

RU2032989C1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ОЦЕНКИ КАЧЕСТВА КАНАЛА В ПРИЕМНИКЕ | 1993 |

|

RU2138909C1 |

| Устройство для контроля качества дискретного канала связи | 1990 |

|

SU1702533A1 |

Авторы

Даты

2003-11-20—Публикация

2002-04-29—Подача