Предлагаемые технические решения объединены единым изобретательским замыслом и относятся к области электросвязи, а именно к технике сжатия дискретных сообщений для их передачи и хранения, таких как преобразованные к цифровому виду речевые, звуковые, телевизионные, факсимильные и т.п. сообщения.

Заявляемые изобретения могут быть использованы для уменьшения времени передачи кодированной последовательности двоичных символов по каналу связи или для уменьшения требуемого объема устройств хранения кодированной последовательности двоичных символов.

Известен способ сжатия кодируемой последовательности из символов упорядоченного m-ичного алфавита в кодированную последовательность двоичных символов, описанный, например, в книге: Р. Фано. "Передача информации. Статистическая теория связи". - М.: Мир, 1965, стр. 94-101. Он заключается в записи кодируемых последовательностей, состоящих из символов упорядоченного m-ичного алфавита, в порядке убывания их вероятностей, последовательного объединения кодируемых последовательностей, начиная с менее вероятных, в два подмножества, имеющие приблизительно одинаковые суммы вероятностей входящих в них кодируемых последовательностей. Данным подмножествам соответствуют нулевые и единичные символы кодированных последовательностей двоичных символов. Последовательное объединение кодируемых последовательностей в два подмножества выполняется до тех пор, пока каждой из кодируемых последовательностей не будет соответствовать уникальная кодированная последовательность двоичных символов,

Известен также способ сжатия кодируемой последовательности из символов упорядоченного m-ичного алфавита в кодированную последовательность двоичных символов описанный, например, в книге: Р.Е. Кричевский. "Сжатие и поиск информации". - М.: Радио и связь, 1988, стр. 5. Он заключается в записи кодируемых последовательностей, состоящих из символов упорядоченного m-ичного алфавита, в порядке убывания их вероятностей и назначении более вероятным кодируемым последовательностям более коротких кодированных последовательностей двоичных символов.

Недостатком известных способов сжатия кодируемой последовательности из символов упорядоченного m-ичного алфавита в кодированную последовательность двоичных символов является большое время передачи кодированной последовательности двоичных символов по каналу связи или большой требуемый объем устройств хранения кодированной последовательности. Это обусловлено тем, что известные способы не способны сжимать кодируемую последовательность, имеющую вероятность P ее появления, в кодированную последовательность двоичных символов длины L бит менее чем значение P logP, что описано, например, в книге: Р. Е. Кричевский. "Сжатие и поиск информации". - М.: Радио и связь, 1988, стр.6.

Известные устройства сжатия кодируемой последовательности из символов упорядоченного m-ичного алфавита в кодированную последовательность двоичных символов описаны, например, в книге: О. И. Лагутенко. "Модемы. Справочник пользователя". - С-Пб.: Издательство "Лань", 1997, стр. 218-226. Данные устройства включают блоки подсчета частости появления символов упорядоченного m-ичного алфавита в кодируемой последовательности и блоки кодирования символов упорядоченного m-ичного алфавита в двоичные символы. Информационные входы блоков кодирования символов упорядоченного m-ичного алфавита в двоичные символы соединены с информационными входами блоков подсчета частости появления символов упорядоченного m-ичного алфавита в кодируемой последовательности и являются входами данных устройств. Выходы блоков подсчета частости появления символов упорядоченного m-ичного алфавита в кодируемой последовательности соединены с управляющими входами блоков кодирования символов упорядоченного m-ичного алфавита в двоичные символы. Работа данных устройств заключается в последовательном отображении символов упорядоченного m-ичного алфавита кодируемой последовательности в кодированную последовательность двоичных символов по правилу, учитывающему вероятности появления символов упорядоченного m-ичного алфавита, подсчитываемыми блоками подсчета частости появления символов упорядоченного m-ичного алфавита в кодируемой последовательности.

Недостатком известных устройств сжатия кодируемой последовательности из символов упорядоченного m-ичного алфавита в кодированную последовательность двоичных символов является большое время передачи кодированной последовательности двоичных символов по каналу связи или большой требуемый объем устройств хранения кодированной последовательности двоичных символов. Это обусловлено тем, что известные устройства не способны сжимать кодируемую последовательность, имеющую вероятность P ее появления, в кодированную последовательность двоичных символов длины L бит менее чем значение P logP, что описано, например, в книге: Р.Е. Кричевский. "Сжатие и поиск информации". - М.: Радио и связь, 1988, стр. 6.

Наиболее близким по своей технической сущности к заявленному способу сжатия кодируемой последовательности из символов упорядоченного m-ичного алфавита в кодированную последовательность двоичных символов является известный способ, описанный в патенте США N 4652856 МПК6 H 03 М 7/30 от 24.03.87. Способ-прототип сжатия кодируемой последовательности из символов упорядоченного m-ичного алфавита в кодированную последовательность двоичных символов заключается в том, что предварительно устанавливают двоичное значение нижней границы кодирования длиной 2w двоичных разрядов, где w ≥ 2, и двоичное значение кодового интервала длиной w двоичных разрядов. Двоичное значение нижней границы кодирования длиной 2w двоичных разрядов устанавливают, равным двоичному числу, состоящему из w нулевых двоичных разрядов в целой его части и из w нулевых двоичных разрядов в дробной его части и двоичное значение кодового интервала длиной w двоичных разрядов устанавливают, равным двоичному числу, состоящему из единичного значения в целой его части и w-1 нулевых двоичных разрядов в дробной его части.

Последовательно, начиная с первого и до последнего, считывают очередной символ кодируемой последовательности, состоящей из k символов, где k ≥ 2, упорядоченного m-ичного алфавита, где m ≥ 2, и идентифицируют его с i-ым, где i=1, 2,..., m, символом упорядоченного m-ичного алфавита.

Затем вычисляют статистические параметры очередного символа кодируемой последовательности, для чего в части кодируемой последовательности, предшествующей очередному символу кодируемой последовательности, определяют двоичное число ni его появлений, сумму Qj двоичных чисел появлений символов кодируемой последовательности, предшествующих очередному символу кодируемой последовательности в упорядоченном m-ичном алфавите, сумму Qm двоичных чисел появлений символов кодируемой последовательности, предшествующих последнему символу в упорядоченном m-ичном алфавите и двоичное число N появлений всех символов упорядоченного m-ичного алфавита.

После чего нормализуют вычисленные статистические параметры N, ni, Qi и Qm очередного символа кодируемой последовательности выполнением следующей последовательности действий: устанавливают нормализованное значение  очередного символа кодируемой последовательности, равным значению последовательно сдвинутого в направлении старших разрядов двоичного числа N появлений всех символов упорядоченного m-ичного алфавита в части кодируемой последовательности, предшествующей очередному символу кодируемой последовательности, на такое число γ разрядов, при котором нормализованное значение

очередного символа кодируемой последовательности, равным значению последовательно сдвинутого в направлении старших разрядов двоичного числа N появлений всех символов упорядоченного m-ичного алфавита в части кодируемой последовательности, предшествующей очередному символу кодируемой последовательности, на такое число γ разрядов, при котором нормализованное значение  будет находиться в предопределенном диапазоне значений. Затем устанавливают нормализованное значение

будет находиться в предопределенном диапазоне значений. Затем устанавливают нормализованное значение  очередного символа кодируемой последовательности, равным значению последовательно сдвинутого в направлении старших разрядов на γ разрядов двоичного числа ni появлений очередного символа кодируемой последовательности в части кодируемой последовательности, предшествующей очередному символу кодируемой последовательности. После чего устанавливают нормализованное значение суммы

очередного символа кодируемой последовательности, равным значению последовательно сдвинутого в направлении старших разрядов на γ разрядов двоичного числа ni появлений очередного символа кодируемой последовательности в части кодируемой последовательности, предшествующей очередному символу кодируемой последовательности. После чего устанавливают нормализованное значение суммы  очередного символа кодируемой последовательности, равным значению последовательно сдвинутой в направлении старших разрядов на γ разрядов суммы Qi двоичных чисел появлений символов кодируемой последовательности, предшествующих очередному символу кодируемой последовательности в упорядоченном m-ичном алфавите, в части кодируемой последовательности, предшествующей очередному символу кодируемой последовательности. Далее устанавливают нормализованное значение суммы

очередного символа кодируемой последовательности, равным значению последовательно сдвинутой в направлении старших разрядов на γ разрядов суммы Qi двоичных чисел появлений символов кодируемой последовательности, предшествующих очередному символу кодируемой последовательности в упорядоченном m-ичном алфавите, в части кодируемой последовательности, предшествующей очередному символу кодируемой последовательности. Далее устанавливают нормализованное значение суммы  очередного символа кодируемой последовательности, равным значению последовательно сдвинутой в направлении старших разрядов на γ разрядов суммы Qj,m двоичных чисел появлений символов кодируемой последовательности, предшествующих последнему символу в упорядоченном m-ичном алфавите, в части кодируемой последовательности, предшествующей очередному символу кодируемой последовательности.

очередного символа кодируемой последовательности, равным значению последовательно сдвинутой в направлении старших разрядов на γ разрядов суммы Qj,m двоичных чисел появлений символов кодируемой последовательности, предшествующих последнему символу в упорядоченном m-ичном алфавите, в части кодируемой последовательности, предшествующей очередному символу кодируемой последовательности.

Нижний предел предопределенного диапазона значений устанавливают равным двоичному числу 0.11, а верхний предел предопределенного диапазона значений устанавливают меньшим двоичного числа 1.1.

Затем по нормализованным значениям статистических параметров  очередного символа кодируемой последовательности уточняют двоичные значения нижней границы кодирования и кодового интервала выполнением следующей последовательности действий.

очередного символа кодируемой последовательности уточняют двоичные значения нижней границы кодирования и кодового интервала выполнением следующей последовательности действий.

Если нормализованное значение суммы  очередного символа кодируемой последовательности меньше двоичного значения кодового интервала, то значение переменной β устанавливают в нулевое значение, иначе значение переменной β устанавливают в единичное значение. Далее, если очередной символ кодируемой последовательности не является последним символом упорядоченного m-ичного алфавита, то двоичное значение нижней границы кодирования заменяют суммой нормализованного значения суммы

очередного символа кодируемой последовательности меньше двоичного значения кодового интервала, то значение переменной β устанавливают в нулевое значение, иначе значение переменной β устанавливают в единичное значение. Далее, если очередной символ кодируемой последовательности не является последним символом упорядоченного m-ичного алфавита, то двоичное значение нижней границы кодирования заменяют суммой нормализованного значения суммы  очередного символа кодируемой последовательности и двоичного значения нижней границы кодирования и двоичное значение кодового интервала заменяют нормализованным значением

очередного символа кодируемой последовательности и двоичного значения нижней границы кодирования и двоичное значение кодового интервала заменяют нормализованным значением  очередного символа кодируемой последовательности. Иначе, если очередной символ кодируемой последовательности является последним символом упорядоченного m-ичного алфавита, то двоичное значение нижней границы кодирования заменяют суммой нормализованного значения суммы

очередного символа кодируемой последовательности. Иначе, если очередной символ кодируемой последовательности является последним символом упорядоченного m-ичного алфавита, то двоичное значение нижней границы кодирования заменяют суммой нормализованного значения суммы  очередного символа кодируемой последовательности и двоичного значения нижней границы кодирования и двоичное значение кодового интервала заменяют разностью между двоичным значением кодового интервала и нормализованным значением суммы

очередного символа кодируемой последовательности и двоичного значения нижней границы кодирования и двоичное значение кодового интервала заменяют разностью между двоичным значением кодового интервала и нормализованным значением суммы  очередного символа кодируемой последовательности. Далее, если переменная β имеет единичное значение, то двоичные значения нижней границы кодирования и кодового интервала сдвигают в направлении их старших разрядов на один разряд.

очередного символа кодируемой последовательности. Далее, если переменная β имеет единичное значение, то двоичные значения нижней границы кодирования и кодового интервала сдвигают в направлении их старших разрядов на один разряд.

Затем выделяют и считывают в кодированную последовательность неизменяемую часть двоичного значения нижней границы кодирования. Выделение неизменяемой части двоичного значения нижней границы кодирования выполняют определением числа старших разрядов двоичного значения нижней границы кодирования, при котором последовательно сдвинутое в направлении старших разрядов двоичное значение кодового интервала будет находиться в предопределенном диапазоне значений.

Далее стирают считанную часть двоичного значения нижней границы кодирования, сдвигают двоичное значение нижней границы кодирования в направлении старших разрядов на число разрядов его считанной части и дополняют таким же числом нулевых двоичных символов двоичное значение нижней границы кодирования со стороны младших разрядов. После уточнения двоичного значения нижней границы кодирования по нормализованным значениям статистических параметров  последнего символа кодируемой последовательности из позиций старших разрядов двоичного значения нижней границы кодирования последовательно считывают w двоичных символов в кодированную последовательность.

последнего символа кодируемой последовательности из позиций старших разрядов двоичного значения нижней границы кодирования последовательно считывают w двоичных символов в кодированную последовательность.

Благодаря перечисленной совокупности существенных признаков способ-прототип по сравнению с известными аналогами способен сжать кодируемую последовательность, имеющую вероятность P ее появления, в кодированную последовательность двоичных символов длины L бит сколь угодно близкой к значению P logP.

Недостатком способа-прототипа является большое время передачи кодированной последовательности двоичных символов по каналу связи или большой требуемый объем устройств хранения кодированной последовательности. Это обусловлено тем, что способ-прототип не способен сжимать кодируемую последовательность, имеющую вероятность P ее появления, в кодированную последовательность двоичных символов длины L бит менее чем значение P logP, что описано, например, в книге: Р.Е. Кричевский. "Сжатие и поиск информации". - М.: Радио и связь, 1988, стр. 6.

Наиболее близким по своей технической сущности к заявленному устройству сжатия кодируемой последовательности из символов упорядоченного m-ичного алфавита в кодированную последовательность двоичных символов является известное устройство, описанное в патенте США N4652856 МПК6 H 03 М 7/30 от 24.03.87. Известное устройство-прототип включает блок идентификации, вход которого является входом устройства. Выход блока идентификации подключен к информационному входу блока вычисления статистических параметров, выход двоичного числа Nj появлений всех символов упорядоченного m-ичного алфавита, в части j-ой аппроксимирующей кодируемой последовательности, предшествующей очередному символу j-ой аппроксимирующей кодируемой последовательности которого подключен к информационному входу первого блока нормализации, выход суммы Qj,m двоичных чисел появлений символов j-ой аппроксимирующей кодируемой последовательности, предшествующих последнему символу в упорядоченном m-ичном алфавите в части j-ой аппроксимирующей кодируемой последовательности, предшествующей очередному символу j-ой аппроксимирующей кодируемой последовательности, выход суммы Qj,i появлений символов j-ой аппроксимирующей кодируемой последовательности, предшествующих очередному символу j-ой аппроксимирующей кодируемой последовательности в упорядоченном m-ичном алфавите в части j-ой аппроксимирующей кодируемой последовательности, предшествующей очередному символу j-ой аппроксимирующей кодируемой последовательности, выход двоичного числа nj,i появлений очередного символа j-ой аппроксимирующей кодируемой последовательности в части j-ой аппроксимирующей кодируемой последовательности, предшествующей очередному символу j-ой аппроксимирующей кодируемой последовательности блока вычисления статистических параметров, подключены к информационным входам, соответственно, первого, второго и третьего регистров нормализующего сдвига. Управляющие входы каждого из регистров нормализующего сдвига объединены и подключены к выходу первого блока нормализации. Выход идентификации очередного символа j-ой аппроксимирующей кодируемой последовательности с последним символом упорядоченного m-ичного алфавита блока вычисления статистических параметров подключен к управляющему входу третьего блока коммутации. Выход первого регистра нормализующего сдвига подключен к первому информационному входу компаратора, выходы второго и третьего регистров нормализующего сдвига подключены к первым входам, соответственно, первого и второго регистров правого сдвига и дополнительно к первым информационным входам, соответственно, первого и второго блоков коммутации. Вторые информационные входы первого и второго блоков коммутации подключены к выходам, соответственно, первого и второго регистров правого сдвига. Выход компаратора подключен к управляющим входам первого и второго блоков коммутации. Выход первого блока коммутации подключен к первым входам вычитателя и сумматора, второй вход вычитателя подключен ко второму информационному входу компаратора и выходу регистра кодового интервала. Выход второго блока коммутации подключен к первому информационному входу третьего блока коммутации, второй информационный вход которого подключен к выходу вычитателя. Выход третьего блока коммутации подключен к информационным входам второго блока нормализации и первого регистра левого сдвига. Выход второго блока нормализации подключен к управляющим входам первого и второго регистров левого сдвига. Информационный вход второго регистра левого сдвига подключен к выходу сумматора, второй вход которого подключен к выходу регистра нижней границы кодирования. Второй информационный вход регистра нижней границы кодирования подключен к выходу первого блока памяти параметров кодирования, выход первого регистра левого сдвига подключен к первому информационному входу регистра кодового интервала, второй информационный вход которого подключен к выходу второго блока памяти параметров кодирования. Выход записи второго регистра левого сдвига является выходом устройства, выход перезаписи второго регистра левого сдвига подключен к первому информационному входу регистра нижней границы кодирования. Блок вычисления статистических параметров, второй блок памяти параметров кодирования и первый блок памяти параметров кодирования снабжены дополнительным управляющим входом, первый блок нормализации, первый и второй регистры правого сдвига, второй блок нормализации, регистр кодового интервала и регистр нижней границы кодирования снабжены двумя дополнительными управляющими входами, а первый, второй и третий регистры нормализующего сдвига, первый и второй регистры левого сдвига снабжены тремя дополнительными управляющими входами.

Благодаря перечисленной совокупности существенных признаков, устройство-прототип по сравнению с известными аналогами способно сжимать кодируемую последовательность, имеющую вероятность P ее появления, в кодированную последовательность двоичных символов длины L бит сколь угодно близкой к значению P logP.

Недостатком устройства-прототипа является большое время передачи кодированной последовательности двоичных символов по каналу связи или большой требуемый объем устройств хранения кодированной последовательности двоичных символов. Это обусловлено тем, что устройство-прототип не способно сжимать кодируемую последовательность, имеющую вероятность P ее появления, в кодированную последовательность двоичных символов длины L бит менее чем значение P logP, что описано, например, в книге: Р.Е. Кричевский. "Сжатие и поиск информации". - М.: Радио и связь, 1988, стр. 6.

Целью заявляемых изобретений является разработка способа и устройства сжатия кодируемой последовательности из символов упорядоченного m-ичного алфавита в кодированную последовательность двоичных символов, обеспечивающих уменьшение времени передачи кодированной последовательности двоичных символов по каналу связи или уменьшения требуемого объема устройств хранения кодированной последовательности двоичных символов за счет дополнительного сжатия кодируемой последовательности, при котором в кодируемую последовательность вносится погрешность, допустимая для ее получателей. В частности, при сжатии кодируемой последовательности из символов упорядоченного m-ичного алфавита, по своей физической сути являющихся последовательностями элементов изображений, глаз человека не замечает погрешности значений яркости элементов изображений, если эта погрешность не превышает 5...7% от их значений яркости, как описано, например, в книге: А.В.Дворкович, В.П. Дворкович, Ю.Б. Зубарев и др. "Цифровая обработка телевизионных и компьютерных изображений". - М.: Издание международного центра научной и технической информации, 1997, стр. 78.

В заявляемом способе поставленная цель достигается тем, что в известном способе сжатия кодируемой последовательности из символов упорядоченного m-ичного алфавита в кодированную последовательность двоичных символов, заключающемся в предварительном формировании T, где T ≅ mk, m ≥ 2, k ≥ 2, аппроксимирующих кодируемых последовательностей, состоящих из k символов упорядоченного m-ичного алфавита, путем выбора k символов из упорядоченного m-ичного алфавита случайным образом. Для каждой из них устанавливают двоичное значение нижней границы кодирования длиной 2w двоичных разрядов, равное двоичному числу, состоящему из w нулевых двоичных разрядов в целой его части и из w нулевых двоичных разрядов в дробной его части, и устанавливают двоичное значение кодового интервала длиной w двоичных разрядов, равным двоичному числу, состоящему из единичного значения в целой его части и w-1 нулевых двоичных разрядов в дробной его части.

Затем из каждой j-ой, где j = 1, 2,..., Т, аппроксимирующей кодируемой последовательности последовательно, начиная с ее первого символа и до последнего, считывают очередной символ j-ой аппроксимирующей кодируемой последовательности и идентифицируют его с i-ым символом упорядоченного m-ичного алфавита.

Далее вычисляют статистические параметры Nj, nj,i, Qj,i и Qj,m очередного символа j-ой аппроксимирующей кодируемой последовательности, для чего в части j-ой аппроксимирующей кодируемой последовательности, предшествующей очередному символу j-ой аппроксимирующей кодируемой последовательности, определяют двоичное число nj,i его появлений, сумму Qj,i двоичных чисел появлений символов j-ой аппроксимирующей кодируемой последовательности, предшествующих очередному символу j-ой аппроксимирующей кодируемой последовательности в упорядоченном m-ичном алфавите, сумму Qm двоичных чисел появлений символов j-ой аппроксимирующей кодируемой последовательности, предшествующих последнему символу в упорядоченном m-ичном алфавите и двоичное число Nj появлений всех символов упорядоченного m-ичного алфавита.

Затем статистические параметры Nj, nj,i, Qj,i и Qj,m очередного символа j-ой аппроксимирующей кодируемой последовательности нормализуют выполнением следующей последовательности действий. Устанавливают нормализованное значение  очередного символа j-ой аппроксимирующей кодируемой последовательности, равным значению последовательно сдвинутого в направлении старших разрядов двоичного числа N появлений всех символов упорядоченного m-ичного алфавита в части j-ой аппроксимирующей кодируемой последовательности, предшествующей очередному символу j-ой аппроксимирующей кодируемой последовательности, на такое число γ разрядов, при котором нормализованное значение

очередного символа j-ой аппроксимирующей кодируемой последовательности, равным значению последовательно сдвинутого в направлении старших разрядов двоичного числа N появлений всех символов упорядоченного m-ичного алфавита в части j-ой аппроксимирующей кодируемой последовательности, предшествующей очередному символу j-ой аппроксимирующей кодируемой последовательности, на такое число γ разрядов, при котором нормализованное значение  будет находиться в предопределенном диапазоне значений. Нижний предел предопределенного диапазона значений устанавливают, равным двоичному числу 0.11, а верхний предел предопределенного диапазона значений устанавливают, меньшим двоичного числа 1.1. Затем устанавливают нормализованное значение

будет находиться в предопределенном диапазоне значений. Нижний предел предопределенного диапазона значений устанавливают, равным двоичному числу 0.11, а верхний предел предопределенного диапазона значений устанавливают, меньшим двоичного числа 1.1. Затем устанавливают нормализованное значение  очередного символа j-ой аппроксимирующей кодируемой последовательности, равным значению последовательно сдвинутого в направлении старших разрядов на γ разрядов двоичного числа nj,i появлений очередного символа j-ой аппроксимирующей кодируемой последовательности в части j-ой аппроксимирующей кодируемой последовательности, предшествующей очередному символу j-й аппроксимирующей кодируемой последовательности. После чего устанавливают нормализованное значение суммы

очередного символа j-ой аппроксимирующей кодируемой последовательности, равным значению последовательно сдвинутого в направлении старших разрядов на γ разрядов двоичного числа nj,i появлений очередного символа j-ой аппроксимирующей кодируемой последовательности в части j-ой аппроксимирующей кодируемой последовательности, предшествующей очередному символу j-й аппроксимирующей кодируемой последовательности. После чего устанавливают нормализованное значение суммы  очередного символа j-ой аппроксимирующей кодируемой последовательности, равным значению последовательно сдвинутой в направлении старших разрядов на γ разрядов суммы Qj,i двоичных чисел появлений символов j-ой аппроксимирующей кодируемой последовательности, предшествующих очередному символу j-ой аппроксимирующей кодируемой последовательности в упорядоченном m-ичном алфавите, в части j-ой аппроксимирующей кодируемой последовательности, предшествующей очередному символу j-ой аппроксимирующей кодируемой последовательности. Далее устанавливают нормализованное значение суммы

очередного символа j-ой аппроксимирующей кодируемой последовательности, равным значению последовательно сдвинутой в направлении старших разрядов на γ разрядов суммы Qj,i двоичных чисел появлений символов j-ой аппроксимирующей кодируемой последовательности, предшествующих очередному символу j-ой аппроксимирующей кодируемой последовательности в упорядоченном m-ичном алфавите, в части j-ой аппроксимирующей кодируемой последовательности, предшествующей очередному символу j-ой аппроксимирующей кодируемой последовательности. Далее устанавливают нормализованное значение суммы  очередного символа j-ой аппроксимирующей кодируемой последовательности, равным значению последовательно сдвинутой в направлении старших разрядов на γ разрядов суммы Qj,m двоичных чисел появлений символов j-ой аппроксимирующей кодируемой последовательности, предшествующих последнему символу в упорядоченном m-ичном алфавите, в части j-ой аппроксимирующей кодируемой последовательности, предшествующей очередному символу j-ой аппроксимирующей кодируемой последовательности.

очередного символа j-ой аппроксимирующей кодируемой последовательности, равным значению последовательно сдвинутой в направлении старших разрядов на γ разрядов суммы Qj,m двоичных чисел появлений символов j-ой аппроксимирующей кодируемой последовательности, предшествующих последнему символу в упорядоченном m-ичном алфавите, в части j-ой аппроксимирующей кодируемой последовательности, предшествующей очередному символу j-ой аппроксимирующей кодируемой последовательности.

Затем по нормализованным значениям статистических параметров  очередного символа j-ой аппроксимирующей кодируемой последовательности j-ые двоичные значения нижней границы кодирования и кодового интервала уточняют выполнением следующей последовательности действий. Если нормализованное значение суммы

очередного символа j-ой аппроксимирующей кодируемой последовательности j-ые двоичные значения нижней границы кодирования и кодового интервала уточняют выполнением следующей последовательности действий. Если нормализованное значение суммы  очередного символа j-ой аппроксимирующей кодируемой последовательности меньше j-ого двоичного значения кодового интервала, то значение переменной β устанавливают в нулевое значение, иначе значение переменной β устанавливают в единичное значение. Далее, если очередной символ j-ой аппроксимирующей кодируемой последовательности не является последним символом упорядоченного m-ичного алфавита, то j-oe двоичное значение нижней границы кодирования заменяют суммой нормализованного значения суммы

очередного символа j-ой аппроксимирующей кодируемой последовательности меньше j-ого двоичного значения кодового интервала, то значение переменной β устанавливают в нулевое значение, иначе значение переменной β устанавливают в единичное значение. Далее, если очередной символ j-ой аппроксимирующей кодируемой последовательности не является последним символом упорядоченного m-ичного алфавита, то j-oe двоичное значение нижней границы кодирования заменяют суммой нормализованного значения суммы  очередного символа j-ой аппроксимирующей кодируемой последовательности и j-ого двоичного значения нижней границы кодирования и j-oe двоичное значение кодового интервала заменяют нормализованным значением

очередного символа j-ой аппроксимирующей кодируемой последовательности и j-ого двоичного значения нижней границы кодирования и j-oe двоичное значение кодового интервала заменяют нормализованным значением  очередного символа j-ой аппроксимирующей кодируемой последовательности. Иначе, если очередной символ j-ой аппроксимирующей кодируемой последовательности является последним символом упорядоченного m-ичного алфавита, то j-oe двоичное значение нижней границы кодирования заменяют суммой нормализованного значения суммы

очередного символа j-ой аппроксимирующей кодируемой последовательности. Иначе, если очередной символ j-ой аппроксимирующей кодируемой последовательности является последним символом упорядоченного m-ичного алфавита, то j-oe двоичное значение нижней границы кодирования заменяют суммой нормализованного значения суммы  очередного символа j-ой аппроксимирующей кодируемой последовательности и j-ого двоичного значения нижней границы кодирования и j-oe двоичное значение кодового интервала заменяют разностью между j-ым двоичным значением кодового интервала и нормализованным значением суммы

очередного символа j-ой аппроксимирующей кодируемой последовательности и j-ого двоичного значения нижней границы кодирования и j-oe двоичное значение кодового интервала заменяют разностью между j-ым двоичным значением кодового интервала и нормализованным значением суммы  очередного символа j-ой аппроксимирующей кодируемой последовательности. Далее, если переменная β имеет единичное значение, то j-ые двоичные значения нижней границы кодирования и кодового интервала сдвигают в направлении их старших разрядов на один разряд.

очередного символа j-ой аппроксимирующей кодируемой последовательности. Далее, если переменная β имеет единичное значение, то j-ые двоичные значения нижней границы кодирования и кодового интервала сдвигают в направлении их старших разрядов на один разряд.

Затем выделяют и считывают в j-ю аппроксимирующую кодированную последовательность неизменяемую часть j-ого двоичного значения нижней границы кодирования. Выделение неизменяемой части j-ого двоичного значения нижней границы кодирования выполняют определением числа старших разрядов j-ого двоичного значения нижней границы кодирования, при котором последовательно сдвинутое в направлении старших разрядов j-oe двоичное значение кодового интервала будет находиться в предопределенном диапазоне значений.

Далее стирают считанную часть j-ого двоичного значения нижней границы кодирования, сдвигают j-oe двоичное значение нижней границы кодирования в направлении старших разрядов на число разрядов его считанной части и дополняют таким же числом нулевых двоичных символов j-oe двоичное значение нижней границы кодирования со стороны младших разрядов.

После уточнения j-ого двоичного значения нижней границы кодирования по нормализованным значениям статистических параметров  последнего символа j-ой аппроксимирующей кодируемой последовательности, из позиций старших разрядов j-ого двоичного значения нижней границы кодирования последовательно считывают w двоичных символов в j-ю аппроксимирующую кодированную последовательность.

последнего символа j-ой аппроксимирующей кодируемой последовательности, из позиций старших разрядов j-ого двоичного значения нижней границы кодирования последовательно считывают w двоичных символов в j-ю аппроксимирующую кодированную последовательность.

Затем определяют и сравнивают длину Lj каждой j-ой аппроксимирующей кодированной последовательности с предварительно заданной предельно допустимой длиной Lпр. Предварительно заданную предельно допустимую длину Lпр устанавливают не менее w+1 двоичных разрядов. Далее j-ые аппроксимирующие кодируемые последовательности, для которых длины Lj соответствующих им аппроксимирующих кодированных последовательностей превышают предельно допустимую длину Lпр, стирают.

После чего оставшиеся аппроксимирующие кодируемые последовательности сравнивают с кодируемой последовательностью, выбирают из них наиболее близкую к кодируемой последовательности и принимают в качестве кодированной последовательности двоичных символов аппроксимирующую кодированную последовательность, соответствующую выбранной аппроксимирующей кодируемой последовательности. Для сравнения каждой j-ой аппроксимирующей кодируемой последовательности с кодируемой последовательностью из значения каждого очередного символа j-ой аппроксимирующей кодируемой последовательности вычитают значение очередного символа кодируемой последовательности, абсолютные значения полученных разностей суммируют, а наиболее близкой к кодируемой последовательности выбирают аппроксимирующую кодируемую последовательность с наименьшей суммой полученных разностей.

Благодаря новой совокупности существенных признаков за счет формирования аппроксимирующих кодируемых последовательностей и замены кодируемой последовательности на такую аппроксимирующую кодируемую последовательность, которую сжимают в аппроксимирующую кодированную последовательность с длиною не более предельно допустимой длины Lпр и которая одновременно является наиболее близкой к кодируемой последовательности, что обеспечивает уменьшение времени передачи кодированной последовательности по каналу связи или уменьшение требуемого объема устройств хранения кодированной последовательности.

В заявленном устройстве поставленная цель достигается тем, что в известном устройстве сжатия кодируемой последовательности из символов упорядоченного m-ичного алфавита в кодированную последовательность двоичных символов, содержащем блок идентификации, выход которого подключен к информационному входу блока вычисления статистических параметров, выход двоичного числа Nj появлений всех символов упорядоченного m-ичного алфавита, в части j-ой аппроксимирующей кодируемой последовательности, предшествующей очередному символу j-ой аппроксимирующей кодируемой последовательности которого подключен к информационному входу первого блока нормализации. Выход суммы Qj,m двоичных чисел появлений символов j-ой аппроксимирующей кодируемой последовательности, предшествующих последнему символу в упорядоченном m-ичном алфавите в части j-ой аппроксимирующей кодируемой последовательности, предшествующей очередному символу j-ой аппроксимирующей кодируемой последовательности, выход суммы Qj,i появлений символов j-ой аппроксимирующей кодируемой последовательности, предшествующих очередному символу j-ой аппроксимирующей кодируемой последовательности в упорядоченном m-ичном алфавите в части j-ой аппроксимирующей кодируемой последовательности, предшествующей очередному символу j-ой аппроксимирующей кодируемой последовательности, и выход двоичного числа nj,i появлений очередного символа j-ой аппроксимирующей кодируемой последовательности в части j-ой аппроксимирующей кодируемой последовательности, предшествующей очередному символу j-ой аппроксимирующей кодируемой последовательности блока вычисления статистических параметров, подключены к информационным входам, соответственно, первого, второго и третьего регистров нормализующего сдвига. Управляющие входы каждого из регистров нормализующего сдвига объединены и подключены к выходу первого блока нормализации, выход идентификации очередного символа j-ой аппроксимирующей кодируемой последовательности с последним символом упорядоченного m-ичного алфавита блока вычисления статистических параметров подключен к управляющему входу третьего блока коммутации. Выход первого регистра нормализующего сдвига подключен к первому информационному входу компаратора, выходы второго и третьего регистров нормализующего сдвига подключены к информационным входам, соответственно, первого и второго регистров правого сдвига и дополнительно к первым информационным входам, соответственно, первого и второго блоков коммутации, а вторые информационные входы первого и второго блоков коммутации подключены к выходам, соответственно, первого и второго регистров правого сдвига. Выход компаратора подключен к управляющим входам первого и второго блоков коммутации, выход первого блока коммутации подключен к первым входам вычитателя и сумматора. Второй вход вычитателя подключен ко второму информационному входу компаратора и выходу регистра кодового интервала, выход второго блока коммутации подключен к первому информационному входу третьего блока коммутации, второй информационный вход которого подключен к выходу вычитателя. Выход третьего блока коммутации подключен к информационным входам второго блока нормализации и первого регистра левого сдвига, выход второго блока нормализации подключен к управляющим входам первого и второго регистров левого сдвига. Информационный вход второго регистра левого сдвига подключен к выходу сумматора, второй вход которого подключен к выходу регистра нижней границы кодирования, первый информационный вход которого подключен к выходу перезаписи второго регистра левого сдвига. Второй информационный вход регистра нижней границы кодирования подключен к выходу первого блока памяти параметров кодирования. Выход первого регистра левого сдвига подключен к первому информационному входу регистра кодового интервала, второй информационный вход которого подключен к выходу второго блока памяти параметров кодирования. Блок вычисления статистических параметров, второй блок памяти параметров кодирования и первый блок памяти параметров кодирования снабжены дополнительным управляющим входом, первый блок нормализации, первый и второй регистры правого сдвига, второй блок нормализации, регистр кодового интервала и регистр нижней границы кодирования снабжены двумя дополнительными управляющими входами, а первый, второй и третий регистры нормализующего сдвига, первый и второй регистры левого сдвига снабжены тремя дополнительными управляющими входами, на которые поступают сигналы управления, формируемыми блоком управления, не входящим в состав заявленного устройства. Дополнительно введены блок памяти кодируемой последовательности, информационный вход которого является входом устройства, а его выход подключен к первому информационному входу блока выбора, второй информационный вход которого подключен к первому выходу коммутатора, второй выход которого подключен к входу блока идентификации. Информационный вход коммутатора подключен к выходу блока памяти аппроксимирующих кодируемых последовательностей, вход выбора которого подключен к выходу блока сравнения. Выход блока выбора подключен к управляющему входу блока памяти аппроксимирующих кодированных последовательностей, вход записи и счетный вход которого подключены к выходу записи и счетному входу, соответственно, второго регистра левого сдвига. Выход считывания блока памяти аппроксимирующих кодированных последовательностей является информационным выходом устройства, выход сравнения блока памяти аппроксимирующих кодированных последовательностей подключен к первому информационному входу блока сравнения, второй информационный вход которого подключен к выходу блока памяти предельно допустимой длины, причем блок памяти кодируемой последовательности, коммутатор, блок сравнения и блок памяти предельно допустимой длины снабжены дополнительным управляющим входом, а блок выбора, блок памяти аппроксимирующих кодируемых последовательностей и блок памяти аппроксимирующих кодированных последовательностей снабжены двумя дополнительными управляющими входами, на которые поступают сигналы управления, формируемыми блоком управления, не входящим в состав заявленного устройства.

Благодаря новой совокупности существенных признаков за счет дополнительного введения блока памяти кодируемой последовательности, блока памяти аппроксимирующих кодируемых последовательностей, коммутатора, блока выбора, блока памяти аппроксимирующих кодированных последовательностей, блока сравнения и блока памяти предельно допустимой длины, выполняющих действия замены кодируемой последовательности на такую аппроксимирующую кодируемую последовательность, которая сжимается в аппроксимирующую кодированную последовательность с длиною не более предельно допустимой длины Lпр и которая одновременно является наиболее близкой к кодируемой последовательности, уменьшается время передачи кодированной последовательности по каналу связи или уменьшается требуемый объем устройств хранения кодированной последовательности.

Проведенный заявителем анализ уровня техники позволил установить, что аналоги, характеризующиеся совокупностями признаков, тождественным всем признакам заявляемых способа и устройства сжатия кодируемой последовательности из символов упорядоченного m-ичного алфавита в кодированную последовательность двоичных символов, отсутствуют. Следовательно, каждое из заявленных изобретений соответствует условию патентоспособности "Новизна".

Результаты поиска известных решений в данной и смежных областях техники с целью выявления признаков, совпадающих с отличительными от прототипов признаками каждого заявляемого изобретения, показали, что они не следуют явным образом из уровня техники. Из определенного заявителем уровня техники не выявлена известность влияния предусматриваемых существенными признаками каждого из заявляемых изобретений на достижение указанного технического результата. Следовательно, каждое из заявляемых изобретений соответствует условию патентоспособности "Изобретательский уровень".

Заявленные объекты изобретения поясняются чертежами, на которых:

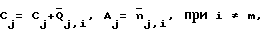

- на фиг. 1 - осциллограммы, поясняющие суть заявляемого способа сжатия кодируемой последовательности из символов упорядоченного m-ичного алфавита в кодированную последовательность двоичных символов;

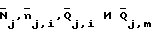

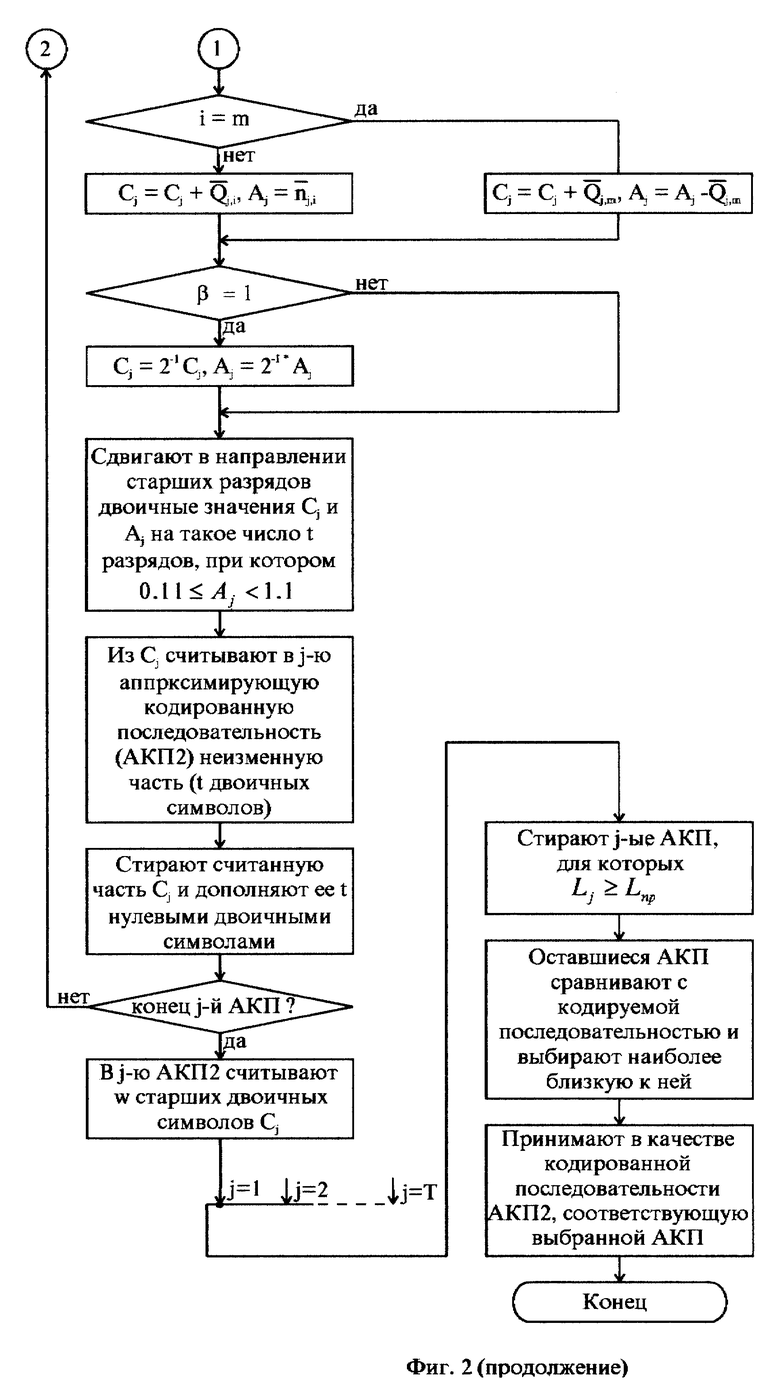

- на фиг. 2 - алгоритм сжатия кодируемой последовательности из символов упорядоченного m-ичного алфавита в кодированную последовательность двоичных символов согласно заявляемого способа;

- на фиг. 3 - структурная схема устройства сжатия кодируемой последовательности из символов упорядоченного m-ичного алфавита в кодированную последовательность двоичных символов;

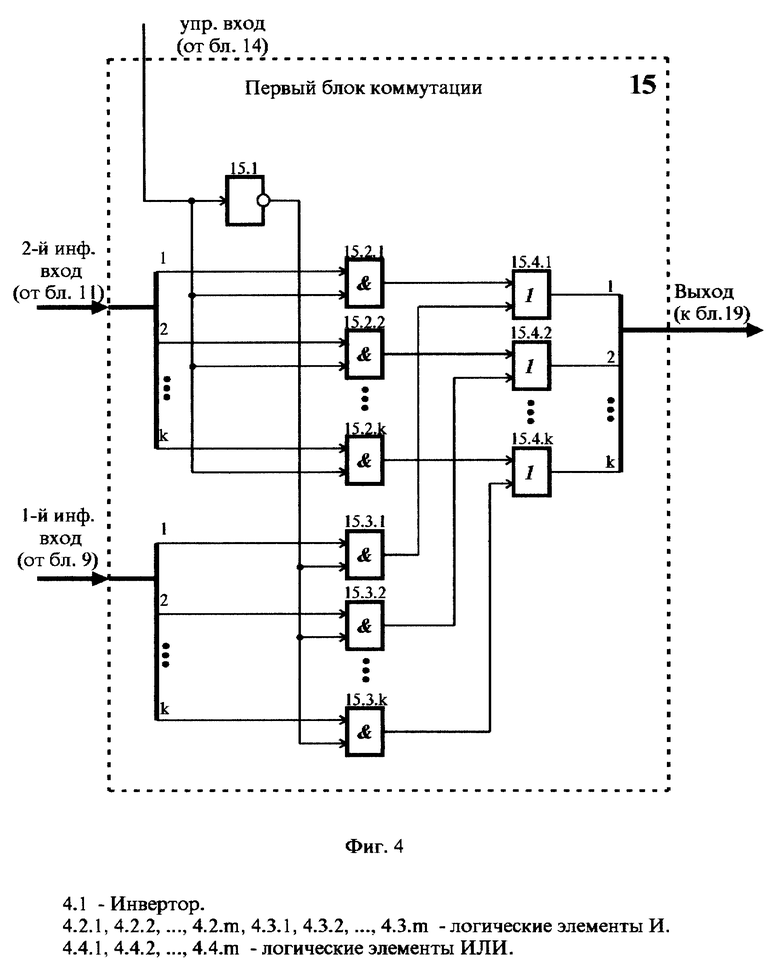

- на фиг. 4 - структурная схема первого блока коммутации 15;

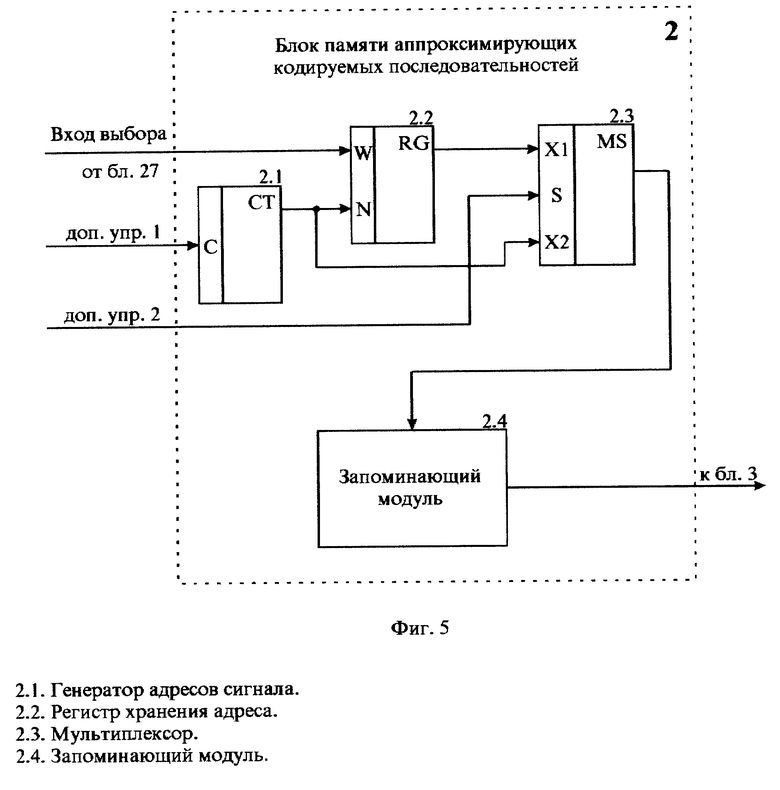

- на фиг. 5 - структурная схема блока памяти аппроксимирующих кодируемых последовательностей 2;

- на фиг. 6 - структурная схема коммутатора 3;

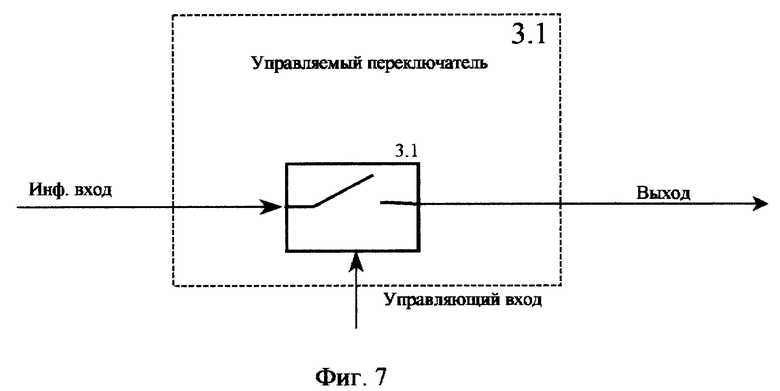

- на фиг. 7 - структурная схема управляемого переключателя 3.1;

- на фиг. 8 - структурная схема блока выбора 4;

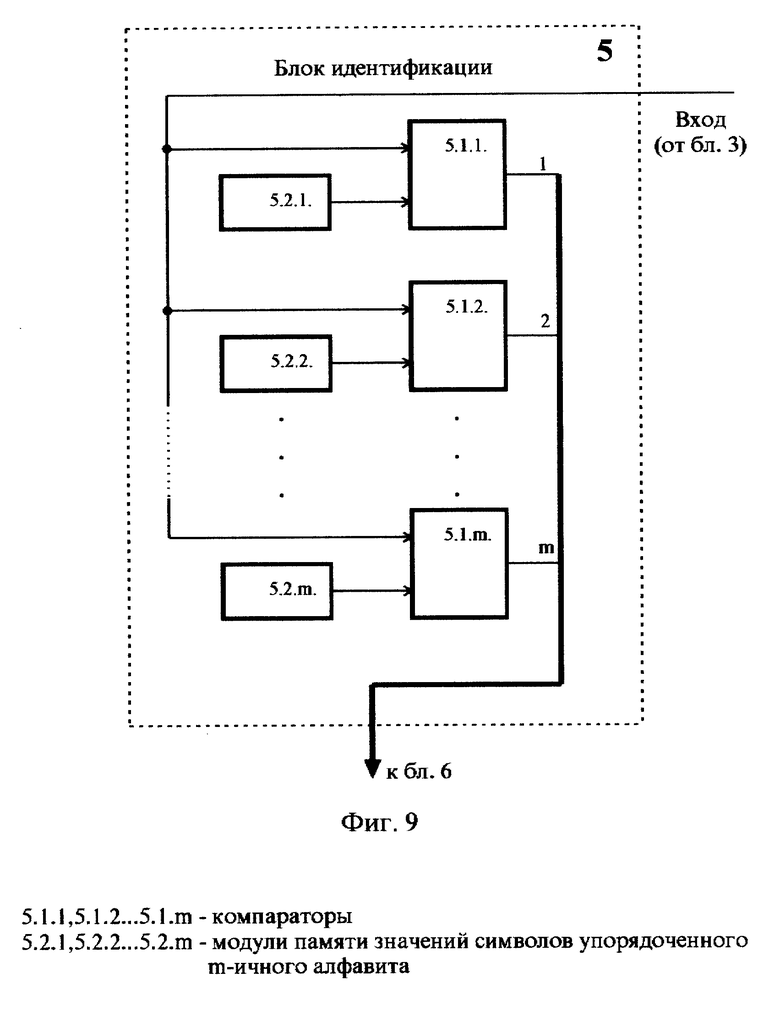

- на фиг. 9 - структурная схема блока идентификации 5;

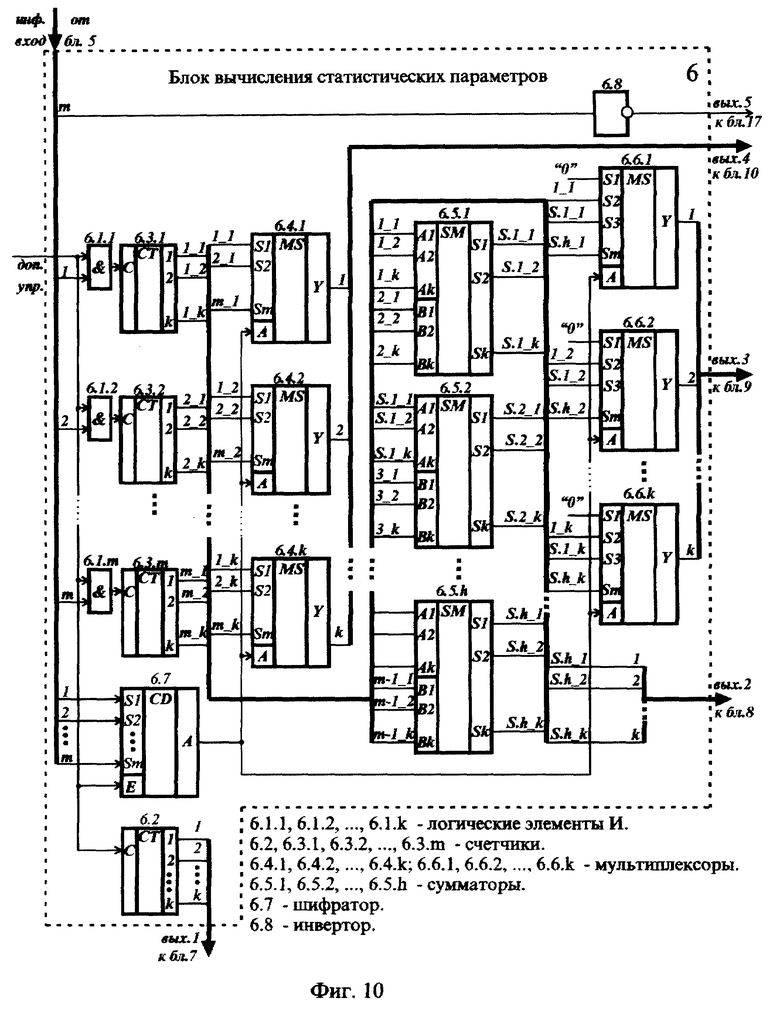

- на фиг. 10 - структурная схема блока вычисления статистических параметров 6;

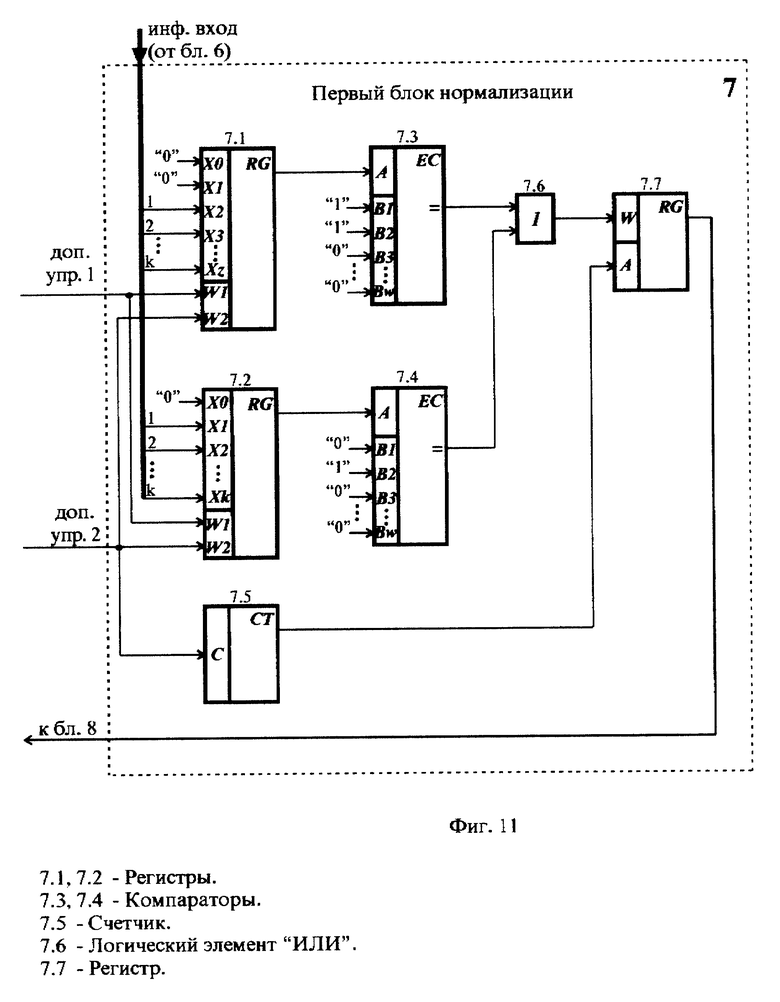

- на фиг. 11 - структурная схема первого блока нормализации 7;

- на фиг. 12 - структурная схема первого регистра нормализующего сдвига 8;

- на фиг. 13 - структурная схема первого регистра правого сдвига 11;

- на фиг. 14 - структурная схема второго блока нормализации 18;

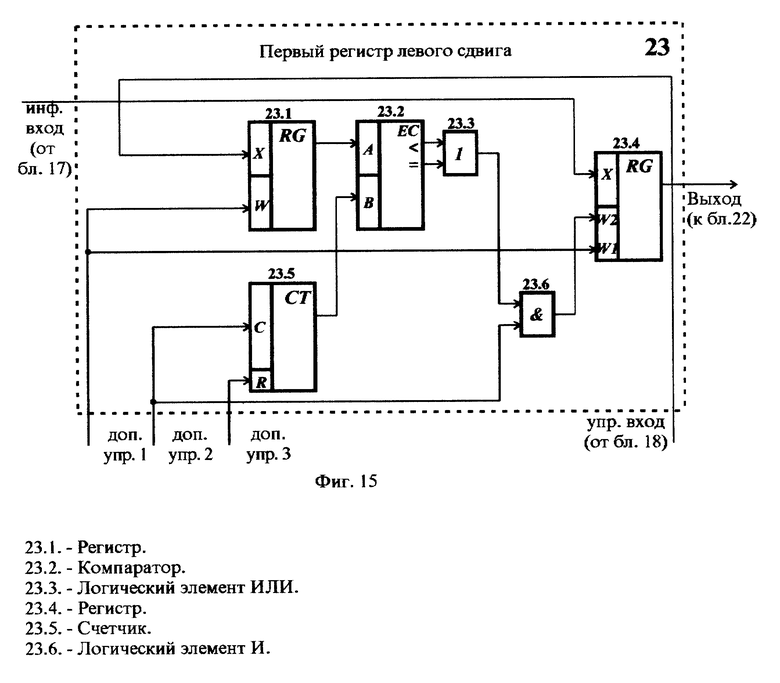

- на фиг. 15 - структурная схема первого регистра левого сдвига 23;

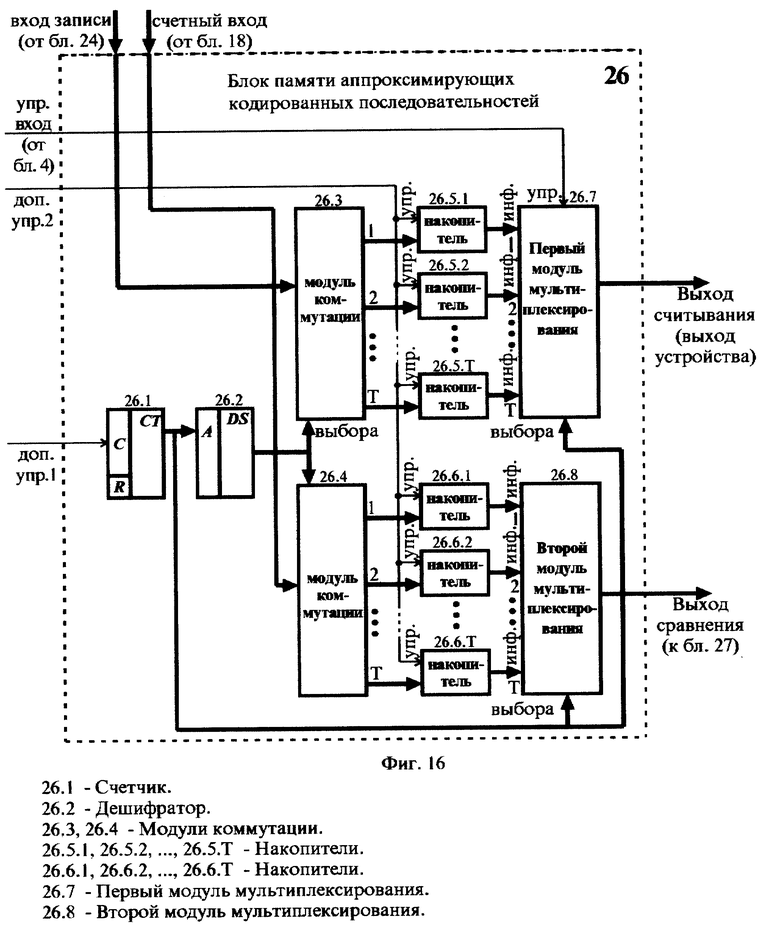

- на фиг. 16 - структурная схема блока памяти аппроксимирующих кодированных последовательностей 26;

- на фиг. 17 - структурная схема блока сравнения 27;

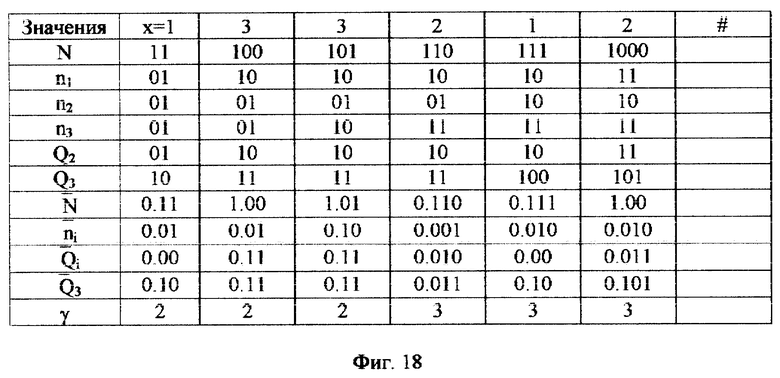

- на фиг. 18 - значения статистических параметров очередного символа кодируемой последовательности согласно способа-прототипа;

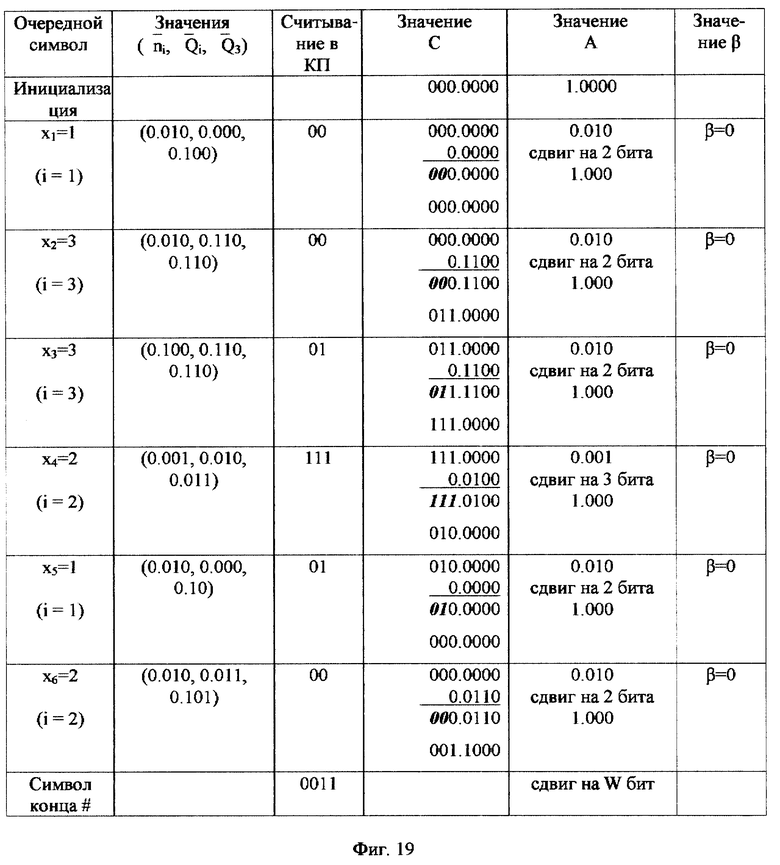

- на фиг. 19 - значения параметров кодирования при сжатии кодируемой последовательности из символов упорядоченного m-ичного алфавита в кодированную последовательность двоичных символов согласно способа-прототипа;

- на фиг. 20 - значения статистических параметров очередного символа кодируемой последовательности согласно заявляемого способа;

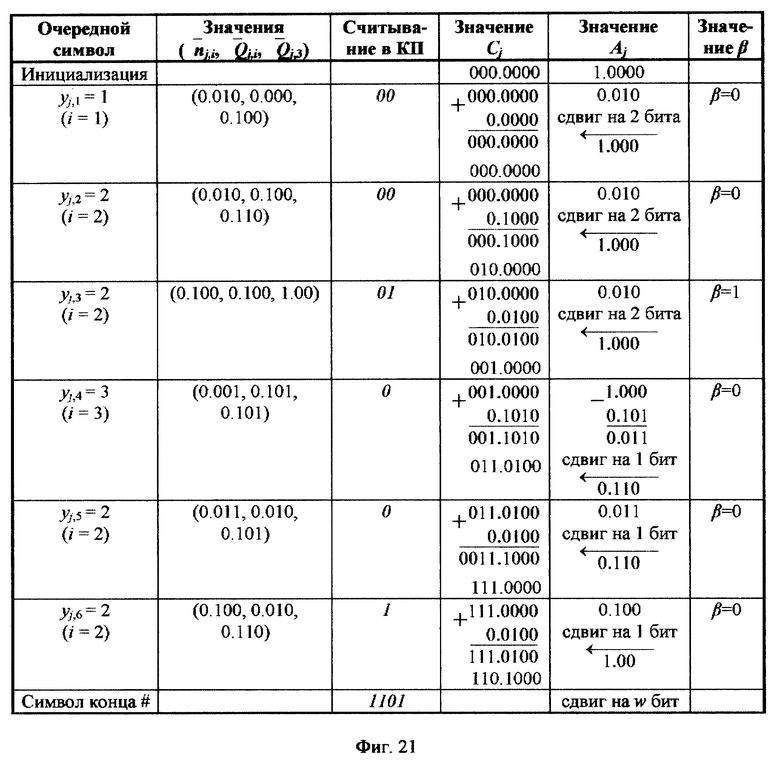

- на фиг. 21 - значения параметров кодирования при сжатии кодируемой последовательности из символов упорядоченного m-ичного алфавита в кодированную последовательность двоичных символов согласно заявляемого способа;

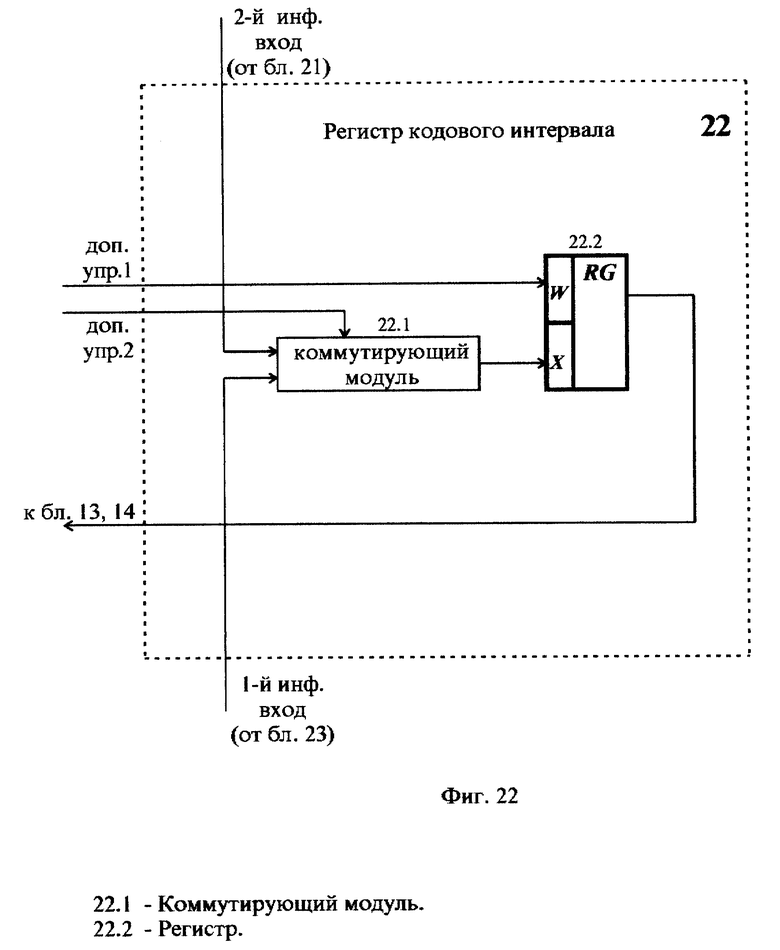

- на фиг. 22 - структурная схема регистра кодового интервала 22;

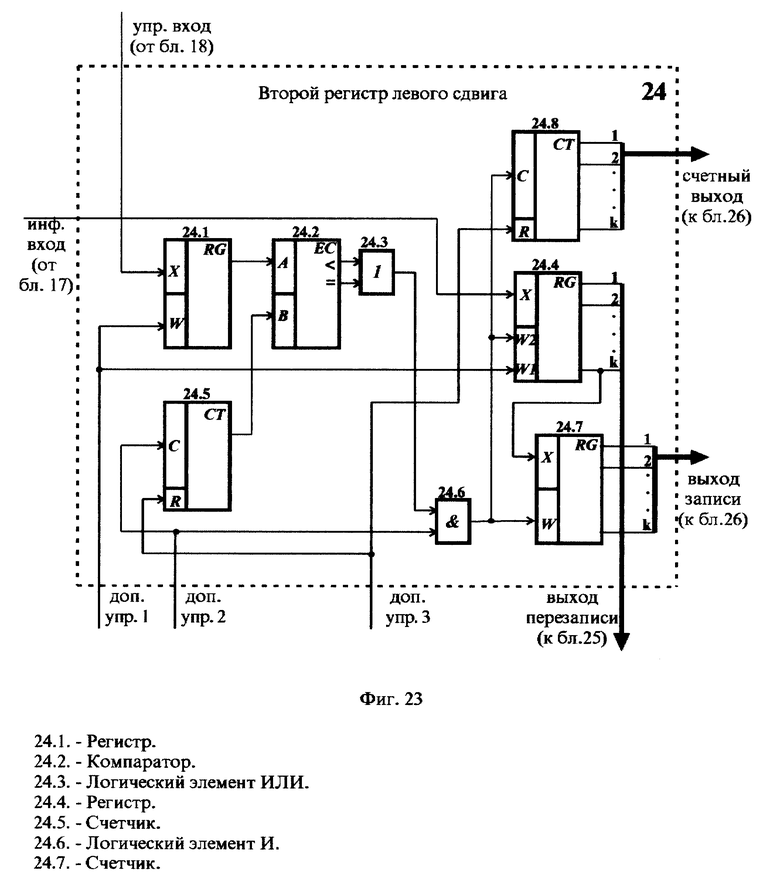

- на фиг. 23 - структурная схема второго регистра левого сдвига 24;

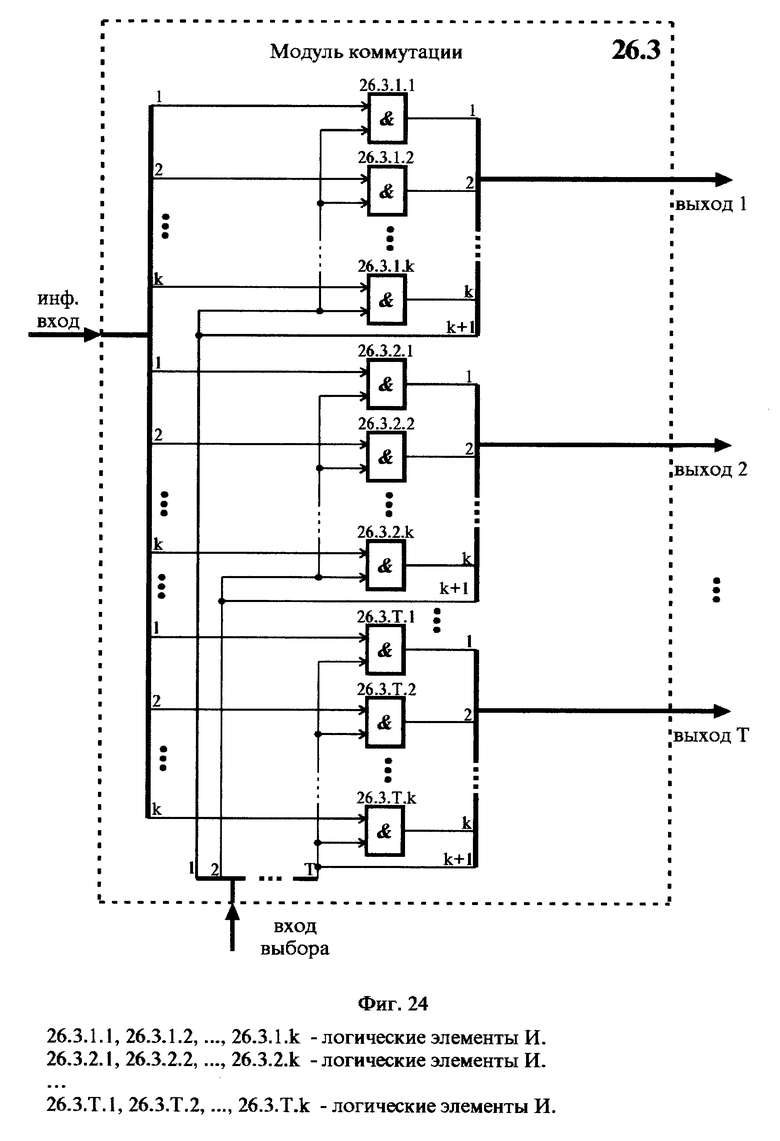

- на фиг. 24 - структурная схема модуля коммутации 26.3;

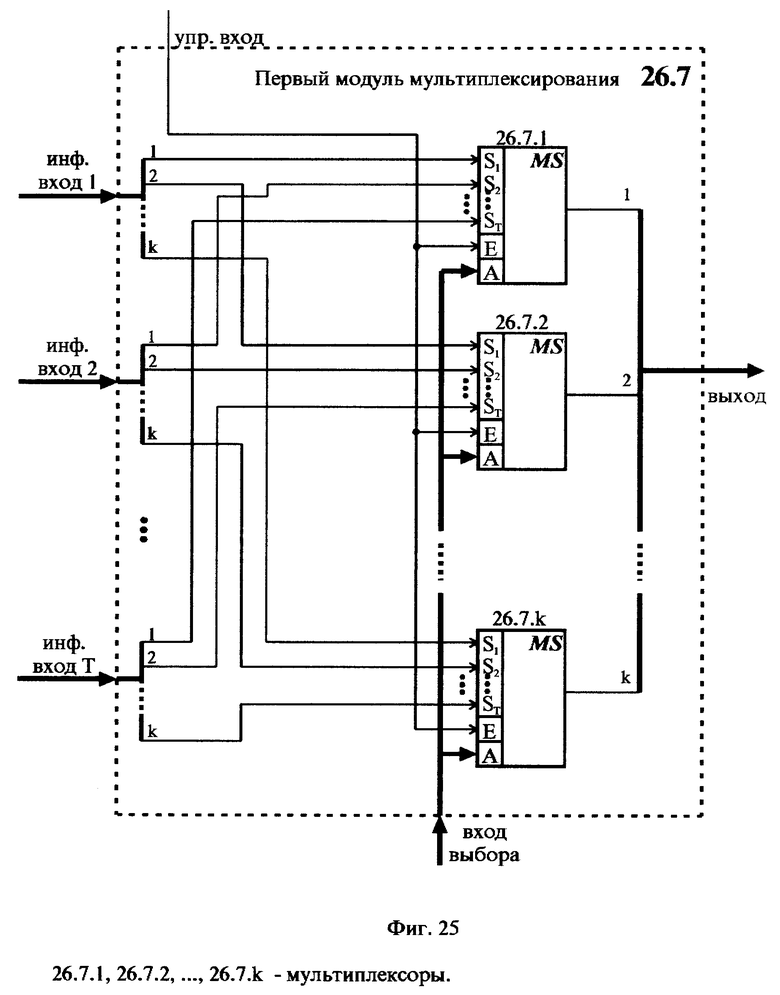

- на фиг. 25 - структурная схема первого модуля мультиплексирования 26.7;

- на фиг. 26 - структурная схема второго модуля мультиплексирования 26.8;

- на фиг. 27 - временные диаграммы, поясняющие суть работы устройства сжатия кодируемой последовательности из символов упорядоченного m-ичного алфавита в кодированную последовательность двоичных символов.

Реализация заявляемого способа объясняется следующим образом.

Для своевременной передачи избыточных кодируемых последовательностей из символов упорядоченного m-ичного алфавита по каналам связи или для их хранения в устройствах хранения с ограниченным допустимым объемом устройств хранения используют их сжатие в кодированные последовательности двоичных символов, что позволяет уменьшить время передачи кодированной последовательности по каналу связи или требуемый объем устройств хранения кодированной последовательности. В известных способах сжатия кодируемой последовательности из символов упорядоченного m-ичного алфавита в кодированную последовательность двоичных символов время передачи кодированной последовательности по каналу связи или требуемый объем устройств хранения кодированной последовательности не может быть сделано меньшим значения L/R, в котором L есть длина кодированной последовательности двоичных символов, равная значению P logP, где P является вероятностью появления кодируемой последовательности из символов упорядоченного m-ичного алфавита, a R есть скорость передачи кодированной последовательности по каналу связи или ее записи в устройство хранения, что описано, например, в книге: Р.Е. Кричевский. "Сжатие и поиск информации". - М.: Радио и связь, 1988, стр. 6. Однако время передачи кодированной последовательности по каналу связи или требуемый объем устройств ее хранения может быть сделано меньшим значения L/R, если сжимать кодируемые последовательности с погрешностью, допустимой для получателя кодируемой последовательности, что описано, например, в книге: К. Шеннон. "Работы по теории информации и кибернетике". - М.: Иностранная литература, 1963, стр. 618. Допустимость указанной погрешности кодируемых последовательностей объясняется тем, что, например, глаз человека не замечает искажение изображения, если яркости составляющих их элементов, являющихся элементами кодируемых последовательностей, искажаются не более чем на 5...7%, как описано, например, в книге: А.В.Дворкович, В.П.Дворкович, Ю.Б.Зубарев и др. "Цифровая обработка телевизионных и компьютерных изображений". - М.: Издание международного центра научной и технической информации, 1997, стр. 78. Вид допускающих погрешность кодируемых последовательностей цифровых речевых, звуковых, телевизионных, факсимильных и подобных им сообщений, дискретизированных с частотой дискретизации F = 1/Т и квантованных на 2m уровней (2m > 2), показан на фиг. 1(а). Вид кодированных последовательностей двоичных символов показан на фиг.1(б). На фиг. 1(б) показано, что длина кодированной последовательности двоичных символов может быть больше предельно допустимой длины Lпр, где значение предельно допустимой длины Lпр установлено меньше значения P logP, где P есть вероятность появления кодируемой последовательности из символов упорядоченного m-ичного алфавита. Дополнительное сжатие кодируемой последовательности с указанной допустимой погрешностью позволяет уменьшить время передачи кодированной последовательности по каналу связи или требуемый объем устройств хранения кодированной последовательности. Поэтому для передачи кодируемых последовательностей по каналам связи или для их хранения в устройствах хранения с ограниченным допустимым объемом устройств хранения существенные преимущества имеет использование сжатия кодируемой последовательности из символов упорядоченного m-ичного алфавита в кодированную последовательность двоичных символов с потерей информации, несущественной для получателя, обеспечивающее уменьшение времени их передачи или объем устройств их хранения.

В заявляемом способе предварительно формируют Т, где T ≅ mk, m ≥ 2, k ≥ 2, аппроксимирующих кодируемых последовательностей, состоящих из k символов упорядоченного m-ичного алфавита. Чем большее количество Т аппроксимирующих кодируемых последовательностей сформировано, тем выше вероятность выбора среди них наиболее близкой к кодируемой последовательности. Каждую аппроксимирующую кодируемую последовательность формируют путем выбора k символов из упорядоченного m-ичного алфавита случайным образом, описанным, например, в книге: Д.Кнут. "Искусство программирования на ЭВМ". - М.: Мир, 1977, т. 2, стр. 22. Вид T аппроксимирующих кодируемых последовательностей представлен на фиг. 1(в).

Для каждой аппроксимирующей кодируемой последовательности устанавливают двоичное значение нижней границы кодирования длиной 2w двоичных разрядов, равное двоичному числу, состоящему из w нулевых двоичных разрядов в целой его части и из w нулевых двоичных разрядов в дробной его части, и устанавливают двоичное значение кодового интервала длиной w двоичных разрядов, равное двоичному числу, состоящему из единичного значения в целой его части и w-1 нулевых двоичных разрядов в дробной его части. Известные способы установления двоичного значения нижней границы кодирования длиной 2w двоичных разрядов и двоичного значения кодового интервала длиной w двоичных разрядов описаны, например, в книге: Rissanen J., Langdon G. Universal modeling and coding. // IEEE Transaction on Information Theory. - Vol. IT-27, 1981, N 1, Jan., p. 12-23.

Последовательно, начиная с ее первого символа и до последнего, считывают очередной символ из каждой j-ой, где j = 1, 2,...,Т, аппроксимирующей кодируемой последовательности. Известные способы последовательного считывания очередного символа из аппроксимирующей кодируемой последовательности описаны, например, в книге: Б.А.Калабеков. "Микропроцессоры и их применение в системах передачи и обработки". - М.: Радио и связь, 1988, стр. 34.

Очередной символ j-ой аппроксимирующей кодируемой последовательности идентифицируют с i-ым символом упорядоченного m-ичного алфавита. Для идентификации очередного символа j-ой аппроксимирующей кодируемой последовательности с i-ым символом упорядоченного m-ичного алфавита его последовательно сравнивают с каждым из m символом упорядоченного m-ичного алфавита до выявления совпадения. Известные способы идентификации описаны, например, в книге: У. Питерсон, Э.Уэлдон. "Коды, исправляющие ошибки". - М.: Мир, 1976, стр. 15.

Далее вычисляют статистические параметры Nj, nj,i, Qj,i и Qj,m очередного символа j-ой аппроксимирующей кодируемой последовательности. Для этого в части j-ой аппроксимирующей кодируемой последовательности, предшествующей очередному символу j-ой аппроксимирующей кодируемой последовательности, определяют двоичное число nj,i его появлений, как описано, например, в патенте США N 4652856 от 24.03.87.

В части j-ой аппроксимирующей кодируемой последовательности, предшествующей ее очередному символу, определяют сумму Qj,i двоичных чисел появлений символов j-ой аппроксимирующей кодируемой последовательности, предшествующих очередному символу j-ой аппроксимирующей кодируемой последовательности в упорядоченном m-ичном алфавите, как описано, например, в патенте США N 4652856 от 24.03.87.

В части j-ой аппроксимирующей кодируемой последовательности, предшествующей очередному символу j-ой аппроксимирующей кодируемой последовательности, определяют сумму Qm двоичных чисел появлений символов j-ой аппроксимирующей кодируемой последовательности, предшествующих последнему символу в упорядоченном m-ичном алфавите, как описано, например, в патенте США N 4652856 от 24.03.87.

В части j-ой аппроксимирующей кодируемой последовательности, предшествующей очередному символу j-ой аппроксимирующей кодируемой последовательности, определяют двоичное число Nj появлений всех символов упорядоченного m-ичного алфавита, как описано, например, в патенте США N 4652856 от 24.03.87.

Затем статистические параметры Nj, nj,i, Qj,i и Qj,m очередного символа j-ой аппроксимирующей кодируемой последовательности нормализуют выполнением следующей последовательности действий. Устанавливают нормализованное значение  очередного символа j-ой аппроксимирующей кодируемой последовательности, равным значению последовательно сдвинутого в направлении старших разрядов двоичного числа N появлений всех символов упорядоченного m-ичного алфавита в части j-ой аппроксимирующей кодируемой последовательности, предшествующей очередному символу j-ой аппроксимирующей кодируемой последовательности, на такое число γ разрядов, при котором нормализованное значение

очередного символа j-ой аппроксимирующей кодируемой последовательности, равным значению последовательно сдвинутого в направлении старших разрядов двоичного числа N появлений всех символов упорядоченного m-ичного алфавита в части j-ой аппроксимирующей кодируемой последовательности, предшествующей очередному символу j-ой аппроксимирующей кодируемой последовательности, на такое число γ разрядов, при котором нормализованное значение  будет находиться в предопределенном диапазоне значений. Нижний предел предопределенного диапазона значений устанавливают, равным двоичному числу 0.11, а верхний предел предопределенного диапазона значений устанавливают, меньшим двоичного числа 1.1. Известные способы последовательного сдвига в направлении старших разрядов двоичного числа описаны, например, в книге: Б. А. Калабеков. "Микропроцессоры и их применение в системах передачи и обработки". - М.: Радио и связь, 1988, стр. 10.

будет находиться в предопределенном диапазоне значений. Нижний предел предопределенного диапазона значений устанавливают, равным двоичному числу 0.11, а верхний предел предопределенного диапазона значений устанавливают, меньшим двоичного числа 1.1. Известные способы последовательного сдвига в направлении старших разрядов двоичного числа описаны, например, в книге: Б. А. Калабеков. "Микропроцессоры и их применение в системах передачи и обработки". - М.: Радио и связь, 1988, стр. 10.

Известные способы сравнения двоичного числа с нижним и верхним пределами предопределенного диапазона значений описаны, например, в книге: Д. Кнут. "Искусство программирования на ЭВМ". - М.: Мир, 1978, т. 3, стр. 219.

Затем устанавливают нормализованное значение  очередного символа j-ой аппроксимирующей кодируемой последовательности, равным значению последовательно сдвинутого в направлении старших разрядов на γ разрядов двоичного числа nj,i появлений очередного символа j-ой аппроксимирующей кодируемой последовательности в части j-ой аппроксимирующей кодируемой последовательности, предшествующей очередному символу j-ой аппроксимирующей кодируемой последовательности. После чего устанавливают нормализованное значение суммы

очередного символа j-ой аппроксимирующей кодируемой последовательности, равным значению последовательно сдвинутого в направлении старших разрядов на γ разрядов двоичного числа nj,i появлений очередного символа j-ой аппроксимирующей кодируемой последовательности в части j-ой аппроксимирующей кодируемой последовательности, предшествующей очередному символу j-ой аппроксимирующей кодируемой последовательности. После чего устанавливают нормализованное значение суммы  очередного символа j-ой аппроксимирующей кодируемой последовательности, равным значению последовательно сдвинутой в направлении старших разрядов на γ разрядов суммы Qj,i двоичных чисел появлений символов j-ой аппроксимирующей кодируемой последовательности, предшествующих очередному символу j-ой аппроксимирующей кодируемой последовательности в упорядоченном m-ичном алфавите, в части j-ой аппроксимирующей кодируемой последовательности, предшествующей очередному символу j-ой аппроксимирующей кодируемой последовательности. Далее устанавливают нормализованное значение суммы

очередного символа j-ой аппроксимирующей кодируемой последовательности, равным значению последовательно сдвинутой в направлении старших разрядов на γ разрядов суммы Qj,i двоичных чисел появлений символов j-ой аппроксимирующей кодируемой последовательности, предшествующих очередному символу j-ой аппроксимирующей кодируемой последовательности в упорядоченном m-ичном алфавите, в части j-ой аппроксимирующей кодируемой последовательности, предшествующей очередному символу j-ой аппроксимирующей кодируемой последовательности. Далее устанавливают нормализованное значение суммы  очередного символа j-ой аппроксимирующей кодируемой последовательности, равным значению последовательно сдвинутой в направлении старших разрядов на γ разрядов суммы Qj,m двоичных чисел появлений символов j-ой аппроксимирующей кодируемой последовательности, предшествующих последнему символу в упорядоченном m-ичном алфавите, в части j-ой аппроксимирующей кодируемой последовательности, предшествующей очередному символу j-ой аппроксимирующей кодируемой последовательности.

очередного символа j-ой аппроксимирующей кодируемой последовательности, равным значению последовательно сдвинутой в направлении старших разрядов на γ разрядов суммы Qj,m двоичных чисел появлений символов j-ой аппроксимирующей кодируемой последовательности, предшествующих последнему символу в упорядоченном m-ичном алфавите, в части j-ой аппроксимирующей кодируемой последовательности, предшествующей очередному символу j-ой аппроксимирующей кодируемой последовательности.

Затем по нормализованным значениям статистических параметров  очередного символа j-ой аппроксимирующей кодируемой последовательности j-ые двоичные значения нижней границы кодирования и кодового интервала уточняют выполнением следующей последовательности действий. Если нормализованное значение суммы

очередного символа j-ой аппроксимирующей кодируемой последовательности j-ые двоичные значения нижней границы кодирования и кодового интервала уточняют выполнением следующей последовательности действий. Если нормализованное значение суммы  очередного символа j-ой аппроксимирующей кодируемой последовательности меньше j-ого двоичного значения кодового интервала, то значение переменной β устанавливают в нулевое значение, иначе значение переменной β устанавливают в единичное значение. Известные способы сравнения нормализованного значения суммы

очередного символа j-ой аппроксимирующей кодируемой последовательности меньше j-ого двоичного значения кодового интервала, то значение переменной β устанавливают в нулевое значение, иначе значение переменной β устанавливают в единичное значение. Известные способы сравнения нормализованного значения суммы  очередного символа j-ой аппроксимирующей кодируемой последовательности с j-ым двоичным значением кодового интервала описаны, например, в книге: Д.Кнут. "Искусство программирования на ЭВМ". - М. : Мир, 1978, т. 3, стр. 219. Далее, если очередной символ j-ой аппроксимирующей кодируемой последовательности не является последним символом упорядоченного m-ичного алфавита, то j-oe двоичное значение нижней границы кодирования заменяют суммой нормализованного значения суммы

очередного символа j-ой аппроксимирующей кодируемой последовательности с j-ым двоичным значением кодового интервала описаны, например, в книге: Д.Кнут. "Искусство программирования на ЭВМ". - М. : Мир, 1978, т. 3, стр. 219. Далее, если очередной символ j-ой аппроксимирующей кодируемой последовательности не является последним символом упорядоченного m-ичного алфавита, то j-oe двоичное значение нижней границы кодирования заменяют суммой нормализованного значения суммы  очередного символа j-ой аппроксимирующей кодируемой последовательности и j-ого двоичного значения нижней границы кодирования и j-oe двоичное значение кодового интервала заменяют нормализованным значением

очередного символа j-ой аппроксимирующей кодируемой последовательности и j-ого двоичного значения нижней границы кодирования и j-oe двоичное значение кодового интервала заменяют нормализованным значением  очередного символа j-ой аппроксимирующей кодируемой последовательности. Иначе, если очередной символ j-ой аппроксимирующей кодируемой последовательности является последним символом упорядоченного m-ичного алфавита, то j-oe двоичное значение нижней границы кодирования заменяют суммой нормализованного значения суммы

очередного символа j-ой аппроксимирующей кодируемой последовательности. Иначе, если очередной символ j-ой аппроксимирующей кодируемой последовательности является последним символом упорядоченного m-ичного алфавита, то j-oe двоичное значение нижней границы кодирования заменяют суммой нормализованного значения суммы  очередного символа j-ой аппроксимирующей кодируемой последовательности и j-ого двоичного значения нижней границы кодирования и j-ое двоичное значение кодового интервала заменяют разностью между j-ым двоичным значением кодового интервала и нормализованным значением суммы

очередного символа j-ой аппроксимирующей кодируемой последовательности и j-ого двоичного значения нижней границы кодирования и j-ое двоичное значение кодового интервала заменяют разностью между j-ым двоичным значением кодового интервала и нормализованным значением суммы  очередного символа j-ой аппроксимирующей кодируемой последовательности. Далее, если переменная β имеет единичное значение, то j-ые двоичные значения нижней границы кодирования и кодового интервала сдвигают в направлении их старших разрядов на один разряд. Известные способы сдвига в направлении старших разрядов на один разряд j-ых двоичных значений нижней границы кодирования и кодового интервала описаны, например, в книге: Б.А. Калабеков. "Микропроцессоры и их применение в системах передачи и обработки". - М.: Радио и связь, 1988, стр. 10.

очередного символа j-ой аппроксимирующей кодируемой последовательности. Далее, если переменная β имеет единичное значение, то j-ые двоичные значения нижней границы кодирования и кодового интервала сдвигают в направлении их старших разрядов на один разряд. Известные способы сдвига в направлении старших разрядов на один разряд j-ых двоичных значений нижней границы кодирования и кодового интервала описаны, например, в книге: Б.А. Калабеков. "Микропроцессоры и их применение в системах передачи и обработки". - М.: Радио и связь, 1988, стр. 10.

Выделение неизменяемой части j-ого двоичного значения нижней границы кодирования заключается в следующем. Выделение неизменяемой части j-ого двоичного значения нижней границы кодирования выполняют определением числа α старших разрядов j-ого двоичного значения нижней границы кодирования, при котором последовательно сдвинутое в направлении старших разрядов j-oe двоичное значение кодового интервала будет находиться в предопределенном диапазоне значений. Часть j-oro двоичного значения нижней границы кодирования, составляющая число α старших разрядов, является неизменяемой частью j-oro двоичного значения нижней границы кодирования. В книге, например, Rissanen J. , Langdon G. Universal modeling and coding. // IEEE Transaction on Information Theory. - Vol.IT-27, 1981, N 1, Jan., p. 12-23, доказывается, что при указанной последовательности действий выделенная часть j-oro двоичного значения нижней границы кодирования не изменяется ни при каких последующих считываемых символах аппроксимирующей кодируемой последовательности, что позволяет считывать в j-ю аппроксимирующую кодированную последовательность неизменяемую часть j-ого двоичного значения нижней границы кодирования. Известные способы выделения неизменяемой части j-ого двоичного значения нижней границы кодирования описаны, например, в патенте США N 4652856 от 24.03.87.

В j-ю аппроксимирующую кодированную последовательность считывают неизменяемую часть j-ого двоичного значения нижней границы кодирования. Известные способы считывания в j-ю аппроксимирующую кодированную последовательность неизменяемой части j-ого двоичного значения нижней границы кодирования описаны, например, в патенте США N 4652856 от 24.03.87.

Считанную часть j-ого двоичного значения нижней границы кодирования стирают. Известные способы стирания считанной части j-ого двоичного значения нижней границы кодирования описаны, например, в книге: У. Питерсон, Э. Уэлдон. "Коды, исправляющие ошибки". - М.: Мир, 1976, стр. 17.

Затем сдвигают j-e двоичное значение нижней границы кодирования в направлении старших разрядов на число разрядов его считанной части и дополняют таким же числом нулевых двоичных символов j-oe двоичное значение нижней границы кодирования со стороны младших разрядов. Известные способы сдвига j-ого двоичного значения нижней границы кодирования в направлении старших разрядов на число разрядов его считанной части описаны, например, в книге: Б.А. Калабеков. "Микропроцессоры и их применение в системах передачи и обработки". - М. : Радио и связь, 1988, стр. 10. Известные способы дополнения таким же числом нулевых двоичных символов j-ого двоичного значения нижней границы кодирования со стороны младших разрядов описаны, например, в книге: Б.А.Калабеков. "Микропроцессоры и их применение в системах передачи и обработки" - М.: Радио и связь, 1988, стр. 14.

После уточнения j-ого двоичного значения нижней границы кодирования по нормализованным значениям статистических параметров  последнего символа j-ой аппроксимирующей кодируемой последовательности, последовательное считывание w двоичных символов из позиций старших разрядов j-ого двоичного значения нижней границы кодирования в j-ю аппроксимирующую кодированную последовательность заключается в следующем. Уточнение j-ого двоичного значения нижней границы кодирования по нормализованным значениям статистических параметров

последнего символа j-ой аппроксимирующей кодируемой последовательности, последовательное считывание w двоичных символов из позиций старших разрядов j-ого двоичного значения нижней границы кодирования в j-ю аппроксимирующую кодированную последовательность заключается в следующем. Уточнение j-ого двоичного значения нижней границы кодирования по нормализованным значениям статистических параметров  последнего символа j-ой аппроксимирующей кодируемой последовательности выполняют точно так же, как уточнение j-ого двоичного значения нижней границы кодирования по нормализованным значениям статистических параметров

последнего символа j-ой аппроксимирующей кодируемой последовательности выполняют точно так же, как уточнение j-ого двоичного значения нижней границы кодирования по нормализованным значениям статистических параметров  очередного символа j-ой аппроксимирующей кодируемой последовательности. В качестве последнего символа j-ой аппроксимирующей кодируемой последовательности используется наиболее редко встречающийся символ конца последовательности, поэтому для обеспечения возможности восстановления кодируемой последовательности из кодированной последовательности необходимо последовательное считывание w двоичных символов из позиций старших разрядов j-ого двоичного значения нижней границы кодирования в j-ю аппроксимирующую кодированную последовательность. Известные способы последовательного считывания w двоичных символов из позиций старших разрядов j-ого двоичного значения нижней границы кодирования в j-ю аппроксимирующую кодированную последовательность описаны, например, в книге: Б.А.Калабеков. "Микропроцессоры и их применение в системах передачи и обработки". - М.: Радио и связь, 1988, стр. 34. Вид Т аппроксимирующих кодированных последовательностей представлен на фиг. 1(г).

очередного символа j-ой аппроксимирующей кодируемой последовательности. В качестве последнего символа j-ой аппроксимирующей кодируемой последовательности используется наиболее редко встречающийся символ конца последовательности, поэтому для обеспечения возможности восстановления кодируемой последовательности из кодированной последовательности необходимо последовательное считывание w двоичных символов из позиций старших разрядов j-ого двоичного значения нижней границы кодирования в j-ю аппроксимирующую кодированную последовательность. Известные способы последовательного считывания w двоичных символов из позиций старших разрядов j-ого двоичного значения нижней границы кодирования в j-ю аппроксимирующую кодированную последовательность описаны, например, в книге: Б.А.Калабеков. "Микропроцессоры и их применение в системах передачи и обработки". - М.: Радио и связь, 1988, стр. 34. Вид Т аппроксимирующих кодированных последовательностей представлен на фиг. 1(г).

Затем определяют и сравнивают длину Lj каждой j-ой аппроксимирующей кодированной последовательности с предварительно заданной предельно допустимой длиной Lпр. Определение длины Lj каждой j-ой аппроксимирующей кодированной последовательности заключается в подсчете числа двоичных разрядов в каждой j-ой аппроксимирующей кодированной последовательности. Известные способы определения длины Lj каждой j-ой аппроксимирующей кодированной последовательности описаны, например, в книге: Б.А.Калабеков. "Микропроцессоры и их применение в системах передачи и обработки". - М.: Радио и связь, 1988, стр. 14. Известные способы сравнения длины Lj каждой j-ой аппроксимирующей кодированной последовательности с предварительно заданной предельно допустимой длиной Lпр описаны, например, в книге: У.Питерсон, Э.Уэлдон. "Коды, исправляющие ошибки". - М.: Мир, 1976, стр. 52.

Установление предварительно заданной предельно допустимой длины Lпр заключается в следующем. Предельно допустимую длину Lпр устанавливают не менее w+1 двоичных разрядов. При увеличении числа двоичных разрядов, равного предельно допустимой длины Lпр, погрешность сжатия кодируемой последовательности из символов упорядоченного m-ичного алфавита в кодированную последовательность двоичных символов уменьшается, что описано, например, в книге: К. Шеннон. "Работы по теории информации и кибернетике". - М.: Иностранная литература, 1963, стр. 618. Известные способы установления предварительно заданной предельно допустимой длины Lпр описаны, например, в книге: К.Шеннон. "Работы по теории информации и кибернетике". - М.: Иностранная литература, 1963, стр. 618.

Стирание j-ых аппроксимирующих кодируемых последовательностей, для которых длины Lj соответствующих им аппроксимирующих кодированных последовательностей превышают предельно допустимую длину Lпр, заключается в следующем. Для каждой j-ой

аппроксимирующей кодируемой последовательности сравнивается ее длина Lj с предельно допустимой длиной Lпр и если значение Lj превышает значение Lпр, j-ую аппроксимирующую кодируемую последовательность стирают. Известные способы стирания аппроксимирующих кодируемых последовательностей описаны, например, в книге: У.Питерсон, Э.Уэлдон. "Коды, исправляющие ошибки". - М.: Мир, 1976, стр. 17. Вид оставшихся аппроксимирующих кодируемых последовательностей представлен на фиг. 1(д).

Оставшиеся аппроксимирующие кодируемые последовательности сравнивают с кодируемой последовательностью. Известные способы сравнения оставшихся аппроксимирующих кодируемых последовательностей с кодируемой последовательностью описаны, например, в книге: У. Питерсон, Э.Уэлдон. " Коды, исправляющие ошибки". - М.: Мир, 1976, стр. 52. Для сравнения используют метрику Ли, в соответствии с которой для сравнения каждой j-ой аппроксимирующей кодируемой последовательности с кодируемой последовательностью из значения каждого очередного символа j-ой аппроксимирующей кодируемой последовательности вычитают значение очередного символа кодируемой последовательности и для каждой j-ой аппроксимирующей кодируемой последовательности абсолютные значения полученных разностей суммируют.

Из оставшихся аппроксимирующих кодируемых последовательностей выбирают наиболее близкую к кодируемой последовательности, соответствующую наименьшей сумме полученных разностей. Известные способы выбора минимального значения среди нескольких значений описаны, например, в книге: Д. Кнут. "Искусство программирования на ЭВМ". - М.: Мир, 1978, т. 3, стр. 219. Примерный вид выбранной аппроксимирующей кодируемой последовательности представлен на фиг. 1(е).

В качестве кодированной последовательности двоичных символов принимают аппроксимирующую кодированную последовательность, соответствующую выбранной аппроксимирующей кодируемой последовательности. Примерный вид принятой в качестве кодированной последовательности двоичных символов аппроксимирующей кодированной последовательности, соответствующей выбранной аппроксимирующей кодируемой последовательности, представлен на фиг. 1(ж). Алгоритм сжатия кодируемой последовательности из символов упорядоченного m-ичного алфавита в кодированную последовательность двоичных символов согласно заявляемого способа представлен на фиг. 2.

В аналитической форме данные действия можно записать следующим образом:

X = (x1, x2,...,xv,...,xk), v=1,2,...,k,

S = (s1, s2,...,si...,sm), i=1,2...,m,

Yj = (y1j, y2j,...,yvj,...,ykj), v=1,2,...,k, j=1,2,...,T, T≅ mk,

Zj = (z1j,z2j,...,zvj,...,zkj), v=1,2,...,k, j=1,2,...,T, T≅ mk,

Qj,i = nj,1 + nj,2 + ...+ nj,i-1,

Qj,m = nj,1 + nj,2 + ...+ nj,m-1,

Nj = nj,1 + nj,2 +...+ nj,m,

0.11≅2γ×Nj<1.1,

Zj* = argmin {d(X,Yj), j = 1,2,..., T}

при условии Lj ≅ Lпр,

где X - кодируемая последовательность, состоящая из k, где k ≥ 2, символов упорядоченного m-ичного алфавита,

S - упорядоченный m-ичный алфавит, состоящий из m, где m ≥ 2, символов,

Yj - j-я аппроксимирующая кодируемая последовательность, состоящая из k символов упорядоченного m-ичного алфавита,

Zj - j-я аппроксимирующая кодированная последовательность двоичных символов,

Qj,i - сумма двоичных чисел появлений символов j-ой аппроксимирующей кодируемой последовательности, предшествующих очередному символу j-ой аппроксимирующей кодируемой последовательности в упорядоченном m-ичном алфавите, в части j-ой аппроксимирующей кодируемой последовательности, предшествующей очередному символу j-ой аппроксимирующей кодируемой последовательности,

Qj,m - сумма двоичных чисел появлений символов j-ой аппроксимирующей кодируемой последовательности, предшествующих последнему символу в упорядоченном m-ичном алфавите, в части j-ой аппроксимирующей кодируемой последовательности, предшествующей очередному символу j-ой аппроксимирующей кодируемой последовательности,

Nj - двоичное число появлений всех символов упорядоченного m-ичного алфавита в части j-ой аппроксимирующей кодируемой последовательности, предшествующей очередному символу j-ой аппроксимирующей кодируемой последовательности,

γ - число разрядов, при котором значение последовательно сдвинутого в направлении старших разрядов двоичного числа Nj появлений всех символов упорядоченного m-ичного алфавита в части j-ой аппроксимирующей кодируемой последовательности, предшествующей очередному символу j-ой аппроксимирующей кодируемой последовательности, будет находиться в предопределенном диапазоне значений, - нормализованные значения статистических параметров очередного символа j-ой аппроксимирующей кодируемой последовательности,

- нормализованные значения статистических параметров очередного символа j-ой аппроксимирующей кодируемой последовательности,

Cj - j-oe двоичное значение нижней границы кодирования,

Aj - j-oe двоичное значение кодового интервала,

Zj* - принятая в качестве кодированной последовательности двоичных символов аппроксимирующая кодированная последовательность, соответствующая выбранной аппроксимирующей кодируемой последовательности.

Возможность уменьшения времени передачи кодированной последовательности двоичных символов по каналу связи или уменьшения требуемого объема устройств хранения кодированной последовательности двоичных символов в предлагаемом способе по сравнению с известным способом-прототипом можно показать следующим образом.

Рассмотрим сжатие кодируемой последовательности из символов упорядоченного троичного (m = 3) алфавита вида {1,2,3} в кодированную последовательность двоичных символов. Пусть требуется сжать кодируемую последовательность вида, например, X=1,3,3,2,1,2,#, состоящую из 6 символов упорядоченного троичного алфавита и символа # конца кодируемой последовательности. На фиг. 18 и 19 последовательно указываются значения параметров при сжатии данной кодируемой последовательности с использованием известного способа-прототипа при w = 4. В третьем столбце таблицы, представленной на фиг. 19, показаны последовательно считываемые в кодируемую последовательность неизменяемые части двоичного значения нижней границы кодирования, выделяемые при сжатии очередного символа данной кодируемой последовательности. Из полученных значений следует, что длина кодированной последовательности двоичных символов, сформированной из данной кодируемой последовательности при использовании известного способа-прототипа, равна 17 двоичных разрядов.