Изобретение относится к вычислительной технике и может найти применение в отказоустойчивых многопроцессорных системах для перераспределения нагрузки между процессорами.

Известно устройство, содержащее группу элементов памяти, дешифратор, блок перебора подстановок и элемент И-НЕ. Однако при больших количествах процессоров n и решаемых ими задач n значительно возрастает время определения допустимого распределения, т.к. количество всех возможных вариантов подстановок равно n! [1].

Наиболее близким по технической сущности к изобретению (прототипом) является устройство для перераспределения задач между процессорами, содержащее блок элементов памяти, дешифратор, блок сдвигов кодов задач, блок счетчиков циклов и элемент И-НЕ.

Однако это устройство характеризуется большим временем определения допустимой подстановки [2].

Действительно, при определенном варианте текущего состояния вычислительной системы (ВС), содержащей n процессоров, каждый из которых способен выполнять одну из n задач, блок сдвигов кодов задач должен сформировать все n! возможные подстановки, что при больших n характеризуется значительными временными затратами.

Технической задачей изобретения является сокращение времени поиска допустимого перераспределения задач путем соответствующего анализа текущего состояния ВС.

Текущее состояние ВС определяется матрицей текущего состояния [ϕij], элемент которой ϕij = 1, если i-ый процессор способен выполнять j-ую задачу, и ϕij = 0 в противном случае. Указанная техническая задача решается благодаря ускоренному определению ненулевого диагонального произведения матрицы текущего состояния, заключающегося в следующем. В матрице определяются i-ая строка и j-ый столбец, содержащие наибольшее количество нулей, причем элемент, находящийся на пересечении их, должен иметь ненулевое значение. После этого i-ому процессору назначается для выполнения j-ая задача. Далее найденные строка и столбец исключаются из матрицы и те же операции выполняются над матрицей размерностью (n-1)•(n-1). В результате каждого последующего шага очередному процессору назначается для выполнения следующая задача. Если в процессе перебора подматриц одна из них окажется нулевой, то возможного варианта распределения задач не существует, что соответствует отказу всей ВС. Таким образом, последовательный переход от матрицы размерностью n•n до матрицы размерностью 1•1 определяет возможный вариант перераспределения n задач между n процессорами. Очевидно, что для этого потребуется n•n•n=n3 шагов вместо n!, реализуемых прототипом. Начиная с n=6, временные затраты на поиск допустимого перераспределения устройством, реализующим представленный метод, значительно сокращаются по сравнению с прототипом: 63 = 216 < 6! = 720 [3].

Для решения указанной технической задачи в устройство для перераспределения задач между процессорами, содержащее блок элементов памяти и первый дешифратор, причем первая группа входов устройства является группой входов первого дешифратора, группа из n выходов которого соединена с первой группой из n входов блока элементов памяти, введены второй дешифратор, блок считывания и записи, блок определения подстановки и блок хранения кодов задач, причем вторая группа входов устройства является группой входов второго дешифратора, группа из n выходов которого соединена со второй группой из n входов блока элементов памяти, первая группа из n выходов которого соединена с первой группой входов, вторая группа из n выходов - со второй группой входов и третья группа из двух выходов - с третьей группой входов блока определения подстановки, первый выход которого соединен с первым входом, второй выход - со вторым входом блока считывания и записи и является первым выходом устройства, а первая группа из n выходов блока считывания и записи соединена с третьей группой входов, вторая группа из n выходов - с четвертой группой входов блока элементов памяти, третья и четвертая группа из m (где m= ] log2n[) выходов блока считывания и записи соединена соответственно с первой и второй группой входов блока хранения кодов задач, группа из n m-разрядных выходов которого является вторым выходом устройства, второй выход соединен с третьим входом блока считывания и записи, третья группа из m входов соединена с группой входов второго дешифратора, а четвертая группа из n входов - с группой соответствующих выходов первого дешифратора.

Введение в состав предлагаемого устройства упомянутых блоков и организация их связей с упомянутой совокупностью являются существенным признаком, т.к. позволяют сократить время поиска допустимого перераспределения задач по сравнению с прототипом.

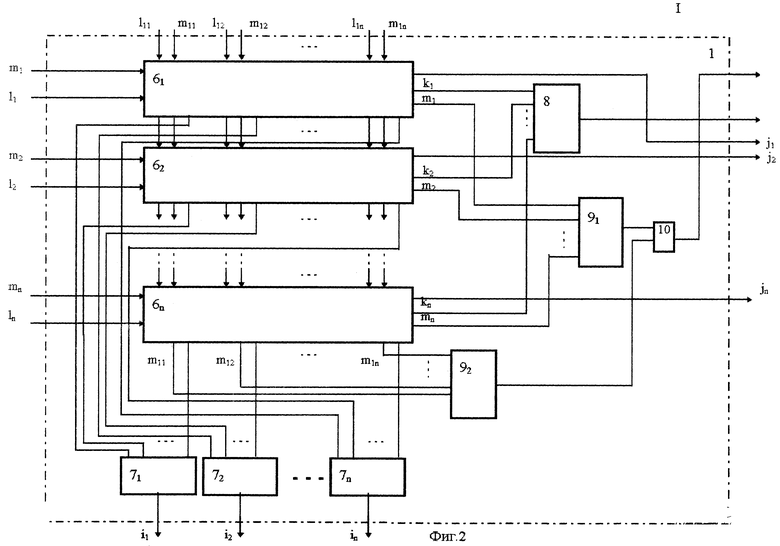

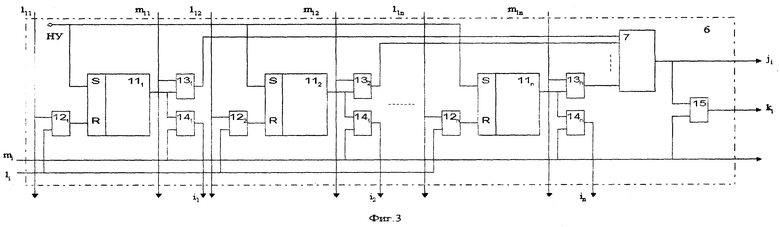

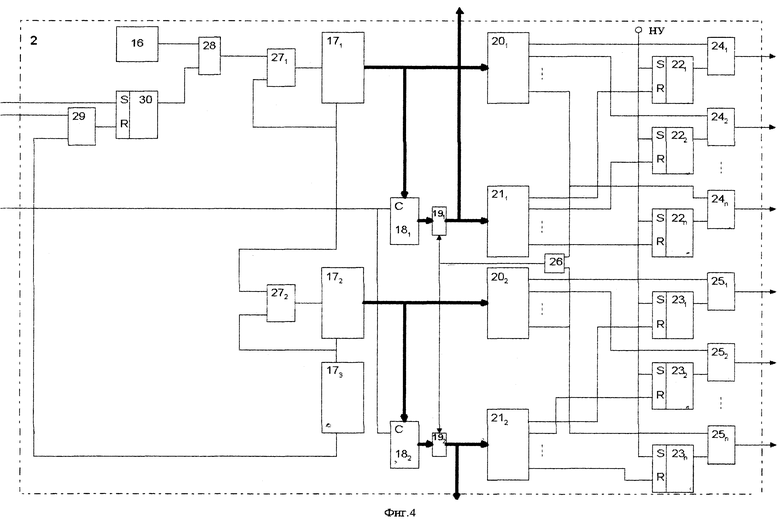

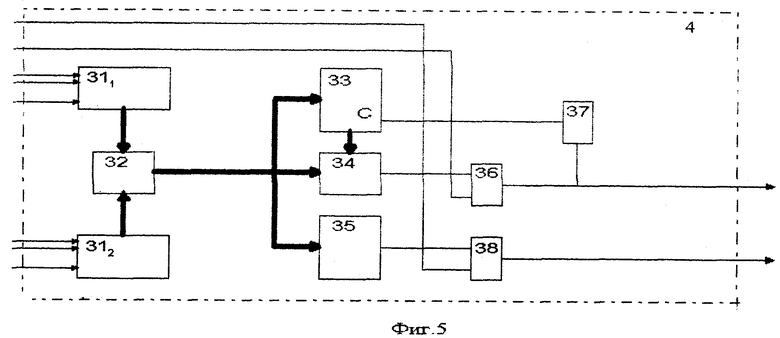

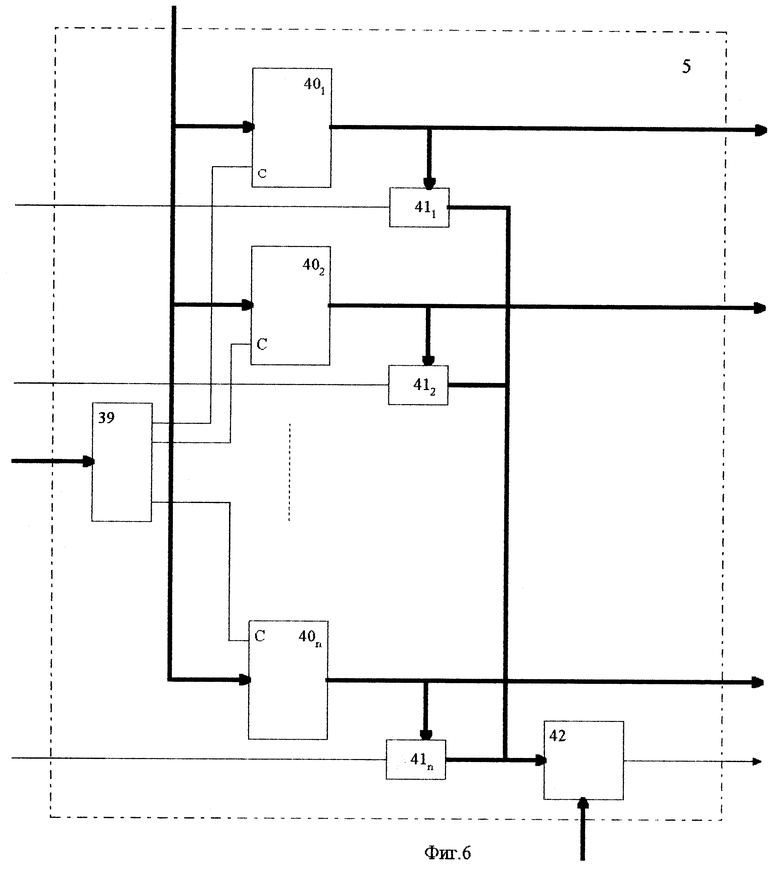

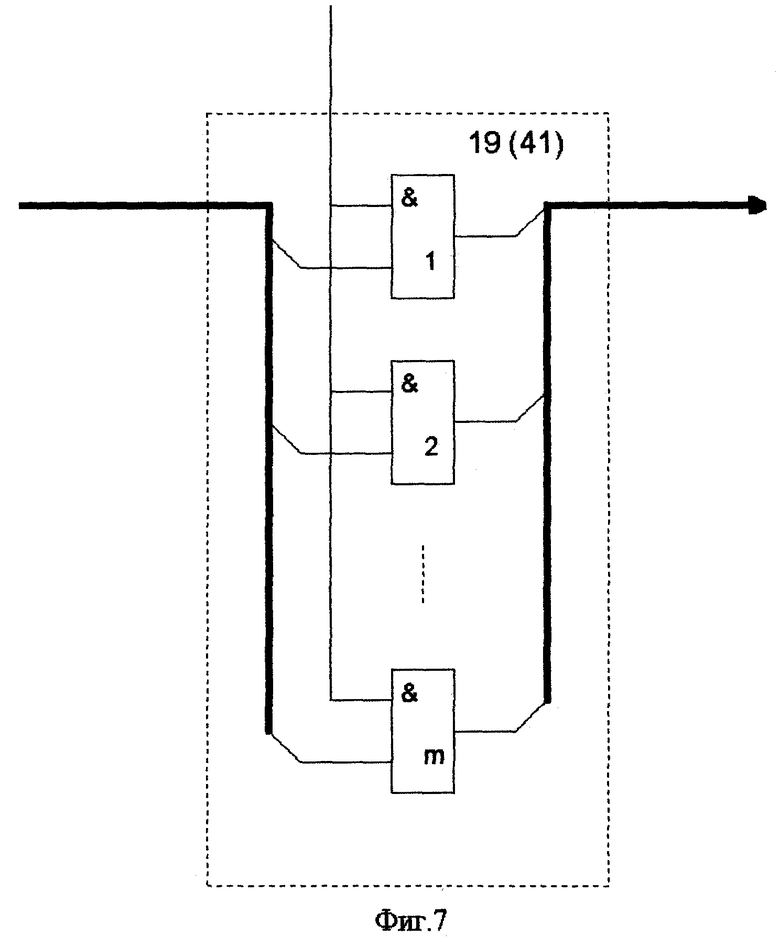

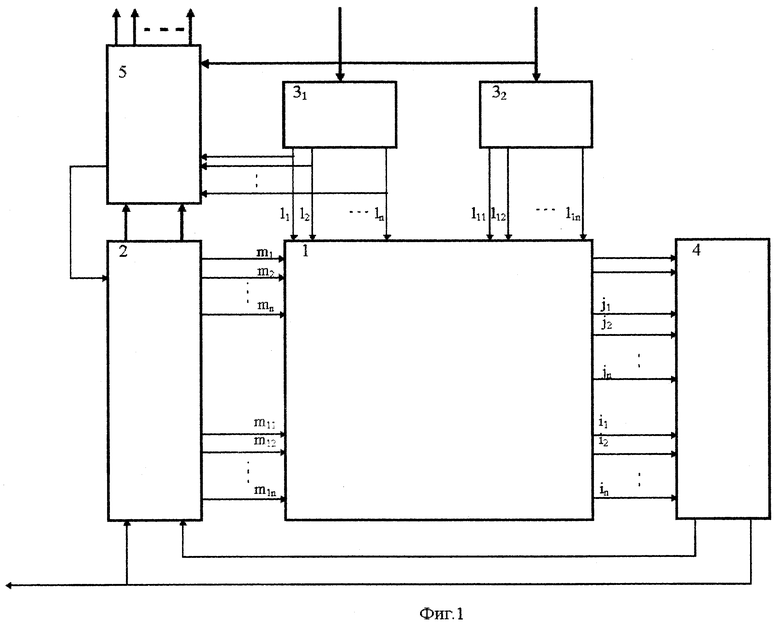

На фиг. 1 приведена структурная схема устройства, на фиг.2 - вариант реализации блока элементов памяти, на фиг. 3 - вариант реализации элемента памяти, на фиг.4 - вариант реализации блока считывания и записи, на фиг.5 - вариант реализации блока определения подстановки, на фиг.6 - вариант реализации блока хранения кодов задач, на фиг. 7 - вариант реализации группы двухвходовых элементов И.

Устройство для перераспределения задач между процессорами содержит (см. фиг. 1) блок элементов памяти 1, блок считывания и записи 2, два дешифратора 31, 32, блок определения подстановки 4, блок хранения кодов задач 5.

Блок элементов памяти 1 (см. фиг. 2) содержит группу элементов памяти 61. ..6n, группу n-входовых элементов ИЛИ 71...7n, n-входовой элемент ИЛИ 8, два n-входовых элемента ИЛИ 91, 92, двухвходовой элемент И 10.

Элемент памяти 6 (см. фиг. 3) содержит группу триггеров 111 ...11n, группу двухвходовых элементов И 121...12n, группу двухвходовых элементов И 131...13n, группу двухвходовых элементов И 141...14n, двухвходовой элемент И 15, n-входовой элемент ИЛИ 7.

Блок считывания и записи 2 (см.фиг.4) содержит генератор импульсов 16, группу m-разрядных счетчиков 171...173, два m-разрядных регистра 181, 182, две группы двухвходовых элементов И по m элементов в каждой 191, 192, два m-разрядных дешифратора 201, 202, два m-разрядных дешифратора 211, 212, две группы триггеров 221...22n и 231...23n, две группы двухвходовых элементов И 241. ..24n и 251...25n, двухвходовой элемент И 26, два двухвходовых элемента ИЛИ 271, 272, двухвходовой элемент И 28, двухвходовой элемент ИЛИ 29, триггер 30.

Блок определения подстановки 4 (см. фиг. 5) содержит два m-разрядных шифратора 311, 311, m-разрядный умножитель 32, 2m-разрядный регистр 33, схему сравнения 34, 2m-входовой элемент ИЛИ 35, двухвходовой элемент И 36, линию задержки 37, двухвходовой элемент И 38.

Блок хранения кодов задач 5 (см. фиг.6) содержит m-разрядный дешифратор 39, группу m-разрядных регистров 401...40n, n групп двухвходовых элементов И по m элементов в каждой 411...41n, схему сравнения 42.

Группа двухвходовых элементов И 19 (41) (см.фиг.7) содержит m двухвходовых элементов И.

Совокупность введенных элементов может быть выполнена на микросхемах любой серии, имеющей в своем составе логические элементы: счетчики, регистры, дешифраторы и т.д. (например, ИМС серий 133, 155, 106, 500 и пр.).

Устройство работает следующим образом. В блок элементов памяти 1 заносится матрица текущего состояния [ϕij], в n регистрах блока хранения кодов задач 5 хранятся коды задач, на выполнение которых настроен каждый из процессоров, в блок определения подстановки 4 заносится число, равное максимально возможному произведению количества единиц в строке и столбце: n•n=n2. При потере i-ым процессором способности выполнять j-ую задачу дешифрированные коды номера задачи и номера отказавшего процессора поступают на входы блока элементов памяти 1 и изменяют матрицу текущего состояния. Одновременно код номера задачи в блоке хранения кодов задач 5 сравнивается с кодом настройки отказавшего процессора и, если они равны, блок хранения кодов задач 5 запускает блок считывания и записи 2 для поиска допустимого перераспределения задач. Блок считывания и записи 2 попарно считывает в блок определения подстановки 4 по одной строке и по одному столбцу матрицы текущего состояния, начиная с 1-ой строки и 1-го столбца и заканчивая n-ой строкой и n-ым столбцом. Блок определения подстановки 4 вычисляет произведение количества единиц в текущих строке и столбце, сравнивает его с содержимым регистра 33, где первоначально хранится число n2. Если число n2 больше текущего произведения, а также на пересечении текущих строки и столбца находится "1", то блок определения подстановки 4 выдает в блок считывания и записи 2 сигнал на сохранение текущих номеров строки и столбца. Одновременно в регистр 33 записывается текущее произведение единиц, с которым проводится сравнение на следующем цикле выбора строки и столбца. Таким образом, после выбора последних строки и столбца в регистрах 181, 182 блока считывания и записи 2 будут храниться номера строки и столбца, содержащие наименьшее количество единиц и на пересечении которых находится ненулевой элемент, местоположение которого в матрице (порядковые номера строки - i и столбца - j) задает настройку i-го процессора на выполнение j-ой задачи. После каждых n•n = n2 шагов код задачи - j заносится в регистр 40i блока хранения кодов задач 5. Одновременно i-ая строка и j-ый столбец исключаются ("вычеркиваются") из матрицы состояния ВС путем установки триггеров 22i и 23j блока считывания и записи 2 в "0" состояние.

После n3 шагов все процессоры будут настроены на выполнение соответствующих задач, если допустимое распределение существует. Если на каком-либо шаге будет считана нулевая строка и (или) столбец (не считая уже исключенных), то блок определения подстановки 4 выдает сигнал об отказе всей ВС и останавливает блок считывания и записи 2, т.к. в этом случае возможного варианта перераспределения задач не существует.

При исправной ВС все триггеры 11 блока элементов памяти 1 находятся в единичном состоянии, т. е. каждый процессор способен выполнять любую из n задач. Запись "0" в ячейку элемента памяти 6 (см.фиг.3) происходит при потере i-ым процессором способности выполнять j-ую задачу. При этом "0" устанавливается на выходе триггера 11j элемента памяти 6i. Одновременно код j-ой задачи подается на вход схемы сравнения (СС) 42 (см.фиг.6) и открывается группа двухвходовых элементов И 41i блока хранения кодов задач 5. Если код j-ой задачи соответствует текущей настройке i-го процессора, то на выходе СС 42 установится "1", которая установит Тг 30 блока считывания и записи 2 в единичное состояние (см. фиг.4), чем откроет ключ И 28 генератора импульсов 16. Импульсы генератора начинают поступать на счетный вход m-разрядного счетчика 171. Выход переполнения счетчика 171 соединен через двухвходовой элемент ИЛИ 272 со счетным входом аналогичного счетчика 172, в свою очередь, выход переполнения счетчика 172 соединен со счетным входом аналогичного счетчика 173. Соединенные таким образом счетчики 171...173 образуют 3m-разрядный счетчик или счетчик до n3 (m=]log2n[). Обратная связь выхода переполнения счетчиков 171, 172 со счетным входом через элементы ИЛИ 271, 272 введена для пропуска нулевого состояния каждого счетчика после каждых n шагов.

Счетчики 171 и 172 соединены информационными выходами с входами дешифраторов 201 и 202. Каждый i-ый выход дешифратора 201 через ключ 24i соединен с шиной mi блока элементов памяти 1 (см.фиг.2), аналогично каждый i-ый выход дешифратора 202 через ключ 25i соединен с шиной m1i. Последовательное возбуждение выходов дешифраторов 201 и 202 позволяет последовательно перебирать элементы памяти 6 (строки матрицы текущего состояния - дешифратором 201) и одноименные триггеры 11 одновременно всех элементов памяти 6 (столбцы матрицы текущего состояния - дешифратором 202). Причем в каждый момент времени выбраны одна строка и один столбец. Элементы строки образуются на выходах элементов И 141...14n выбранного элемента памяти 6, элементы столбца образуются на выходах одноименных элементов И 13 всех элементов памяти 61...6n. n-входовые элементы ИЛИ 7 необходимы для развязки выходов элементов И 13 и И 14.

Блок определения подстановки 4 работает следующим образом (см.фиг.5). В регистре 33 первоначально хранится число n2. На вход шифратора 311 поступает n-разрядный код, каждый разряд которого соответствует состоянию одного элемента выбранной строки матрицы состояния, аналогично, на вход шифратора 312 поступают элементы выбранного столбца. С выходов шифраторов 311, 312 на входы умножителя 32 поступают суммы единиц в выбранных строке и столбце соответственно. С выхода умножителя 32 произведение количества единиц в строке и столбце поступает на СС 34, где сравнивается с содержимым регистра 33 (первоначально с числом n2). СС 34 выдает сигнал на первый вход двухвходового элемента И 36, если содержимое регистра 33 больше поступающего произведения. На второй вход элемента И 36 из блока элементов памяти 1 поступает сигнал о том, что на пересечении выбранной строки и выбранного столбца находится "1". При наличии двух этих сигналов "1" с выхода элемента И 36 через линию задержки (ЛЗ) 37 поступает на вход разрешения записи регистра 33, куда записывается новое произведение единиц в выбранных строке и столбце. Одновременно в блок считывания и записи 2 выдается сигнал на запоминание номеров этой строки и этого столбца. Произведение единиц поступает также на входы элемента ИЛИ-НЕ 35, сигнал на выходе которого появляется, если произведение равно нулю, т.е. выбрана нулевая строка и(или) нулевой столбец. Выход элемента ИЛИ-НЕ 35 связан с первым входом двухвходового элемента И 38. "1" на второй вход элемента И 38 поступает из блока элементов памяти 1, если выбранная строка и столбец "не вычеркнуты". При наличии двух этих сигналов с выхода элемента И 38 поступает сигнал на остановку блока считывания и записи 2 и донесение "Отказ ВС", т.к. допустимого перераспределения задач между процессорами не существует.

По каждому сигналу из блока определения подстановки 4 код номера строки и код номера столбца записываются в регистры 181, 182 блока считывания и записи 2 (см. фиг. 4). Таким образом, через n2 шагов в регистрах 181, 182 будут храниться коды i-ой строки и j-го столбца, содержащих наименьшее количество единиц, что и определяет новую настройку i-ого процессора - ему предписывается выполнять j-ую задачу. Через n2 шагов сигнал с выхода элемента И 26 открывает группы двухвходовых элементов И 191, 192 и хранящиеся в регистрах 181, 182 коды поступают на запись в блок хранения кодов задач 5 и на входы соответствующего дешифратора 211, 212. Возбужденный i-ый выход дешифратора 211 установит Тг 22i в "0" состояние, закроется ключ 24i и шина mi блока элементов памяти 1 установится в "0" состояние. В следующем цикле работы блока считывания и записи 2, когда будет выбрана шина mi (i-ая строка), ее содержимое не будет передано в блок определения подстановки 4, т.к. нулевое состояние шины mi закроет все элементы И 141...14n (см.фиг.3). Другими словами, i-ая строка будет "вычеркнута" из матрицы текущего состояния. Аналогичным образом будет "вычеркнут" j-ый столбец.

Новый вариант распределения задач в виде пар чисел (номер процессора и номер задачи) через каждые n2 шагов последовательно записывается в блок хранения кодов задач 5 (см.фиг.6). Код номера строки (номер процессора) из блока считывания и записи 2 поступает на вход дешифратора 39, код номера столбца (номер задачи) поступает параллельно на входы всех регистров 401... 40n. Дешифратор 39 дает разрешение на запись кода задачи только тому регистру, номер которого соответствует поступившему номеру процессора. Очевидно, через n3 шагов во всех регистрах 401...40n будет храниться новая настройка ВС, если это возможно.

Элемент памяти 6 работает следующим образом (см.фиг.3). При исправном состоянии ВС все процессоры способны выполнять любую из n задач, поэтому все триггеры 111. ..11n установлены в единичное состояние. При потере i-ым процессором способности выполнять j-ую задачу на шинах li и l1j появляются логические единицы, которые поступают на первый и второй входы двухвходового элемента И 12i, находящегося на пересечении этих шин. "1" на выходе элемента И 12i установит триггер 11i в нулевое состояние.

При считывании состояний триггеров 11 блок считывания и записи 2 последовательно возбуждает шины mi и m1j блока элементов памяти 1. Содержимое строки, возбужденной шиной mi, образуется на выходах i1, i2,...in, содержимое столбца, возбужденного шиной m1j, образуется на выходах j1, j2,...jn (см. фиг.2). n-входовые элементы ИЛИ 71...7n необходимы для развязки выходов элементов И 13, 14. "1" на выходе ki элемента памяти 6 свидетельствует, что на пересечении выбранной строки и выбранного столбца находится ненулевой элемент матрицы текущего состояния: "1" на первом входе двухвходового элемента И 15 появляется при возбуждении шины mi (выборе строки), "1" на втором входе появляется, если Тг 11j, возбужденный шиной m1j, (при выборе столбца) находится в "1" состоянии. Выходы ki всех элементов памяти 6 объединяются n-входовым элементом ИЛИ 8. Шины m1, m2,...,mn объединяются элементом ИЛИ 91, шины m11, m12,..., m1n объединяются элементом ИЛИ 92. "1" на выходе элемента И 10 сигнализирует о том, что в данный момент шины mi и m1j находятся в возбужденном состоянии, т. е. i-ая строка и j-ый столбец не вычеркнуты из матрицы состояния.

Остановка блока считывания и записи 2 (см.фиг.4) происходит через n3 шагов, если существует возможный вариант перераспределения задач. При этом "1" с разряда переполнения счетчика 173 через элемент ИЛИ 29 устанавливает Тг 30 в "0" состояние, ключ И 28 закрывается и препятствует прохождению импульсов с генератора 16. Если возможного варианта перераспределения не существует, сигнал на другой вход элемента ИЛИ 29 поступает из блока определения подстановки 4.

Технико-экономическая эффективность предлагаемого устройства заключается в сокращении времени поиска варианта перераспределения задач между процессорами. Возможен такой случай отказов процессоров, когда прототипу для поиска перераспределения потребуется перебор всех n! возможных вариантов. В предлагаемом устройстве при любых отказах потребуется только n3 шагов, а если такого варианта не существует, устройство останавливается и выдает донесение "Отказ ВС" немедленно, как только в матрице состояния будет обнаружена нулевая подматрица. При достаточно больших значениях n (n ≥ 6) выигрыш во времени по сравнению с прототипом оказывается существенным.

Данное устройство может найти применение при проектировании отказоустойчивых вычислительных систем, в которых восстановление работоспособности после отказа достигается перераспределением функций, возложенных на процессоры.

ЛИТЕРАТУРА

1. Авторское свидетельство СССР 982005, G 06 F 9/46, 1989 г.

2. Авторское свидетельство РФ 2023292, G 06 F 9/46, 1994 г.

3. Справочник по математике для научных работников и инженеров. Корн Г., Корн Т. - М. : Наука. Главная редакция физико-математической литературы, 1984.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ОБРАБОТКИ ДАННЫХ | 1994 |

|

RU2129731C1 |

| УСТРОЙСТВО БЕСШНУРОВОЙ КРОССОВОЙ КОММУТАЦИИ КАНАЛОВ | 2001 |

|

RU2214067C2 |

| УСТРОЙСТВО ДЛЯ ВЫБОРА ОПТИМАЛЬНЫХ РЕШЕНИЙ | 1998 |

|

RU2150144C1 |

| УСТРОЙСТВО ДЛЯ ВЫБОРА ОПТИМАЛЬНЫХ РЕШЕНИЙ МЕТОДОМ МАКСИМАЛЬНЫХ РАССТОЯНИЙ | 1999 |

|

RU2158957C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ОБУЧЕНИЕМ И ОЦЕНИВАНИЕМ ЗНАНИЙ ОБУЧАЮЩИХСЯ В СИСТЕМЕ ДИСТАНЦИОННОГО ОБУЧЕНИЯ | 2011 |

|

RU2467388C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕРАСПРЕДЕЛЕНИЯ ЗАДАЧ МЕЖДУ ПРОЦЕССОРАМИ | 1991 |

|

RU2023292C1 |

| УСТРОЙСТВО ДЛЯ ЗАДЕРЖКИ СИГНАЛОВ | 1992 |

|

RU2024186C1 |

| УСТРОЙСТВО ДЛЯ ВЫБОРА ОПТИМАЛЬНЫХ РЕШЕНИЙ | 2002 |

|

RU2262133C2 |

| УСТРОЙСТВО ДЛЯ ВЫБОРА ОПТИМАЛЬНЫХ РЕШЕНИЙ | 2002 |

|

RU2234733C1 |

| УСТРОЙСТВО ОПЕРАТИВНОЙ ТЕЛЕФОННОЙ СВЯЗИ | 2000 |

|

RU2197071C2 |

Изобретение относится к вычислительной технике и может найти применение в отказоустойчивых многопроцессорных системах для перераспределения нагрузки между процессорами во время отказов. Технической задачей изобретения является сокращение времени поиска допустимого перераспределения задач путем анализа текущего состояния вычислительной системы. Указанная техническая задача решается за счет того, что устройство содержит блок элементов памяти, два дешифратора, блок считывания и записи, блок определения подстановки и блок хранения кодов задач. 1 з.п.ф-лы, 7 ил.

| УСТРОЙСТВО ДЛЯ ПЕРЕРАСПРЕДЕЛЕНИЯ ЗАДАЧ МЕЖДУ ПРОЦЕССОРАМИ | 1991 |

|

RU2023292C1 |

| Устройство для распределения задач между процессорами | 1981 |

|

SU982005A1 |

| Устройство для распределения заданий процессорам | 1985 |

|

SU1317438A1 |

| Устройство для распределения задач процессорам | 1987 |

|

SU1425671A1 |

Авторы

Даты

2000-07-27—Публикация

1999-01-21—Подача