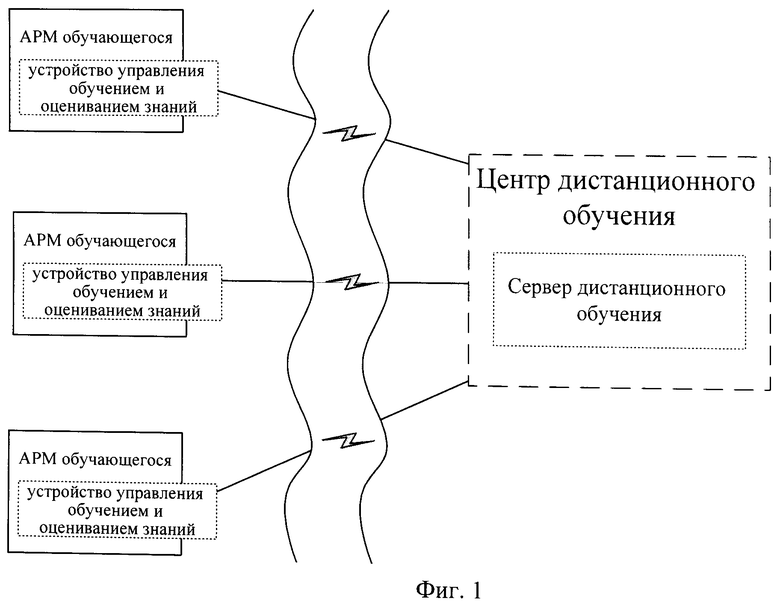

Изобретение относится к вычислительной технике, в частности к устройствам управления обучением и оцениванием знаний обучающихся, и может быть использовано в системах дистанционного обучения (фиг.1) в условиях значительной удаленности обучающихся от места размещения сервера дистанционного обучения, когда взаимодействие с сервером осуществляется по каналам передачи данных, не обеспечивающих непрерывное устойчивое соединение АРМ обучающихся с сервером в течение всего времени прохождения теста (обучения) или не обеспечивающих требуемую пропускную способность в условиях значительного объема мультимедийной информации, необходимой для отображения на экране АРМ обучающегося содержания очередного тестового задания или учебной информации.

Известно устройство для управления предъявлением информации в системе дистанционного обучения (см. Авт.св. РФ №2248605, кл. G06F 3/153, 2005), состоящее из трех регистров, блока памяти, двух групп элементов И, группы элементов ИЛИ, трех элементов задержки, триггера, двух элементов И, двух элементов ИЛИ, счетчика, компаратора и селектора базового адреса, в состав которого входит два элемента задержки, дешифратор, две группы элементов И, постоянное запоминающее устройство и регистр.

Первый аналог позволяет обеспечить сокращение временных затрат на поиск и формирование наборов данных, которые должны быть предъявлены обучающемуся в системе дистанционного обучения.

Недостатком первого аналога является узкая область применения, ограниченная возможностью использования устройства только для обучения путем изучения обучающимся предъявляемого ему материала, отсутствие возможности проверки качества подготовки обучающегося как в режиме самоконтроля, так и в режиме тестирования.

Известно устройство для экспертной оценки экстремальных ситуаций в системе дистанционного обучения (см. авт.св. РФ №2246758, кл. G06F 19/00, 2005), состоящее из трех регистров, дешифратора, двух групп элементов И, постоянного запоминающего устройства, четырех элементов задержки, блока памяти, триггера, двух компараторов, трех элементов И, элемента ИЛИ, счетчика и блока ввода признаков, в состав которого входит четыре элемента И, группа триггеров, элемент задержки и регистр.

Второй аналог позволяет реализовать дистанционное обучение путем предъявления обучающемуся заданий (входных ситуаций) и сравнения его ответов с эталонными, обеспечивает возможность проведения самоконтроля обучающимся, позволяет вести централизованный учет сигналов об ошибках обучающегося, а также обеспечивает повышение производительности системы дистанционного обучения за счет сокращения временных затрат на выявление и исправление ошибок, допущенных в описании тестов (входных ситуаций).

Недостатком второго аналога является отсутствие возможности формирования итоговой оценки по результатам обучения, обеспечивающей определение степени достижения целей обучения.

Наиболее близким аналогом (прототипом) по своей технической сущности заявленному устройству является устройство для управления получением оценки качества знаний в системе дистанционного обучения (см. авт.св. РФ №2248610, кл. G06F 19/00, 2005), состоящее из трех регистров, двух компараторов, двух счетчиков, сумматора, дешифратора, двух триггеров, блока памяти, трех элементов ИЛИ, семи элементов И, двух групп элементов И, пяти элементов задержки и определителя опорного адреса теста, в состав которого входит дешифратор, группа элементов И, постоянное запоминающее устройство, регистр и два элемента задержки.

Такая схема позволяет, по сравнению с устройствами-аналогами, обеспечить возможность оценивания знаний обучающегося в системе дистанционного обучения, как в интересах реализации самоконтроля обучающимся, так и для централизованного учета результатов обучения. Однако устройство-прототип имеет недостатки, а именно:

1. Относительно низкую достоверность оценки знаний обучающихся, обусловленную отсутствием возможности учета при формировании оценки относительных весовых коэффициентов заданий из состава теста, имеющих различный уровень сложности [1].

2. Узкую область применения, ограниченную возможностью применения только для оценивания знаний обучающихся посредством гомогенных тестов [3], тестов, основанных на содержании какой-либо одной дисциплины, так как устройство-прототип не позволяет произвести учет относительных весовых коэффициентов заданий, входящих в состав тестов [2]. В то же время на практике часто возникает необходимость в применении гетерогенных тестов, тестов, основанных на содержании нескольких дисциплин, позволяющих получить комплексную оценку знаний обучающихся одновременно по результатам изучения нескольких дисциплин [2, 3]. Вследствие перехода вузов на федеральные государственные образовательные стандарты нового (третьего) поколения, ориентированные на компетентностный подход в обучении [4], возникает необходимость применения гетерогенных тестов, так как они позволяют оценить степень сформированности компетенций при проведении промежуточного контроля обучающихся по результатам изучения профессиональных модулей (междисциплинарных курсов) или при проведении итогового контроля выпускников.

Целью изобретения является разработка устройства оценивания знаний обучающихся, обеспечивающего расширение области его применения и повышение достоверности оценки знаний обучающихся за счет дифференциации заданий теста путем сопоставления с каждым из них соответствующего относительного весового коэффициента и учета указанных коэффициентов при формировании итоговой оценки по результатам тестирования.

Поставленная цель достигается тем, что в устройство, содержащее первый и второй регистры, первый, второй и третий элементы ИЛИ, первый, второй, третий, четвертый и пятый элементы задержки, первый блок памяти, первый и второй компараторы, первый, второй, третий, четвертый, пятый, шестой и седьмой элементы И, счетчик, первый сумматор, первый и второй триггеры, группу трехвходовых элементов И, вторую группу двухвходовых элементов И, дешифратор, блок определения опорного адреса теста (БООАТ), управляющий вход которого является первым управляющим входом устройства, s-й разряд, где s=1, 2, …, 5, L-разрядного выхода "Опорный адрес теста" БООАТ, где L=S+R, причем R - количество разрядов, достаточное для представления кода, соответствующего максимальному количеству тестовых заданий в любом из тестов, соединен с s-м разрядом первого L-разрядного информационного входа первого сумматора, j-й разряд, где j=(L-R)+1, (L-R)+2, …, L, L-разрядного выхода "Опорный адрес теста" БООАТ соединен с j-м разрядом первого L-разрядного информационного входа первого компаратора, синхронизирующий выход БООАТ соединен с первым входом первого элемента ИЛИ, выход которого соединен с входом первого элемента задержки, прямой выход первого компаратора соединен с первым входом второго элемента И, инверсный выход первого компаратора соединен с первым входом первого элемента И, выход которого соединен с счетным входом счетчика и вторым входом первого элемента ИЛИ, выход второго элемента И соединен с входом сброса счетчика, входом сброса первого сумматора, вторым входом третьего элемента ИЛИ и вторыми входами двухвходовых элементов И второй группы двухвходовых элементов И и является выходом "Конец теста" устройства, выход первого элемента задержки соединен с входом второго элемента задержки и управляющим входом первого сумматора, выход второго элемента задержки соединен с управляющим входом первого блока памяти и входом третьего элемента задержки, выход которого соединен с вторым входом второго элемента И и управляющим входом первого регистра, d-й разряд Q-разрядного выхода первого блока памяти, где d=1, 2, …, D, является d-м разрядом D-разрядного выхода "Тест" устройства, где D - количество разрядов, достаточное для хранения кода, соответствующего содержанию любого из тестовых заданий и возможных вариантов ответа на него, Q=D+N, где N - количество разрядов, достаточное для представления кода, соответствующего максимальному количеству вариантов ответов в любом из тестовых заданий, i - разряд Q-разрядного выхода первого блока памяти, где i=(Q-N)+1, (Q-N)+2, …, Q, соединен с n-м разрядом N-разрядного информационного входа первого регистра, где n=1, 2, …, N, L-разрядный адресный вход первого блока памяти соединен с L-разрядным выходом первого сумматора, L-разрядный выход счетчика соединен с вторым L-разрядным информационным входом первого сумматора и с вторым L-разрядным входом первого компаратора, n-й разряд N-разрядного выхода первого регистра соединен с первым входом n-го трехвходового элемента И группы трехвходовых элементов И и соответствующим разрядом первого N-разрядного входа второго компаратора, прямой выход которого соединен с первым входом третьего элемента И, а его инверсный выход соединен с первым входом четвертого элемента И, выход которого соединен с первым входом шестого элемента И, управляющим входом первого триггера и вторым входом седьмого элемента И, выход которого соединен с вторым входом второго элемента ИЛИ, выход которого соединен с вторым входом первого элемента И, выход третьего элемента И соединен с первым входом второго элемента ИЛИ и первым входом пятого элемента И, выход которого является выходом "Верный ответ" устройства, N-разрядный информационный вход второго регистра является N-разрядным входом "Код ответа" устройства, а его разряд N-разрядный выход соединен с вторым N-разрядным входом второго компаратора, управляющий вход второго регистра соединен с входом четвертого элемента задержки и является вторым управляющим входом устройства, выход четвертого элемента задержки соединен с управляющим входом второго компаратора и входом пятого элемента задержки, выход которого соединен с вторым входом третьего элемента И и вторым входом четвертого элемента И, вторые входы трехвходовых элементов И группы трехвходовых элементов И соединены с прямым выходом первого триггера, вход сброса которого является третьим управляющим входом устройства, управляющий вход второго триггера и первый вход третьего элемента ИЛИ являются соответственно первым и вторым входами "Выбор режима" устройства, выход третьего элемента ИЛИ соединен с входом сброса второго триггера, инверсный выход которого соединен с первым входом седьмого элемента И, а его прямой выход соединен с третьими входами трехвходовых элементов И группы трехвходовых элементов И, вторым входом пятого элемента И и вторым входом шестого элемента И, выход которого является выходом "Ошибка" устройства, выход n-го трехвходового элемента И группы трехвходовых элементов И является n-м разрядом N-разрядного выхода "Код правильного ответа" устройства, k-й разряд, где k=1, 2, …, K, K-разрядного выхода дешифратора, где K - количество баллов, используемое для оценивания знаний обучающихся, соединен с первым входом k-го двухвходового элемента И второй группы двухвходовых элементов И, выход k-го двухвходового элемента И второй группы двухвходовых элементов И является k-м разрядом K-разрядного выхода "Оценка" устройства, дополнительно введены второй блок памяти, второй сумматор, шестой элемент задержки, первая группа двухвходовых элементов И и третий регистр, M-разрядный выход которого, где М=log2K - количество разрядов, достаточное для представления максимально возможной суммы весов ответов при прохождении теста, соединен с M-разрядным входом дешифратора и первым M-разрядным информационным входом второго сумматора, M-разрядный выход которого соединен с M-разрядным информационным входом третьего регистра, управляющий вход третьего регистра соединен с выходом шестого элемента задержки, вход которого соединен с управляющим входом второго сумматора и выходом четвертого элемента И, управляющий вход второго блока памяти соединен с выходом второго элемента задержки, L-разрядный адресный вход второго блока памяти соединен с L-разрядным выходом первого сумматора, m-й разряд M-разрядного выхода второго блока памяти, где m=1, 2, …, M, соединен с первым входом m-го двухвходового элемента И первой группы двухвходовых элементов И и m-м разрядом второго M-разрядного информационного входа второго сумматора, вторые входы двухвходовых элементов И первой группы двухвходовых элементов И объединены между собой и соединены с прямым выходом второго триггера, выход m-го двухвходового элемента И первой группы двухвходовых элементов И является m-м разрядом M-разрядного выхода "Вес ответа" устройства, вход сброса третьего регистра и вход сброса второго сумматора соединены с выходом второго элемента И, а V - разрядный вход "Номер теста" БООАТ является V-разрядным входом "Номер теста" устройства, где V - количество разрядов, достаточное для представления кода, соответствующего максимальному количеству тестов, предусмотренных для оценивания знаний обучающегося.

Изобретение поясняется чертежами, на которых показаны:

на фиг.1 - фрагмент структуры организации системы дистанционного обучения,

на фиг.2 - структурная схема устройства,

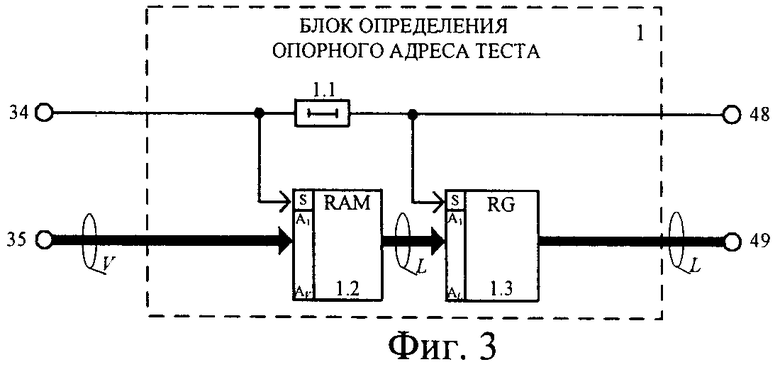

на фиг.3 - пример конкретного конструктивного выполнения блока определения опорного адреса теста (БООАТ),

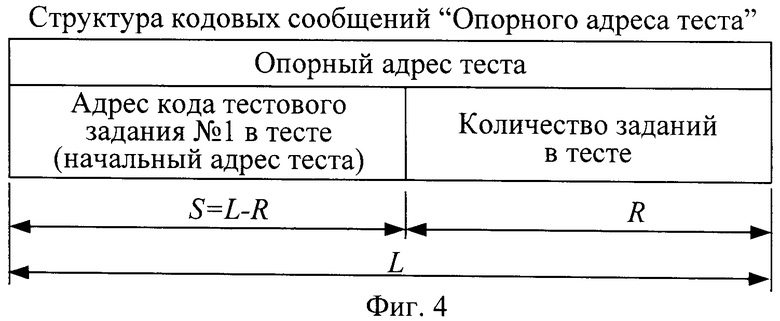

на фиг.4 - структура кодовых сообщений "Опорного адреса теста", хранящихся в блоке памяти БООАТ,

на фиг.5 - структура кодовых сообщений "Код тестового задания", хранящихся в первом и во втором блоке памяти устройства,

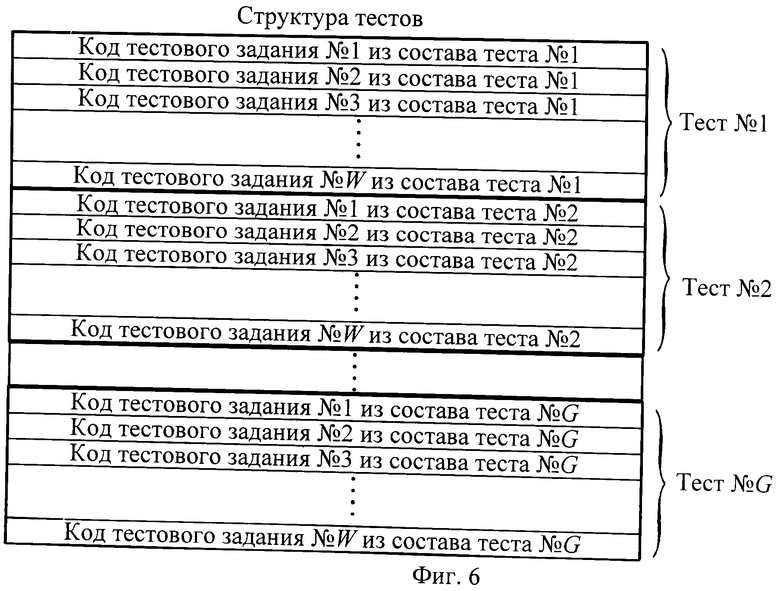

на фиг.6 - структура тестов.

Заявленное устройство, показанное на фиг.2, содержит блок определения опорного адреса теста 1, первый 13, второй 14 и третий 31 регистры, первый 6 и второй 15 компараторы, счетчик 9, первый 10 и второй 29 сумматоры, дешифратор 32, первый 5 и второй 12 блок памяти, первый 23 и второй 26 триггеры, первый 7, второй 8, третий 16, четвертый 17, пятый 19, шестой 20 и седьмой 28 элементы И, первую 251-25M и вторую 331-33K группы двухвходовых элементов И, группу трехвходовых элементов И 241-24N, первый 2, второй 18 и третий 27 элементы ИЛИ, первый 3, второй 4, третий 11, четвертый 21, пятый 22 и шестой 30 элементы задержки.

На фиг.2 также показаны первый 34, второй 37 и третий 38 управляющие входы устройства, V-разрядный вход "Номер теста" 35, N-разрядный вход "Код ответа" 36, первый 39 и второй 40 входы "Выбор режима", а также D-разрядный выход "Тест" 41, выход "Конец теста" 42, выход "Верный ответ" 43, выход "Ошибка" 44, N-разрядный выход "Код правильного ответа" 45, M-разрядный выход "Вес ответа" 46, K-разрядный выход "Оценка" 47, синхронизирующий выход 48 и L-разрядный выход "Опорный адрес теста" 49.

Блок определения опорного адреса теста 1 (фиг.3) предназначен для хранения кодовых сообщений "Опорный адрес теста" и их выдачи при получении соответствующего кода номера теста. Реализация данного блока может быть различной, в частности, как показано на фиг.3.

БООАТ 1 состоит из элемента задержки 1.1, блока памяти 1.2 и регистра 1.3. На чертеже также показаны управляющий вход БООАТ 34, V-разрядный вход "Номер теста" 35, L-разрядный выход "Опорный адрес теста" 49 и синхронизирующий выход 48.

Остальные элементы, входящие в общую структурную схему, показанную на фиг.2, а именно элементы И, элементы ИЛИ, элементы задержки, блоки памяти, компараторы, счетчик, сумматоры, регистры, триггеры и дешифратор известны и описаны в [5].

Все узлы и элементы устройства выполнены на стандартных потенциально-импульсных элементах.

В основу работы устройства для получения оценки знаний положены задания для самоконтроля и контроля, реализуемые в этих двух различных режимах работы.

Методология построения тестов (т.е. серии тестовых заданий) для самоконтроля и контроля усвоения знаний обучающихся в какой-либо предметной области в целом сходная. Однако есть и различия. Так, прямое и единственное назначение контрольных тестов - это проверка усвоения знаний по изучаемой дисциплине, в то время как задания для самоконтроля включают в себя и элементы обучения, ибо в этом случае при проведении контроля сообщаются правильные ответы [6].

Исходя из этого, требования к корректности составления контрольных тестов более жесткие, поскольку исследуемый уровень знаний должен быть адекватно отражен некоторыми количественными показателями. Для того чтобы подготовленные тесты действительно позволяли оценить степень усвоения учебного материала, они должны быть составлены в соответствии с определенными требованиями классической теории тестирования [7].

Устройство работает следующим образом.

Автоматизированное рабочее место обучающегося состоит из ПЭВМ, имеющего дисплей для воспроизведения тестовых заданий и клавиатуры персонального компьютера, примеры которых приведены в упомянутом источнике [6]. Управление контролем знаний в системе дистанционного обучения осуществляется с сервера дистанционного обучения (фиг.1).

Перед началом очередного цикла работы из сервера на V-разрядный вход "Номер теста" 35 сервер выдает код номера теста. Этот код номера теста поступает на вход блока памяти 1.2 БООАТ (см. фиг.3). В фиксированной ячейке этого блока памяти хранится кодовое сообщение "Опорный адрес теста", структура которого представлена на фиг.4, где в первых S-разрядах, где S=L-R, хранится адрес кода тестового задания №1 в тесте (начальный адрес теста), а во вторых R-разрядах хранится количество заданий в данном тесте.

Кроме того, с сервера задается один из двух режимов работы устройства: режим контроля или режим самоконтроля, реализуемые с помощью второго триггера 26, управляемого с первого 39 и второго 40 входов "Выбор режима". Если второй триггер 26 находится в исходном ("нулевом") состоянии, то он реализует режим контроля, при котором он блокирует цепи выдачи "подсказок" через пятый 19 и шестой 20 элементы И, группу трехвходовых элементов И 241-24N и первую группу двухвходовых элементов И 251-25M. Если же второй триггер 26 будет переведен в единичное состояние, то это будет означать работу устройства в режиме самоконтроля. При этом высоким потенциалом прямого выхода второго триггера 26 пятый 19 и шестой 20 элементы И, группа трехвходовых элементов И 241-24N и первая группа двухвходовых элементов И 251-25M будут открыты для выдачи подсказок на экран дисплея.

Для начала работы с сервера подается синхронизирующий сигнал, который поступает на первый управляющий вход 34 и задержанным элементом задержки 1.1 БООАТ на время срабатывания блока памяти 1.2 БООАТ, поступает на управляющий вход регистра 1.3 БООАТ и содержимое фиксированной ячейки блока памяти 1.3 БООАТ заносится в регистр 1.3 БООАТ.

Содержимое первых S-разрядов с выхода регистра 1.3 БООАТ через выход 49 БООАТ поступает на первый информационный вход первого сумматора 10, а содержимое вторых R-разрядов поступает на первый информационный вход первого компаратора 6.

Синхронизирующий импульс с выхода элемента задержки 1.1 БООАТ через выход 48 БООАТ проходит через первый элемент ИЛИ 2 на вход первого элемента задержки 3, где задерживается на время установки кода на входе первого сумматора 10. Учитывая, что к этому моменту счетчик 9, выход которого соединен со вторым информационным входом первого сумматора 10, находится в исходном ("нулевом") состоянии, то на втором информационном входе первого сумматора 10 будет содержаться код, соответствующий нулевому значению, а на первом информационном входе первого сумматора будет содержимое первых S-разрядов кодового сообщения "Опорный адрес теста".

При поступлении синхронизирующего импульса на управляющий вход первого сумматора 10 с выхода первого элемента задержки 3 будет произведено суммирование и на выходе первого сумматора 10 будет сформирован адрес кода i-го задания теста, в данном случае первого задания. Этот же импульс, задержанный вторым элементом задержки 4 на время переходных процессов в первом сумматоре 10, поступает на управляющий вход первого блока памяти 5 и адрес кода i-го тестового задания, считывается с выхода первого сумматора 10 в первый блок памяти 5. Этот же импульс поступает на управляющий вход второго блока памяти 12 и адрес кода i-го тестового задания, считывается с выхода первого сумматора 10 во второй блок памяти 12, по которому хранится вес ответа данного тестового задания.

Структура кодового сообщения "Опорный адрес теста" представлена на фиг.4, где первые S-разрядов, где S=L-R, отведены под адрес первого тестового задания, а вторые R-разрядов содержат адрес кода количества заданий в тексте.

Структура кодового сообщения "Код тестового задания" представлена на фиг.5, где первые D-разрядов, где D=Q-N, отведены под код содержания i-го тестового задания, а вторые N-разрядов содержат код правильного ответа i-го тестового задания.

После считывания D-разрядов содержимое ячейки в виде текста i-го тестового задания выдаются на экран дисплея через выход устройства "Тест" 41, а вторые N-разрядов, содержащие код правильного ответа i-го тестового задания, поступают на информационный вход первого регистра 13, куда и заносятся импульсом, поступающим на управляющий вход первого регистра 13 с выхода третьего элемента задержки 11, которым он был задержан на время срабатывания первого блока памяти 5.

По классической теории тестирования [7] на оптимальное количество (4-6) вариантов ответов должен быть только один правильный вариант ответа и этот ответ хранится в первом регистре 13.

Обучающийся из предлагаемых вариантов ответа выбирает тот, который он считает правильным, и набирает на клавиатуре соответствующий знак или символ. Код ответа с N-разрядного входа "Код ответа" 36 поступает на информационный вход второго регистра 14, куда и заносится синхронизирующим импульсом, поступающим на управляющий вход второго регистра 14 со второго управляющего входа 37.

Одновременно с этим, тот же синхроимпульс со второго управляющего входа 37 задерживается четвертым элементом задержки 21 на время записи кода во второй регистр 14 и затем поступает на синхронизирующий вход второго компаратора 15, на информационные входы которого подаются коды с первого 13 и второго 14 регистров. Если коды регистров совпали, то на прямом выходе второго компаратора 15 будет высокий потенциал, которым будет открыт третий элемент И 16, на другой вход которого поступает синхронизирующий импульс с выхода пятого элемента задержки 22, задержанный на время срабатывания второго компаратора 15.

Импульс с выхода пятого элемента задержки 22 проходит третий элемент И 16 и далее поступает, во-первых, на вход пятого элемента И 19, открытый по второму входу вторым триггером 26 в режиме самоконтроля. В результате на выходе устройства "Верный ответ" 43 появится сигнал "Верный ответ".

Во-вторых, импульс с выхода третьего элемента И 16 через второй элемент ИЛИ 18 поступает на второй вход первого элемента И 7, состояние которого определяется потенциалом с инверсного выхода первого компаратора 6. Учитывая то обстоятельство, что на одном входе первого компаратора 6 будет код, фиксирующий число заданий в тесте, а на другом - код счетчика 9, в данный момент, соответствующий нулевому значению, то на прямом выходе первого компаратора 6 будет низкий потенциал, а на инверсном - высокий, поддерживающий первый элемент И 7 в открытом состоянии.

В результате импульс с выхода второго элемента ИЛИ 18 проходит через первый элемент И 7 и далее поступает как на счетный вход счетчика 9, увеличивая его показания на единицу, так и на второй вход первого элемента ИЛИ 2 и задержанный первым элементом задержки 3 на время срабатывания счетчика 9, на синхронизирующий вход первого сумматора 10, фиксируя факт увеличения кода на адресном входе первого 5 и второго 12 блока памяти на единицу.

Далее осуществляется считывание описанным выше образом следующего тестового задания и записи соответствующего ему кода правильного ответа в первый регистр 13.

Если же в процессе выбора ответа на очередное тестирующее задание во второй регистр 14 будет введен неправильный ответ, то этот факт будет зафиксирован вторым компаратором 15, выдачей высокого потенциала на его инверсном выходе. В результате этого третий элемент И 16 будет закрыт, а четвертый элемент И 17 открыт. Импульс с выхода пятого элемента задержки 22 пройдет через четвертый элемент И 17 и поступит, во-первых, на управляющий вход первого триггера 23, фиксирующего факт ошибки и открывающего по второму входу трехвходовую группу элементов И 241-24N. Учитывая, что в режиме самоконтроля второй триггер 26 открывает трехвходовую группу элементов И 241-24N по третьему входу, и, соответственно, импульс проходит на выход тех из них, которые будут открыты соответствующим выходом первого регистра 13, и код правильного ответа будет выдан на экран дисплея в виде информации "Код правильного ответа" через N-разрядный выход "Код правильного ответа" 45.

Возвращение первого триггера 23 в исходное ("нулевое") состояние осуществляется сигналом с третьего управляющего входа 38 начальной установки с пульта управления устройства (не показан) перед набором ответа обучающимся.

Также в режиме самоконтроля первые входы двухвходовых элементов И первой группы двухвходовых элементов И 251-25M будут открыты, то импульс проходит на выход тех из них, которые будут открыты соответствующим выходом второго блока памяти 12 и вес ответа i-го тестового задания будет выдан на экран дисплея в виде информации "Вес ответа" через M-разрядный выход "Вес ответа" 46.

Во-вторых, он пройдет через шестой элемент И 20, открытый высоким потенциалом второго триггера 26 в режиме самоконтроля, на выход "Ошибка" 44 в качестве сигнала "Ошибка".

В-третьих, импульс с выхода четвертого элемента И 17 поступает на управляющий вход второго сумматора 29 и М-разрядов веса i-го тестового задания, находящихся на втором информационном входе, суммируются с M-разрядами третьего регистра 31, находящихся на первом информационном входе второго сумматора 29.

В-четвертых, поступает на управляющий вход третьего регистра 31, задержанный шестым элементом задержки 30 на время срабатывания второго сумматора 29, и результат суммирования записывается в третий регистр 31. Показания третьего регистра 31 поступают на вход дешифратора 32, который в зависимости от показаний регистра открывает один из двухвходовых элементов И второй группы двухвходовых элементов И 331-33K. Выходам соответствующих двухвходовых элементов И второй группы двухвходовых элементов И 331-33K поставлены в соответствие возможные оценки знаний, которые выдаются на K-разрядный выходы "Оценка" 47.

В-пятых, этот же импульс поступает на второй вход седьмого элемента И 28, состояние которого определяется потенциалом с инверсного выхода второго триггера 26. Если в данный момент второй триггер 26 находится в режиме самоконтроля, то низким потенциалом с инверсного выхода второго триггера 26 седьмой элемент И 28 будет закрыт и продолжение цикла предъявления очередного тестового задания будет возможно лишь после повторного ввода теперь уже правильного ответа, отраженного на экране дисплея с выхода "Верный ответ", во второй регистр 14.

В этом случае второй компаратор 15 зафиксирует факт равенства кодов первого 13 и второго 14 регистров и высоким потенциалом откроет третий элемент И 16, через который синхронизирующий импульс с выхода пятого элемента задержки 22 проходит через второй элемент ИЛИ 18 и первый элемент И 7 как на счетный вход счетчика 9, так и через первый элемент ИЛИ 2 и, задержанный первым элементом задержки 3 на время срабатывания счетчика 9, на управляющий вход первого сумматора 10. Далее осуществляется считывание описанным выше образом следующего тестового задания, соответствующего ему кода правильного ответа в первый регистр 13 и веса ответа i-го тестового задания во второй сумматор 29.

Если же второй триггер 26 находился в исходном ("нулевом") состоянии, что соответствует режиму работы устройства в режиме контроля, то высоким потенциалом с инверсного выхода будет открыт седьмой элемент И 28 и импульс с выхода четвертого элемента И 17 пройдет через седьмой элемент И 28, второй элемент ИЛИ 18, первый элемент И 7 и поступит на счетный вход счетчика 9 и через первый элемент ИЛИ 2 и, задержанный первым элементом задержки 3 на время срабатывания счетчика 9, на управляющий вход первого сумматора 10.

Описанный процесс будет продолжаться до тех пор, пока первый компаратор 6 не зафиксирует равенства кодов "Количество заданий в тесте" в регистре 1.3 БООАТ и счетчика 9. Как только первый компаратор 6 зафиксирует равенство кодов "Количество заданий в тесте" в регистре 1.3 БООАТ и счетчика 9, то на прямом выходе первого компаратора 6 появится высокий потенциал, которым по первому входу открывается второй элемент И 8, на второй вход которого поступает синхронизирующий импульс с выхода третьего элемента задержки 11. Синхронизирующий импульс проходит второй элемент И 8 и поступает, во-первых, как на выход "Конец теста" 42 в качестве сигнала серверу об окончании предъявления тестовых заданий, так и на установочный вход счетчика 9 и первого сумматора 10, возвращая их в исходное ("нулевое") состояние. Во-вторых, этот же импульс поступает на вторые входы двухвходовых элементов И второй группы двухвходовых элементов И 331-33К и проходит на выход того из них, который будет открыт соответствующим выходом дешифратора 32, что определяет вид оценки, которую заслужил обучающийся по результатам работы.

В-третьих, этот же импульс поступает на установочный вход третьего регистра 31 и через третий элемент ИЛИ 27 - на установочный вход второго триггера 26, устанавливая его в исходное ("нулевое") состояние, которое соответствует режиму контроля знаний.

Таким образом, введение новых узлов и конструктивных связей позволило существенно повысить точность оценки знаний обучающихся по всем разделам изучаемых предметных областей.

Источники информации

1. Дружинин В.Н. Экспериментальная психология - СПб: Изд. «Питер», 2000.

2. Ковалева Г.С., Татур А.О., Челышкова М.Б. Требования к характеристикам заданий, включаемых в банк заданий для единого экзамена. - Сборник статей интернет-семинар повышения квалификации по проблемам подготовки к экзамену по русскому языку в рамках ЕГЭ.

3. Морев И.А. Образовательные информационные технологии. Часть 2. Педагогические измерения: Уч. пособие. - Владивосток: Изд-во Дальневост. ун-та, 2004.

4. Компетентностный подход к формированию основных образовательных программ третьего поколения. - СПб.: Изд. СПбГУЭФ, 2010.

5. Шило В.Л. Популярные цифровые микросхемы: Справочник. - 2-е изд., исправленное. - М.: Радио и связь, 1989.

6. Романов А.Н. и др. Технология дистанционного обучения в системе заочного экономического образования. - М.: ЮНИТИ-ДАНА, 2000.

7. Клайн П. Справочное руководство по конструированию тестов. Киев: ПАН-ЛТД, 1994.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМА ДИСТАНЦИОННОГО ОБУЧЕНИЯ | 2005 |

|

RU2282247C1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПОЛУЧЕНИЕМ ОЦЕНКИ КАЧЕСТВА ЗНАНИЙ В СИСТЕМЕ ДИСТАНЦИОННОГО ОБУЧЕНИЯ | 2001 |

|

RU2248610C2 |

| СИСТЕМА ДИСТАНЦИОННОГО ОБУЧЕНИЯ СТУДЕНТОВ | 2006 |

|

RU2315364C1 |

| ТЕСТЕР УРОВНЯ ИННОВАЦИОННОГО ИНТЕЛЛЕКТА ЛИЧНОСТИ | 2013 |

|

RU2522992C1 |

| УСТРОЙСТВО ОПРЕДЕЛЕНИЯ РОЛЕВОЙ ФУНКЦИИ УЧАСТНИКА ТВОРЧЕСКОГО КОЛЛЕКТИВА | 2013 |

|

RU2541431C1 |

| ПРИБОР ДЛЯ РЕЙТИНГОВОЙ ОЦЕНКИ УРОВНЯ ГОТОВНОСТИ К ИННОВАЦИОННОЙ ДЕЯТЕЛЬНОСТИ | 2014 |

|

RU2548478C1 |

| УСТРОЙСТВО ОБУЧЕНИЯ ОПЕРАТОРОВ | 1997 |

|

RU2129734C1 |

| Устройство для обучения операторов | 1989 |

|

SU1709372A1 |

| САМОНАСТРАИВАЮЩЕЕСЯ ЦИФРОВОЕ СГЛАЖИВАЮЩЕЕ УСТРОЙСТВО | 2017 |

|

RU2665906C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2006 |

|

RU2313128C1 |

Изобретение относится к вычислительной технике, в частности к устройствам оценивания знаний обучающихся, и может быть использовано для контроля знаний обучающихся. Техническим результатом является расширение области применения устройства оценивания знаний обучающихся и повышение достоверности оценки знаний обучающихся за счет дифференциации заданий теста путем сопоставления с каждым из них соответствующего относительно весового коэффициента и учета указанных коэффициентов при формировании итоговой оценки по результатам тестирования. Для этого устройство содержит блок определения опорного адреса теста, элементы ИЛИ, элементы задержки, блоки памяти, компараторы, элементы И, счетчик, сумматоры, регистры, триггеры, группу трехвходовых элементов И, группы двухвходовых элементов И, дешифратор. 1 з.п. ф-лы, 6 ил.

1. Устройство оценивания знаний, содержащее первый и второй регистры, первый, второй и третий элементы ИЛИ, первый, второй, третий, четвертый и пятый элементы задержки, первый блок памяти, первый и второй компараторы, первый, второй, третий, четвертый, пятый, шестой и седьмой элементы И, счетчик, первый сумматор, первый и второй триггеры, группу трехвходовых элементов И, вторую группу двухвходовых элементов И, дешифратор, блок определения опорного адреса теста (БООАТ), управляющий вход которого является первым управляющим входом устройства, s-й разряд, где s=1, 2, …, S, L-разрядного выхода "Опорный адрес теста" БООАТ, где L=S+R, причем R - количество разрядов, достаточное для представления кода, соответствующего максимальному количеству тестовых заданий в любом из тестов, соединен с s-м разрядом первого L-разрядного информационного входа первого сумматора, j-й разряд, где j=(L-R)+1, (L-R)+2, …, L, L-разрядного выхода "Опорный адрес теста" БООАТ соединен с j-м разрядом первого L-разрядного информационного входа первого компаратора, синхронизирующий выход БООАТ соединен с первым входом первого элемента ИЛИ, выход которого соединен с входом первого элемента задержки, прямой выход первого компаратора соединен с первым входом второго элемента И, инверсный выход первого компаратора соединен с первым входом первого элемента И, выход которого соединен с счетным входом счетчика и вторым входом первого элемента ИЛИ, выход второго элемента И соединен с входом сброса счетчика, входом сброса первого сумматора, вторым входом третьего элемента ИЛИ и вторыми входами двухвходовых элементов И второй группы двухвходовых элементов И и является выходом "Конец теста" устройства, выход первого элемента задержки соединен с входом второго элемента задержки и управляющим входом первого сумматора, выход второго элемента задержки соединен с управляющим входом первого блока памяти и входом третьего элемента задержки, выход которого соединен с вторым входом второго элемента И и управляющим входом первого регистра, d-й разряд Q-разрядного выхода первого блока памяти, где d=1, 2, …, D, является d-м разрядом D-разрядного выхода "Тест" устройства, где D - количество разрядов, достаточное для хранения кода, соответствующего содержанию любого из тестовых заданий и возможных вариантов ответа на него, Q=D+N, где N - количество разрядов, достаточное для представления кода, соответствующего максимальному количеству вариантов ответов в любом из тестовых заданий, i-разряд Q-разрядного выхода первого блока памяти, где i=(Q-N)+1, (Q-N)+2, …, Q, соединен с n-м разрядом N-разрядного информационного входа первого регистра, где n=1, 2, …, N, L-разрядный адресный вход первого блока памяти соединен с L-разрядным выходом первого сумматора, L-разрядный выход счетчика соединен с вторым L-разрядным информационным входом первого сумматора и с вторым L-разрядным входом первого компаратора, n-й разряд N-разрядного выхода первого регистра соединен с первым входом n-го трехвходового элемента И группы трехвходовых элементов И и соответствующим разрядом первого N-разрядного входа второго компаратора, прямой выход которого соединен с первым входом третьего элемента И, а его инверсный выход соединен с первым входом четвертого элемента И, выход которого соединен с первым входом шестого элемента И, управляющим входом первого триггера и вторым входом седьмого элемента И, выход которого соединен с вторым входом второго элемента ИЛИ, выход которого соединен с вторым входом первого элемента И, выход третьего элемента И соединен с первым входом второго элемента ИЛИ и первым входом пятого элемента И, выход которого является выходом "Верный ответ" устройства, N-разрядный информационный вход второго регистра является N-разрядным входом "Код ответа" устройства, а его N-разрядный выход соединен с вторым N-разрядным входом второго компаратора, управляющий вход второго регистра соединен с входом четвертого элемента задержки и является вторым управляющим входом устройства, выход четвертого элемента задержки соединен с управляющим входом второго компаратора и входом пятого элемента задержки, выход которого соединен с вторым входом третьего элемента И и вторым входом четвертого элемента И, вторые входы трехвходовых элементов И группы трехвходовых элементов И соединены с прямым выходом первого триггера, вход сброса которого является третьим управляющим входом устройства, управляющий вход второго триггера и первый вход третьего элемента ИЛИ являются соответственно первым и вторым входами "Выбор режима" устройства, выход третьего элемента ИЛИ соединен с входом сброса второго триггера, инверсный выход которого соединен с первым входом седьмого элемента И, а его прямой выход соединен с третьими входами трехвходовых элементов И группы трехвходовых элементов И, вторым входом пятого элемента И и вторым входом шестого элемента И, выход которого является выходом "Ошибка" устройства, выход n-го трехвходового элемента И группы трехвходовых элементов И является n-м разрядом N-разрядного выхода "Код правильного ответа" устройства, k-й разряд, где k=1, 2, …, K, K-разрядного выхода дешифратора, где K - количество баллов, используемое для оценивания знаний обучающихся, соединен с первым входом k-го двухвходового элемента И второй группы двухвходовых элементов И, выход k-го двухвходового элемента И второй группы двухвходовых элементов И является k-м разрядом K-разрядного выхода "Оценка" устройства, отличающееся тем, что дополнительно введены второй блок памяти, второй сумматор, шестой элемент задержки, первая группа двухвходовых элементов И и третий регистр, М-разрядный выход которого, где M=log2K - количество разрядов, достаточное для представления максимально возможной суммы весов ответов при прохождении теста, соединен с М-разрядным входом дешифратора и первым М-разрядным информационным входом второго сумматора, М-разрядный выход которого соединен с М-разрядным информационным входом третьего регистра, управляющий вход третьего регистра соединен с выходом шестого элемента задержки, вход которого соединен с управляющим входом второго сумматора и выходом четвертого элемента И, управляющий вход второго блока памяти соединен с выходом второго элемента задержки, L-разрядный адресный вход второго блока памяти соединен с L-разрядным выходом первого сумматора, m-й разряд М-разрядного выхода второго блока памяти, где m=1, 2, …, М, соединен с первым входом m-го двухвходового элемента И первой группы двухвходовых элементов И и m-м разрядом второго М-разрядного информационного входа второго сумматора, вторые входы двухвходовых элементов И первой группы двухвходовых элементов И объединены между собой и соединены с прямым выходом второго триггера, выход m-го двухвходового элемента И первой группы двухвходовых элементов И является m-м разрядом М-разрядного выхода "Вес ответа" устройства, вход сброса третьего регистра и вход сброса второго сумматора соединены с выходом второго элемента И, а V-разрядный вход "Номер теста" БООАТ является V-разрядным входом "Номер теста" устройства, где V - количество разрядов, достаточное для представления кода, соответствующего максимальному количеству тестов, предусмотренных для оценивания знаний обучающегося.

2. Устройство по п.1, отличающееся тем, что БООАТ состоит из элемента задержки, блока памяти и регистра, L-разрядный выход которого является L-разрядным выходом "Опорный адрес теста" БООАТ, L-разрядный информационный вход регистра соединен с L-разрядным выходом блока памяти, V-разрядный адресный вход которого является V-разрядным входом "Номер теста" БООАТ, вход элемента задержки соединен с управляющим входом блока памяти и является управляющим входом БООАТ, выход элемента задержки соединен с управляющим входом регистра и является синхронизирующим выходом БООАТ.

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПОЛУЧЕНИЕМ ОЦЕНКИ КАЧЕСТВА ЗНАНИЙ В СИСТЕМЕ ДИСТАНЦИОННОГО ОБУЧЕНИЯ | 2001 |

|

RU2248610C2 |

| Сместитель-подогреватель | 1941 |

|

SU63955A1 |

| УСТРОЙСТВО ОБУЧЕНИЯ ОПЕРАТОРОВ | 1997 |

|

RU2129734C1 |

| Колосоуборка | 1923 |

|

SU2009A1 |

Авторы

Даты

2012-11-20—Публикация

2011-12-14—Подача