Изобретение относится к импульсной технике, в частности к устройствам для задержки сигналов, выполненных на основе оперативно-запоминающих блоков с использованием других элементов цифровой вычислительной техники.

Известно устройство для задержки сигналов, содержащее оперативно-запоминающий блок (ОЗБ), регистры, управляемый многоканальный усилитель и блок управления, включающий генератор тактовых импульсов, счетчик импульсов, логический блок, блок постоянной памяти и регистр [1]. В известном устройстве входной непрерывный информационный сигнал квантуется по времени с получением отдельных битов дискретной двоичной информации, т.е. квантов задержки, записывается в ОЗБ, где хранится заданное время, и затем считывается из ОЗБ в выходной регистр.

Недостаток известного устройства - невысокая точность задержки из-за низкой граничной, максимально возможной частоты квантования входного сигнала. Известно, что максимальная частота квантования, величина которой определяет точность задержки, может быть определена по граничной рабочей частоте наиболее инерционного элемента в указанной цепи преобразования. В данном случае таким элементом является ОЗБ. Минимальная длительность цикла записи-считывания микросхем - ОЗБ из наиболее широко применяемой серии 537 не превышает 0,4 мкс, поэтому при использовании серийно выпускаемых в настоящее время дискретных элементов вычислительной техники для построения известного устройства оно принципиально не может обеспечить погрешность задержки менее 0,4 мкс, что часто является неприемлемым. В аппаратуре, разрабатываемой на предприятии-заявителе, эта погрешность не должна превышать 20 нс (частота квантования 50 МГц), что делает неприемлемым использование известного технического решения в указанном случае из-за низкой точности задержки.

Известно устройство для задержки сигналов [2], содержащее времязадающий и фазосдвигающий блоки, счетчик m запоминающих регистров (m=1,2,3...), блок оперативной памяти, включающий m ОЗБ, блок управления и элемент ИЛИ. В этом устройстве входной сигнал разделяется на m каналов, в каждом из которых квантуется по времени с частотой задающего генератора времязадающего блока, сдвинутой по фазе относительно частоты в соседних каналах. Затем полученные отдельные биты информации в каждом канале записываются в ОЗБ, хранятся в нем заданное время и далее считываются из ОЗБ, после чего объединяются в один выходной сигнал. В устройстве, таким образом, реализован принцип повышения точности задержки путем увеличения числа параллельно работающих каналов.

Недостаток известного технического решения - его сложность и неэкономичность из-за большой потребляемой мощности от источников питания, которая увеличивается практически пропорционально повышению точности задержки, так как при каждом увеличении точности задержки, например, в 2 раза требуется усложнение устройства задержки в это же число раз, т.е. фактическое построение двух устройств.

Известно устройство для задержки сигналов [3], наиболее близкое по технической сущности к предложенному устройству, содержащее последовательно соединенные первый регистр сдвига, вход которого соединен с первой входной шиной, первый запоминающий регистр, ОЗБ, второй запоминающий регистр, второй регистр сдвига, мультиплексор и включенные параллельно два D-триггера, выходы которых являются выходами устройства. Выход мультиплексора также соединен с информационным входом второго D-триггера через элемент ИСКЛЮЧАЮЩЕЕ ИЛИ. В устройство также входит управляющий блок, содержащий задающий генератор тактовых импульсов, распределитель импульсов, второй вход которого соединен с второй входной шиной, формирователь импульсов и первый мультиплексор, соединенные последовательно, два счетчика импульсов, первые входы которых соединены с выходом формирователя импульсов, вторые входы - с второй входной шиной, а выходы - с вторым и третьим входами первого мультиплексора, причем второй вход второго счетчика импульсов соединен с третьей входной шиной, а второй его выход через D-триггер, второй мультиплексор, преобразователь код-временной интервал, параллельно соединенные второй преобразователь код-временной интервал и делитель частоты следования импульсов соединен с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ. Кроме того, выход распределителя импульсов соединен с вторым входом второго мультиплексора, третий вход которого соединен с вторым входом мультиплексора устройства и его четвертой входной шиной.

В этом устройстве входной информационный сигнал квантуется по времени и получаемые отдельные двоичные биты информации (кванты задержки) последовательно запоминаются в количестве n квантов (n=4, 8, 16, 32). Далее в определенные моменты времени и с частотой в n раз ниже частоты квантования запомненные n квантов одновременно переписываются в запоминающий n-разрядный регистр, в результате чего формируются n-разрядные слова, которые записываются в ОЗБ, хранятся в нем заданое время, считываются из ОЗБ и преобразуются обратно из слов в последовательные кванты задержки с длительностью квантов, равной длительности входных квантов, т.е. в реальном масштабе времени. Таким образом, в известном устройстве использован принцип повышения точности задержки, заключающийся в накоплении последовательных квантов задержки в количестве n квантов с максимальной частотой квантования, формировании n-разрядных слов в промежутках между моментами квантования и обратном преобразовании n-разрядных слов в последовательные кванты задержки с той же высокой частотой квантования.

Недостаток такого технического решения - низкая экономичность из-за увеличения потребляемой мощности практически пропорционально повышению частоты квантования, что точно соблюдается при высоких частотах квантования (более 10 МГц) и ведет при увеличении точности задержки к существенному увеличению потребляемой мощности, которое не позволяет использовать известное техническое решение.

В известном устройстве при высоких частотах квантования определяющими по потреблению становятся элементы, работающие на самых высоких частотах, т. е. на частоте квантования входного сигнала. Такими энергоемкими элементами в соответствии с используемым принципом повышения точности в известном устройстве являются 4n элементов с памятью, составляющих входной и выходной регистры сдвига, буферные запоминающие регистры и распределитель импульсов блока управления.

При увеличении точности необходимо увеличивать величину n, что приводит к пропорциональному увеличению потребляемой мощности.

Указанный недостаток поясняется с помощью следующего примера. При n=32 и частоте квантования 50 МГц указанные узлы, работающие на высокой частоте, должны быть выполнены в соответствии с используемым принципом, например, на 32 микросхемах 530ИР11 (или аналогичных), каждая из которых потребляет мощность 0,7 Вт, суммарная мощность составит более 20 Вт, что во много раз больше потребляемой мощности других элементов устройства, в том числе и ОЗБ.

Сущность изобретения заключается в том, что последовательные двоичные кванты задержки преобразуют в разрядные слова до максимальной величины n= 4,8,16, ... за m операций (m=log2 n), увеличивая за каждую операцию разрядность каждого слова в 2 раза, при этом одновременно и параллельно понижают каждый раз частоту преобразования (квантования) также в 2 раза и обратное преобразование n-разрядных слов в последовательные кванты задержки осуществляют коммутацией сигналов отдельных разрядов слов с помощью сигналов с пропорционально пониженными частотами преобразования в трансформированном масштабе времени. В результате устраняются наиболее энергоемкие операции сдвига информации на самой высокой частоте квантования, реализуемые на большом количестве (4 n) элементов с памятью, которое растет с увеличением точности задержки, и заменяются операциями деления и записи, которые выполняются на элементах с памятью, число которых не зависит от величины n, работающих к тому же на частоте квантования, в два раза более низкой, чем частота, на которой выполняется операция сдвига информации в известном устройстве.

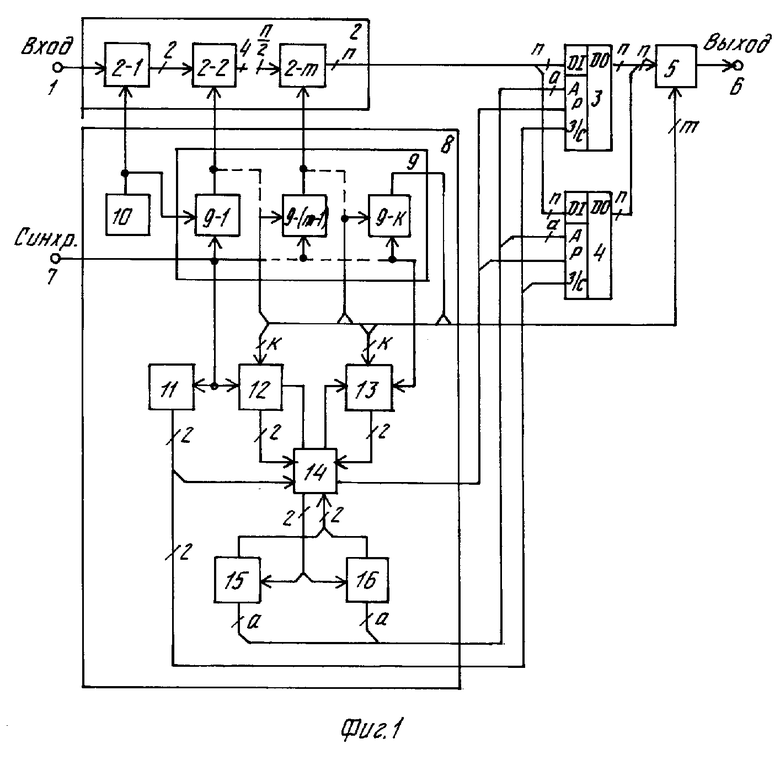

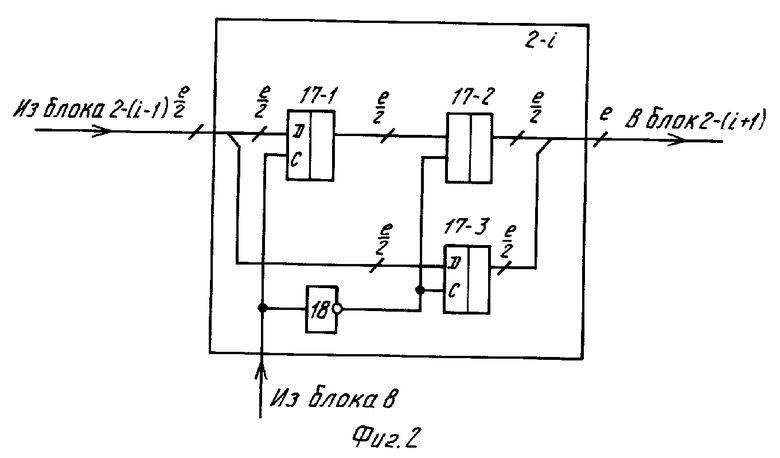

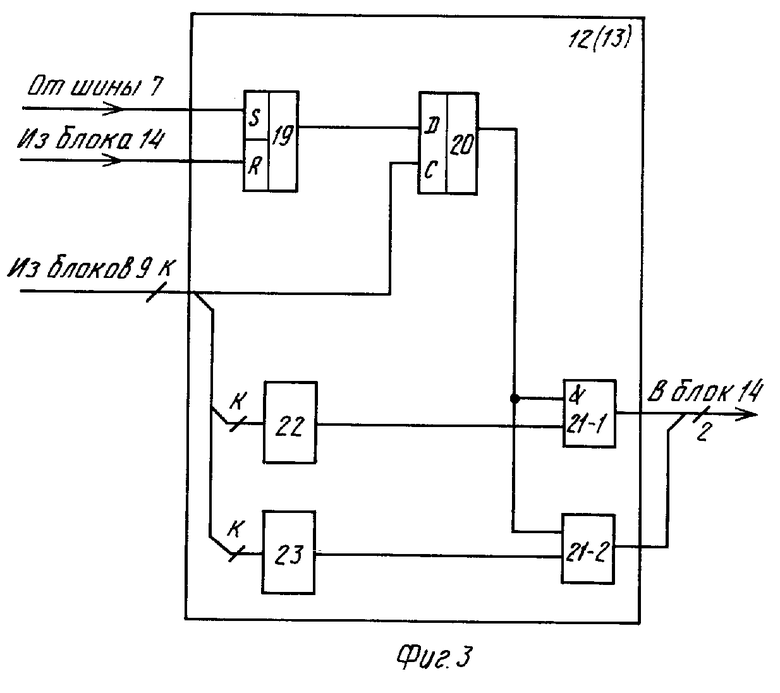

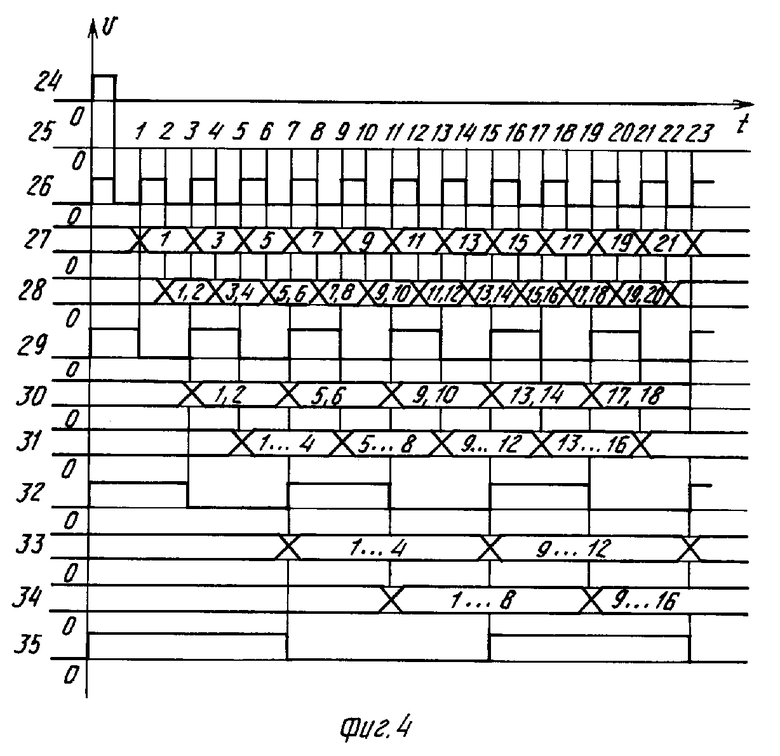

Сущность изобретения поясняется с помощью функциональной схемы предложенного устройства для задержки сигналов на фиг. 1, функциональных схем его отдельных блоков на фиг. 2 и 3 и временных диаграмм напряжений в характерных точках устройства на фиг. 4.

На фиг. 1 приняты следующие обозначения: 1 - входная информационная шина, 2 (2-1, 2-2, ..., 2-m) - блоки запоминающих регистров в количестве m с разрядностью выходов 2,4 ..... n соответственно, 3, 4 - ОЗБ, каждый из которых имеет группы D1 и D0 из n информационных входов и выходов, группу А из а адресных кодированных входов и входы записи - считывания (З/С) и разрешения (Р) записи-считывания, где а= 2,3,..., 5 - блок коммутаторов сигналов, 6 - выходная информационная шина, 7 - входная шина синхронизации, 8 - блок управления, где 9[9-1...9-(m-1)...9-К] - последовательные делители частоты следования импульсов задающего генератора, где К=2, 3,..., в количестве К делителей, 10 - задающий генератор тактовых импульсов, 11 - счетный триггер, 12 и 13 - формирователи импульсов управления реального и трансформированного масштабов времени соответственно, 14 - коммутатор сигналов, 15, 16 - адресные счетчики импульсов, имеющие а+1 разрядов.

В блоке 2-i, где 1 ≅ i ≅ m, 17 - запоминающий е/2-разрядный регистр (е= 2i) с входами D и C информации и синхронизации, 18 - логический элемент НЕ (инвертор).

В формирователе 12 (13) 19 - триггер с установочными R- и S-входами, 20 - триггер с входами D и С информации и синхронизации, 21 - элемент И, 22 и 23 - дешифраторы.

На фиг. 1 информационная входная шина 1 соединена через m блоков 2 запоминающих регистров, ОЗБ 3 и 4, соединенные параллельно, и блок 5 коммутаторов сигналов с выходной шиной 6. Вторая входная шина 7 (синхросигнала) соединена с входом блока 8 управления, первая и вторая группы из m выходов которого соединены с входом синхронизации каждого из m блоков 2 запоминающих регистров и управляющими входами блока 5 коммутаторов сигналов соответственно, две группы выходов из а выходов соединены с адресными входами из а входов каждого из ОЗБ 3 и 4, первая и вторая группы из двух выходов соединены с входами записи-считывания и разрешения записи-считывания ОЗБ 3 и 4. В блоке 8 управления вход синхронизации соединен с входами установки К делителей 9-1. . .9-(m-1)...9-K частоты следования импульсов задающего генератора 10, выход которого, а также выходы делителей 9-1...9-(m-1) частоты образуют первую группу из m выходов блока 8 управления, выходы старших разрядов которых с 9-(К-m) по 9-К являются второй группой из m выходов блока 8 управления. Кроме того, вход 7 синхронизации блока соединен с входом синхронизации счетного триггера 11, прямой и инверсный выходы которого образуют первую группу из двух выходов блока 8 управления, и входами запуска формирователей 12 и 13 импульсов реального и трансформированного масштабов времени. Вторые входы формирователей 12 и 13 импульсов подключены к выходам коммутатора 14 импульсов, его группа из двух выходов является второй группой выходов блока 8 управления, вторая группа из двух выходов соединена с входами синхронизации счетчиков 15 и 16 импульсов, адресные выходы которых образуют две группы по а выходов блока 8 управления. Первая и вторая группы из двух входов коммутатора 14 импульсов соединены с выходами формирователей 12 и 13 импульсов, и управляющий вход коммутатора 14 импульсов соединен с одним из двух выходов счетного триггера 11.

На фиг. 2 запоминающие регистры 17-1 и 17-2 блока 2-i соединены последовательно, группа из е/2 входов соединена с входами регистров 17-1 и 17-3, выходы регистров 17-2 и 17-3 образуют группу из е выходов, а вход блока 2-i запоминающих регистров непосредственно соединен с входом синхронизации С регистра 17-1 и через инвертор 18 - с входами С регистров 17-2 и 17-3, причем е=2i.

На фиг. 3 первый и второй входы формирователей 12(13) импульсов соединены с установочными R- и S-входами триггера 19, выход которого через триггер 20, имеющий информационный вход D и вход С синхронизации, соединен с первыми входами элементов И 21-1 и 21-2. Выходы последних образуют выходы формирователей 12(13) импульсов, а вторые входы элементов И 21 соединены через дешифраторы 22 и 23 с группой из К входов, один из которых подключен к входу С триггера 20.

На фиг. 4 по оси абсцисс временных диаграмм 24...35 отложено время t, а по оси ординат - напряжение U.

Устройство для задержки сигналов работает следующим образом.

Устройство предназначено для задержки периодического дискретного двоичного сигнала, поступающего на входную шину 1, на величину периода его повторения с измененным, т. е. трансформированным, масштабом времени выходного сигнала, снимаемого с выходной шины 6.

Устройство выполнено на интегральных микросхемах цифровой вычислительной техники [4]. В каждом периоде повторения входной информационный сигнал может иметь произвольную, случайную кодовую двоичную структуру, с помощью которой передается необходимая информация, но появляется только в определенной временной зоне, начало которой совпадает (задается) с короткими импульсами синхронизации, поступающими на шину 7. Длительность указанной зоны определяется числом, например, М квантов задержки - битов входной информации.

Выходной сигнал имеет одинаковую с входным кодовую структуру и то же число М квантов задержки, длительность которых, однако, увеличена, например, в целое число С раз, называемое коэффициентом трансформации масштаба времени (С=1, 2, 3,...). Предполагается, что длительность отдельных кодовых информационных элементов входного сигнала не менее чем в два раза больше периода квантования сигнала в устройстве задержки, и поэтому потери информации в задержанном сигнале не происходит.

Входной информационный кодированный сигнал с шины 1 поступает на информационный вход первого блока 2-1 запоминающих регистров, на другой вход которого - вход синхронизации - подается из блока 8 управления сигнал квантования, т. е. непрерывная последовательность импульсов, период повторения которых равен двум квантам задержки реального масштаба времени, так как квантование в блоке 2-1 осуществляется по фронтам и спадам импульсов квантования. С помощью блока 2-1 запоминающих регистров осуществляется преобразование последовательных квантов задержки в двухразрядный дискретный сигнал, т.е. в двухразрядные двоичные слова. Далее информационный сигнал последовательно проходит через каждый из m блоков 2 запоминающих регистров, где разрядность указанных двоичных слов увеличивается в два раза до максимальной величины n.

Принцип работы одного из блоков 2 запоминающих регистров, имеющего произвольный, например i-й, порядковый номер, под воздействием сигнала квантования, формируемого блоком 8 управления, более подробно поясняется с помощью фиг. 2 и 4. Блок 2-i запоминающих регистров содержит три одинаковых е/2-разрядных запоминающих регистра, имеющих информационные D-входы и входы С синхронизации (е=2i). Благодаря наличию инвертора 18 одинаковые регистры 17 записывают информацию по различным (положительным и отрицательным) перепадам импульсов квантования. В результате увеличения разрядности слов на выходе блока увеличивается также в два раза длительность, в течение которой эти слова существует на выходе блока. Вследствие этого для обеспечения работы следующего, (i+1)-го блока 2 запоминающих регистров может быть использована частота квантования, пониженная также в два раза. В результате требуемое число сигналов квантования с постепенно понижающейся частотой может быть получена наиболее простым способом, с наименьшими энергозатратами, а именно с помощью последовательных делителей 9 частоты следования импульсов задающего генератора 10 блока 8 управления. При этом устраняется необходимость применения распределителя импульсов, все разряды которого работают на самой высокой частоте квантования. Выходные сигналы делителей 9-1. . .9-(m-1)...9-К частоты также используются для формирования импульсов управления в реальном и трансформированном масштабе времени. Эти сигналы вырабатываются в блоке 8 управления, предназначенном для формирования управляющих импульсов и кодированных сигналов, обеспечивающих работу остальных блоков устройства.

Принцип работы блока основан на суммировании временных интервалов и делении частоты следования высокостабильных, высокочастотных импульсов, вырабатываемых задающим генератором 10. С выхода генератора 10, например, снимаются тактовые импульсы частотой 25 МГц для обеспечения длительности квантов реального времени 20 нс. Соответственно задающий генератор 10 может быть выполнен на микросхеме 530ГГ1 с подключенным кварцевым резонатором ([4], с. 271).

На фиг. 4 показан принцип формирования n=8-разрядных слов и импульсов управления реального и трансформированного масштабов времени для пояснения конкретной реализации предложенного принципа и специфических особенностей нового принципа работы предложенного технического решения, позволяющего существенно снизить потребляемую мощность. На диаграмме 24 показан короткий импульс синхронизации, поступающий на входную шину 7. Этот импульс устанавливает в определенное, а именно в единичное, состояние, показанное на диаграммах 29, 32 и 35, делители 9-1...9-3 частоты так же, как и все последующие. На диаграмме 25 условно цифрами, начиная с 1, показаны номера квантов задержки, которые должны быть преобразованы в восьмиразрядные слова. На диаграмме 34 показано первое сформированное слово, условно обозначенное цифрами 1. ..8. На диаграмме 27 показана информация, переписываемая по положительным фронтам первых импульсов квантования (диаграмма 26) и возникающая на информационных выходах запоминающего регистра 17-1 блока 2-1 в виде нечетных квантов задержки 1, 3, 5... Далее эта информация и входная информация одновременно переписываются по отрицательным фронтам импульсов квантования на выходы регистров 17-2 и 17-3, где формируются двухразрядные слова, обозначенные цифрами 1, 2, 3, 4 и т.д. на диаграмме 28. Следующий блок 2-2 запоминающих регистров уже с уменьшенной в два раза частотой квантования обеспечивает формирование аналогично блоку 2-1 четырехразрядных слов, как это показано на диаграммах 29...31. Уменьшение рабочей частоты позволяет выполнить блок 2-2 и в особенности последующие блоки на более низкочастотных элементах вычислительной техники, например серии 1554, потребление по питанию которых качественно отличается от быстродействующих элементов серии 530, что сразу же снижает мощность, потребляемую устройством задержки от источников питания, и определяет одну из возможностей, которые поясняются далее, повышения экономичности предложенного технического решения. Формирование восьмиразрядных слов показано на диаграммах 32...34. Первое слово 1. . . 8 (диаграмма 34) появляется через 12 квантов реального времени, т.е. через полтора периода выходного сигнала делителя 9-2 после поступления импульса синхронизации (диаграмма 24), что далее учитывается с помощью триггера 20 задержки (фиг. 3) в формирователе 12 импульсов управления реального масштаба времени, вырабатывающего импульсы разрешения записи-считывания и счетные импульсы для формирования с помощью счетчиков 15 и 16 импульсов кодированных адресов ОЗБ 3 и 4. Аналогичные импульсы, но в другом масштабе времени, увеличенном в С раз, и не имеющие указанной ранее задержки, вырабатываются формирователем 13 импульсов управления трансформированного масштаба времени. Формирование указанных импульсов осуществляется путем декодирования определенных состояний делителей 9-1...9-К частоты с помощью дешифраторов 22 и 23 формирователей 12 и 13, как это показано на фиг. 4.

Таким образом, на выходе блока 2-m формируется после поступления каждого импульса синхронизации на шину 7 M/n слов, т.е. n-разрядных значений кодов, являющихся цифровым эквивалентом входного сигнала за один период. Для задержки этой информации на период ее повторения указанные n-разрядные слова попеременно от периода к периоду записываются в ОЗБ 3 и 4, режим записи или считывания которых определяется сигналами противоположного логического значения (логические "0" или "1"), снимаемого с прямого или инверсного выхода счетного триггера 11, срабатывающего от фронта сигнала с шины 7, который может быть выполнен на микросхеме 1564ТМ2. В соответствии с рабочим режимом переключаются выходным сигналом счетного триггера 11 с помощью коммутатора 14 импульсов сигналы разрешения записи-считывания реального и трансформированного масштабов времени и счетные импульсы счетчиков 15 и 16, а также выходы их а+1 разрядов для сброса (выключения) в каждом периоде формирования импульсов управления. Коммутатор 14 импульсов может быть выполнен на мультиплексорах 1533КП11, на его информационные входы подаются указанные входные сигналы. Сигнал с выхода триггера 11 подается на управляющий вход мультиплексора.

ОВБ 3 и 4 предназначены для записи, хранения и считывания информации в виде n-разрядных слов (с. 214, [4]). Каждый из ОЗБ 3 и 4 поочередно от периода к периоду импульсов синхронизации на шине 7 работает в режиме записи или считывания и построен так (т.е. имеет определенную структуру), что имеет М/n строк. Каждая строка имеет свой а-разрядный двоичный номер, где а= log2 M/n. ОЗБ 3 и 4 могут быть выполнены на основе, например, микросхем серии 537. В этом случае каждый из них кроме адресных входов имеет управляющие входы записи-считывания (логический уровень "0" - запись, "1" - считывание) и вход разрешения записи-считывания. Как известно, ОЗБ разделяются на синхронные, на входах или выходах которых установлены дополнительные буферные запоминающие регистры, и асинхронные, в которых указанные регистры отсутствуют. Управление асинхронных ОЗБ упрощается, так как при считывании сигналы записи-считывания и разрешения можно подавать в виде постоянных логических уровней напряжения в соответствии с техническими условиями на конкретные используемые ОЗБ.

В случае использования микросхем серии 537 для построения ОЗБ 3 и 4 и n= 8 из фиг. 4 видно, что импульсы разрешения реального масштаба времени могут быть получены путем декодирования логических "1" (высокий уровень напряжения двоичных сигналов) сигналов, изображенных на диаграммах 29 и 32 (выходы делителей 9-1 и 9-2). Счетные импульсы для адресных счетчиков 15 и 16 в реальном масштабе времени при n=8, как видно из диаграмм фиг. 4, могут быть сформированы из импульсов на диаграмме 32.

Работа формирователя 12 импульсов реального масштаба времени заключается в следующем (фиг. 3). В исходном состоянии до прихода импульса синхронизации импульсы с выхода формирователя не выдаются, так как элементы И 21-1,2 выключены выходным сигналом триггера 20. Также в исходном, статическом состоянии находятся счетчики 15 и 16 импульсов, с младших а разрядов которых снимаются нулевые кодированные адресные сигналы для ОЗБ 3 и 4. При поступлении запускающего импульса синхронизации с шины 7 триггер 19 переключается в состояние, при котором снимается запрещающий сигнал с триггера 20, и он может переключаться и вырабатывать разрешающий сигнал для инверторов 21. Этот разрешающий сигнал с информационного входа D триггера 20 на его выход переписывается выходным сигналом делителя 9-3 (диаграмма 35), подаваемым на вход синхронизации С триггера 20. Через элементы И 21-1 и 21-2 начинают выдаваться импульсы разрешения и адресные счетные импульсы, сформированные с помощью дешифраторов 22 и 23, как это было показано ранее, на соответствующие входы счетчика 15 или 16 импульсов и ОЗБ 3 или 4 после коммутации с помощью коммутатора 14 импульсов. Таким образом выдается М/n счетных импульсов до переполнения счетчиков. При поступлении (M/n+1)-го счетного импульса а первых разрядов счетчика 15 или 16 устанавливаются в нулевое состояние, а на информационном выходе (а+1)-го разряда появляется логическая "1", которая через коммутатор 14 импульсов, поступая на вход R триггера 19 формирователя 12, возвращает его в исходное состояние.

Работа формирователя 13 импульсов управления трансформированного масштаба времени осуществляется аналогично работе формирователя 12. Для упрощенного случая при С=2, когда К=m, как это показано на фиг. 4, импульсы разрешения формируются путем декодированная логических "1" выходных сигналов делителей 9-2 и 9-3 частоты (диаграммы 32 и 35), и последние из указанных импульсов следует использовать в качестве счетных для счетчиков 15 и 16 при их поочередной работе в трансформированном масштабе времени.

Как указывалось, если ОЗБ 3 и 4 являются асинхронными, то в динамическом режиме работы формирователя 13 импульсов требуется только формирование счетных импульсов для изменения адресных сигналов на входах А ОЗБ 3 и 4 (с. 220, [4]).

Для преобразования n-разрядных кодированных сигналов, т.е. n-разрядных слов, с выходов ОЗБ 3 и 4 в последовательные кванты задержки предназначен блок 5 коммутаторов сигналов, принцип действия которого соответствует его наименованию. Преобразование осуществляется с использованием самых элементарных и соответственно малоэнергоемких операций с использованием управляющих сигналов, частоты которых уменьшены, т.е. трансформированы, в С раз, что является одной из реализованных возможностей существенного уменьшения мощности, потребляемой блоком от источника питания. При n=8 блок 5 коммутаторов сигналов может быть выполнен на мультиплексоре 1564КП7, на информационные входы которого подается информация с выходов ОЗБ 3 или 4, а на управляющие входы при С=2 - сигналы с выходов делителей 9-1...9-3 (диаграммы 29, 32 и 35 на фиг. 4).

Техническим преимуществом предложенного устройства для задержки сигналов является его существенно более высокая экономичность по потребляемой мощности от источника питания. Указанное преимущество достигнуто в результате использования нового принципа преобразования последовательных квантов задержки в многоразрядные двоичные слова, записи этих слов в ОЗБ, считывания слов и обратного преобразования в последовательные кванты задержки. Этот принцип реализуется с использованием наиболее простых и экономичных операций при максимально пониженных рабочих частотах преобразования и управления, при которых потребление от источников питания существенно снижается.

| название | год | авторы | номер документа |

|---|---|---|---|

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1992 |

|

RU2012014C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| УСТРОЙСТВО СОПРОВОЖДЕНИЯ ТРАЕКТОРИИ ДВИЖУЩИХСЯ ОБЪЕКТОВ | 1994 |

|

RU2079150C1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2017241C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С ВНЕШНИМ АБОНЕНТОМ | 1992 |

|

RU2084952C1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 2000 |

|

RU2170444C1 |

| УСТРОЙСТВО СЧИТЫВАНИЯ ИНФОРМАЦИИ ДЛЯ ТРАНСПОРТНОГО СРЕДСТВА | 1994 |

|

RU2083411C1 |

Использование: импульсная техника. Сущность изобретения заключается в том, что последовательные кванты задержки преобразуют в разрядные слова до максимальной задержки n = 4,8,16 за m операций, где m = log2n увеличивая за каждую операцию разрядность каждого слова в 2 раза, при этом частоту квантования понижают также в 2 раза, и обратное преобразование осуществляют коммутацией сигналов отдельных разрядов слоев с пропорционально пониженными частотами преобразования в трансформированном масштабе времени. 3 з.п.ф-лы, 4 ил.

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Пухальский Г.И., Новосельцева Т.Я | |||

| Проектирование дискретных устройств на интегральных микросхемах | |||

| Справочник | |||

| - М.: Радио и связь, 1990. | |||

Авторы

Даты

1994-11-30—Публикация

1992-07-07—Подача