Область техники

В соответствии с первым аспектом настоящее изобретение относится к способу и системе для синхронизации в коммутаторе ячейки передачи пользовательских элементов данных, которые могут включать в себя различные числа битов данных, между портами коммутатора и ядром (центральной частью) коммутатора посредством двусторонней линии связи.

В соответствии со вторым аспектом изобретение относится к системе для синхронизации в системе передачи данных, передачи данных в форме потока битов между функциональными элементами двусторонней линии связи, причем битов между функциональными средствами, которыми являются порт коммутатора и ядро коммутатора, двусторонней линии связи, причем каждый функциональный элемент имеет средства для ввода данных, приходящих данных, в зависимости от размера соответствующих пользовательских данных.

Во многих системах передачи данных различные функциональные элементы связаны между собой линией связи. В частности, это имеет место в телекоммуникационных системах. Стоимость канала связи во многих случаях зависит от числа физических межсоединений. Чем больше число межсоединений, тем выше должна быть стоимость. Поэтому обычной практикой является ввод всей требуемой информации в одно физическое соединение, осуществляющее передачу цифрового сигнала. Это приводит к необходимости восстановления логической структуры на приемном конце линии связи. Для выполнения этого необходимо передавать информацию, в неявном виде указывающую на структуру на различных уровнях.

Примерами такой неявной информации, которая кодируется в цифровом сигнале, являются тактовый сигнал, который обеспечивает выравнивание битов, и синхронизирующая комбинация данных, которая обеспечивает выполнение выравнивания байтов, кодовых слов, элементов данных режима асинхронной передачи (РАП элементов данных) или любых других структур данных более высокого уровня, чем биты.

Предшествующий уровень техники

Синхронизация в аспекте передачи РАП элементов данных приводит к проблемам, в частности, в случае наличия элементов данных различного размера.

Линия связи для передачи РАП элементов данных использует механизм синхронизации элементов, основанный на так называемом поле коррекции ошибки заголовка (поле КОЗ) в РАП элементе данных и на соответствующей последовательности обработки. Некоторая форма вычислений, обозначаемая КСЗ (контрольная сумма заголовка), основывается на четырех байтах отсчета и на остатке, включаемом в поле КОЗ. Последовательность обработки основывается на использовании конечного автомата, имеющего состояния ПОИСК (поиск), ПРЕСИН (предварительная синхронизация) и СИН (синхронизация). Хорошо известный конечный автомат, подходящий для использования в таких целях, описан в документе Bellcore FA-NWT-001109. Корректное вычисление контрольной суммы КСЗ переводит конечный автомат в состояние ПРЕСИН. При условии, что в этом состоянии появятся шесть последовательных корректных вычисленных значений контрольной суммы КСЗ, будет выполнен переход в состояние СИН, в противном случае осуществляется переход в состояние ПОИСК. После того как в состоянии СИН будут иметь место семь последовательных некорректных вычислений контрольной суммы КСЗ, аналогичным образом произойдет переход в состояние ПОИСК.

Существенным недостатком при использовании такого автомата ограниченных состояний, работающего без поддержки стороны, являющейся источником, являются затраты времени на достижение состояния синхронизации и соответственно потеря элементов данных при потере синхронизации. Более 60 элементов данных могут быть потеряны, прежде чем линия связи будет приведена в рабочее состояние. Другим недостатком является то, что рассматриваемый способ не обеспечивает возможность передачи по линии связи элементов данных различных размеров.

В патенте США N 5123013 описана синхронизация элементов данных системы связи с пакетной передачей данных, предназначенной для передачи и приема последовательности элементов данных, состоящей из элементов данных фиксированной длины, включающих передаваемые данные. По меньшей мере, один элемент синхронизации, содержащий комбинацию синхронизации (синхрокомбинацию), вводится между элементами данных.

Элемент или элементы синхронизации передаются в определенных ситуациях, например в течение периода времени, когда не передаются элементы данных, или после того, как элементы информационных данных успешно переданы в течение предварительно определенного интервала после передачи элемента синхронизации.

В патентном документе GB 1550121 описана система декодирования цифровых данных, характеризуемая допуском на скорость передачи данных. Цифровые кодовые слова запоминаются в элементах данных примерно одинаковой длительности, за исключением начального элемента каждого кодового слова, которое называется синхроэлементом и имеет удвоенную длительность.

В патентном документе DE 3842371 описано устройство, предназначенное для тактовой синхронизации цифрового сигнала, структурированного в элементы данных.

Сущность изобретения

Задача изобретения состоит в создании способа, обеспечивающего выравнивание элементов данных в потоке битов, содержащем элементы данных различного размера. В принципе, эта задача решается в соответствии с изобретением путем использования быстродействующего алгоритма синхронизации, основанного на малых элементах данных синхронизации и на использовании соответствующих устройств на каждом конце двусторонней линии связи.

В способе согласно первому аспекту изобретения передача данных по линии связи инициируется и контролируется посредством элементов данных синхронизации (синхроэлементов), которыми обмениваются функциональные элементы и каждый из которых содержит, с одной стороны, синхрокомбинацию, посредством которой можно идентифицировать синхроэлемент, и, с другой стороны, данные управления. Функциональные элементы могут установить данные управления на значения, обеспечивающие взаимную проверку, что синхронизация превалирует, либо на значение, которое при состоянии работы линии связи, воспринимаемом как означающее потерю синхронизма, вынуждает функциональные элементы системы принимать меры для восстановления синхронизма.

В системе согласно первому аспекту изобретения функция управления линией связи включена в каждый функциональный элемент, содержащий функции для начала и управления передачей данных на линии связи посредством сннхроэлементов, которыми производится обмен между функциями управления линии связи, управляемыми конечным автоматом синхронизации, который имеет три состояния. В состоянии ПОИСК функция управления линией связи осуществляет анализ синхроэлемента, приходящего из линии связи, для определения того, совпадает ли он с предварительно определенной комбинацией для синхроэлементов. В состоянии ПРЕСИН, которому предшествует совпадение синхроэлемента с предварительно определенной комбинацией, найденной в состоянии ПОИСК, функция управления линией связи обеспечивает анализ предварительно определенного числа последовательных синхроэлементов, приходящих после этого, для определения того, совпадают ли они с предварительно определенной комбинацией. Возврат в состояние ПОИСК выполняется в том случае, если указанное не имеет места. В состоянии СИН, которому предшествует совпадение предварительно определенного числа синхроэлементов с предварительно определенной комбинацией в состоянии ПРЕСИН, допускается передача данных по линии связи при осуществлении контроля данных на предмет обнаружения ошибок. Переход в состояние ПОИСК выполняется, если обнаружена ошибка.

В системе согласно второму аспекту изобретения функция управления линией связи включена в каждый из функциональных блоков с функциями инициирования и управления передачей данных по линии связи с помощью синхроэлементов, которыми осуществляется обмен между функциями управления линией связи и каждый из которых включает в себя, с одной стороны, информацию идентификации, посредством которой синхроэлементы могут быть идентифицированы, и, с другой стороны, данные управления. Каждая функция управления линией связи может задать для данных управления такие значения, которые означают при взаимной проверке, что синхронизм имеет место, или значение, которое в некотором рабочем состоянии линии связи, воспринимаемом как означающее потерю синхронизма, вынуждает обе функции управления линией связи предпринимать меры по восстановлению синхронизма. Функция выхода в линию связи имеет функцию ввода синхроэлемента, которая получает поток элементов данных пользователя и вводит в него синхроэлементы; первая функция преобразования принимает результирующий поток, состоящий из элементов данных пользователя и синхроэлементов, и преобразует его в сигнал потока битов, который тактируется 1-битовым тактовым сигналом для передачи по линии связи. Функция входа из линии связи содержит вторую функцию преобразования, которая принимает сигнал потока битов, приходящий из линии связи, и преобразует его в n-битовый параллельный формат, который обычным образом тактируется на каждый n-ый бит n-битовым тактовым сигналом от функции входа. Функция сравнения имеет связь для поиска и идентификации в n-битовом параллельном формате информации идентификации синхроэлемента и при ее нахождении передает сигнал подтверждения. Функция тактирования обеспечивает тактирование каждого бита с использованием 1-битового тактового сигнала из n-битового параллельного формата от функции входа. Конечный автомат синхронизации принимает сигнал подтверждения для управления переходом от тактирования n-битовым параллельным форматом с использованием n-битового тактового сигнала к тактированию 1-битовым тактовым сигналом.

Важные преимущества изобретения состоят в обеспечении высокоскоростной синхронизации и в том, что обеспечивается обработка элементов данных различных размеров.

Описание чертежей

Изобретение ниже описывается более подробно со ссылками на иллюстрирующие его чертежи, на которых показано следующее:

Фиг. 1 - схематичное представление коммутатора телекоммуникационной системы, предназначенного для использования линейных соединений режимов асинхронной передачи (РАП) и синхронной передачи (РСП), в котором может быть использовано изобретение;

Фиг. 2 - более детальное представление в увеличенном масштабе фрагмента коммутатора по фиг. 1, включая двустороннюю линию связи между портом коммутатора и центральной частью коммутатора, иллюстрирующее некоторые основные аспекты изобретения;

Фиг. 3 - диаграмма состояний синхронизации для конечного автомата синхронизации, используемого для синхронизации элементов данных, выполняемой в соответствии с изобретением, в линии связи, согласно фиг.2;

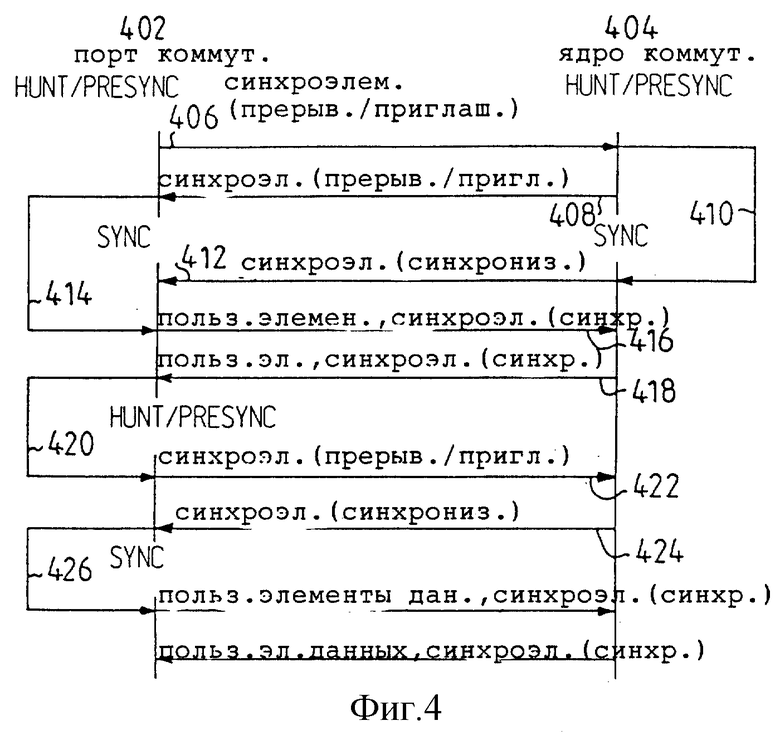

Фиг. 4 - диаграмма состояний перехода между портом коммутатора и центральной частью коммутатора при использовании конечного автомата синхронизации согласно фиг. 3 для возможного на практике сценария синхронизации;

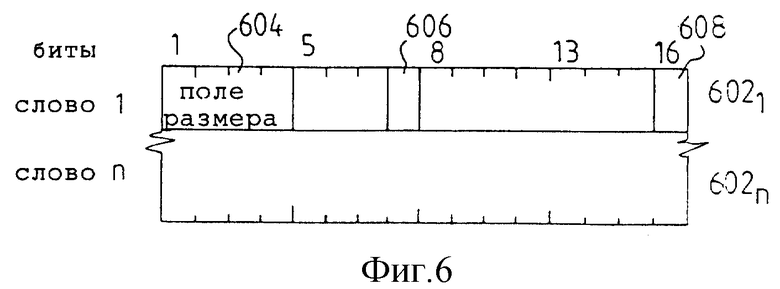

Фиг. 5 и 6 - примеры вариантов осуществления элемента данных синхронизации (синхроэлемента) и элемента данных пользователя соответственно;

Фиг. 7 - функциональная диаграмма варианта осуществления системы управления линией связи, соответствующей изобретению, в том виде, как она включена в состав каждого порта и центральную часть коммутатора по фиг. 3;

Фиг. 8 - функциональная диаграмма части системы управления линией связи согласно фиг.7, показанная более детально;

Фиг. 9 - упрощенная диаграмма состояний синхронизации для конечного автомата синхронизации, используемого для выполнения синхронизации элементов данных в соответствии с изобретением;

Фиг. 10 - диаграмма состояний перехода между портом коммутатора и центральной частью коммутатора при использовании конечного автомата синхронизации согласно фиг.9 для возможного на практике сценария синхронизации;

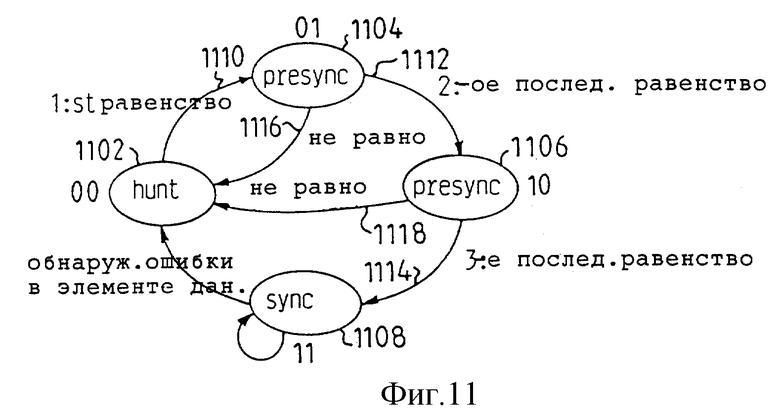

Фиг. 11 - более детальная диаграмма состояний синхронизации для конечного автомата синхронизации, используемого в варианте осуществления системы управления линией связи, согласно изобретению, как описано выше со ссылками на последующие чертежи;

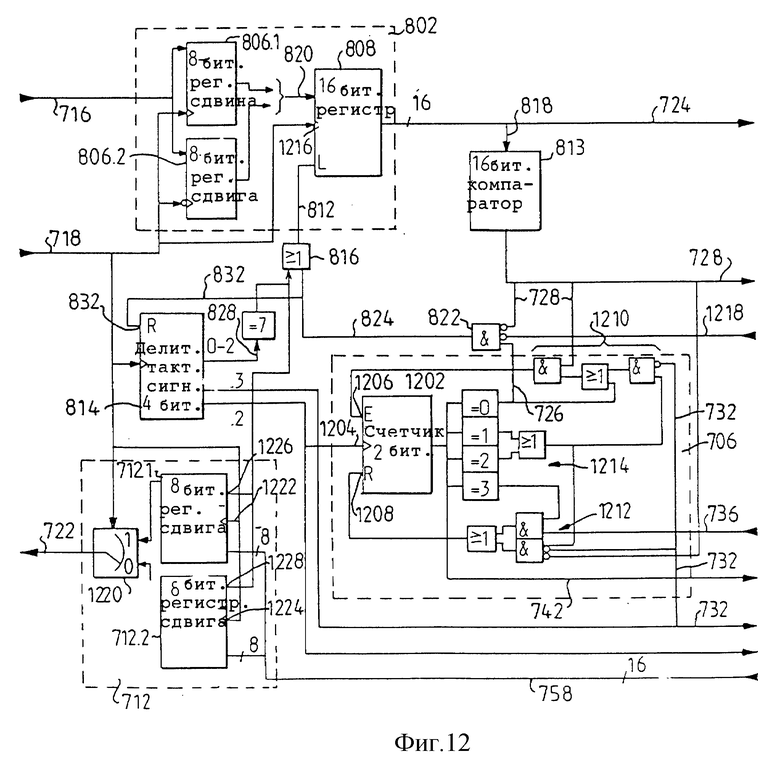

Фиг. 12 - функциональная диаграмма функции управления линией связи, в которую включен конечный автомат синхронизации согласно фиг. 11;

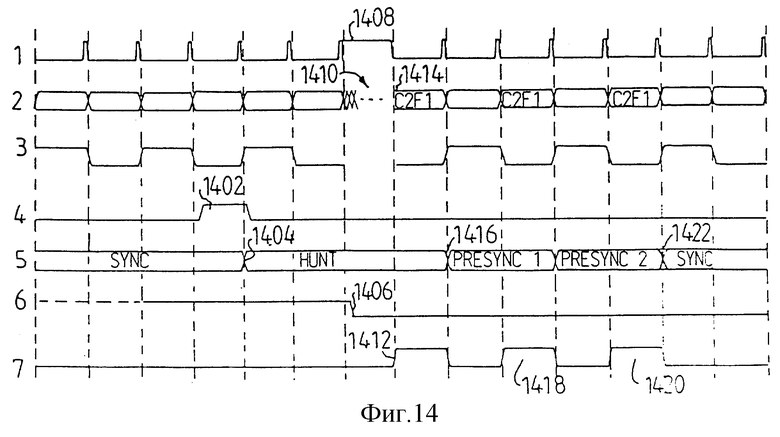

Фиг. 13 и 14 - временные диаграммы управления для примеров процедур синхронизации линии связи в системе управления линией связи по фиг. 13.

Предпочтительные варианты осуществления изобретения

На фиг. 1 показан коммутатор телекоммуникационной системы, предназначенный для соединения линий связи, предназначенных для работы в режимах РАП (асинхронный режим передачи) и РСП (синхронный режим передачи). Коммутатор содержит множество портов 1021-102n, соединенных с центральной частью (ядром) 104 коммутатора посредством каждой из двусторонних линий связи 1061-106n. Порты 102 коммутатора соединены, например, с коммуникационной сетью, которая может содержать, например, входящие линии 107 и 108, процессоры и т.п. Линии 107 и 108 могут предназначаться для передачи РАП элементов данных или временных интервалов РСП - передач. Порты 1021 и 1022 коммутатора показаны схематично в качестве примера как расположенные на схемной плате 1101 интерфейса линии для РСП-линии передачи и на схемной плате 1102 интерфейса линии для РАП-линии передачи соответственно. Схемные платы 1021 и 1022 интерфейсов линий показаны схематично как содержащие соответствующую линейную нагрузку 1121 и 1122, каждая из которых через соответствующую линию связи 1141 и 1142 для пользовательских данных соединена с соответствующим портом 1021 и 1022 коммутатора соответственно. Порт 102n коммутатора схематично показан в качестве примера как расположенный на плате сервера 110n, которая включает процессор 116, соединенный с портом коммутатора через линию связи 114n для пользовательских данных.

На фиг. 2 более детально показан двусторонний трафик между, например, портом 102n коммутатора и ядром 104 коммутатора посредством линии связи 106n. Порт 102n коммутатора использует приходящие пользовательские данные в виде элементов данных пользователя. Размер этих элементов данных пользователя выбирается так, чтобы соответствовать передаваемым пользовательским данным. Для РАП элемента данных из 53 байтов может быть выбран размер элемента данных 56 байтов, т.е. 53 байта плюс информация о размере элемента данных плюс контрольные суммы. Временные интервалы РСП-передач используются при малых элементах данных. Элемент данных пользователя затем передается с порта коммутатора к другому порту коммутатора через ядро коммутатора. Более детальное описание данного способа применения пользовательских данных в виде элементов данных и различные случаи в данном контексте содержатся в заявке на патент Швеции N 9402051-8.

Порт 102n коммутатора содержит функциональное средство 202 управления линией связи, которое принимает элементы данных пользователя, основанные на пользовательских данных, приходящих извне для передачи по линии связи 106n, и передает элементы данных пользователя, приходящие из линии связи, информационные данные которых должны передаваться вовне, например в сеть, как показано двойной стрелкой 204. Канал трафика между портом 102n коммутатора и ядром 104 коммутатора реализуется между функциональным средством 202 управления линией связи и функциональным средством 206 управления линией связи в ядре коммутатора. Функциональные средства 202 и 206 управления линией связи управляют синхронизацией элементов данных, как будет описано более подробно ниже.

Элементы данных различных размеров передаются по линии связи в виде потока битов в обоих направлениях, эти потоки битов схематично показаны позициями 208 и 210. В потоках битов 208 и 210 элементы данных пользователя обозначены как 212 и 214 соответственно. При этом информация, относящаяся к началу элемента данных, в явном виде не передается. Поэтому обе стороны должны выполнить выравнивание элемента данных для синхронизации линии связи. Для этой цели используются элементы данных синхронизации, которые должны быть введены в поток пользовательских данных. В потоках битов 208 и 210 синхроэлемент обозначен в качестве примера как 216 и 218 соответственно. Синхроэлементы инициируются и завершаются в функциональных средствах 202 и 206 управления линией связи соответственно на каждой стороне, т.е. они не проявляются в портах коммутатора и в ядре коммутатора вне функциональных средств управления линией связи. Элементы данных пользователя передаются без какого-либо воздействия на них функциональными средствами управления линией связи. Осуществление и метод работы функциональных средств управления линией раскрыты в нижеследующем описании вариантов осуществления изобретения.

На фиг. 3 показана диаграмма состояний синхронизации, иллюстрирующая способ работы конечного автомата состояний для реализации функций управления линией связи на каждой стороне линии связи, который используется для синхронизации линии связи. Синхроэлементы, приходящие из линии связи и поступающие в функциональное средство управления линией связи, сравниваются с предварительно определенной комбинацией для синхроэлементов. Первое обнаруженное совпадение между приходящим синхроэлементом и предварительно определенной комбинацией вынуждает конечный автомат перейти согласно стрелке 302 в состояние 304 ПРЕСИН. При условии, что после этого обнаружены два последовательных синхроэлемента в состоянии ПРЕСИН, что указывает на совпадение с предварительно определенной комбинацией, осуществляется переход по стрелке 306 в состояние 308 СИН, в противном случае переход осуществляется по стрелке 310 в состояние 312 ПОИСК. В состоянии СИН может осуществляться передача элементов данных пользователя. Каждый элемент данных пользователя должен включать в себя информацию, обеспечивающую поддержание синхронизации элемента данных, а также иметь коды ошибок, обеспечивающие возможность обнаружения ошибки в размере элемента данных. Обнаруженная ошибка в состоянии 308 СИН аналогичным образом переводит конечный автомат в состояние 312 в соответствии со стрелкой 314. Для гарантии истинности состояния СИН, если коды ошибок в элементах данных пользователя не могут быть рассмотрены как достаточные, к состоянию СИН может быть добавлен конечный автомат контроля. Эта функция контроля обуславливает переход конечного автомата в состояние 312 согласно стрелке 314, если обнаружено предварительно определенное число n последовательных элементов данных пользователя. Более детальная информация в связи с вышеупомянутым относительно конструкции и полезных свойств элементов данных пользователя содержится в вышеуказанной заявке на патент Швеции N 9402051-8.

Для достижения быстрой синхронизации и для поддержания линии связи в рабочем состоянии требуется, чтобы блок управления линией связи на стороне, принимающей элементы данных пользователя, мог передавать данные управления в синхроэлементах по линии связи, предназначающиеся для управления линией связи на стороне, являющейся источником передаваемых данных.

Примерами таких данных управления (команд) и обусловленных этим мероприятий, которые могут проявиться в блоке управления линией связи на стороне, являющейся источником передаваемых данных, являются следующие:

1. Данные управления: прекращение. Означает команду для блока управления линией связи на стороне источника передачи остановить текущую передачу пользовательских элементов данных и вместо этого передавать синхроэлемент. Текущая передача синхроэлементов должна быть после этого завершена и введен новый синхроэлемент.

2. Данные управления: приглашение. Указывает, что имеет место состояние СИН и означает команду блоку управления линией связи на стороне источника передачи на повторное введение синхроэлемента в первый подходящий момент времени. Более конкретно, повторный синхроэлемент должен быть введен в обычный поток элементов данных с наименьшим возможным возмущением для нормального режима работы.

3. Данные управления: синхронизация. Указывает, что не требуется введение синхроэлемента со стороны источника передачи.

Использование указанных выше трех видов данных управления или команд будет пояснено ниже со ссылками на фиг. 5. 6 и 7.

Команда прерывания может быть заменена на команду приглашения, как будет пояснено ниже при описании со ссылками на фиг. 5. Результатом будет несколько более медленное достижение синхронизации, если в данный момент времени передается большой пользовательский элемент данных.

Для конечного автомата применимы следующие правила перехода для синхроэлементов:

1. Состояние ПОИСК/ПРЕСИН. Соответствует передаче стороне, являющейся источником передаваемых данных, синхроэлементов, содержащих команду прерывания или приглашение. Синхроэлемент должен передаваться в первый подходящий момент времени без прерывания текущей передачи элементов данных.

2. Состояние СИН. Соответствует передаче пользовательских элементов данных или передаче синхроэлементов, если принята команда прерывания или приглашение. Если обратно вводятся синхроэлементы, то они обычно будут содержать данные управления синхронизации.

На фиг. 4 схематично показана диаграмма состояний простых переходов между портом 402 коммутатора и ядром 404 коммутатора для возможного сценария синхронизации.

Вначале обе стороны находятся в любом из состояний ПОИСК и ПРЕСИН. Соответственно они передают синхроэлементы с данными управления "приглашение" или "прерывание", как показано стрелками 406 и 408 соответственно. Спустя определенное число последовательных синхроэлементов обе они переходят в состояние СИН. В показанном примере сторона, соответствующая ядру 404 коммутатора, переходит в состояние СИН согласно стрелке 410 раньше, чем порт коммутатора. Поэтому ядро коммутатора реагирует на синхроэлементы с данными управления "прерывание"/"приглашение" передачей синхроэлемента с данными управления "синхронизация" (стрелка 412). Порт 402 коммутатора затем переходит в состояние синхронизации, что показано стрелкой 414. Порт коммутатора знает, что ядро коммутатора уже находится в состоянии СИН и поэтому разрешает передачу пользовательских элементов данных, как показано стрелкой 416. Ядро 404 коммутатора, принимающее теперь пользовательские элементы данных, может, в свою очередь, разрешить передачу пользовательских элементов данных (стрелка 418). С этого момента линия связи находится в рабочем состоянии на обоих сторонах и будет сохранять это состояние до тех пор, пока любая из сторон не перейдет в состояние ПОИСК вследствие обнаружения ошибки или ввода в действие функции контроля.

В рассматриваемом примере порт 402 коммутатора подвергается некоторому воздействию и переходит в состояние ПОИСК согласно стрелке 420. Затем порт коммутатора передает синхроэлемент с данными управления "прерывание"/"приглашение", как показано стрелкой 422. Ядро 404 коммутатора должно реагировать путем передачи синхроэлементов, содержащих данные управления "синхронизация" вместо пользовательских элементов данных, как показано стрелкой 424. После передачи требуемого числа последовательных синхроэлементов порт коммутатора восстанавливает состояние СИН (стрелка 426).

При нормальном режиме работы обе стороны линии связи могут проверять друг друга, находятся ли они действительно в состоянии СИН. Это может быть осуществлено путем регулярной передачи синхроэлементов с данными управления "приглашение". Другая сторона должна реагировать в пределах предварительно определенного интервала времени синхроэлементом с данными управления "синхронизация". Если этого не происходит, то можно предположить, что она находится в состоянии ошибочной синхронизации некоторого рода. Синхронизация может быть, например, потеряна, но это не обнаруживается вследствие наличия корректной комбинации данных в пользовательских элементах данных на тех их позициях, где выполняется анализ элемента данных, и это состояние может превалировать в течение длительного периода времени. Правильным действием в случае, если в обратной передаче не появляется синхроэлемент, является остановка передачи пользовательских элементов данных и перевод другой стороны в состояние синхронизации. Описанный способ может завершать или заменять ранее описанную функцию контроля.

Первый вариант осуществления системы управления линией связи в соответствии с изобретением будет описан ниже более подробно со ссылками на фиг. 5-8.

Для достижения быстрой синхронизации синхроэлемент должен быть соответственно по возможности меньше, но вместе с тем достаточно большим, чтобы получить комбинацию, которая маловероятна для нахождения в пользовательских элементах данных за непрерывный интервал времени. На фиг. 5 показан пример реализации синхроэлемента. Размер синхроэлемента ограничен двумя словами 502 и 504. Все коды даны в тетрабинарной форме. Первое слово 502 содержит комбинацию синхронизации (синхрокомбинацию) в виде шестнадцатиричного значения C2F1. Второе слово 504 содержит данные управления "синхронизация" и "приглашение", последнее в этом случае заменило "прерывание", эта возможность упомянута как альтернатива. Соответственно главной альтернативе поле данных управления 504 на фиг. 5 может поэтому включать, помимо двух типов указанных данных управления "синхронизация" и "приглашение", также данные управления "прерывание". На фиг. 5 коды 0100 и 0200 показаны в качестве примера для данных управления "синхронизация" и "приглашение" соответственно.

Направление передачи соответствует от бита 1 к биту 16 и от кода 1 к коду 2. Старший по значимости бит поля передается первым. Крайний правый бит является наименьшим по значимости битом. Показанные комбинации синхронизации приведены лишь для примера; могут использоваться также другие коды. Синхрокомбинация вместе с кодами управления выбирается так, чтобы обеспечить однозначное определение начальной позиции в синхроэлементе в последовательности синхроэлементов. Коды управления выбираются с Хэмминговым расстоянием два. Также могут применяться и другие коды.

На фиг. 6 показан пользовательский элемент данных, содержащий ряд слов 6021 - 602n. Поле размера 604 содержит коды для различных предварительно определенных размеров с избыточным кодированием для обеспечения обнаружения ошибок. Этот способ хорошо известен в технике и может быть основан на коде Хэмминга или ином коде. Пользовательский элемент данных также содержит два бита проверки на четность 606 и 608. Дополнительные сведения о кодировании содержатся в вышеупомянутой заявке на патент Швеции 9402051-8. Не допустимо использовать код, подобный коду синхроэлемента. Если возникает ошибка в поле размера или в битах проверки четности, то конечный автомат согласно фиг. 3 переходит в состояние ПОИСК 312.

На Фиг.7 показана блок-схема функционального средства управления линией связи, которая в общих чертах описана выше со ссылками на Фиг.2 и которая включена в каждый порт коммутатора и в ядро коммутатора. Как и на Фиг.2, обозначение 206 использовано на Фиг.7 для линии связи между двумя функциональными средствами управления линией связи, а обозначение 204 - для потока пользовательских элементов данных к функциональному средству управления линией связи и от нее. На Фиг. 7, однако, предусмотрено подразделение, при котором поток пользовательских элементов данных от функционального средства управления линией связи обозначен 204f, а поток пользовательских элементов данных к функциональному средству управления линией связи обозначен 204t. Функциональное средство управления линией связи включает в себя функциональный блок 702 последовательно/параллельного преобразования и выравнивания синхроэлементов, функциональный блок 704 анализа элементов данных, конечный автомат 706 синхронизации, функциональный блок 708 ввода синхроэлементов, функциональное средство тактирования (тактовый генератор) 710 и параллельно/последовательный преобразователь 712. Функция конечного автомата синхронизации 706 может быть реализована согласно Фиг.4.

В линии связи 106 между портом коммутатора и ядром коммутатора сигнал потока битов и тактовый сигнал битов передаются в каждом направлении, показанном стрелками 716 и 718 для направления приема и стрелками 720 и 722 для направления передачи соответственно. Функциональный блок последовательно/параллельного преобразония и выравнивания 702 синхроэлементов принимает поток битов 716 и преобразует его в 16-разрядные данные в параллельном коде, которые передаются в виде потока кодовых слов 724 на функциональный блок анализа 704 элементов.

Всякий раз, когда состояние ПОИСК является истинным для конечного автомата 706 синхронизации, он передает сигнал поиска 726 на функциональный блок последовательно/параллельного преобразования и выравнивания 702 синхроэлементов, вынуждая его осуществлять поиск комбинации синхроэлемента для каждой позиции битов (фиг. 5). При обнаружении этой комбинации функциональный блок 702 передает сигнал совпадения синхронизации 728 на конечный автомат 706 синхронизации и сигнал начала синхронизации 730 на функциональный блок анализа 704 элементов. Сигнал совпадения синхронизации 728 переводит конечный автомат синхронизации 706 в состояние ПРЕСИН и блокирует сигнал поиска 726. Сигнал начала синхронизации 730, который находится в активном состоянии только при активном состоянии сигнала поиска, указывает функциональному блоку анализа 704 элементов, что синхроэлемент обнаружен.

Функциональный блок последовательно/параллельного преобразования и выравнивания 702 синхроэлементов затем переходит в параллельный режим и тактирует приходящий поток битов 716 по каждому слову. Каждое слово указывается сигналом тактирования 732 слов функциональному блоку анализа 704 элементов. Функциональный блок последовательно/параллельного преобразования и выравнивания 702 синхроэлементов передает сигнал совпадения синхронизации 728 конечному автомату синхронизации всякий раз, когда он идентифицирует синхрокомбинацию.

Функциональный блок анализа 704 ячеек содержит внутренний счетчик размера элемента (не показан), который запускается при приеме сигнала начала синхронизации 730. Счетчик тактируется сигналом тактирования слов 732. Когда размер элемента данных будет отсчитан в обратном направлении, функциональный блок анализа 704 элементов передаст на конечный автомат синхронизации 706 сигнал 734 нового элемента, который указывает, что ожидается новый элемент. Функциональный блок анализа 704 элементов исследует новый элемент для проверки, имеет ли он допустимый формат в поле размера. Недопустимый код приводит в результате к передаче сигнала ошибки 736 на конечный автомат синхронизации 706. Сигнал ошибки 736 переводит конечный автомат синхронизации 706 в состояние поиска.

Функциональный блок анализа 704 элементов передает (по стрелке 204f) полученные пользовательские элементы данных для последующей обработки в порте коммутатора и в ядре коммутатора соответственно. Синхроэлемент загружается в функциональный блок анализа 704 элементов. Данные управления синхроэлемента выделяются и, если указано приглашение (как описано выше со ссылками на фиг. 3 и 5), сигнал приглашения 740 передается на функциональный блок ввода синхроэлемента 708. Неизвестный код управления приводит к передаче сигнала ошибки 736 на конечный автомат синхронизации 706.

Последовательность функций конечного автомата синхронизации 706 вытекает из диаграммы состояний соответственно фиг. 3. Справедливы следующие правила: если сигнал совпадения синхронизации 728 появляется в состоянии ПОИСК, то оно будет переведено в состояние ПРЕСИН. Сигнал нового элемента 734 вместе с сигналом совпадения синхронизации 728 обусловит переход в состояние СИН после двух последовательных синхроэлементов. Если используется функция контроля, она будет сбрасываться каждым сигналом нового элемента 734 вместе с сигналом совпадения синхронизации 728. Запуск функции контроля переводит конечный автомат синхронизации в состояние ПОИСК. Конечный автомат синхронизации 706 передает сигнал поиска 726 на функциональный блок последовательно/параллельного преобразования и выравнивания 702 синхроэлементов всякий раз, когда он находится в состоянии ПОИСК, и синхросигнал 742 на функциональный блок 708 ввода синхроэлемента всякий раз, когда он находится в состоянии ПОИСК.

Функциональный блок 708 ввода синхроэлемента использует синхросигнал 742 для генерирования в генераторе 744 кода управления в исходящих синхроэлементах и для передачи обязательных синхроэлементов 746 на функциональный блок 748 коммутации синхроэлементов и пользовательских элементов данных, когда синхросигнал деактивирован (указывая состояние ПОИСК или ПРЕСИН). В функциональном блоке 748 синхроэлемент 746 вводится в поток 750 пользовательских элементов данных, когда появляется сигнал приглашения 740.

Поток элементов данных 750 берет начало из блока ОПП 752 (обработки в порядке поступления), в котором пользовательские элементы данных, поступающие, в соответствии с ошибкой в потоке 204t, в функциональный блок 708 ввода синхроэлементов, останавливаются, когда синхроэлемент вводится в функциональный блок коммутации 748. Функциональный блок 708 ввода синхроэлементов использует тактовый сигнал с тактового генератора 710 для управления его логикой (стрелка 756).

Параллельно/последовательный преобразователь 712 принимает данные в формате слов (стрелка 758) и создает последовательный поток битов, образующий исходящий поток битов 722 для передачи по линии связи 206 на порт коммутатора и на ядро коммутатора соответственно со скоростью, определенной (стрелка 760) тактовым генератором 710.

Тактовый генератор 710 устанавливает тактовый сигнал битов и тактирует блоки 722 потока битов в исходящем направлении. Тактовый генератор 710 мог бы использовать тактовый сигнал 718 входящего потока битов для обеспечения одной и той же скорости в обоих направлениях, как показано пунктирной линией 762. В этом случае другая сторона должна иметь задающий тактовый генератор и генерировать тактовый сигнал, в то время как сторона, использующая приходящий тактовый сигнал битов 718 для тактирования исходящего потока битов 722, является ведомой. В этом случае ведомая сторона не должна передавать тактовый сигнал 720 в линию связи 106.

На фиг. 8 показан более детально функциональный блок 702 последовательно/параллельного преобразования и выравнивания синхроэлементов. В частности, он показан в виде разделенного на последовательно/параллельный преобразователь 802 и функциональный блок 804 выравнивания синхроэлементов, а также поясняется внутренняя логика.

Последовательно/параллельный преобразователь 802 содержит 16-битовый сдвиговый регистр 806 и 16-битовый регистр 808, Управляемый тактовым сигналом битов 818, 16-битовый сдвиговый регистр 806 преобразует входящий поток битов в 16-битовый параллельный формат 810. Как будет пояснено ниже, 16-битовый регистр нормально тактируется выравнивающим тактовым сигналом 812 на каждый 16-ый тактовый импульс битов для завершения последовательно/ параллельного преобразования и на каждый тактовый импульс битов в процессе поиска синхрокомбинации.

Функциональный блок 804 выравнивания синхроэлементов содержит компаратор 813, делитель тактового сигнала битов 814, выполненный в виде 4-битового счетчика, мультиплексор 816 с некоторой комбинаторной логикой. Компаратор 813 соединен с выходом регистра 808 для определения того (стрелка 818), когда в потоке слов 724 появится шестнадцатеричная комбинация C2F1. При обнаружении этого события компаратор 813 передает сигнал совпадения синхронизации 728, ниже называемый также сигналом равенства, на конечный автомат синхронизации 706 (см. фиг. 7). Сигнал совпадения синхронизации 728, умноженный на сигнал поиска 726, образует сигнал запуска синхронизации 730. Это показано функцией И 820, два входа которой подсоединены для приема сигнала совпадения синхронизации 728 и сигнала поиска 726 соответственно, а на выходе которого формируется сигнал запуска синхронизации 730 при появлении как сигнала совпадения синхронизации, так и сигнала поиска.

Инвертированный сигнал совпадения синхронизации 728, умноженный на сигнал поиска 726, управляет мультиплексором 816. Это обозначено функцией И 822, один вход которой подсоединен для приема сигнала поиска 726, а другой, инвертированный, вход подсоединен для приема сигнала совпадения синхронизации 728. Выход 824 функционального блока И 822 подсоединен для управления мультиплексором 816. Мультиплексор 816 подсоединен для приема тактового сигнала битов 718 и выходного сигнала 828 с выхода схемы И 829, на входах которой принимается каждый из четырех битов, появляющихся на выходе счетчика 814. Если поступает сигнал поиска 726, но отсутствует сигнал совпадения синхронизации 728, т.е. на выходе схемы И 822 имеется высокий логический уровень, то тактовый сигнал битов 718 выбирается мультиплексором 816 в качестве тактового сигнала выравнивания на тактовом входе 812 регистра 808. Если поступают оба сигнала, т.е. сигнал поиска 726 и сигнал совпадения синхронизации 728, на выходе функции И 822 устанавливается низкий логический уровень, и сигнал 828, полученный с делителя 814 тактового сигнала битов, выбирается в качестве тактового сигнала выравнивания. Этот полученный тактовый сигнал действует на каждый 16-ый такт времени.

Четырехбитовый счетчик делителя 814 тактового сигнала битов отсчитывает один шаг на каждый тактовый импульс битов. Биты, появляющиеся на четырех выходах делителя 814 тактового сигнала битов, обозначены как b0, b1, b2, b3. Наивысший по значимости бит b3 используется в качестве тактового сигнала слов 732. Делитель тактового сигнала битов 814 имеет вход сброса 832, соединенный с выходом 824 функционального блока И 822. Делитель тактового сигнала битов сбрасывается, когда на выходе 824 устанавливается высокий логический уровень вследствие отсутствия сигнала совпадения синхронизации 728 на инвертирующем входе блока И 822, т.е. когда тактовый сигнала битов 718 выбирается в качестве тактового сигнала выравнивания. Когда синхрокомбинация обнаружена, т.е. на выходе 824 устанавливается низкий логический уровень вследствие появления сигнала совпадения синхронизации 728 на инвертирующем входе схемы И 822, делитель тактового сигнала битов 832 начинает осуществлять отсчет с перезапуском через 16 шагов.

Пример конечного автомата и диаграмма переходов состояний между портом коммутатора и ядром коммутатора для возможного сценария синхронизации и повторной синхронизации, соответствующего этому конечному автомату, будут описаны ниже со ссылками на фиг. 9 и 10.

В данном примере будут передаваться состояния и соответствующие коды, указанные ниже, что будет приводить на приемной стороне к следующим одновременно устанавливающимся состояниям:

1 - СИН - указывает принимающей стороне, что сторона, являющаяся источником передаваемых данных, находится в состоянии СИН.

2 - ПРЕСИН - информирует принимающую сторону, что сторона, являющаяся источником передаваемых данных, находится в состоянии ПРЕСИН и сообщает о желательности передачи синхроэлемента по обратному каналу в первый подходящий момент времени. Возвращенный назад синхроэлемент должен вводиться в обычный поток элементов данных таким образом, чтобы вызывать минимальные помехи нормальному режиму работы.

На фиг. 9 показана диаграмма состояний синхронизации для одной стороны.

Приходящие синхроэлементы с противоположной стороны линии связи сравниваются с предварительно определенной комбинацией для синхроэлементов. В состоянии ПРЕСИН 902 и спустя три последовательных синхроэлемента возникает состояние СИН 906 согласно стрелке 904. В состоянии СИН 906 может начинаться последовательность передачи пользовательских элементов данных. Пользовательские элементы данных содержат информацию относительно их размера, которая используется для поддержания синхронизации элементов данных в состоянии СИН. Обнаружение ошибки в пользовательских элементах данных непосредственно приводит к переводу конечного автомата синхронизации в состояние ПРЕСИН 902, как показано стрелкой 908.

Для достижения быстрой синхронизации и поддержания линии связи в рабочем состоянии требуется, чтобы состояние противоположной стороны могло быть передано в синхроэлементах. Состояния приводятся в спецификации синхроэлементов.

Следующие правила перехода для синхроэлементов справедливы для конечного автомата синхронизации:

1. В состоянии ПРЕСИН. Передача синхроэлементов к противоположной стороне с индикацией относительно состояния ПРЕСИН. Ядро коммутатора должно закончить текущую передачу пользовательских элементов данных в направлении порта коммутатора. Порт коммутатора имеет возможность прервать или закончить текущую передачу в направлении к ядру коммутатора.

2. В состоянии СИН. Разрешена передача пользовательских элементов данных. Прием синхроэлементов с индикацией состояния ПРЕСИН должен привести к соответствующему синхроэлементу после завершения текущей передачи пользовательских элементов данных.

3. Последовательные синхроэлементы, указывающие состояние ПРЕСИН, будут соответствовать последовательному потоку синхроэлементов после допустимой задержки инициирования, обусловленной текущей передачей пользовательского элемента данных.

4. Порт коммутатора будет передавать синхроэлементы, которые моделируют состояние ПРЕСИН, на регулярной основе для проверки в состоянии СИН, что ядро коммутатора находится в истинно синхронном состоянии.

Согласно фиг. 10, обе стороны находятся сначала в состоянии ПРЕСИН. Соответственно они передают синхроэлементы, в общем обозначенные позицией 1002 с состоянием ПРЕСИН. Спустя определенное число последовательных синхроэлементов обе стороны входят в состояние СИН, что проявляется в разные моменты времени. В показанном на чертеже примере ядро 1004 коммутатора первым входит в состояние СИН (стрелка 1006), прежде чем порт 1008 коммутатора. Ядро 1004 коммутатора поэтому реагирует на свои три принятые синхроэлемента, указывающие состояние ПРЕСИН, передачей (стрелка 1010) синхроэлемента, указывающего состояние СИН, на каждый принятый синхроэлемент, указывающий состояние ПРЕСИН. Спустя, по меньшей мере, три последовательных синхроэлемента 1002, которые были переданы ядром 1004 коммутатора, порт 1008 коммутатора входит в состояние синхронизации (стрелка 1012). Порт коммутатора 1008 затем начинает передачу пользовательских элементов данных (стрелка 1014), поскольку от ядра 1004 коммутатора не поступают синхроэлементы с состоянием ПРЕСИН. Ядро 1004 коммутатора, принимающее теперь пользовательские элементы данных, может, в свою очередь, разрешить передачу пользовательских данных (стрелка 1016). Таким образом, линия связи теперь находится в рабочем состоянии на обеих сторонах и будет поддерживать это состояние до тех пор, пока какая-либо из сторон не перейдет в состояние ПРЕСИН вследствие обнаруженной ошибки.

В рассматриваемом примере порт 1008 коммутатора обнаруживает ошибку в принятом пользовательском элементе данных (стрелка 1018) и вводит состояние ПРЕСИН (стрелка 1020). Порт 1008 коммутатора затем передает синхроэлементы с состоянием ПРЕСИН (стрелка 1022). Ядро 1004 коммутатора должно теперь реагировать (стрелка 1024) передачей синхроэлементов, указывающих состояние СИН (стрелка 1026), вместо пользовательских элементов данных. Спустя требуемое число синхроэлементов порт 1008 коммутатора возобновляет состояние СИН (стрелка 1028). После этого обе стороны возвращаются к передаче друг другу пользовательских элементов данных (стрелка 1030).

Соответствующая процедура, когда ядро 1004 коммутатора обнаруживает ошибку в принятом пользовательском элементе данных (стрелка 1032), также показана. Она вводит (стрелка 1034) состояние ПРЕСИН и передаче синхроэлементы, указывающие состояние ПРЕСИН (стрелка 1036). Порт 1008 коммутатора должен теперь реагировать (стрелка 1038) передачей синхроэлементов, указывающих состояние СИН (стрелка 1040), вместо пользовательских элементов данных. Спустя требуемое число синхроэлементов ядро 1004 коммутатора восстанавливает состояние синхронизации (стрелка 1042). После этого обе стороны возвращаются к передаче друг другу пользовательских элементов данных согласно двойной стрелке 1044.

Теоретически имеется малая вероятность того, что ядро коммутатора перейдет в ложное состояние СИН. Это означает, что синхронизация потеряна, но это не обнаружено. Причина может быть связана с корректной синхрокомбинацией в пользовательских элементах данных или с ошибочным заголовком пользовательского элемента данных. Эта ситуация может теоретически продолжаться в течение длительного интервала времени. Для исключения такой ситуации сторона порта 1008 коммутатора при нормальной работе может проверять, находится ли ядро 1004 коммутатора действительно в состоянии СИН, путем регулярной передачи синхроэлемента (стрелка 1046), моделирующего состояние ПРЕСИН. В течение предварительно определенного периода времени, после передачи текущего пользовательского элемента данных, ядро 1004 коммутатора будет реагировать (стрелка 1048) передачей синхроэлемента с состоянием СИН (стрелка 1050). Если это не происходит, то можно считать, что ядро коммутатора находится в ложном состоянии СИН.

Если синхроэлемент обратно не передается, то передача пользовательских элементов данных заканчивается и сторона линии связи, соответствующая порту коммутатора, переводится в режим синхронизации.

При нормальном режиме работы порт коммутатора может поддерживать нагрузку на своей стороне в реальном состоянии СИН просто путем поддержания синхроэлементов в моделируемом состоянии ПРЕСИН в течение периода времени, соответствующего, по меньшей мере, пользовательскому элементу наибольшей длины.

Со ссылками на фиг. 11-14 будет представлено более детальное описание модифицированного варианта части функционального блока управления линией связи, представленного на фиг. 7 и 8. Свойства и события, приводящие к переходам состояний, являются сходными с ранее описанным вариантом. Входящий последовательный поток битов должен синхронизироваться; последовательные данные преобразуются в 16-битовые данные параллельного кода, и при выравнивании синхронизации выполняется процедура выравнивания данных для корректировки границ элементов данных. Скорость входящего тактового сигнала будет преобразовываться путем деления для получения скорости тактового сигнала, используемого в ядре коммутатора. В направлении выхода, к порту коммутатора, исходящий поток 16-битовых данных параллельного кода будет преобразовываться в последовательный поток битов.

На фиг. 12 элементы, соответствующие элементам, представленным на фиг. 7 и 8, обозначены теми же ссылочными позициями.

Вариант, представленный на фиг.11-14, основывается на использовании того факта, что максимально быстрая синхронизация элементов данных при использовании наименьшей возможной величины пространства кодовых элементов может быть достигнута использованием только 16-битового компаратора 813 и осуществления сравнений синхрокомбинаций на каждый тактовый цикл. Компаратор 813 сравнивает 16-битовые данные с последовательно/параллельного преобразователя 808 с комбинацией, которая должна быть включена в первые 16 битов синхроэлемента. Конечный автомат синхронизации 706 поддерживает отслеживание согласно фиг. 11 текущего одного из четырех состояний синхронизации, а именно: состояние ПОИСК 1102, первое состояние ПРЕСИН 1104, второе состояние ПРЕСИН 1106 и состояние СИН 1108.

В состоянии ПОИСК 1102 активизируется процедура синхронизации линии связи. Если компаратор 813 указывает сходство комбинаций, процедура переходит в первое состояние ПРЕСИН 1104 (стрелка 1110). После установления сходства для трех последовательных комбинаций (стрелки 1112 и 1114) может быть осуществлен переход в состояние СИН 1108 и начата работа в нормальном режиме.

В состояниях СИН 1108 и ПРЕСИН 1104/1106 выходной регистр 808 в последовательно/параллельном преобразователе 802 загружается только один раз на каждый 16-битовый цикл данных, так чтобы обеспечивать завершение нового 16-битового слова после каждого 16-го бита данных. В процессе синхронизации регистр 808 должен тактироваться на каждый тактовый цикл (тактовым сигналом 718 данных с порта коммутатора). В результате биты во входящем последовательном потоке данных 716 сдвигаются на две битовые позиции на каждый цикл тактового сигнала данных (сдвиг на два бита обусловлен данными с порта коммутатора, изменяющимися на оба фронта тактового сигнала) с новым битом в битовой позиции и в битовой позиции 1 соответственно. В течение каждого тактового цикла компаратор 813 сканирует исходящий поток кодовых слов для поиска синхрокомбинации. При обнаружении сходства комбинаций выдается сигнал 728, который запускает нормальный режим работы блока синхронизации. Это означает, что регистр 808 останавливает загрузку на каждый тактовый цикл, происходит переход в первое состояние ПРЕСИН 1104 (стрелка 1110) и делитель 814 тактового сигнала, который был установлен в исходное состояние в течение процедуры синхронизации линии связи, начинает отсчет от 0 до 15. Если следующий элемент представляет собой синхроэлемент, то осуществляется переход во второе состояние ПРЕСИН 1106 (стрелка 1112), в противном случае выполняется переход в состояние ПОИСК, как показано стрелкой 1116, и осуществляется повторный запуск процедуры синхронизации линии связи. После установления сходства для трех последовательных синхрокомбинаций процедура переходит в состояние СИН 1108 (стрелка 1114), в противном случае осуществляются возврат в состояние ПОИСК 1102 согласно стрелке 1118 и перезапуск синхронизации линии связи. Возврат в состояние ПОИСК 1102 из состояния СИН 1108 выполняется, когда блок анализа элементов данных 704 указывает, что в элементе данных обнаружена ошибка проверки четности или некоторая иная ошибка.

При описанном способе синхронизации проверялись все 16 возможных битовых позиций в элементе данных как начальные позиции в цикле элемента данных. И только 16 битов проверяются для положительного фронта тактового сигнала данных. Блок синхронизации элементов данных согласно фиг. 12 использует оба фронта тактового сигнала данных с порта коммутатора. Первый бит каждого пользовательского элемента данных, принятого с порта коммутатора, должен появляться на положительный фронт тактового сигнала.

Делитель 814 тактового сигнала представляет собой 4-битовый счетчик, который используется для формирования различных тактовых сигналов, используемых в ядре коммутатора. Счет осуществляется на передний фронт тактового сигнала данных 718, но только если сигнал сброса на входе сброса (установки в исходное состояние) 832 не действует. В состояниях ПРЕСИН и СИН 1104/1106 и 1108 соответственно счетчик 814 осуществляет счет от 0 до 15 и после этого снова начинает отсчет с 0. В состоянии ПОИСК 1102 активизируется вход установки в исходное состояние 832. Синхронный счет/сброс выполняется по переднему фронту тактового сигнала данных 718.

Конечный автомат синхронизации 706 содержит 2-битовый счетчик 1202, который на своем счетном входе 1204 принимает бит 2 с делителя 814 тактового сигнала, и поддерживает отслеживание текущего состояния синхронизации. Как показано на фиг. 11, состоянию ПОИСК соответствует 00, первому состоянию ПРЕСИН - 01, второму состоянию ПРЕСИН - 10 и состоянию СИН -11. Четыре состояния показаны на выходе счетчика 1202 на фиг. 12 как = 0, = 1, = 2 и = 3 соответственно. Синхронный счет выполняется по заднему фронту тактового сигнала при запуске счета посредством активизации входа 1206, на котором устанавливается высокий логический уровень. Синхронный сброс выполняется по заднему фронту тактового сигнала при активизации входа сброса 1208.

Счет активизируется при следующих условиях:

- имеет место состояние ПОИСК 202, и сигнал равенства 728 с компаратора 813 присутствует на входе запуска 1206;

- имеет место состояние ПРЕСИН, и сигнал равенства 728 появляется на входе запуска 1206 в течение первого слова нового элемента данных.

Сброс активизируется при следующих условиях:

- имеет место состояние СИН 1208, и с функционального блока 704 анализа элементов данных получен сигнал 736 ошибки;

- имеет место состояние ПРЕСИН, и с компаратора 813 не получен сигнал равенства 728 в течение первого слова элемента данных.

Более подробные сведения о реализации функций конечного автомата синхронизации, описанного выше в общих чертах, будут понятны для специалистов в данной области техники, исходя из представления логических блоков, показанных на фиг. 12 и обозначенных позициями 1210, 1212 и 1214, а также их взаимными и внешними связями с учетом ссылочных позиций, показанных на фиг. 7.

Последовательно/параллельный преобразователь 802 преобразует последовательный поток битов в 16-битовые данные в параллельном коде. Он состоит из двух 8-битовых сдвиговых регистров 806.1 и 806.2 и из 16-битового сдвигового регистра 808. Сдвиговый регистр 806.1 тактируется по переднему фронту битовым тактовым сигналом 818, а сдвиговый регистр 806.2 тактируется по заднему фронту. В результате каждый из сдвиговых регистров 806.1 и 806.2 тактируется на каждый второй битовый цикл. Это означает, что когда принимаются шестнадцать битов, то биты 1, 3,...,15 находятся в регистре 806.1, а биты 2,4,..., 16 - в регистре 806.2 (бит 1 принимается первым, а бит 16 - последним). Первый бит, т.е. бит 1, будет приниматься на положительный фронт тактового сигнала битов 718.

После приема шестнадцати битов 16-битовый регистр 808 загружен. Синхронная загрузка выполняется по переднему фронту тактового сигнала битов 718 на тактовом входе 1216, если активизирован вход загрузки 812. Вход загрузки 812 будет активизироваться посредством мультиплексора 816 всякий раз, когда делитель тактового сигнала 814 будет показывать значение 7 или если состояние ПОИСК имеет место в соответствии с выходным сигналом схемы И 822. 16-битовые входные данные регистра 808 выбираются из 2 х 8-битовых параллельных выходных со сдвиговых регистров 806.1, 806.2 таким образом, что позиции битов 1,3, . . .,15 выбираются с регистра 806.1, а позиции битов 2,4,...,6 - с регистра 806.2.

Помимо инвертирующего входа для сигнала 728 с компаратора 813 и входа для сигнала 726 схема И 822 имеет также инвертирующий вход для сигнала пользовательских элементов данных 1218 с генератора синхроэлементов 744. Этот сигнал 1218 указывает, что пользовательский элемент данных передается на порт коммутатора. Если возникает ошибка и происходит изменение состояния ПОИСК, процесс восстановления синхронизации не начнется, пока не закончится передача элемента данных к порту коммутатора.

Параллельно/последовательный преобразователь 712 преобразует 16-битовые выходные данные в параллельном коде в последовательный поток данных 722, передаваемый к порту коммутатора. Он состоит из двух 8-битовых сдвиговых регистров 712.1 и 712.2 и из мультиплексора 1220. Оба сдвиговых регистра 712.1 и 712.2 загружаются одновременно тактовым сигналом битов 712 на тактовых входах 1222 и 1224 соответственно, если входы загрузки 1226 и 1228 соответственно активизированы выходным сигналом 828 делителя 814 тактового сигнала. Вход загрузки будет активизироваться каждый раз, когда 4-битовый счетчик 814 будет иметь значение 7 или 15 на своем выходе, который согласно вышеизложенному соединен с входами загрузки 1226 и 1228. Биты 1,3,...,15 16-битовых выходных данных в параллельном коде загружаются в регистр 712.1, а биты 2, 4,...,16 загружаются в регистр 712.2. Оба сдвиговых регистра 712.1 и 712.2 тактируются (сдвигаются) по переднему фронту битового тактового сигнала 718, что означает, что они сдвигаются на каждый второй битовый цикл. Сдвиг не выполняется, если активизируется вход загрузки 1226 или 1228.

Мультиплексор 1220 использует битовый тактовый сигнал в 1230 для выбора между выходами двух сдвиговых регистров 712.1 и 712.2. Если битовый тактовый сигнал = 1, то выбирается регистр 712.1, если битовый тактовый сигнал = 0, то выбирается регистр 712.2. В результате после загрузки 16-битовых выходных данных первый бит 1 будет передан в порт коммутатора, затем бит 2, после этого сдвиговые регистры сдвигают данные и передается бит 3, затем бит 4 и т.д.

Компаратор 813 сравнивает параллельные входные данные с предварительно определенной комбинацией первых 16 битов в синхроэлементе (C2FI). Если комбинации совпадают, то передается сигнал 828 совпадения синхронизации.

Временные диаграммы, представленные на фиг. 13 и 14, иллюстрируют во времени процедуру управления процессом синхронизации линии связи.

На фиг. 13 показано следующее:

линия 1 - битовый тактовый сигнал 718,

линия 2 - выходные данные с регистра 806.1,

линия 3 - выходные данные с регистра 806.2,

линия 4 - сигнал активизации на входе загрузки 812 16-битового регистра 808,

линия 5 - параллельные данные 724 с выхода регистра 808,

линия 6 - сигнал подобия 728,

линия 7 - сигнал состояния синхронизации 742 с конечного автомата синхронизации 706,

линия 8 - сигнал счета 828 с 4-битового счетчика 814,

линия 9 - сигнал 1204 бита 2 с 4-битового счетчика 814 на счетном входе счетчика 1202.

Из линий 1-3 на фиг. 13 видно, как сдвиговые регистры 806.1 и 806.2 сдвигаются на каждый положительный фронт 1302 тактового сигнала и на отрицательный фронт 1304 тактового сигнала соответственно для сигнала 718. Сначала блок синхронизации находится в состоянии ПОИСК 202 (фиг. 11), как показано позицией 1306 на линии 7 диаграммы, и поэтому регистр 808 загружается на каждый положительный фронт тактового сигнала. Каждый тактовый цикл осуществляет поиск параллельных данных 724 компаратора 813 для обнаружения синхрокомбинации C2FI. После нескольких тактовых циклов обнаруживается указанная комбинация (позиция 1308 на линии 5), что индицируется сигналом 728 совпадения синхронизации на линии 6 диаграммы 1310. Начальная часть сигнала 728 совпадения синхронизации заштрихована (1312) для индикации того, что некоторое время необходимо для выполнения сравнения и для предотвращения возможности новой загрузки регистра 808 в течение следующего тактового цикла. Задержка должна быть не менее одного цикла тактового сигнала данных. Если появляется сигнал 728 совпадения синхронизации, то делитель 814 тактового сигнала начинает счет (1314 на линии 8). Возникает состояние синхронизации ПРЕСИН, как показано а точке 1316 на линии 7, когда 4-битовый делитель 814 тактового сигнала на своем выходе 828 сформировал значение 7. Спустя три последовательных синхрокомбинации будет осуществлен переход в состояние синхронизации, как описано ниже со ссылками на Фиг. 14.

Фиг. 14 иллюстрирует то, что происходит при обнаружении ошибки в элементе данных функциональным блоком 704 анализа элементов данных. На фиг. 14 показано следующее:

линия 1 - сигнал 812 на входе загрузки 1216 регистра 808,

линия 2 - поток слов 724 с регистра 808,

линия 3 - поток слов 732, т.е. бит 3 с делителя тактового сигнала 814,

линия 4 - сигнал ошибки 736 с функционального блока 704 анализа элементов данных для конечного автомата синхронизации 706,

линия 5 - сигнал состояния синхронизации 742 с конечного автомата синхронизации 706 для блока введения синхроэлементов 708,

линия 6 - сигнал пользовательских элементов данных 1218 с генератора синхроэлементов 744,

линия 7 - сигнал равенства 728 с функционального блока сравнения 813.

Если функциональным блоком анализа элементов данных 704 обнаружена ошибка в элементе данных, например как обозначено позицией 1402 на линии 4, то происходит переход в состояние ПОИСК (позиция 1404 на линии 5). Ввиду того, что сигнал пользовательских элементов данных 1218 с генератора 744 синхроэлементов указывает, что элемент передается к порту коммутатора, процесс синхронизации не начинается немедленно. Сначала, когда заканчивается сигнал 1218 текущего пользовательского элемента данных (позиция 1406 на линии 6) и при этом сдвиговый регистр 808 получает сигнал загрузки 812 на своем входе загрузки (позиция 1408), начинается поиск для обнаружения синхронизации. На линии 2 это проявляется в виде быстрого изменения (позиция 1410) сигнала 724. В данном случае это потребует 16 циклов битового тактового сигнала, прежде чем сигнал 728 совпадения синхронизации укажет (1412 на линии 7), что обнаружена соответствующая комбинация (1414 на линии 2). Выполняется переход в состояние ПРЕСИН в момент 1416 (линия 5). Спустя три последовательных совпадения синхронизации 1412, 1418, 1420 выполняется переход в состояние синхронизации СИН в момент 1422 (линия 5).

Задержки, связанные с логическими схемами, входящими в состав устройства, показанного на фиг. 12, весьма критичны в процедуре синхронизации. Если используется скорость данных 200 Мбит/с, то каждый тактовый период составляет всего лишь 10 нс. Поиск синхрокомбинации и остановка подачи сигнала активизации загрузки 812 на регистр 808 и сигнала сброса 832 на делитель 814 тактового сигнала должны выполняться за время, меньшее, чем указанное.

Задержка, приходящаяся на одну логическую схему, примерно равна 0,3 нс. Число уровней логических схем от выхода компаратора 813 до входа загрузки 812 регистра 808 и входа сброса 832 делителя тактового сигнала 814 примерно составляет 5-6, что означает интервал времени менее 1,8 нс.

Вышеописанная синхронизация элементов данных соответственно изобретению требуется потому, что тактовый сигнал элементов данных не передается. Управление линией связи в значительной степени не потребовалось бы, если бы тактовый сигнал, указывающий начало для каждого нового элемента данных, передавался бы по линии связи в обоих направлениях. Однако желательно, чтобы в случае коммутатора, основанного на элементах данных, ядро коммутатора можно было бы создать на одной микросхеме, при этом, однако, каждый соединительный вывод связан с дополнительными затратами. С использованием вышеописанного способа, соответствующего изобретению, предусматривающего выполнение ядра коммутатора с подчиненным тактовым сигналом, для линии связи потребуется лишь половинное количество соединительных выводов.

Изобретение относится к способу и системе для синхронизации передачи пользовательских элементов данных и передачи данных в форме потока битов между функциональными элементами двусторонней линии связи в системе передачи данных. Технический результат - обеспечение высокоскоростной синхронизации и обработки элементов данных различных размеров. Сущность изобретения заключается в том, что передача осуществляется по двусторонней линии связи между функциональными элементами, каждый из которых включает в себя функциональное средство управления линией связи, имеющее функциональные средства для запуска и управления передачей данных по линии связи с помощью синхроэлементов, предназначенных для обмена между функциональными средствами управления линией связи. Обмен синхроэлементами управляется конечным автоматом синхронизации, имеющим три состояния. В состоянии поиска функциональное средство управления линией связи анализирует синхроэлемент, поступающий из линии связи, для установления его совпадения с предварительно определенной комбинацией синхроэлемента. В состоянии предварительной синхронизации, возникающем после обнаружения предварительно определенной комбинации сихроэлемента в состоянии поиска функциональное средство управления линией связи анализирует предварительно определенное число приходящих вслед за тем синхроэлементов для определения того, содержится ли в них предварительно определенная комбинация. Если это не имеет места, то осуществляется возврат в состояние поиска. В состоянии синхронизации, которое запускается после предварительно определенного числа синхроэлементов, содержащих предварительно определенную комбинацию, обнаруженных в состоянии предварительной синхронизации, обеспечивается передача данных по линии связи при контроле данных для обнаружения ошибок. При обнаружения ошибок процедура управления переходит в состояние поиска. 3 с. и 18 з.п. ф-лы, 14 ил.

| US 975906 А, 04.12.1990 | |||

| Электромагнитный вентиль тормозов железнодорожного подвижного состава | 1973 |

|

SU468818A1 |

| Глушитель шума | 1989 |

|

SU1666785A1 |

| Цилиндровый замок для двери | 1975 |

|

SU522318A1 |

| Генератор случайных чисел | 1974 |

|

SU516042A2 |

| US 4688215 А, 18.08.1987. | |||

Авторы

Даты

2000-09-10—Публикация

1996-06-13—Подача