Это изобретение относится к системам связи с расширенным спектром и, в частности, к обработке сигналов сотовой телефонной системы.

Уровень техники

Для обслуживания большого числа абонентов в системе связи с ограниченным спектром используется один из ряда способов многостанционного доступа с расширенным спектром. Эти способы включают, например, многостанционный доступ с временным разделением каналов TDMA (time division multiple access), многостанционный доступ к частотным разделением каналов FDMA (frequency division multiple access) и многостанционный доступ с кодовым разделением каналов CDMA (code division multiple access). CDMA-технология имеет много преимуществ перед другими технологиями и примерная система с CDMA описана в патенте США N 4901307, выданном 13 февраля 1990 г., озаглавленном "Система связи с расширенным спектром с многостанционным доступом, использующая спутниковые или наземные ретрансляторы", патентовладельцем которого является заявитель настоящего изобретения.

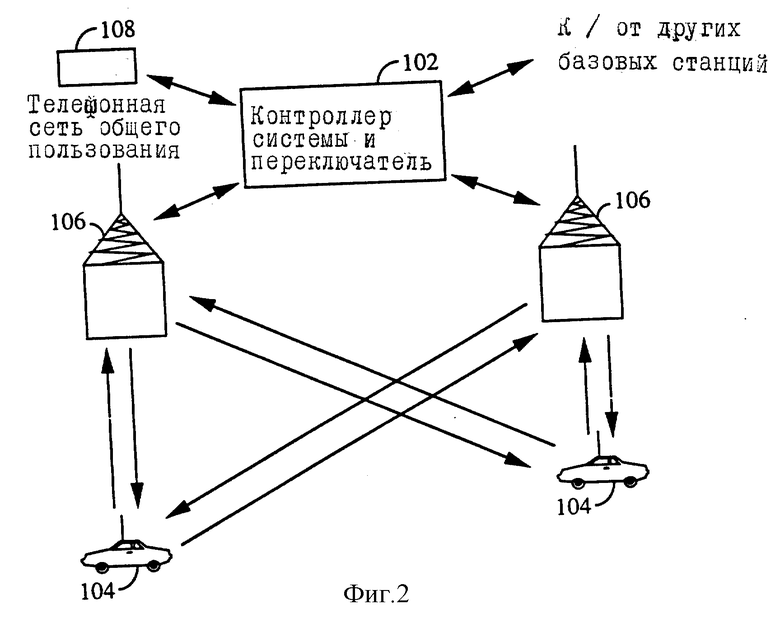

В сотовой телефонной системе с CDMA, описанной в вышеуказанном патенте США N 4901307, большое число абонентов системы подвижной связи, каждый из которых имеет приемопередатчик, осуществляет связь через спутниковые ретрансляторы или наземные базовые станции, которые также называются станциями места соты, сотовыми местами или просто сотами. Каждая сота охватывает ограниченный географический район и направляет вызовы, исходящие от сотовых телефонных приемопередатчиков в соте к и от телефонной сети общего пользования PSTN (public switched telephone network). Когда абонент сотового телефона перемещается в новую соту, маршрутизация этого абонентского вызова переносится в новую соту.

Таким образом, сотовый телефонный приемопередатчик или подвижная установка осуществляет радиопередачи подвижного сигнала, который принимается базовой станцией и затем направляет к PSTN и к телефонным линиями или другим подвижным установкам. Базовая станция передает сигнал соты, который принимается подвижными установками внутри района соты. Передачу сигналов от базовой станции к подвижной установке обычно называют прямой связью и передачу сигнала от подвижной установки к базовой станции называют обратной связью.

CDMA-технология разделяет имеющийся частотный спектр системы на множество подполос и дает возможность эффективно использовать частотный спектр много раз в пределах одного и того же промежутка времени, таким образом позволяя увеличить количество вызовов, которые могут иметь место в любой один период времени. CDMA-технология, описанная в вышеупомянутом патенте США N 4901307, использует высокочастотную псевдошумовую PN (pseudonoise) модуляцию вызовов, а также модуляцию вызовов ортогональными бинарными последовательностями для комбинирования многих вызовов и радиопередаче суммы данных в виде одного CDMA сигнала. Таким образом CDMA технология позволяет осуществлять дискриминацию между многими вызовами, которые занимают одну и ту же полосу частот и обеспечивает повышенную спектральную эффективность по сравнению с другими технологиями. В частности, система, описанная в патенте, модулирует все вызовы от той же самой соты с теми же самыми "внешними" PN кодами, которые определяют синфазный (I) канал и квадратурный (Q) канал. Индивидуальные вызовы далее модулируются "внутренним" PN кодом абонента и ортогональной бинарной последовательностью типа, известной как функции Уолша, также известная как матрицы Хадамарда.

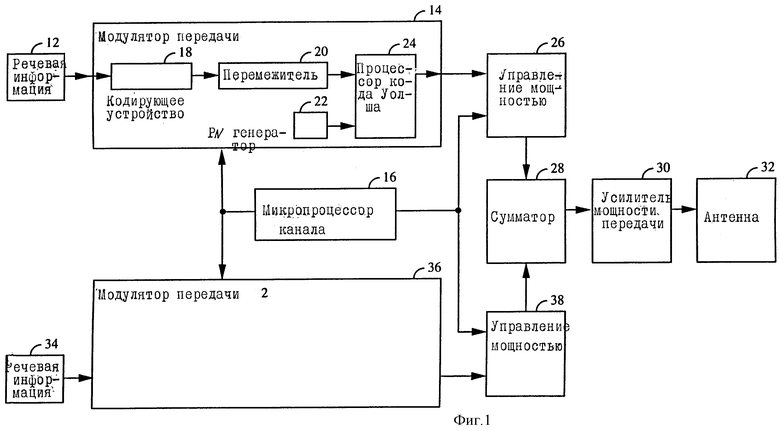

Таким образом, CDMA вызывной сигнал, передаваемый базовой станцией к подвижным установкам по тракту сигнала прямой связи будет содержать сумму многих модулированных вызовов, которые занимают ту же самую полосу частот. Система и способ модуляции и демодуляции CDMA вызывных сигналов описаны, например, в патенте США N 5103459, выданном 07.04.92 г. и озаглавленном "Система и способ генерирования сигналов в сотовой телефонной системе с CDMA", патентовладельцем которого является заявитель настоящего изобретения. На фиг. 1 показана блок-схема оборудования базовой станции описанного в патенте США N 5103459, для передачи CDMA сигнала подвижным установкам.

На фиг. 1 показано, что абонент вызывного канала генерирует, например, речевую информацию в блоке речевой информации 12, который обеспечивает данные первому модулятору передачи 14, который работает под управлением микропроцессора канала 16. В модуляторе передачи речевая информация поступает к кодирующему устройству 18 и затем к перемежителю 20, который вместе с блоком PN генератора 22 обеспечивают входные сигналы для процессора кода Уолша 24. Выходной сигнал процессора кода Уолша покидает модулятор 14 и поступает к блоку управления мощностью передачи 26, который добавляет биты управления мощностью для регулирования мощности передаваемого сигнала. Выходной сигнал блока управления мощностью передачи поступает к сумматору 28 и затем к усилителю мощности передачи 30 и к антенне для радиопередачи подвижным абонентам в соте, связанной с антенной.

В системе, описанной в патенте США N 5103459, речевая информация от блока речевой информации 34 и выходной сигнал от второго модулятора передачи 36 могут быть суммированы с выходным сигналом от первого модулятора передачи 14 сумматором 28 перед подачей к усилителю мощности передачи 30. То есть, сумматор является дискретным компонентом, который суммирует сигналы от двух отдельных модуляторов передачи и полученный результат подает к усилителю для усиления и последующей радиопередачи. Сумматор уменьшает количество необходимых усилителей и связанных управляющих схем и тем самым снижает стоимость и повышает эффективность. Количество выходных сигналов модулятора передачи и количество используемых сумматоров, а также и поддерживающих логических схем может быть приспособлено для удовлетворения требований конкретных применений. При желании многие модуляторы могут обеспечивать данные сумматору 28 или многие сумматоры могут обеспечивать суммарный выходной сигнал, подаваемый к усилителю 30, для комбинирования желаемого количества сигналов данных.

Как отмечено в патенте N 5103459, кодирование речевой информации PN данными и данными Уолша гарантирует, что индивидуальные вызовы могут быть впоследствии декодированы и отличены один от другого. В частности, данные от каждого блока управления мощностью 26, 38 получаются в объемах выборки из девяти бит и выход сумматора 28 получается в объемах выборки из десяти бит. Данные получаются в I и (Q) каналах на частоте 5 МГц, тем самым получая поток данных 90 Мбит/сек. Каждый модулятор включает 4 параллельных выходных линий. Таким образом, подсоединение трех модуляторов к сумматору приводит к шестнадцати межсоединениям фиксированного монтажа между модуляторами и усилителем передачи.

Из-за того, что сумматор 28 является дискретным компонентом, он требует межсоединений фиксированного монтажа между каждым сигналом канала. Эти межсоединения повышают стоимость, занимают место и обеспечивают возможность возникновения разрывов цепи, что прерывает передачу сигнала. Количество модуляторов передачи, подсоединяемых к каждому сумматору, могло бы быть увеличено, но каждый модулятор передачи потребовал бы еще межсоединения фиксированного монтажа и связанные управляющие схемы могли бы стать сравнительно сложными. Кроме того, сравнительно большое количество межсоединений фиксированного монтажа может стать объемистым и громоздким и может повышать издержки производства. Также, количество межсоединений может быть ограничено имеющимся для этого пространством. Наконец, при увеличении количества межсоединений возникает риск совершения ошибок вследствие поврежденных соединений или оборванных проводов.

Сущность изобретения

Исходя из вышеприведенного должно быть очевидно, что существует потребность в устройстве, которое может эффективно суммировать выходные сигналы от многих модуляторов передачи без увеличения риска ошибок или требования чрезмерного количества межсоединений фиксированного монтажа. Настоящее изобретение удовлетворяет эту потребность.

Согласно изобретению устройство для модуляции данных в системе связи с расширенным спектром включает процессор модулятора, который не только принимает локальные данные и обрабатывает их для последующей передачи, но также принимает входной сигнал в виде независимо обработанных данных от одного или нескольких других модуляторов, суммирует входные данные с обработанными локальными данными и выдает сумму в качестве данных для последующего модулятора или в качестве конечного выходного сигнала для другого процессора системы. Таким образом, нет необходимости в отдельном дискретном сумматоре сигнала, который суммирует модулированные данные от нескольких модуляторов. Скорее, ряд модуляторов может быть последовательно соединен и их соответствующие сигналы суммированы перед тем, как выходной сигнал последнего модулятора ряда получается в качестве конечного выходного сигнала, который может подаваться непосредственно к усилителю мощности для передачи через систему. Это упрощает топологию схемы для суммирования модулированных данных, уменьшает количество межсоединений фиксированного монтажа и связанных схем, снижает стоимость и повышает надежность. При желании модуляторы могут быть изготовлены на одном кристалле интегральных схем.

В одном варианте предлагаемого изобретения процессор модулятора может работать в одном из нескольких рабочих состояний, так что входные данные могут автоматически суммироваться с обработанными локальными данными модулятора или могут быть пропущены прямо к следующему процессору без суммирования или могут быть забракованы, так что к следующему процессору проходят только обработанные локальные данные. При желании может осуществляться автоматическое переключение между рабочими состояниями в ответ на обнаруженные ошибки входных данных. Входные данные могут включать, например, суммированные данные разговорного канала от ряда предыдущих модуляторов.

В другом варианте предлагаемого изобретения каждый процессор модулятора включает в своем выходном сигнале данные четности и имеет способность автоматического блокирования входных данных от функций суммирования, если неправильными являются данные четности, принятые с входным сигналом. Данные четности могут быть использованы для проверки неисправностей, таких, которые могли бы быть введены, например, путем ошибочной передачи или разорванного межсоединения фиксированного монтажа или ошибок кадровой синхронизации данных. При обнаружении во входных данных ошибок четности и блокирования функции суммирования модулятора ошибка может быть указана микропроцессору канала. Таким образом, входные данные от всех предыдущих модуляторов могут игнорироваться и обработанные локальные данные от модулятора могут проходить без суммирования.

Другие особенности и преимущества настоящего изобретения должны быть очевидными из следующего описания предпочтительного воплощения, которое иллюстрирует в качестве примера принципы изобретения.

Описание чертежей

Фиг.1 изображает блок-схему известной системы модуляции сети связи с расширенным спектром,

фиг.2 схематично изображает примерную систему связи с CDMA,

фиг. 3 изображает блок-схему модема базовой станции, включающего процессор модулятора, который сконструирован согласно настоящему изобретению,

фиг.4 изображает блок-схему сумматора, показанного на фиг. 3,

фиг. 5 изображает блок-схему цепи отметки времени процессора модулятора, показанного на фиг.3,

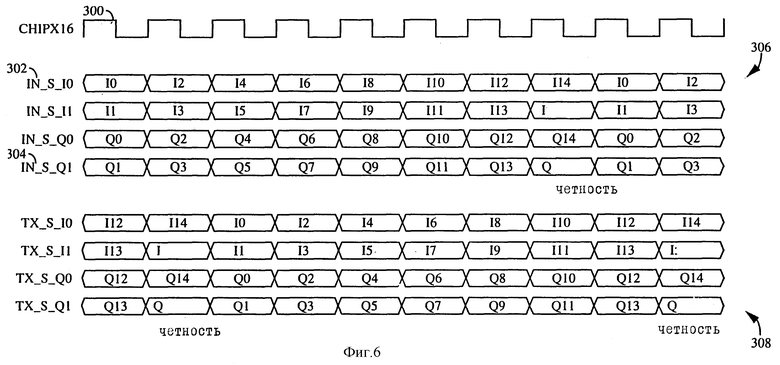

фиг. 6 изображает сигналы данных во входных регистрах и выходных регистрах процессора модулятора, представленного на фиг.3,

фиг.7 изображает блок-схему сумматора, сконструированного в соответствии с настоящим изобретением, который также включает детектор состояния переполнения.

Реализация изобретения

Настоящее изобретение может осуществляться в широком ряду применений по передаче данных и в предпочтительном воплощении осуществляется внутри системы связи с многостанционным доступом с расширенным спектром, показанной на фиг.2, для разговорного канала и передачи данных. В системе связи контроллер системы и переключатель, также называемый коммутационной телефонной станцией подвижной связи MTSO (mobile telephone switching office) 102, выполняет функции сопряжения и управления для обеспечения возможности вызовов между подвижными установками 104 и базовыми станциями 106. MTSO станции также управляет маршрутизацией вызовов между PSTN 108 и базовыми станциями для передачи к и от подвижных установок. Подвижные установки обычно не осуществляют связь непосредственно друг с другом, а осуществляют связь через MTSO и PSTN. Что касается передачи и обработки данных разговорного канала система связи работает в соответствии с CDMA технологией, описанной в вышеупомянутых патентах.

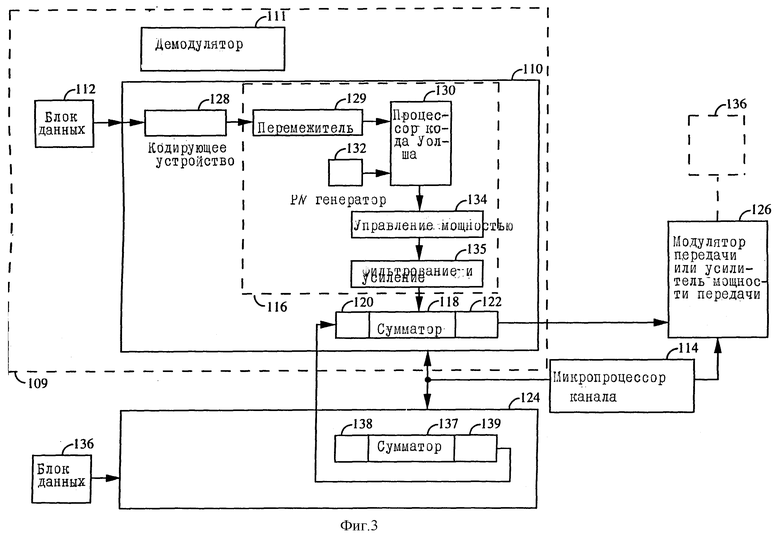

Фиг. 3 иллюстрирует первый модем базовой станции 109 системы связи, показанной на фиг. 2, который связан с одним каналом вызова. Модем включает модулятор 110 и демодулятор 111. Модулятор 110 принимает локальные данные, которые могут включать речевую информацию, например, от блока данных 112. Модулятор работает под управлением микропроцессора канала 114 для обработки локальных данных разговорного канала с помощью блока модуляции 116, который генерирует модулированные данные речевого канала. Модулятор также включает внутренний сумматор 118, который может принимать независимо модулированные данные от второго модулятора 124, суммировать два потока модулированных данных и выдавать на выходе суммарный сигнал, подаваемый к выходному усилителю мощности системы или, альтернативно, к третьему модулятору 126. В свою очередь, второй модулятор 124 принимает модулированные данные 140 от другого блока модуляции, генерируемые аналогично генерированию данных от блока модуляции 116. Таким образом, модулятор 110 может быть последовательно соединен с предшествующим модулятором 124 и последующим модулятором 126. Таким образом, сумма независимых сигналов данных может получаться путем предоставления возможности модулятору 110 непосредственно принимать данные от другого модулятора и получать суммарный выходной сигнал, включающий собственные локальные данные, вместо того, чтобы полагаться на отдельный дискретный сумматор. Тем самым модулятор, сконструированный в соответствии с настоящим изобретением, упрощает межсоединения фиксированного монтажа для получения суммарного выходного сигнала, тем самым повышая надежность системы и снижая затраты.

Модулятор 110, показанный на фиг. 3, может быть изготовлен с использованием технологии интегральных схем, так что блок модуляции 116 и сумматор 118 могут быть выполнены в одном чипе с интегральной схемой. Другие модуляторы 124 и 126 могут быть выполнены в виде единственных чипов и могут быть соединены через проводники печатной схемы на уровне платы или другие модуляторы могут быть изготовлены на том же самом чипе с интегральной схемой первого модулятора 110. В любом случае, межсоединения, необходимые для последовательного соединения и суммирования выходных сигналов от многих модуляторов являются менее сложными по топологии и количеству межсоединений по сравнению с дискретными внешними сумматорами, такими, как показано на фиг. 1, тем самым повышая надежность и снижая стоимость.

В частности, в предпочтительном воплощении выходной сигнал модулятора 110 получается в объемах выборки из 15-ти бит выходных данных и одного бита данных четности, хотя блок модуляции 116 имеет только 11 бит динамического диапазона и поэтому выдает только 11 бит данных. Дополнительные биты обеспечивают запас разрядности, требуемый при суммировании многих независимых выборок и потоков данных. Выборочные данные получают в I и (Q) каналах на частоте 2,5 МГц, тем самым выдавая поток данных 80 Мбит/сек. Каждый модулятор включает четыре параллельные выходные линии. Эти выходные линии представляют два бита I данных и два бита (Q) данных и требуют восемь периодов тактовых импульсов на частоте 20 МГц для представления 16-ти битовых I и Q выборок. Микропроцессор 114 выдает управляющие сигналы для использования различными обрабатывающими элементами.

Блок модуляции 116, показанный на фиг. 3, включает кодирующее устройство 128, которое обрабатывает локальные данные от блока данных 112 и подает обработанные локальные данные к перемежителю 129 и затем к процессору кода Уолша 130. Процессор 130 принимает также данные от блока процессора PN последовательности 132. Блок 132 генерирует PN-I и PN-Q данные, используемые для расширения полосы сигнала. После обработки процессором 130 потока данных обработанные данные поступают к блоку управления мощностью 134, который добавляет биты управления мощностью передачи для генерирования модулированных данных канала и затем к фильтру и блоку усиления 135 для управления шириной полосы сигнала и установления уровня выходного сигнала. Затем обработанные данные подаются к внутреннему сумматору 118.

Понятно, что второй модулятор 124, а также и третий модулятор 126, включают блок модуляции, аналогичный по конструкции блоку 116, с кодирующим устройством, перемежителем, процессором кода Уолша, процессором PN последовательности, блоком управления мощностью, фильтром и блоком усиления и сумматором, как показано в связи с первым модулятором 110. Для простоты и облегчения понимания такие элементы не показаны на фиг.3. Аналогично, другие модуляторы 124, 126 могут принимать данные от соответствующих блоков локальных данных 136. Для любого конкретного модулятора данные, выдаваемые на выходе соответствующего блока модуляции, должны называться локальными данными канала и должны различаться от входных данных канала, принимаемых от другого модулятора. Другие модуляторы также включают внутренние сумматоры 137, каждый из которых имеет входные регистры 138 и выходные регистры 139.

Сумматоры 118, 137 работают в нормальном режиме, в котором входные данные, принимаемые от предыдущего процессора модулятора, суммируются с локальными данными для получения выходных данных, которые подаются к последующему процессору модулятора в цепочке (или в качестве конечного выходного сигнала к блоку процессора). Сумматоры также выгодно работают в шунтирующем режиме, в котором входные данные пропускаются, и локальном режиме, в котором входной сигнал бракуется.

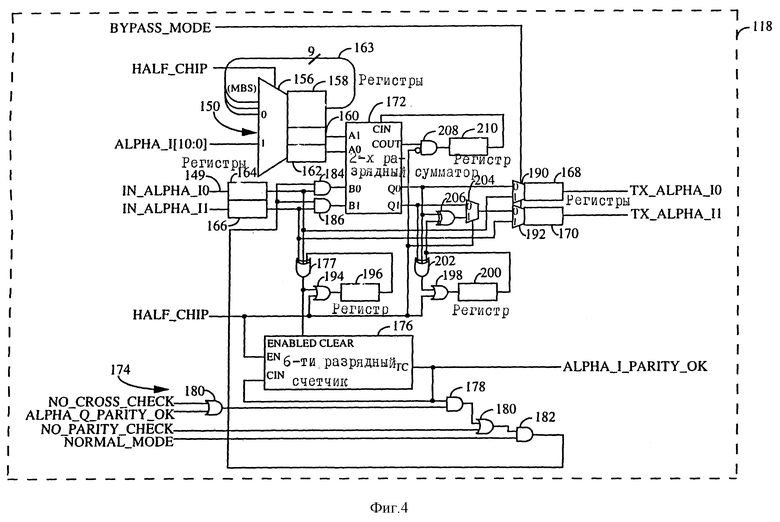

Некоторые из элементов первого сумматора 118 показаны более детально на блок-схеме, представленной на фиг. 4. Должно быть понятно, что географический район, охватываемый базовыми станциями 106, показанными на фиг. 2, включает три сектора, каждый из которых требует независимого модулятора в каждом модеме базовой станции. Фиг. 4 иллюстрирует элементы сумматора, связанные с данными канала, предназначенными только для одного из этих секторов. На фиг. 4 канал произвольно обозначен как канал Альфа. В иллюстративных целях произвольно показаны PN-I данные от сектора Альфа. Данные канала, принимаемые сумматором 118 от блока модуляции 116 (фиг.3), принимаются в виде одиннадцатибитовых выборок с шины входных данных 150, обозначенных "alpha_ J/10: 0/" должно быть понятно, что полные элементы данных канала для модулятора 110 должны были бы включать обработку данных речевого канала сектора Альфа PN-Q последовательностью. Для модема 109 базовой станции требуются модуляторы для двух других секторов соты, названных Бета и Гамма, и связанные с ними PM-I и PN-Q потоки данных. Таким образом, в модеме базовой станции всего используется 6 комплектов блоков обработки, таких как показано на фиг. 4.

Обработка внутри сумматора 118 осуществляется по два бита одновременно в потоке данных из нечетно-пронумерованных бит и потоке данных из четно-пронумерованных бит. Сумматор обрабатывает восьмибитовые пары данных для представления каждой шестнадцатибитовой выборки данных. Битовые пары упорядочены со временем, начиная с самых младших бит и переходя к самым старшим битам. Таким образом, сумматор должен быть выравнен по времени с входными выборками. Сумматор выполняет это с помощью сигнала, названного получиповым (halt-chip) и преобразователя данных из параллельной в последовательную форму 150. Получиповый сигнал представляет собой импульс, который поднимается с началом каждой новой выборки данных и используется для установки в исходные состояния схем сумматора.

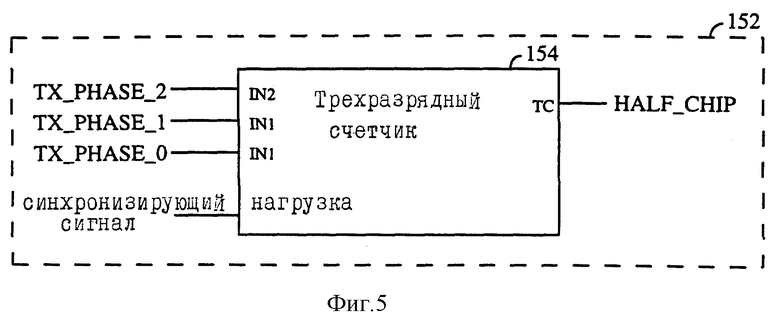

На фиг. 5 показана схема отметки времени 152, которая выдает получиповый сигнал. Схема 152 включает трехбитовый (трехразрядный) счетчик 154, который может быть совместно использован всеми сумматорами передачи модулятора базовой станции. Трехбитовый счетчик вызывает переход получипового сигнала от TC штыря выходного электрического соединителя через каждые 8 периодов синхронизирующих импульсов генератора синхронизирующих импульсов системы. Иллюстрируемый входной сигнал СИНХРОНИЗАЦИЯ (SYNCHRONJZE) вызывает состояние готовности трехбитового счетчика быть нагруженным входными сигналами фазы передачи (TX) и синхронизируется с временем системы. Трехбитовый счетчик принимает три сигнала выбора фазы передачи, называемые TX_PHASE_0, TX_PHASE_ 1 и TX_PHASE_2. TX входные фазовые сигналы описывают, где находится этот конкретный модем базовой станции во входной суммирующей цепи (см. фиг. 3). Получиповый сигнал появляется через каждые 8 периодов синхронизирующих импульсов из-за того, что, как отмечалось выше, выходные линии требуют 8 периодов синхронизирующих импульсов для представления каждой выборки.

Как показано на фиг. 4, получиповый сигнал принимается преобразователем данных из параллельной в последовательную форму 150, который принимает локальные данные и считывает их по два бита одновременно. В частности, преобразователь 150 включает мультиплексор 156, который принимает получиповый сигнал, и связанные регистры 158, 160, 162, которые принимают поток данных, обозначенный на фиг. 4 как alpha_J и сдвигают поток данных на два бита за раз вниз при поступлении получипового сигнала. Мультиплексор 156 и подсоединенный регистр 158 используют девятибитовую по ширине последовательную шину 163 для преобразования из параллельной в последовательную форму входных данных с тем, чтобы получить PN-I четные и нечетные информационные биты, которые помещаются на два выходных регистра 160 и 162, соответственно, для использования остальными схемами сумматора.

Входные регистры сумматора 120, иллюстрируемые на фиг. 3, для приема входных данных от находящегося вне чипа сумматора, реализуются в виде двух внешних входных регистров 164, 166, показанных на фиг.4, принимающих потоки данных, обозначенных как "JN_ALPHA_J0" и "JN_ALPHA_J1", соответственно, для указания того, что предварительно промодулированные PN-I данные сектора Альфа принимаются в потоке четных и нечетных бит. Специалистами в данной области техники могут быть представлены другие формы реализации входных регистров. Выходные регистры сумматора 122, иллюстрируемые на фиг. 3, для обеспечения выходных данных реализованы, как показано на фиг. 4, в виде двух выходных регистров 168, 170. Выходные данные сектора Альфа обозначаются как "TX_ A_ _J0" и "TX_A_J1" и содержат четные и нечетные биты, соответственно. Необходимо заметить, что входные "IN" и выходные "TX" сигналы имеют тот же самый формат с задержкой на два синхронизирующих импульса от входных регистров 164, 166 к выходным регистрам 168, 170 независимо от того, шунтируются или суммируются входные данные.

На фиг. 6 иллюстрируется зависимость между потоком входных данных "IN" и потоком выходных данных "TX", на которой представлена временная диаграмма данных, на которой синхронизирующий сигнал системы обозначение как CH1Px16. Показано, что данные последовательностей PN-I и PN-Q, принимаемые за раз по два бита, разделяются на четные и нечетные биты. Например, один поток входного сигнала 302 обозначается как "JN_S_J0" для указания четно-пронумерованных PN-Jвходных бит для сигнала сектора "S" и другой поток входного сигнала 304 обозначается как "JN_S_Q1" для указания нечетно-пронумерованных PH-Q входных бит сигнала сектора "S". Например, в предпочтительном воплощении соты делятся на три сектора и секторы базовой станции обозначаются как Альфа, Бета и Гамма. На фиг. 6 показано, что через каждый восьмой CH1Px16 синхронизирующий импульс относительное положение бита данных принимаемых данных (таких, как J0 или J3 или Q1 и т.д.) повторяется. То есть, потоки данных имеют время цикла, равное восьми периодам CH1Px16 синхронизирующих импульсов. Фиг. 6 также иллюстрирует задержку на два синхронизирующих импульса предпочтительного воплощения.

Таким образом, сумматор 118 принимает обработанные локальные данные от блока обработки 116 (фиг. 3) во входных регистрах 160, 162 и принимает входные данные от сумматора другого модулятора во внешних входных регистрах данных 164, 166. Два входных потока могут суммироваться в течение восьми периодов синхронизирующих импульсов и выдаваться в качестве битов выходных данных передачи на двух выходных регистрах 168, 170.

Как отмечено выше, сумматор 118 может работать в одном из трех режимов, или шунтирующем, или локальном, или нормальном режиме. В шунтирующем режиме не происходит суммирование внешних входных данных с обработанными локальными данными. Вернее, входные данные маршрутизируются непосредственно через сумматор только с единственной задержкой в потоке данных вследствие входных и выходных регистров сумматора. В локальном режиме данные на выходных регистрах 168, 170 принимаются только от входных регистров обработанных локальных данных 160, 162. Любые данные на входных регистрах данных 164, 166 не суммируются с обработанными локальными данными канала. В нормальном режиме данные на выходных регистрах формируются в виде суммы только что промодулированных данных канала и предварительно модулированных данных канала, принятых на входных регистрах. Сигнал, обозначенный как "BYPASS_MODE" переводит модулятор 110 в шунтирующий режим и сигнал, обозначенный как "NORMAL_MODE" управляет переключением модулятора в нормальный режим из локального режима, когда он находится не в шунтирующем режиме.

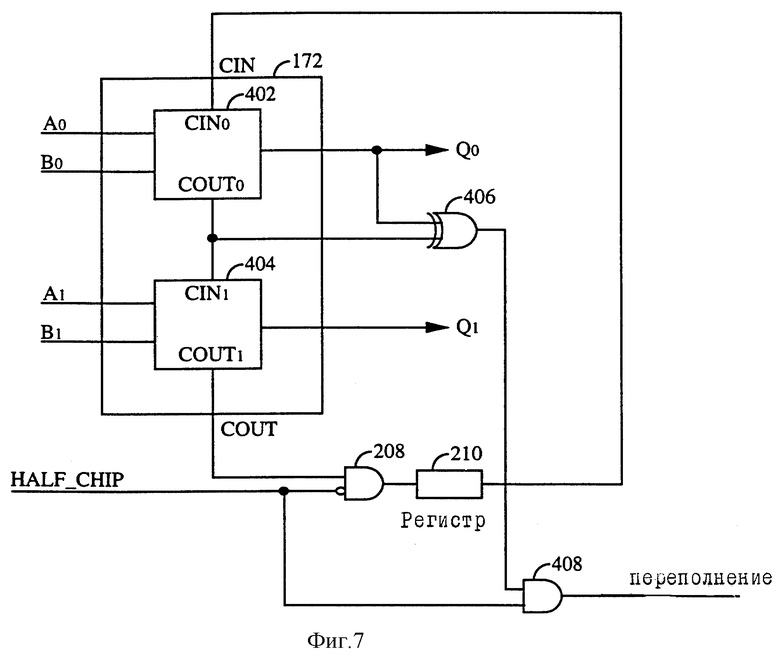

Суммирование двух потоков данных в нормальном рабочем режиме обеспечивается двухразрядным сумматором 172. Как показано на фиг. 4, двухразрядный сумматор принимает поток обработанных локальных данных с четными и нечетными битами от входных регистров 160, 162 на портах ввода, обозначенных A0 и A1, соответственно. Сумматор принимает предварительно промодулированные четные и нечетные данные от внешних входных регистров данных 164, 166 на портах ввода, обозначенных соответственно B0 и B1. Сумматор также принимает входной бит переноса "cin" от регистра переноса 210. Выходной сигнал сумматора потока четных и нечетных данных выдается на портах вывода Q0 и Q1, соответственно. Выходной бит переноса сумматора 172 обозначен "cout". Выходной сигнал сумматора потока четных и нечетных данных подается к выходным регистрам 168, 170, соответственно.

Специалистам в данной области техники понятно, что в описанном воплощении для распространения бита данных через сумматор 118 требуется два синхронизирующих импульса, однако хорошо известными в данной области техники являются другие воплощения, которые могут обеспечить возможность распространения альтернативными способами. Дополнительно, один период синхронизирующих импульсов используется для фиксирования входных данных и другой период синхронизирующих импульсов используется для фиксирования выходных данных. Биты данных должны помещаться во входные регистры 160, 162, 164, 166 для двухразрядного сумматора 172 с первым синхронизирующим импульсом и затем должны помещаться в выходные регистры 168, 170 со вторым синхронизирующим импульсом. Это иллюстрируется на временной диаграмме данных, показанной на фиг. 6, где данный бит входных данных (такой, как бит J0 JN_S_J0 потока данных), который случается на одном CH1Px16 синхронизирующем импульсе, появляется в качестве выходного бита данных (такого, как бит J0 TX_S_J0 потока данных) после двух CH1Px16 синхронизирующих импульсов.

Суммирование двух потоков данных управляется частично блоком проверки четности 174, содержащем шестиразрядный счетчик 176 и ряд логических элементов. Хорошо известными являются другие схемы, которые выполняют функцию синхронизации четности, которые могут подставляться вместо блока проверки четности 174, включающие использование регистра сдвига вместо счетчика 176. Проверка четности выполняется с помощью логического элемента исключающего ИЛИ 177, присоединенного к выходным линиям внешних входных регистров предварительно промодулированных данных 164, 166. В частности, шестиразрядный счетчик 176 считает количество последовательных входных сигналов с хорошей четностью. Четность оценивается, когда счетчик принимает получиповый сигнал. Если счет шестиразрядного счетчика меньше 63, тогда сигнал, появляющийся на TC порте вывода шестиразрядного счетчика имеет низкий уровень. Этот выходной сигнал обозначен на фиг. 4 как "alpha_J_parity_ok" для указания того, что высокий уровень сигнала указывает на отсутствие ошибки четности. Этот сигнал четности подается к микропроцессору канала 114 (фиг. 3) и также к одному входу логического элемента и 178. Другим входным сигналом логического элемента и 178 является сигнал, принимаемый от логического произведения сигнала "NO_CROSS_CHECK" и сигнала "alpha_Q_parity_ok".

Сигнал NO_CROSS_CHECK является сигналом, принимаемым от микропроцессора канала 114, уровень которого устанавливается высоким, если нежелательна перекрестная проверка четности данных I и (Q) каналов. Сигнал alpha_Q_parity_ok является выходным сигналом четности шестиразрядного счетчика четности (не показан), обрабатывающего поток данных Q канала того же самого сектора Альфа. Таким образом, сумматоры каналов секторов Бета и Гамма имеют способность перекрестной проверки четности и поэтому сумматор I канала каждого сектора принимает данные сумматора Q канала, в то время, как сумматор Q канала принимает данные сумматора I канала. Сигнал NO_CROSS_CHECKH сигнал alpha_Q_parity_ ok посылаются через логический элемент ИЛИ 180 для получения сигнала логического произведения для логического элемента И 178.

Таким образом, если высокий уровень имеет или сигнал NO_CROSS_CHECK (нежелательна перекрестная проверка) или сигнал alpha_Q_parity_ok (отсутствие ошибки четности в противоположном канале), тогда состояние отсутствия ошибки четности от счетчика 176 вызывает получение выходного сигнала высокого уровня от логического элемента И 178. Если оба сигнала перекрестной проверки имеют низкий уровень, что означает, что желательна перекрестная проверка и что противоположный канал имеет ошибку четности, тогда выходной сигнал от логического элемента И 178 должен иметь низкий уровень независимо от выходного сигнала счетчика 176.

В блоке проверки четности 174 выходной сигнал логического элемента И 178 является следующим, обеспечиваемым в качестве одного входного сигнала к логическому элементу ИЛИ 180, другим входным сигналом для которого является сигнал NO_ PARJTY_CHECK. Сигнал NO_PARJTY_CHECK имеет высокий уровень, если не желают проводить проверку четности принимаемых внешних входных данных. Таким образом, если оба входных сигнала логического элемента имеют низкий уровень, указывая на то, что сигнал NO PARJTY_CHECK имеет низкий уровень и или не была желательна и была плохой четность противоположного канала или была плохой четность I канала, тогда выходной сигнал логического элемента ИЛИ должен иметь низкий уровень. Затем, выходной сигнал логического элемента ИЛИ 180 и сигнал NORMAL_MODE, принимаемый от микропроцессора канала, прикладываются к логическому элементу И управления суммированием нормального режима 182 для управления суммированием внешних входных данных.

Когда выходной сигнал от логического элемента И 182 имеет высокий уровень, выходные сигналы от внешних входных регистров 164, 166 подаются через внешние входные логические элементы И 184, 186 к портам ввода B0 и B1 двухразрядного сумматора 172. Когда выходной сигнал от логического элемента И 182 имеет низкий уровень, внешние входные данные к двухразрядному сумматору выключаются и функция суммирования становится непригодной, переводя сумматор в локальный рабочий режим. Поэтому, если имеет место ошибка четности на входящем потоке внешних входных данных, сумматор может автоматически ввести локальный рабочий режим и прекратить добавление внешних входных данных к потоку выходных данных. Таким образом, все данные от сумматоров модулятора, которые находятся вверху по течению в цепочке последовательно соединенных модуляторов должны быть забракованы.

Таким образом, должно быть ясно, что функция суммирования становится непригодной, если (1) сигнал NORMAI_MODE имеет низкий уровень или если (2) оба, сигнал NO_PARJTY_CHECK и/или (a) сигнал alpha_J_parity_ok (ошибка четности) или (b) сигнал NO_CROSS_CHECK имеют низкий уровень и сигнал alpha_Q_ parity_ok имеет низкий уровень (ошибка четности противоположного канала).

Также должно быть отмечено, что шестиразрядный счетчик 176 обеспечивает средство автоматического восстановления функции суммирования двухразрядного сумматора 172 после обнаружения ошибки четности, если имеет место 63 последовательных циклов ввода без ошибки четности. То есть, выходной сигнал шестиразрядного счетчика приобретает высокий уровень после 63-х последовательных импульсов от логического элемента, исключающего ИЛИ 177, который принимает внешние четные и нечетные биты данных и осуществляет проверку на нечетность. Таким образом, выходной сигнал шестиразрядного счетчика приобретает высокий уровень после 63-х периодов синхронизирующих импульсов без ошибки четности входных данных, поступающих из-за пределов чипа.

Шунтирующий режим непосредственно не влияет на операцию суммирования, но выбирает данные для выходных регистров 168, 170, поступающие или от портов вывода Q0 и Q1 двухразрядного сумматора 172, или от внешних входных регистров 164, 166. Выбор выходного сигнала от внешних входных регистров имеет место при выборе шунтирующего режима, что случается, когда сигнал, обозначенный BYPASS_MODE приобретает высокий уровень. Сигнал BYPASS_MODE выбирает между "0" и "1" установкой входных линий двух выходных мультиплексоров 190, 192, от которых выходные регистры 168, 170 обеспечивают выходные данные TX_ ALPHA_ J0 и TX_ALPHA_J1. То есть, если сигнал BYPASS_MODE установлен на "0", тогда выходные мультиплексоры выбирают входные данные от суммированных портов вывода Q1 и Q1 двухразрядного сумматора 172. Если сигнал BYPASS_MODE устанавливается на "1", тогда выходные мультиплексоры выбирают входные данные от внешних входных регистров данных 164, 166 для получения потока ALPHA_J данных. При выборе шунтирующего режима, как отмечалось выше, данные, появляющиеся на выходных регистрах 168, 170 должны представлять собой задержанные на два синхронизирующих импульса копии данных на внешних входных регистрах 164, 166. Таким образом, сигнал BYPASS_MODE выбирает, должна ли шунтироваться суммирующая обработка.

Шунтирующий режим обеспечивает удобное средство очистки и шунтирования отдельных сумматоров. Например, регистр очистки (не показан) мог бы устанавливаться таким образом, что, когда устанавливается высокий уровень значения регистра, это вызывает получение сигнала высокого уровня, который используется в качестве BYPASS_MODE сигнала. Например, микропроцессор канала 114 может управлять установкой регистра очистки. Микропроцессор канала 114 мог бы, например, выбирать шунтирование сумматора, если конфигурация модулятора базовой станции 110 такова, что не используется функция суммирования сумматора. Шунтирующий режим обеспечивает средство шунтирования со сравнительно высокой надежностью, так как единственными аппаратными компонентами, которые должны соответствующим образом функционировать для соответствующей работы в шунтирующем режиме являются линия прохождения сигнала BYPASS_MODE, внешние входные регистры, выходные регистры и связанные мультиплексоры.

Получиповый сигнал, упомянутый выше в связи со схемой отметки времени 152, также обеспечивается к другим различным логическим элементам сумматора для гарантирования того, что значения регистра, индексы данных и т.п. инициализируются, где уместно, при каждой новой выборке данных. Таким образом, получиповый сигнал обеспечивается к логическому элементу ИЛИ проверки четности внешнего входного сигнала 194, таким образом счет четности, поддерживаемый в регистре 196 от логического элемента, исключающего ИЛИ 177, устанавливается для каждой новой выборки данных. Аналогично, получиповый сигнал обеспечивается к логическому элементу ИЛИ 198, так что счет четности, поддерживаемый в регистре 200 для двухразрядного сумматора от логического элемента, исключающего ИЛИ 202, устанавливается для каждой новой выборки данных. Получиповый сигнал также обеспечивается к мультиплексору 204, который выбирает данные или от Q1 выхода двухразрядного сумматора 172 или от выхода логического элемента, исключающего ИЛИ 206, на который подается выходной сигнал с порта Q0 сумматора и выходной сигнал с регистра четности сумматора 200.

Наконец, получиповый сигнал также обеспечивается после инвертирования к входу логического элемента И 208. Выходной сигнал переноса от порта "cout" двухразрядного сумматора 172 является другим входным сигналом для логического элемента И 208, выходной сигнал от которого подается к регистру переноса 210, который, в свою очередь подает выходной сигнал к порту ввода "cin" двухразрядного сумматора 172.

При желании сумматор 118 может обнаруживать состояние переполнения двухразрядного сумматора 172. Состояние переполнения могло бы указывать, например, ошибочные данные, ошибку кадровой синхронизации данных или разорванное межсоединение. Фиг. 7 иллюстрирует, как в сумматоре могло бы быть осуществлено такое обнаружение переполнения.

На фиг. 7 показано, что внутренняя конструкция двухразрядного сумматора 172 может включать два одноразрядных сумматора 402, 404, которые принимают A0, B0 четные биты данных и A1, B1 нечетные биты данных. Одноразрядные сумматоры 402, 404 выдают Q0 и Q1 выходные биты, соответственно. Выходной сигнал переноса от порта cout0 четного сумматора 402 подается к порту ввода cin1 сигнала переноса нечетного сумматора 404. Выходной сигнал переноса от порта cout1 нечетного сумматора 404 является выходным сигналом переноса от порта cout двухразрядного сумматора 172. На фиг. 7 показано, что выходной сигнал Q0 и выходной сигнал переноса от порта четного сумматора 402 подаются к логическому элементу, исключающему ИЛИ 406, выходной сигнал от которого и получиповый сигнал подаются к логическому элементу И переполнения 408 для получения сигнала переполнения.

Сигнал переполнения в значительной степени используется аналогично сигналу alpha_J_parity_ok для управления работой сумматора и подается к штырьку разрешающего очистку сигнала (enabled clear) шестиразрядного счетчика 176 (вместе с выходным сигналом от логического элемента, исключающего ИЛИ 177). Таким образом, если сигнал переполнения приобретает высокий уровень, сумматор автоматически переводится в локальный режим и его выходной сигнал вычеркивается из цепочки последовательно соединенных модуляторов.

С одиннадцатью битами данных и битом четности, используемыми в потоке данных, структура данных, определенная в предпочтительном воплощении, оставляет четыре бита (разряда) запаса. Четыре бита запаса указывают, что может быть суммировано вплоть до 16-ти модулированных сигналов речевого канала без опасения возникновения при суммировании. Таким образом, в то время, как конструкция модулятора, показанного на фиг.1, позволяла суммировать выходные сигналы двух модуляторов с помощью дискретного сумматора фиксированного монтажа и связанных схем управления, модулятор в соответствии с настоящим изобретением дает возможность соединять вместе до 16-ти модуляторов перед тем, как должны использоваться межсоединения дискретного сумматора фиксированного монтажа и связанных схем управления. Это уменьшение количества межсоединений снижает требования системы к занимаемому объему, снижает стоимость и повышает надежность.

Таким образом, процессор модулятора, описанный выше, включает интегрированный сумматор, который принимает локальные данные и также принимает входные данные от второго модулятора. Модулятор может суммировать оба потока и выдавать на выходе сумму. Выходные данные могут подаваться к следующему модулятору для суммирования или могут обеспечиваться в качестве конечного выходного сигнала в ряде модуляторов для подачи к усилителю мощности передачи для радиопередачи в системе связи. Проверка четности входных данных дает возможность игнорировать ошибочные данные и предотвращать распространение ошибок. Таким образом, количество компонент и межсоединений фиксированного монтажа, необходимое для последовательного соединения модуляторов, уменьшается, приводя к пониженным требованиям к занимаемому объему, сниженной стоимости и повышенной надежности.

Настоящее изобретение было описано выше по предпочтительному воплощению для лучшего его понимания. Однако в настоящем описании, в частности не описаны многие конфигурации для модемов и систем сотовой телефонной связи, но с которыми применимо предлагаемое устройство. Поэтому настоящее изобретение не должно рассматриваться как ограниченное описанным конкретным воплощением, но скорее должно быть понятно, что настоящее изобретение имеет широкую применимость вообще к модемам связи. Поэтому все модификации, изменения или эквивалентные устройства, которые не выходят за пределы объема прилагаемой формулы изобретения, должны рассматриваться как входящие в объем изобретения.

Изобретение относится к системам связи с расширенным спектром и может использоваться для обработки сигналов сотовой телефонной системы. Достигаемый технический результат - суммирование выходных сигналов от многих модуляторов передачи без увеличения риска ошибок или требования чрезмерного количества межсоединений. Устройство для использования в системе связи с расширенным спектром для генерирования сигнала для последующей радиопередачи по всей системе содержит сумматоры, блоки модуляции, контроллер, передатчик. Модем для системы связи с расширенным спектром содержит демодулятор, модулятор, сумматор, контроллер, который управляет демодулятором и модулятором для выполнения соответствующей обработки сигнала. Способ суммирования данных сигнала от множества абонентов в системе с расширенным спектром включает операции: прием информационных слов и их обработку, суммирование рядов обработанных данных, проверку четности для определения наличия ошибки четности, добавление данных четности к принятым информационным словам. 3 с. и 14 з.п. ф-лы, 7 ил.

| US 5224120 A, 29.06.1993 | |||

| Способ радиосвязи с подвижными объектами в системе связи сотовой структуры | 1989 |

|

SU1626412A1 |

| EP 0446194 A1, 11.09.1991 | |||

| Устройство контроля двух синхронизированных генераторов импульсов | 1973 |

|

SU493904A1 |

Авторы

Даты

2000-11-10—Публикация

1995-09-29—Подача