Изобретение относится к микроэлектронике и может быть использовано в технологии изготовления интегральных микросхем и наноструктур различного назначения.

Известен способ металлизации многослойных интегральных микросхем, включающий формирование в кремниевой пластине с активными областями межслойных диэлектрических покрытий и выполнение сквозь них межслойных проводящих соединений (см. описание к патенту США N 5607880, H 01 L 21/44, НКИ 437/195, 1997 [1] ). Недостатком известного способа является сложность его осуществления, заключающаяся в том, что при его осуществлении используются приемы фотолитографии, приводящие к необходимости нанесения слоев фоторезиста, вскрытие окон избирательным травлением для формирования масок, удаление слоев фоторезиста после завершения изготовления слоя, а при изготовлении многослойных схем указанные операции повторяют многократно.

Известен способ формирования многослойной металлизации микросхем без использования операций метода фотолитографии (см. описание к патенту США N 5569624, H 01 L 21/28, НКИ 437/200, 1996 [2]). Известный способ предусматривает изготовление полупроводниковых вентилей, легирование которых осуществляется путем перенесения легирующих примесей из вышележащего специально подготовленного слоя в нижележащий, подвергаемый легированию, под воздействием излучения эксимерного лазера. Недостатком известного способа является ограниченность его применения, поскольку он применим только для изготовления вентилей и не обеспечивает формирование многослойных проводящих соединений.

Наиболее близким к заявляемому по своей технической сущности и достигаемому результату является известный способ изготовления интегральных микросхем, который обеспечивает формирование в них межуровневых (межслойных) соединений (см. описание к патенту РФ N 1547611, H 01 L 21/28, 1996 [3]). Известный способ предусматривает, что после формирования омических и выпрямляющих контактов к созданным активным областям формируют рисунок межсоединений по первому уровню, затем наносят межслойный диэлектрик, в нем вскрывают окна и выполняют межслойное соединение, а затем формируют следующий слой. При этом при формировании межслойных соединений используют технологию фотолитографии.

Недостатком известного способа является сложность его реализации, обусловленная использованием фотолитографических процессов и последовательным выполнением межслойных соединений, в результате чего обрабатываемую пластину неоднократно извлекают из вакуумной системы для удаления фоторезиста и возвращают в нее для осуществления последующих операций.

Заявляемый в качестве изобретения способ формирования многоуровневой металлизации направлен на упрощение технологического процесса.

Указанный результат достигается тем, что способ формирования многоуровневой металлизации интегральных схем включает формирование в исходной пластине с активными областями проводящего рисунка межсоединений по каждому уровню, нанесение межслойных диэлектрических покрытий и формирование межслойных соединений, при этом все межслойные соединения формируют до нанесения межслойных диэлектрических покрытий и выполняют их в виде вертикальных проводов различной высоты, напыляемых на исходную пластину перед формированием проводящего рисунка первого и последующих слоев металлизации, при этом все потоки ионов металлов, направляемых к исходной пластине, подвергают пространственной модуляции с помощью шаблонов.

Отличительными признаками заявляемого способа являются:

- выполнение всех межслойных соединений до нанесения межслойных диэлектрических покрытий;

- выполнение межслойных соединений в виде вертикальных проводов различной высоты, напыляемых на кремниевую пластину;

- пространственная модуляция потоков ионов металла, направляемых на обрабатываемую кремниевую пластину;

- использование шаблонов для пространственной модуляции.

Выполнение всех межслойных соединений до нанесения межслойных диэлектрических покрытий упрощает технологию формирования многоуровневой металлизации, так как отпадает необходимость во вскрытии соответствующих окон в межслойных диэлектрических покрытиях и формирования в них проводящих структур, поскольку в предлагаемом способе вертикальные элементы проводящей структуры, выполненные в виде вертикальных проводов-столбиков, будут пронизывать заданное количество слоев микросхемы и межслойные покрытия будут "нанизываться" на них по мере их нанесения.

Использование пространственной модуляции потоков ионов металлов, направляемых на обрабатываемую пластину, позволяет существенно упростить процесс формирования слоев металлизации, так как отпадает необходимость в использовании процесса фотолитографии и связанных с ним операций. Формирование проводящей структуры может обеспечиваться путем пространственной модуляции потока ионов металла, используемого при напылении металлических слоев. И только поток ионов диэлектрика не нуждается в модуляции, поскольку при напылении им должна покрываться вся поверхность обрабатываемой пластины.

Поскольку использование пространственной модуляции позволяет отказаться от процессов фотолитографии и осуществлять все стадии технологического цикла многослойной металлизации в вакуумной системе, то это также упрощает реализацию заявленного способа. В вакуумную систему, оснащенную соответствующими источниками для напыления металлов и диэлектриков, помещают исходную пластину со сформированными активными областями и после проведения всех операций вынимают готовую микросхему, не прибегая к разгерметизации системы в процессе изготовления, как это имеет место в прототипе.

Наиболее простым средством пространственной модуляции является шаблон, помещаемый на пути потока частиц, атомов или ионов. Поэтому использование шаблонов упрощает способ.

Сущность заявляемого изобретения поясняется примером его реализации и чертежами. На фиг. 1-8 схематично представлен поперечный разрез изготавливаемой микросхемы на различных стадиях осуществления способа.

Пример 1. В общем случае способ реализуется следующим образом (на примере трехслойной схемы).

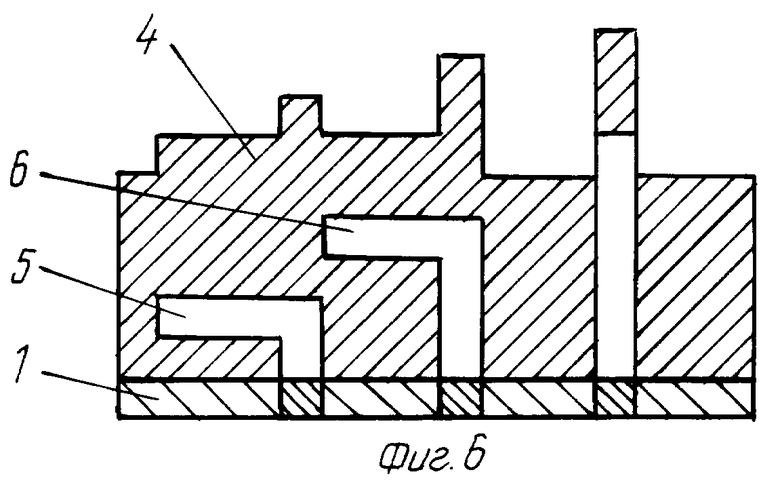

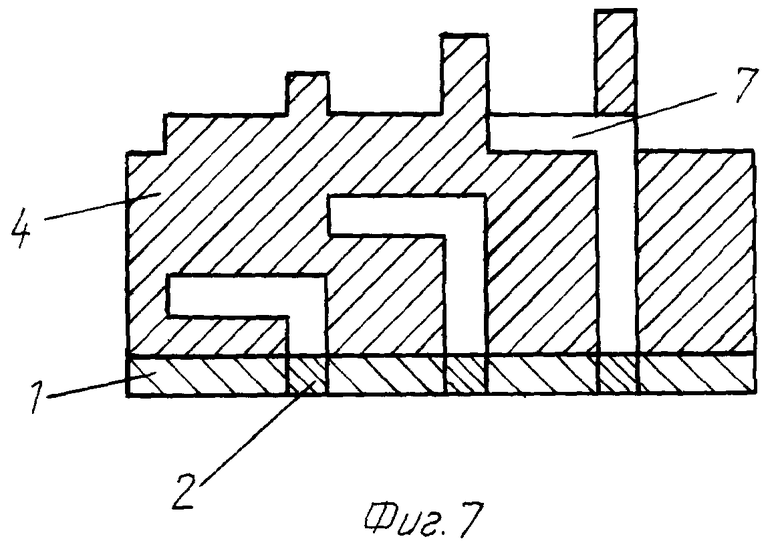

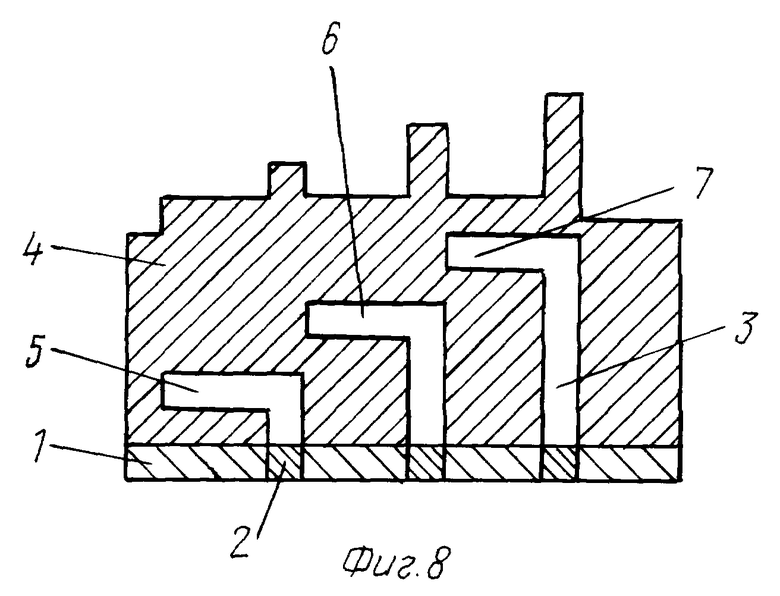

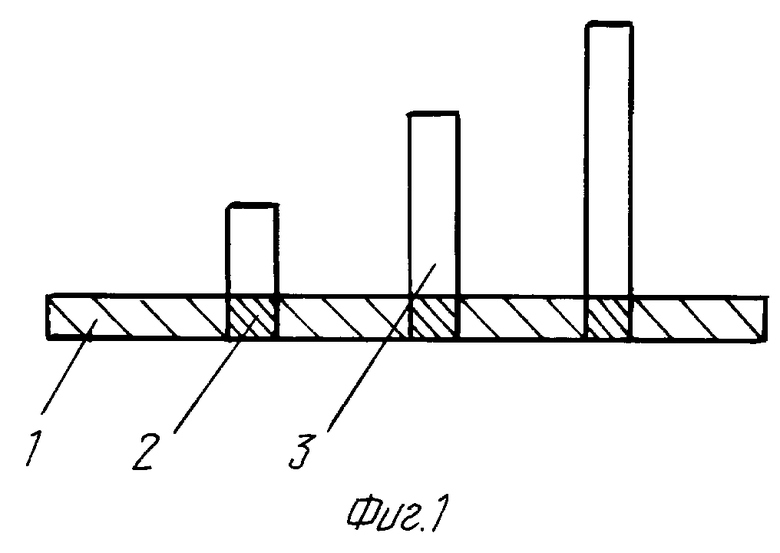

Исходную пластину монокристаллического кремния 1 со сформированными активными областями 2 размещают внутри вакуумной установки, включающей ионно-проецирующее устройство и снабженной необходимыми средствами для напыления металлических и диэлектрических слоев, которые могут быть выбраны из числа известных (см. , например, У. Тилл, Дж. Лаксон. Интегральные схемы. М., "Мир", 1985 [4]). Затем на поверхности кремниевой пластины в соответствии с топологией изготавливаемой микросхемы последовательно формируют вертикальные провода 3 разной высоты путем пространственной модуляции пучка ионов металла при прохождении его через шаблоны, что позволяет исключить использование масок из резиста (фиг. 1). Применение различных шаблонов при вакуумном напылении вертикальных проводов обеспечивает соответствующее их расположение на микросхеме и различную их высоту.

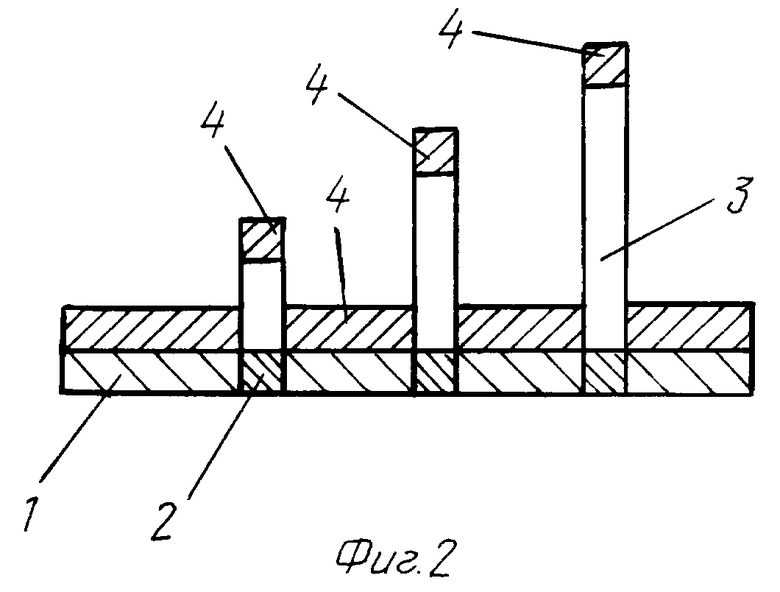

После формирования вертикальных проводов 3 разной высоты пластина покрывается первым слоем межслоевого диэлектрика 4 (фиг. 2). При этом на поверхности вертикальных проводов образуются "шапки" из диэлектрика толщиной, равной толщине первого слоя диэлектрика. На последующих стадиях процесса толщина "шапок" из диэлектрика растет пропорционально количеству слоев диэлектрика и он интегрируется в общий слой переменной толщины.

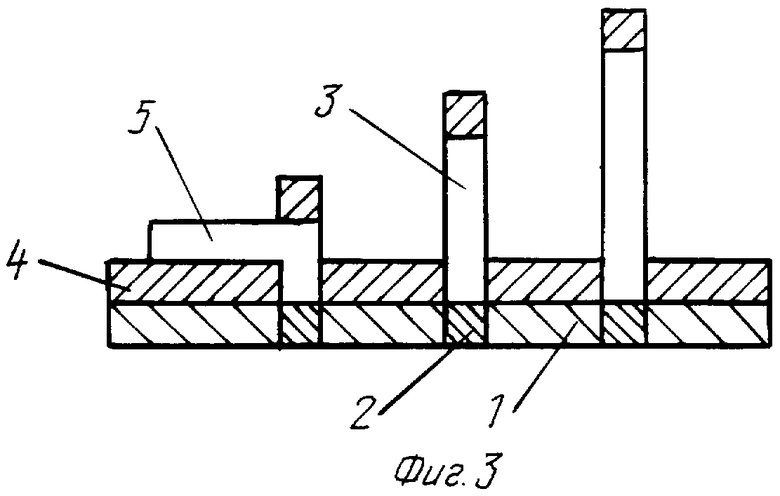

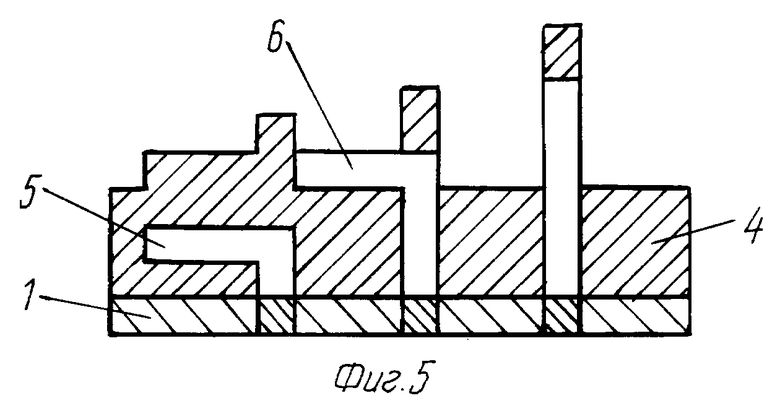

На следующем этапе (фиг. 3) через шаблон формируют горизонтальные провода первого уровня 5. Аналогичные операции формирования горизонтальных проводов второго 6 и третьего слоя 7 осуществляют через шаблоны в соответствии с топологией изготавливаемой микросхемы. Данные операции представлены на фиг. 5 и 7.

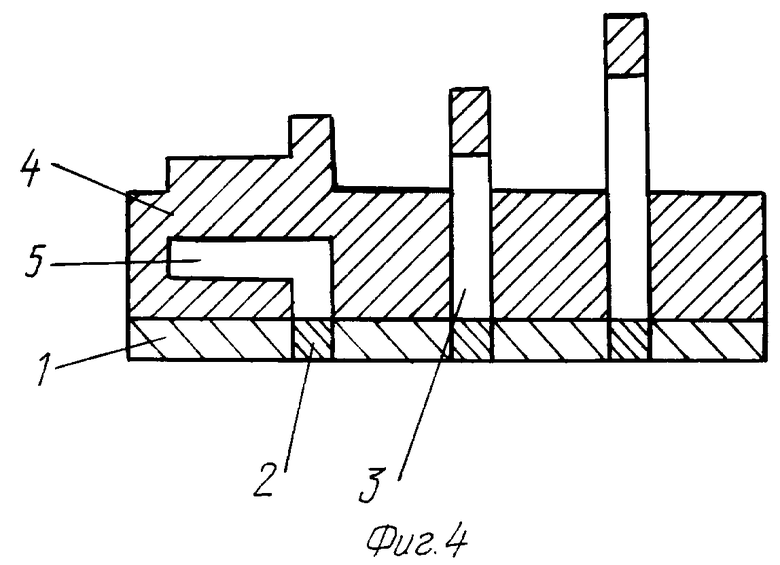

После формирования горизонтальных проводов в каждом из слоев металлизации вся пластина покрывается слоем диэлектрика 4 (фиг. 4, 6, 8). Процесс изготовления микросхемы в вакуумной установке заканчивается нанесением слоя диэлектрика, покрывающего всю разводку, как это показано на фиг. 8.

По изложенному выше алгоритму могут формироваться микросхемы с любым количеством слоев.

Для осуществления операций, составляющих способ, могут использоваться известные устройства и материалы - металлы для формирования проводящих структур (алюминий, медь и т.д.), диэлектрики для формирования межслойных покрытий и т.д.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИЗГОТОВЛЕНИЯ МНОГОУРОВНЕВЫХ ТОНКОПЛЕНОЧНЫХ МИКРОСХЕМ | 2004 |

|

RU2264676C1 |

| Способ изготовления СВЧ-гибридной интегральной микросхемы космического назначения с многоуровневой коммутацией | 2019 |

|

RU2713572C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ТОНКОПЛЕНОЧНЫХ МНОГОУРОВНЕВЫХ ПЛАТ ДЛЯ МНОГОКРИСТАЛЬНЫХ МОДУЛЕЙ, ГИБРИДНЫХ ИНТЕГРАЛЬНЫХ СХЕМ И МИКРОСБОРОК | 2011 |

|

RU2459314C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МНОГОУРОВНЕВЫХ МЕЖСОЕДИНЕНИЙ ИНТЕГРАЛЬНЫХ МИКРОСХЕМ С ВОЗДУШНЫМИ ЗАЗОРАМИ | 2010 |

|

RU2436188C1 |

| СПОСОБ ФОРМИРОВАНИЯ СИСТЕМЫ МНОГОУРОВНЕВОЙ МЕТАЛЛИЗАЦИИ НА ОСНОВЕ ВОЛЬФРАМА ДЛЯ ВЫСОКОТЕМПЕРАТУРНЫХ ИНТЕГРАЛЬНЫХ МИКРОСХЕМ | 2015 |

|

RU2611098C1 |

| СПОСОБ СОЗДАНИЯ МНОГОУРОВНЕВЫХ МЕЖСОЕДИНЕНИЙ ИНТЕГРАЛЬНЫХ МИКРОСХЕМ | 1991 |

|

RU2028696C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МНОГОУРОВНЕВОЙ МЕДНОЙ МЕТАЛЛИЗАЦИИ С УЛЬТРАНИЗКИМ ЗНАЧЕНИЕМ ДИЭЛЕКТРИЧЕСКОЙ ПОСТОЯННОЙ ВНУТРИУРОВНЕВОЙ ИЗОЛЯЦИИ | 2013 |

|

RU2548523C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ТОНКОПЛЕНОЧНОЙ МИКРОСХЕМЫ | 1991 |

|

RU2040131C1 |

| Многослойная коммутационная плата СВЧ-гибридной интегральной микросхемы космического назначения и способ её получения (варианты) | 2019 |

|

RU2715412C1 |

| ВСТРАИВАЕМАЯ С СБИС ТЕХНОЛОГИИ КМОП/КНИ ПАМЯТЬ "MRAM" И СПОСОБ ЕЕ ИЗГОТОВЛЕНИЯ (ВАРИАНТЫ) | 2012 |

|

RU2532589C2 |

Использование: в технологии изготовления интегральных микросхем и наноструктур различного назначения. Сущность изобретения: способ формирования многоуровневой металлизации интегральных схем включает формирование в исходной пластине с активными областями проводящего рисунка межсоединений по каждому уровню, нанесение межслойных диэлектрических покрытий и формирование межслойных соединений, при этом все межслойные соединения формируют до нанесения межслойных диэлектрических покрытий и выполняют их в виде вертикальных проводов различной высоты, напыляемых на исходную пластину перед формированием проводящего рисунка первого и последующих слоев металлизации, при этом все потоки ионов металлов, направляемые к исходной пластине, подвергают пространственной модуляции с помощью шаблонов. Техническим результатом изобретения является упрощение технологического процесса. 8 ил.

Способ формирования многоуровневой металлизации интегральных схем, включающий формирование в исходной пластине с активными областями проводящего рисунка межсоединений по каждому уровню, нанесение межслойных диэлектрических покрытий и формирование межслойных соединений, отличающийся тем, что все межслойные соединения формируют до нанесения межслойных диэлектрических покрытий и выполняют их в виде вертикальных проводов различной высоты, напыляемых на исходную пластину перед формированием проводящего рисунка первого и последующих слоев металлизации, при этом все потоки ионов металлов, направляемые к исходной пластине, подвергают пространственной модуляции с помощью шаблонов.

| RU 1547611 A1, 20.01.1996 | |||

| US 5607880 A, 04.03.1997 | |||

| СПОСОБ ФОРМИРОВАНИЯ МЕЖСОЕДИНЕНИЙ В МАТРИЦЕ ТРЕХМЕРНЫХ ПОЛУПРОВОДНИКОВЫХ ЭЛЕМЕНТОВ | 1991 |

|

RU2012090C1 |

| US 5514613 A, 07.05.1996 | |||

| Загрузчик стеклянных полублоков | 1977 |

|

SU687005A1 |

| Установка для пайки волной расплавленного припоя | 1978 |

|

SU724292A2 |

Авторы

Даты

2001-04-10—Публикация

2000-02-11—Подача