Изобретение относится к области микроэлектроники, в частности к технологии изготовления многослойных структур на подложках из различных материалов, а именно многоуровневых тонкопленочных интегральных микросхем с многоуровневой коммутацией.

Известны способы изготовления интегральных микросхем с многоуровневой коммутацией, представляющие собой последовательный многостадийный процесс формирования слоев проводников различных уровней коммутации с межслойной изоляцией и межуровневой коммутацией, включающий, например, формирование слоя проводников первого уровня коммутации, нанесение на него полиимидной пленки для межслойной изоляции, вскрытие в ней окон под межуровневые контакты посредством импульсного лазерного излучения и формирование второго уровня коммутации методом вакуумного напыления металла с последующей фотолитографией для создания рисунка проводников (см. патент США №4508749, В 44 С 1/22, 1985 г.).

Однако приведенный типичный аналог послойного наращивания многослойной тонкопленочной структуры характеризуется сложностью технологического оборудования и низкой производительностью изготовления.

Известен также способ изготовления двухуровневых тонкопленочных коммутационных плат, включающий нанесение ионно-плазменным распылением на диэлектрическую подложку слоев V-Cu-V-Al первого уровня металлизации, формирование методом селективной фотолитографии с использованием позитивного фоторезиста рисунка проводников первого уровня коммутации и с помощью негативного фоторезиста защитной маски с окнами для переходных контактных столбиков с последующим травлением нижележащих защитного (Al) и адгезионного (V) слоев над проводящей пленкой (Cu) для выполнения самих окон с промежуточной обработкой припоем через окна полученных медных контактных площадок их окунанием в ванну с припоем, приводящим к образованию контактных столбиков, затем нанесение диэлектрической пленки с последующей обработкой припоем для расплавления полученных контактных столбиков вторым погружением в ванну с припоем, приводящим к разрыву диэлектрической пленки и наращиванию столбиков на дополнительную величину, и после чего напыление слоев V-Cu-V-Al для получения второго уровня металлизации с фотолитографическим формированием рисунка проводников второго уровня коммутации (см. а.с. №1358777, Н 05 К 3/46, 1996 г).

Для этого способа изготовления, повышающего выход годных, свойственны технологическая насыщенность производственными операциями, низкая производительность изготовления и ухудшение технологичности техпроцесса из-за необходимости обработки припоем.

Наиболее близким заявляемому способу по решаемой технической задаче - изготовлению многоуровневых тонкопленочных гибридных интегральных микросхем с улучшенными характеристиками качества и техпроцесса выбран способ, представляющий собой формирование двухуровнего рисунка проводников с межслойной изоляцией в виде полиимидной пленки, имеющей окна для межуровневой коммутации, включающий нанесение методом вакуумного осаждения на диэлектрическую подложку слоев хрома, меди, хрома, получение рисунка проводников нижнего уровня коммутации с помощью фотолитографии, с последующим нанесением технологического слоя ванадия и формированием в нем окон на участках межслойной изоляции, которую формируют нанесением слоя полиимида с вскрытием в нем окон для межслойных переходов и последующим удалением технологического слоя ванадия с помощью селективного травления, после чего производят последовательное вакуумное осаждение сплошных слоев ванадия и меди с гальваническим наращиванием слоя меди на очищенной поверхности подложки, с рисунком проводников нижнего уровня коммутации и межслойной изоляцией с окнами для межуровневой коммутации, и последующее формирование рисунка проводников верхнего уровня коммутации с помощью фотолитографии (см. патент РФ №1816170, Н 01 L 49/02, Н 05 К 3/00, опубликован в 2002 г.).

Данный способ - прототип также характеризуется общими недостатками послойного наращивания тонкопленочной структуры, такими как сложность техпроцесса и низкая производительность изготовления.

Технический результат предлагаемого изобретения - упрощение техпроцесса и повышение производительности изготовления многоуровневых тонкопленочных микросхем, повышение степени их интеграции и эффективности использования проводникового слоя, расширение ассортимента изделий за счет обеспечения работоспособности предлагаемой технологии в широком интервале толщин слоев изготавливаемых многоуровневых интегральных микросхем, универсализация и расширение области применения способа за счет его совместимости с традиционной технологией изготовления микросхем, а также удешевление изготовления в результате снижения затрат на материалы и оборудование для изготовления многоуровневых микросхем.

Указанный технический результат достигается тем, что в способе изготовления многоуровневых тонкопленочных микросхем, включающем получение в проводниковых слоях рисунка проводников и выполнение в диэлектрических слоях окон методом фотолитографии и формирование из проводниковых и диэлектрических слоев многослойной интегральной микросхемы, имеющей межуровневую коммутацию в виде электрических соединений, созданных в окнах диэлектрических слоев, микросхему формируют путем последовательного совмещения отдельных одноуровневых тонкопленочных плат между собой и создания в окнах диэлектрических слоев этих плат неразъемных соединений, сочетающих в себе функции межуровневой коммутации - электрического соединения и конструкционного скрепления - механического соединения, посредством, например, микросварки приведенных в положение взаимного контакта участков проводниковых слоев, предварительно топологически предусмотренных над окнами во время получения рисунка проводников, и в случае недостаточности конструкционной прочности микросхемы ее формирование сопровождают созданием в дополнительных окнах диэлектрических слоев плат неразъемных соединений, несущих функцию только конструкционного скрепления, посредством, например, микросварки приведенных в положение взаимного контакта участков проводниковых слоев, предварительно топологически предусмотренных над дополнительными окнами во время получения рисунка проводников без включения этих участков в него, при этом формирование микросхемы производят через оба типа окон, выполненных с осями, совпадаемыми при совмещении плат, и при увеличении числа соединяемых плат - через окна с осями, разнесенными в совмещаемых платах для уменьшения прогиба соединяемых участков проводниковых слоев, включая при топологической необходимости создание неразъемных соединений контактируемых участков проводниковых слоев в сквозных окнах в промежуточных платах.

Для повышения надежности контакта при прогибе в окнах соединяемых участков проводниковых слоев, последние выполняют с частичным покрытием ими обоих типов окон, в целях повышения эффективности технологии для выполнения участков используют во время получения рисунков проводников исходный слой проводников одноуровневых плат, а для предотвращения замыкания проводниковых слоев промежуточных плат неразъемное соединение контактируемых участков проводниковых слоев через сквозные окна в промежуточных платах создают в условиях напуска диэлектрического слоя в этих окнах.

В конкретном осуществлении способа исходные одноуровневые тонкопленочные платы получают путем вакуумного напыления проводникового металла, например, меди, хрома, золота и других на полиимидную пленку или нанесением лака на фольгу из проводникового металла с последующей фотолитографией для получения одноуровневой топологии плат.

В предлагаемом способе предусмотрено соединение плат между собой в конструкцию микросхемы с дополнительным увеличением конструкционной прочности микросхемы посредством нанесения между платами клеевых композиций или усиление соединения плат между собой окунанием сформированной многослойной микросхемы в полиимидный лак с последующей фотолитографией поверхности микросхемы для вскрытия в ней участков под монтаж навесных компонентов и имидизацией полиимидного лака.

Предлагаемый способ допускает возможность развития технологии заявляемого изготовления микросхем, в соответствии с которой формирование микросхем начинают с соединения одноуровневых тонкопленочных плат с одно- или двухсторонней платой, выполненной на основе общей для всей многоуровневой микросхемы жесткой диэлектрической подложки, например керамики, анодированного алюминия, стеклотекстолита или металлической подложки, и продолжают соединение, соответственно, по одну или обе стороны от этой подложки с пропусканием фрагмента одноуровневой тонкопленочной платы через отверстия, выполненные в общей жесткой подложке, или металлизацией таких отверстий для обеспечения непрерывности межуровневой коммутации микросхемы, а также вариант изготовления, в соответствии с которым формирование многоуровневой микросхемы завершают присоединением к соединенным между собой одноуровневым тонкопленочным платам с обеих их сторон дополнительных одноуровневых плат, выполненных на основе жесткой подложки и снабженных средствами механического соединения многослойной микросхемы, например, конструктивными крепежными элементами для усиления скрепления плат по периметру конструкции микросхемы.

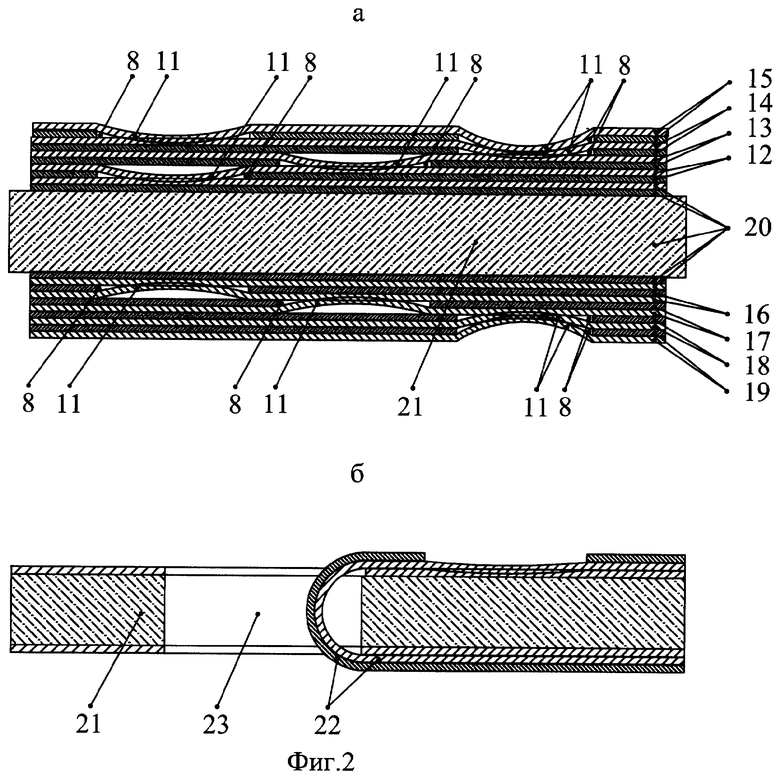

На фиг.1 изображена схема, поясняющая изготовление многоуровневых тонкопленочных микросхем в соответствии с заявляемым способом:

а - в случае совмещения и соединения двух одноуровневых тонкопленочных плат,

б - в случае совмещения трех одноуровневых тонкопленочных плат и соединения между собой через сквозные окна с напуском в них диэлектрической пленки,

в - в случае соединения одноуровневых тонкопленочных плат в количестве более трех со ступенчатым разнесением осей окон по уровням коммутации,

г - в случае соединения плат с сочетанием разнесения и совпадения осей окон в совмещаемых платах;

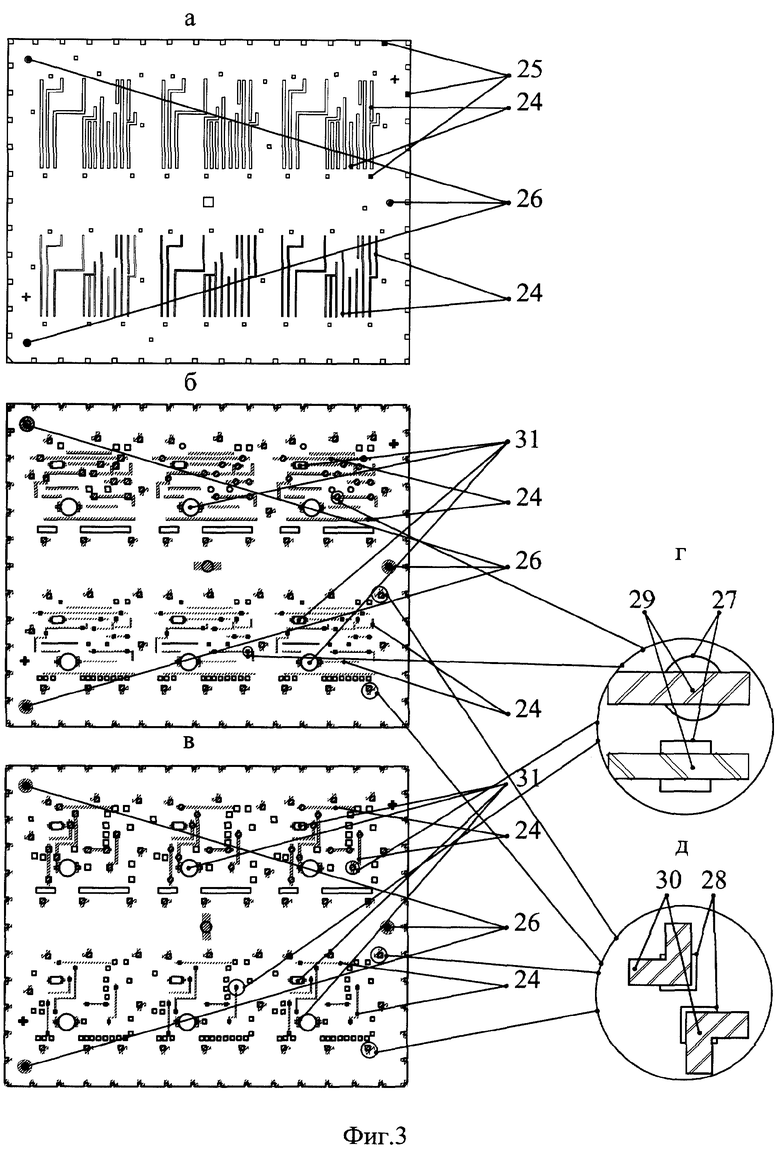

на фиг.2а - схема, поясняющая изготовление многоуровневых тонкопленочных микросхем в соответствии с заявляемым способом в случае формирования микросхемы на основе общей жесткой диэлектрической подложки с соединением с ней и между собой одноуровневых тонкопленочных плат по обе стороны от нее,

на фиг.2б - схема технологической операции изготовления микросхемы, показанной на фиг.2а, заключающейся в пропускании фрагмента гибкой одноуровневой тонкопленочной платы через отверстие в общей жесткой подложке;

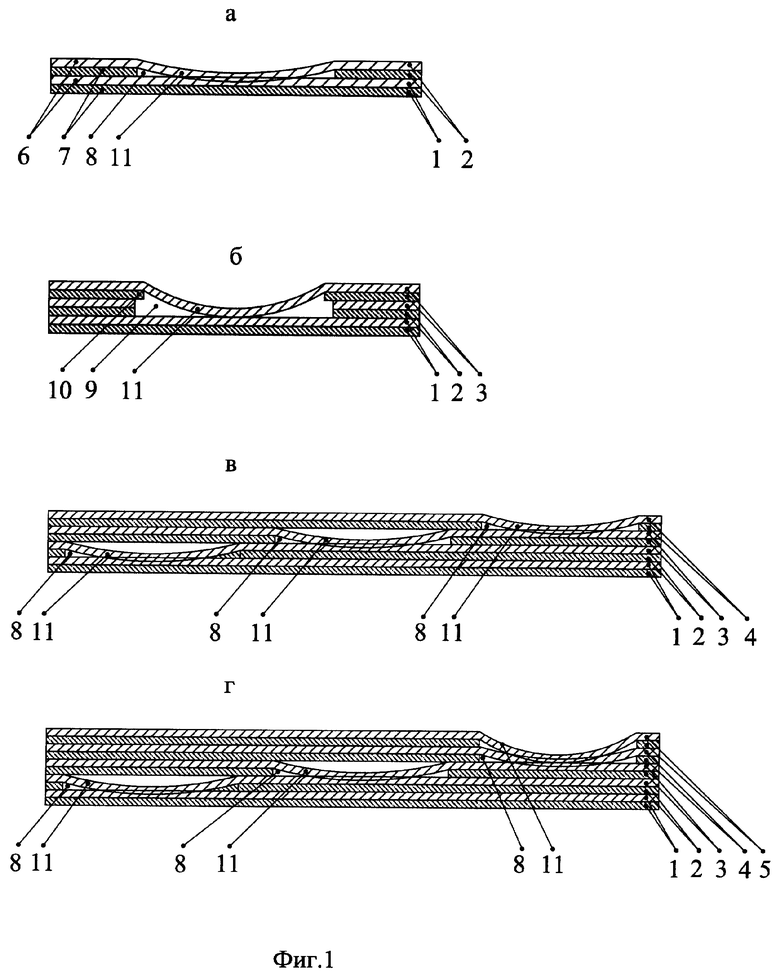

на фиг.3 - конкретный пример соединения с односторонней платой (а), выполненной на основе керамической подложки, одноуровневых гибких тонкопленочных лакофольговых плат (б) и (в), с выносами (г, д) изображения полоски - элемента над окном в диэлектрическом слое платы под неразъемное соединение.

Заявляемый способ осуществляют следующим образом. В одноуровневых тонкопленочных платах 2-5 (см. фиг.1а-г), а также платах 12-19 (см. фиг.2а), содержащих слои - проводниковый 6 и диэлектрический 7 и представляющих собой, например, металлизированную полимерную пленку, полученную в результате нанесения проводникового металла, например меди, хрома, золота и других на полиимидную пленку или лакофольговую пленку, полученную в результате нанесения лакового покрытия на проводниковую фольгу, в диэлектрических слоях 7 этих плат выполняют окна 8 под последующие неразъемные соединения плат 1-5 (см. фиг.1а-г), а также плат 12-20 (см. фиг.2а) между собой, и при топологической необходимости в промежуточных одноуровневых тонкопленочных платах выполняют сквозные окна под неразъемные соединения одновременно нескольких плат между собой, в частности, в плате 2 - сквозное окно 9 с напуском 10 диэлектрического слоя 7 платы 3 под неразъемное соединение плат 1-3 между собой с использованием напуска 10 для предотвращения замыкания проводникового слоя 6 платы 2 с проводниковыми слоями 6 плат 1-3 при последующем создании неразъемного соединения в окне 9 (см. фиг.1б). При этом во время получения рисунка проводников в одноуровневых платах 2-5 и 12-19 над окнами 8 сохраняют участки 11 проводникового слоя 6, в виде исходных полосок - элементов 29 и 30 под последующие неразъемные соединения таких плат (см. фиг.3г, д) с включением в рисунок проводников участков 11 в виде полосок - элементов 29 под неразъемные соединения плат, сочетающие в себе функции межуровневой коммутации и конструкционного скрепления, и без включения в рисунок проводников участков 11 в виде полосок - элементов 30 под неразъемные соединения плат, несущие функцию только конструкционного скрепления.

Затем подготовленные для соединения в многослойную конструкцию, платы 1-5 (см. фиг.1а-г), поочередно совмещают, приводя в контактное положение их участки 11 проводниковых слоев 6 в окнах 8, и создают в них по ходу последовательного совмещения плат посредством, например, микросварки, неразъемные соединения участков 11 соседних плат между собой, начиная с соединения участка 11 платы 2 с проводниковым слоем 6 платы 1, включая варианты создания неразъемного соединения плат 1-3 через сквозное окно 9 (см. фиг.1б), и со ступенчатым разнесением окон 8 соединяемых плат 1-4 для уменьшения прогиба соединяемых участков 11 (см. фиг.1в).

Для увеличения конструкционной прочности микросхемы в процессе ее формирования поочередным созданием неразъемных соединений одноуровневых плат 1-5 между собой предусмотрена возможность нанесения между платами клеевых композиций или для увеличения эксплуатационного запаса прочности микросхемы после формирования ее многослойной конструкции посредством неразъемных соединений плат 1-5 между собой, микросхему окунают в полиимидный лак с последующей фотолитографией поверхности микросхемы для вскрытия в ней участков под монтаж навесных компонентов и имидизацией полиимидного лака воздействием на него ультрафиолетовыми лучами (на фиг.1-3 обе операции не отражены).

Предлагаемый способ предусматривает последовательное соединение одноуровневых тонкопленочных плат 12-19 (см. фиг.2а), начиная с соединения с двухсторонней платой 20, выполненной на основе общей для всей многоуровневой микросхемы жесткой диэлектрической подложки 21, например, керамики, анодированного алюминия, стеклотекстолита или металлической подложки, по обе стороны от этой подложки с обеспечением непрерывности коммутации многоуровневого рисунка проводников посредством пропускания фрагмента 22 гибкой одноуровневой тонкопленочной платы через отверстие 23 в подложке 21 (см. фиг.2б) или металлизации такого отверстия в начальной стадии изготовления, а также завершение формирования многоуровневой микросхемы присоединением к соединенным между собой одноуровневым тонкопленочным платам с обеих их сторон дополнительных одноуровневых плат, выполненных на основе жесткой подложки и снабженных средствами механического соединения многослойной микросхемы, например, конструктивными крепежными элементами для усиления скрепления плат по периметру конструкции микросхемы (на фиг.1-3 вторая операция не отражена).

В конкретном примере изготовления многоуровневой микросхемы (см. фиг.3) в качестве исходной платы (а) взята керамическая подложка из Поликора 22ХС с размерами 60×48×1,0 мм с полученными с помощью вакуумного напыления и фотолитографии односторонним рисунком проводников 24 из меди (или алюминия) и участками 25 проводникового слоя под конструкционное скрепление с присоединяемыми платами, а также с просверленными отверстиями 26 для совмещения соединяемых плат. Для соединения с платой (а) подготовлены тонкопленочные платы (б) и (в) из материала ДЛПМ (ЫУ 037102 ТУ), представляющие собой лакофольговую пленку с толщиной проводникового слоя из меди (или алюминия) 30 мкм и диэлектрического слоя - полиимидной пленки 25 мкм с полученными на этих заготовках фотолитографией и травлением рисунком проводников 24 и окнами 27 для межуровневой коммутации, совмещенной с конструкционным скреплением, и окнами 28 для скрепления без коммутации с сохранением над обоими типами окон, соответственно, полосок - элементов 29 и 30 проводникового слоя под последующую сварку, а также окнами 31 под установку дискретных элементов микросхемы.

Для формирования многослойной структуры изготавливаемой микросхемы (слои в количестве трех показаны на фиг.3 для подтверждения промышленной применимости заявляемого способа) технологическая оснастка - проста и надежна и представляет собой (на фигурах не показана) корпус с направляющими стержнями для отверстий 26 для совмещения заготовок с несложными приспособлениями для приведения в положение контакта соединяемых участков проводниковых слоев в виде полосок - элементов 29 и 30 и их микроконтактной сварки через окна 27 и 28 на установке типа УС.ИММ-2 с управлением с помощью микроконтроллера на базе процессора AT 89 LS 8252 "Atmell"

Предлагаемый способ изготовления в настоящее время находится в стадии промышленного освоения и позволит повысить степень интегральности межуровневых микросхемных соединений, в том числе за счет повышения числа соединяемых заготовок - до 15-ти и более и производительности изготовления многослойных интегральных структур в 1,5-2,0 раза с удешевлением технологии изготовления в 3-4 раза в сравнении с прототипом.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИЗГОТОВЛЕНИЯ ТОНКОПЛЕНОЧНЫХ МНОГОУРОВНЕВЫХ ПЛАТ ДЛЯ МНОГОКРИСТАЛЬНЫХ МОДУЛЕЙ, ГИБРИДНЫХ ИНТЕГРАЛЬНЫХ СХЕМ И МИКРОСБОРОК | 2011 |

|

RU2459314C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МНОГОУРОВНЕВЫХ ТОНКОПЛЕНОЧНЫХ МИКРОСХЕМ | 2011 |

|

RU2474004C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МНОГОСЛОЙНЫХ ГИБКО-ЖЕСТКИХ ИНТЕГРАЛЬНЫХ ПЛАТ | 2012 |

|

RU2489814C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ТОНКОПЛЕНОЧНОЙ МИКРОСХЕМЫ | 1991 |

|

RU2040131C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МИКРОПЛАТ С МНОГОУРОВНЕВОЙ ТОНКОПЛЕНОЧНОЙ КОММУТАЦИЕЙ | 2009 |

|

RU2398369C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ТОНКОПЛЕНОЧНОЙ СТРУКТУРЫ ГИБРИДНОЙ ИНТЕГРАЛЬНОЙ МИКРОСХЕМЫ СВЕРХВЫСОКОЧАСТОТНОГО ДИАПАЗОНА | 2005 |

|

RU2293400C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ТОНКОПЛЕНОЧНОЙ МИКРОСХЕМЫ | 1989 |

|

SU1816170A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МНОГОУРОВНЕВОЙ КОММУТАЦИИ ИНТЕГРАЛЬНЫХ МИКРОСХЕМ | 1992 |

|

RU2017353C1 |

| Гибкая прецизионная плата | 2018 |

|

RU2706213C2 |

| СПОСОБ ИЗГОТОВЛЕНИЯ РАДИОЭЛЕКТРОННЫХ УЗЛОВ | 2014 |

|

RU2575641C2 |

Использование: в области микроэлектроники при изготовлении многослойных структур на подложках из различных материалов, а именно, многоуровневых тонкопленочных интегральных микросхем с многоуровневой коммутацией. Технический результат - упрощение техпроцесса и повышение производительности изготовления многоуровневых тонкопленочных микросхем, повышение степени их интеграции и эффективности использования проводникового слоя, расширение ассортимента изделий за счет обеспечения работоспособности предлагаемой технологии в широком интервале толщин слоев изготавливаемых многоуровневых интегральных микросхем, универсализация и расширение области применения способа за счет его совместимости с традиционной технологией изготовления микросхем, а также удешевление изготовления в результате снижения затрат на материалы и оборудование для изготовления многоуровневых микросхем. Сущность изобретения: в способе изготовления многоуровневых тонкопленочных микросхем, включающем получение в проводниковых слоях рисунка проводников и выполнение в диэлектрических слоях окон методом фотолитографии и формирование из проводниковых и диэлектрических слоев многослойной интегральной микросхемы, имеющей межуровневую коммутацию в виде электрических соединений, созданных в окнах диэлектрических слоев, микросхему формируют путем последовательного совмещения отдельных одноуровневых тонкопленочных плат между собой и создания в окнах диэлектрических слоев этих плат неразъемных соединений, сочетающих в себе функции межуровневой коммутации - электрического соединения и конструкционного скрепления - механического соединения, посредством, например, микросварки приведенных в положение взаимного контакта участков проводниковых слоев, предварительно топологически предусмотренных над окнами во время получения рисунка проводников, и в случае недостаточности конструкционной прочности микросхемы ее формирование сопровождают созданием в дополнительных окнах диэлектрических слоев плат неразъемных соединений, несущих функцию только конструкционного скрепления, посредством, например, микросварки, приведенных в положение взаимного контакта участков проводниковых слоев, предварительно топологически предусмотренных над дополнительными окнами во время получения рисунка проводников без включения этих участков в него, при этом формирование микросхемы производят через оба типа окон, выполненных с осями, совпадаемыми при совмещении плат, и при увеличении числа соединяемых плат - через окна с осями, разнесенными в совмещаемых платах для уменьшения прогиба соединяемых участков проводниковых слоев, включая при топологической необходимости создание неразъемных соединений контактируемых участков проводниковых слоев в сквозных окнах в промежуточных платах. 7 з.п. ф-лы, 3 ил.

| СПОСОБ ИЗГОТОВЛЕНИЯ ТОНКОПЛЕНОЧНОЙ МИКРОСХЕМЫ | 1989 |

|

SU1816170A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ТОНКОПЛЕНОЧНОЙ МИКРОСХЕМЫ | 1991 |

|

RU2040131C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МНОГОУРОВНЕВОЙ КОММУТАЦИИ ИНТЕГРАЛЬНЫХ МИКРОСХЕМ | 1992 |

|

RU2017353C1 |

| US 5950102 A, 07.09.1999 | |||

| US 4508749 А, 02.04.1985. | |||

Авторы

Даты

2005-11-20—Публикация

2004-03-29—Подача