Предлагаемое изобретение относится к микроэлектронике в области приборостроения и может быть использовано при разработке конструкции и технологических процессов изготовления тонкопленочных многоуровневых плат повышенной степени интеграции для гибридных интегральных схем (ГИС), микросборок (МСБ) и многокристальных модулей (МКМ), обеспечивающих стабильную работу устройств, собранных на разработанном коммутационном основании в области высоких тактовых частот.

При изготовлении многослойных тонкопленочных структур следует принимать во внимание, что при малых толщинах диэлектрических слоев велико влияние сквозной пористости, приводящей к возникновению коротких замыканий между уровнями коммутации. Увеличение толщины диэлектрика вызывает возрастание роли внутренних механических напряжений, приводящих к отслаиванию. Кроме того, появляется проблема надежной металлизации «ступенек» в местах переходов с одного уровня металлизации на другой, переходящая в проблему межслойной паразитной емкости при уменьшении толщины диэлектрического слоя.

Известен способ изготовления многоуровневых плат, в которых межслойные изоляционные слои на подложке получают нанесением полимерного материала при центрифугировании, причем их формируют с помощью маски, имеющей окна. Маска закреплена на поверхности подложки магнитным полем. Центрифугирование проводят со скоростью 1500 об/мин. Нанесение полимерного материала осуществляют при нагревании подложки до температуры полимеризации с последующим охлаждением. Причем маску используют из материала с температурным коэффициентом линейного расширения (ТКЛР), большим ТКЛР материала подложки в 2-6 раз. Заявляемый способ и устройство позволяют значительно повысить технологичность и снизить трудоемкость процесса получения диэлектрических слоев на локальных участках подложки (Патент РФ №2076478, МПК H05K 3/46, опубл. 20.01.1995).

Недостатком известного способа являются ограниченная применимость данного метода (только для локальных участков) и предельные размеры и точность изготовления изоляционных участков, сложность в изготовлении разработанной конструкции.

Известен способ изготовления многоуровневых плат, где решается проблема межслойного разделения проводников при изготовлении ГИС, включающий создание рисунка нижнего слоя коммутации путем вакуумного напыления проводящего материала на поверхность диэлектрической подложки и проведения процесса фотолитографии, нанесения на поверхность подложки изоляционного слоя, например фоторезиста ФН-103, закрывающего участки нижнего слоя проводников в местах их скрещивания с проводниками верхнего слоя, полимеризации изоляционного слоя и формирования верхнего слоя проводников, например, путем вакуумного напыления и проведения процесса фотолитографии (Гимпельсон В.Д., Родионов Ю.А. Тонкопленочные микросхемы для приборостроения. М.: Машиностроение, 1976, с.254).

Недостаток известного способа состоит в наличии рельефа на поверхности подложки. Рельеф на поверхности подложки возникает из-за резкого перепада высот («ступенек») на границе проводников толщиной 0,8-1,2 мкм и участков межслойной изоляции толщиной 10 мкм. Существование рельефа на поверхности подложки значительно затрудняет напыление проводников одинаковой толщины и способствует появлению обрывов проводников верхнего слоя коммутации на границе участков межслойной изоляции, что негативно отражается на надежности сборки.

Известен способ изготовления двухуровневой тонкопленочной коммутационной платы, включающий формирование топологического рисунка первого электропроводного слоя и межслойной изоляции, травление переходных отверстий, формирование топологического рисунка второго электропроводного слоя, формирование защитного диэлектрика, вскрытие контактных отверстий и их облуживание, при этом для упрощения технологии и повышения надежности платы путем исключения коротких замыканий между электропроводными слоями двух уровней контактные площадки электропроводных слоев размещают с взаимным перекрытием не менее чем на удвоенную толщину межслойной изоляции, переходные отверстия выполняют в зоне частичного перекрытия контактных площадок, а травление переходных отверстий выполняют одновременно после формирования защитного диэлектрика. (Патент SU №1614739, МПК H05K 3/00, опубл. 20.12.2005).

Недостатком известного способа является необходимость выравнивания рельефа и трудоемкость при облуживании переходных отверстий, необходимость наличия больших контактных площадок, малая топологическая плотность проводящих слоев, большая вероятность внесения дефектов при обработке припоем.

Наиболее близким к предлагаемому способу является способ, взятый в качестве прототипа, в котором для получения планарной структуры проводят гальваническое наращивание меди. Способ включает в себя последовательное вакуумное осаждение на керамическую подложку слоев ванадий-медь-ванадий и формирование нижнего уровня коммутации фотолитографией, нанесение технологического слоя ванадия и формирование в нем окон на участках межслойной изоляции, которую формируют нанесением слоя полиимида, вскрытие в нем окон для межслойных переходов и последующее удаление технологического слоя ванадия с помощью селективного травления, после чего производят последовательное вакуумное осаждение сплошных слоев ванадия и меди с гальваническим наращиванием слоя меди и последующее формирование рисунка проводников верхнего уровня коммутации с помощью фотолитографии (патент РФ №02040131, МПК Н05K 3/46, опубл. 20.07.1995 г.).

Недостатком способа-прототипа является необходимость выравнивания рельефа путем наращивания толщины второго проводникового слоя, что ведет к увеличению напряженности слоя и, как следствие, ухудшение адгезии проводниковых слоев к межслойной изоляции. При изготовлении многоуровневой платы с числом слоев более двух это становится актуальным, поскольку с увеличением числа слоев напряженность проводящих слоев платы суммируется.

Задачей авторов изобретения является разработка конструкции и технологии изготовления тонкопленочной многоуровневой платы для МКМ, ГИС и МСБ, обеспечивающей стабильную работу устройств, спроектированных на ее основе.

Новый технический результат изобретения заключается в повышении устойчивости работы устройств, собранных на разработанном коммутационном основании в области высоких тактовых частот за счет применения отдельных «потенциальных» слоев большой площади, что снижает электрическое сопротивление цепей «земля» и «питание»; повышении плотности компоновки ГИС, МКМ и МСБ за счет применения принципа многоуровневости, что ведет к повышению степени интеграции, снижению массогабаритных характеристик; упрощении технологического процесса в результате применения принципа «ступенчатости» для формирования межуровневых переходов и мест пересечения проводников; обеспечении гарантированной сварки готовых плат при монтаже навесных компонентов за счет расположения всех контактных площадок в первом проводящем слое.

Дополнительный технический результат заключается в повышении температуростойкости платы за счет применения полиимидного лака АД9103.

Указанные задача и новый технический результат обеспечиваются тем, что в известном способе изготовления многоуровневых тонкопленочных плат для МКМ, ГИС и МСБ, включающем подготовку базовой платы, на которой формируются уровни коммутации последовательным нанесением слоев металлизации в вакууме и формированием топологии первого и последующих уровней коммутации в виде заданного токопроводящего контура методом фотолитографии в сочетании с чередованием последовательного нанесения слоев межуровневой изоляции в виде органического диэлектрика центрифугированием и последующим формированием топологии слоев изоляции, с образованием контактных окон, контактных площадок и участков пересечения проводников, разведение уровней коммутации с использованием контактных окон, согласно изобретению все контактные площадки схемы как для последующего соединения их с выводами активных компонентов ГИС, или МКМ, или микросборок, так и контактные площадки для электрического соединения к внешним выводам ГИС, или МКМ, или микросборок располагают в первом проводящем уровне, выполненном в виде многослойного покрытия V-Cu-Ni + химический Ni, где химический Ni используют в качестве стоп-слоя при формировании последующих уровней коммутации, разведение проводниковых слоев «сигнальный» и потенциальных - «питание» и «земля» осуществляют в индивидуальных уровнях, применяют принцип «ступенчатости» чередующихся слоев металлизации и изоляции для мест расположения пересечения проводников разных уровней коммутации и мест расположения межуровневых соединений, для чего выполняют межуровневые переходы в виде ступенчатонисходящих размеров отверстий (контактные окна) в каждом слое, а формирование межуровневых соединений и слоев металлизации осуществляют в одном технологическом цикле путем напыления на внутренние поверхности указанных отверстий слоя металлизации с последующим формированием их топологии, формирование последовательно наносимых слоев межуровневой многослойной изоляции осуществляют в каждом уровне коммутации из светочувствительного органического диэлектрика методом фотолитографии.

Кроме того, в качестве изоляционного материала используют полиимидный лак АД9103, формирование топологии изоляционных слоев производят плазмохимическим травлением в среде кислорода через контактные металлизированные защитные маски.

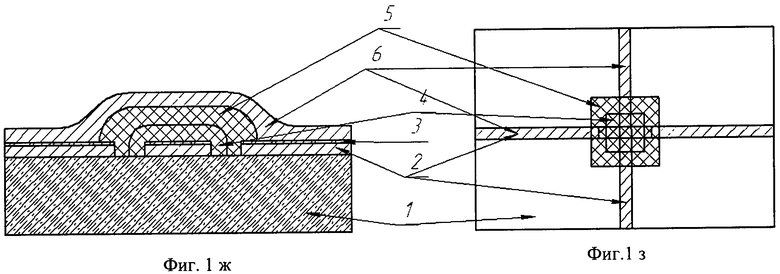

Предлагаемый способ поясняется следующим образом. Многоуровневая плата содержит следующие слои: 1-й слой - первый проводящий уровень V-Cu-Ni-хим.Ni; 2-й и 3-й слои - изоляционные слои в виде отдельных ступенчатовосходящих квадратов в местах пересечения проводников первого и второго уровней; 4-й слой - второй проводящий уровень; 5-й и 6-й слои - изоляционные слои со ступенчатонисходящими квадратами отверстий в местах межуровневых соединений; 7-й слой - третий проводящий уровень; 8-й слой - защитный. Изготовление тонкопленочных многоуровневых плат для МКМ, ГИС и МСБ основано на вакуумном напылении всех уровней коммутации с последующими отдельными циклами фотолитографии для создания топологии соответствующего проводникового уровня, нанесении между ними центрифугированием и формированием межслойной изоляции на основе органического светочувствительного диэлектрика, формирование рисунка межслойной изоляции проводят методом фотолитографии, одновременно формируют межуровневые переходы в требуемых местах перехода в виде послойной ступенчатой структуры.

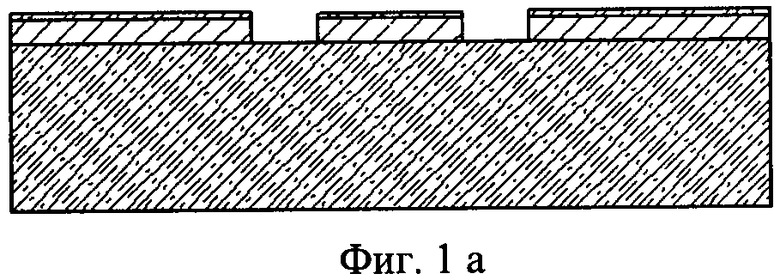

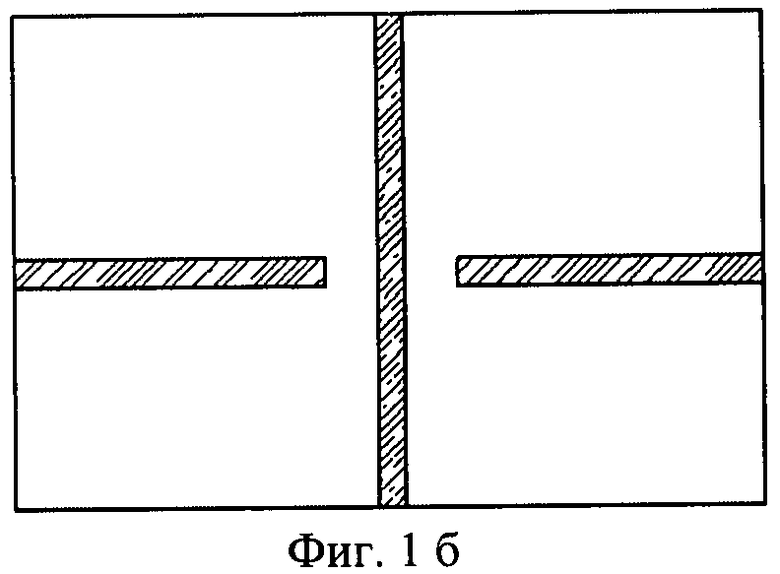

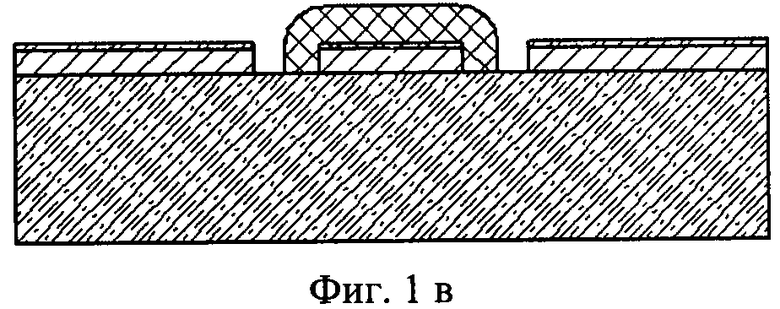

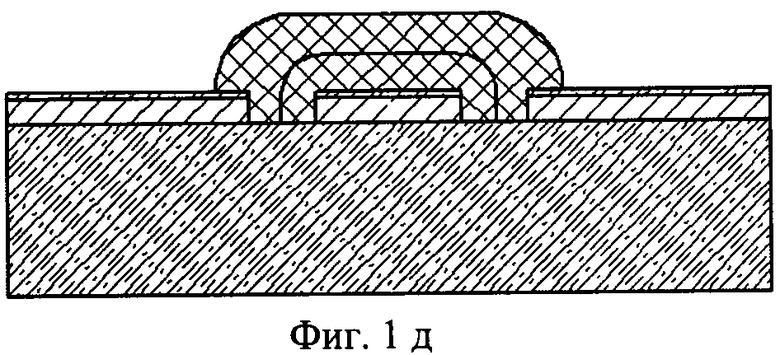

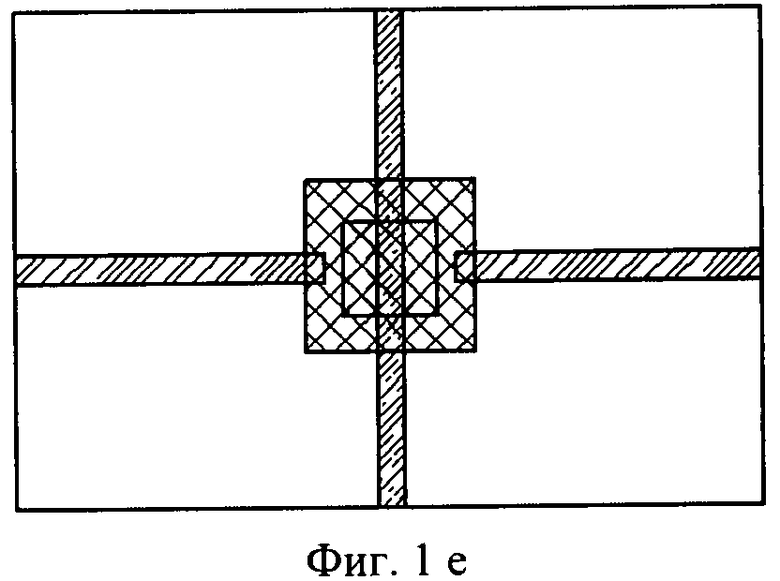

На фиг.1а-з представлен техпроцесс изготовления пересекающихся проводников и изоляции между ними, где 1 - изоляционная подложка, 2 - первый проводниковый уровень, 3 - слой химического никеля, 4 - первый слой первой межуровневой изоляции, 5 - второй слой первой межуровневой изоляции, 6 - второй проводниковый уровень.

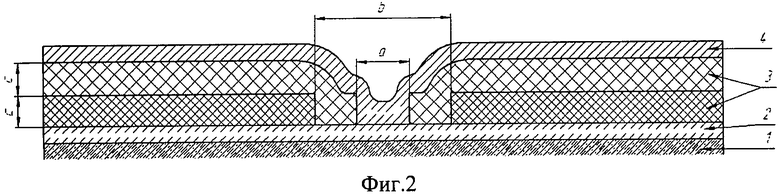

На фиг.2 представлена схема осуществления межуровневого перехода смежных проводниковых слоев, где 1 - подложка, 2 - нижний проводниковый уровень, 3 - первый и второй слои изоляции, 4 - верхний проводниковый уровень.

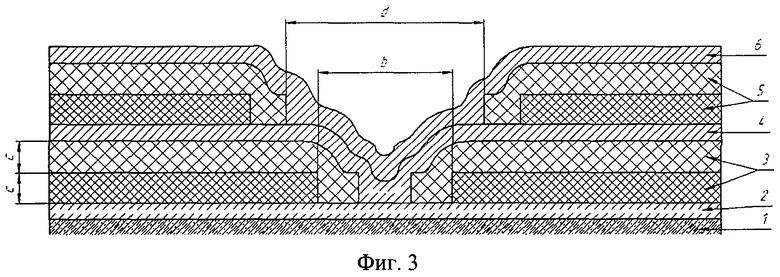

На фиг.3 представлена схема осуществления межуровневого перехода для сквозного соединения проводников, где 1 - изоляционная подложка, 2 - проводник первого уровня, 3 - первый и второй слои первого изоляционного слоя, 4 - проводник второго уровня, 5 - первый и второй слои второго изоляционного слоя, 6 - третий проводниковый уровень.

Для обеспечения плавного межуровневого перехода второй слой в изоляционном слое должен перекрывать нижний слой изоляции на величину не менее толщины изоляционного слоя, т.е. для осуществления надежных межуровневых соединений необходимо учитывать следующее: отличие размера окна во втором слое любой изоляции (поз.b, фиг.2) должна быть больше размера окна первого слоя этого же изоляционного слоя на величину не менее двойной толщины слоя изоляции (поз.с, фиг.2), т.е. должно выполняться условие:

b-a≥2c

Аналогично сохраняется соотношение размеров для вышележащих изоляционных слоев по отношению к нижележащим (фиг.3):

d-a≥4c

Это условие относится и к изоляции пересекающихся проводников: размер верхнего изоляционного большего квадрата изоляционного слоя (поз.5 фиг.1ж и 1з) должна быть больше размера меньшего квадрата (поз.4 фиг.1,ж и 1,з) на величину не менее чем две толщины изоляционного слоя.

Сравнительный анализ предлагаемого способа с прототипом показал, что в прототипе при изготовлении тонкопленочных многоуровневых плат для многокристальных модулей и микросборок применяют прием колодцеобразного межуровневого перехода, что повышает требования к планарности уровней коммутации, тогда как в предлагаемом способе при использовании принципа ступенчатого межуровневого перехода и мест пересечения проводников планарность не критична, что позволяет увеличить надежность межуровневого перехода при разведении слоев коммутации через технологические окна и мест пересечения проводников, не применяют слой химического никеля в качестве стоп-слоя при формировании последующих уровней проводников, а также наличие более двух уровней, в котором сигнальные проводники и потенциальные разведены в разных уровнях, что обеспечивает уменьшение сопротивления шин «питание» и «земля», что подтверждает соответствие предлагаемого способа критерию изобретения "изобретательский уровень", выявил наличие новых операций, иную их последовательность, а именно следующую.

Первоначально на поверхности диэлектрической (ситалловой, поликоровой или металлической с диэлектрическим покрытием) платы наносят методом магнетронного распыления в вакууме многослойную тонкопленочную пленку V-Cu-Ni толщиной не менее 1,5 мкм, формируют методом фотолитографии топологию проводников первого уровня и контактных площадок, на поверхности которых выращивают слой химического никеля толщиной от 0,8 до 1,2 мкм, используемый в качестве стоп-слоя (фиг.1,а и фиг.1,б), наносят центрифугированием и полимеризуют фоточувствительный органический диэлектрик (например, фоторезист ФП-2550) толщиной от 2,3 до 3,7 мкм, формируют топологию первого слоя первой изоляции методом фотолитографии (фиг.1,в и фиг.1,г). Наносят второй слой первой изоляции и формируют его аналогично первому слою (фиг.1,д и фиг.1,е). Наносят в вакууме и формируют методом фотолитографии топологию проводника второго уровня V-Cu-V толщиной не менее 1,9 мкм (фиг.1,ж и фиг.1,з). Последующие уровни проводников и изоляции формируются аналогично описанным выше. Материалом последующих проводниковых слоев является V-Cu-V толщиной не менее 1,9 мкм. Последним слоем формируют защитный слой, топология которого покрывает всю плату за исключением контактных площадок.

Таким образом, использование всех процедур и условий предлагаемого способа обеспечивает повышение плотности компоновки ГИС, МКМ и МСБ за счет применения принципа многоуровневости, что ведет к повышению степени интеграции, снижению массогабаритных характеристик; упрощение технологического процесса в результате применения принципа «ступенчатости» для формирования межуровневых переходов и мест пересечения проводников; обеспечение гарантированной сварки готовых плат при монтаже навесных компонентов за счет расположения всех контактных площадок в первом проводящем слое.

Возможность промышленной применимости изобретения подтверждается следующим примером.

Пример 1.

В лабораторных условиях предлагаемый способ опробован на опытном образце. Предлагаемый способ изготовления плат с многоуровневой коммутацией содержит следующие операции.

1. Обработка ситалловых (поликоровых) подложек традиционным химическим способом, например, в аммиачно-перекисном растворе.

2. Нанесение многослойного тонкопленочного покрытия V-Cu-Ni методом магнетронного распыления с общей толщиной не менее 1,5 мкм.

3. Формирование топологии первого проводящего слоя методом фотолитографии.

4. Осаждение химического никеля толщиной от 0,8 до 1,2 мкм.

5. Отжиг слоя химического никеля, осажденного на поверхности пленочных элементов платы, при температуре от 260 до 270°C в течение 1 часа.

6. Формирование первого слоя первой изоляции

- нанесение фоторезиста ФП-2550 на подложки центрифугированием,

- сушка фоторезиста в два этапа: сначала подложки выдерживают при комнатной температуре в течение 25 мин в закрытой таре, а затем в термошкафу при температуре 90°C в течение 40 мин,

- экспонирование в течение (40-60) с при освещенности от 35000 до 45000 Лк и проявление фоторезиста, сушка при температуре 120, 150°C по 20 минут; 180°C - 1 час.

7. Формирование второго слоя первой изоляции проводят аналогично п.6.

8. Нанесение второго проводящего уровня - многослойного тонкопленочного покрытия V-Cu-V методом магнетронного распыления.

9. Формирование топологии второго проводящего уровня методом фотолитографии.

10. Нанесение и формирование первого и второго слоев второй изоляции проводят в соответствии с п.6.

11. Нанесение и формирование топологии проводниковых слоев третьего уровня проводят в соответствии с пп.8, 9.

13. Формирование защитного слоя методом фотолитографии из фоторезиста ФП-2550 согласно п.6.

Предлагаемый способ позволил изготовить микроплаты с 3 уровнями коммутации, которые имели следующие характеристики:

- удельное поверхностное сопротивление проводников не более 0,02 Ом/□,

- переходное сопротивление 0,02 Ом,

- сопротивление изоляции - более 20 МОм.

- получена стабильная адгезия металлизированных слоев «ванадий-медь-ванадий» к большой площади поверхности изоляционного слоя на основе фоторезиста ФП-2550.

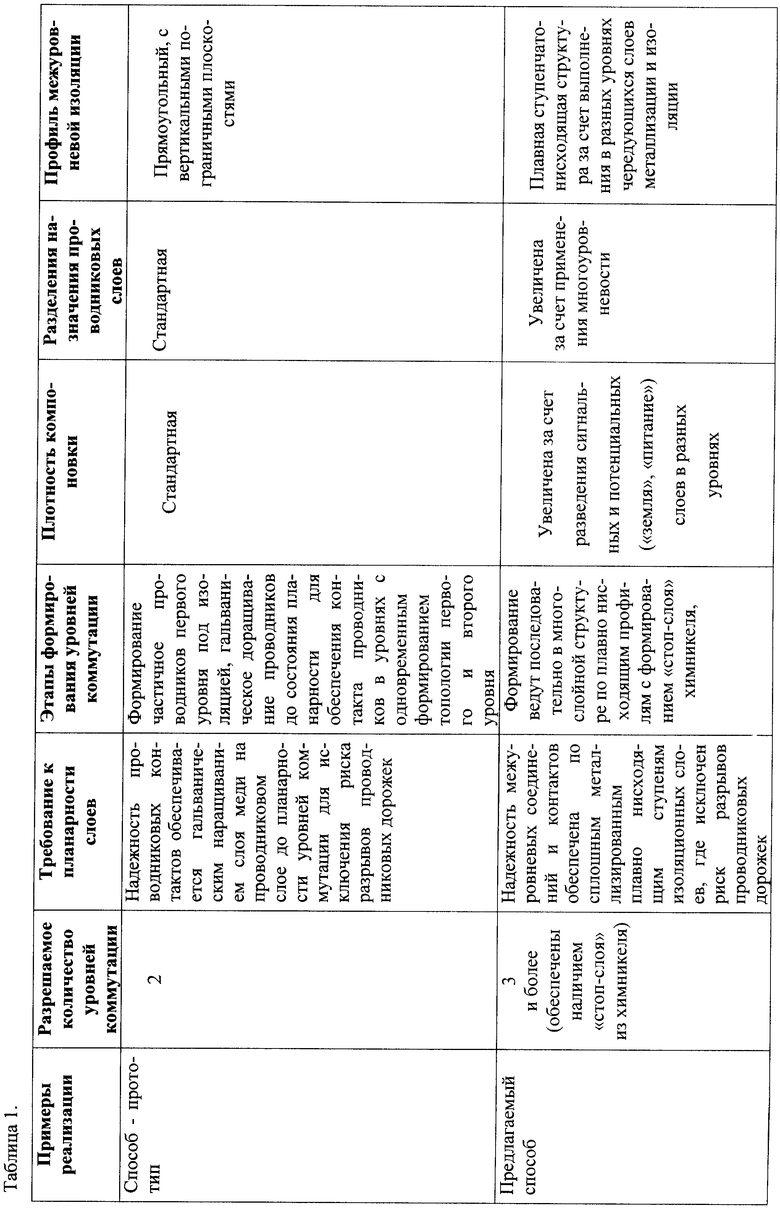

Результаты реализации предлагаемого способа сведены в таблицу 1.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИЗГОТОВЛЕНИЯ МНОГОУРОВНЕВЫХ ТОНКОПЛЕНОЧНЫХ МИКРОСХЕМ | 2004 |

|

RU2264676C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МНОГОУРОВНЕВЫХ ТОНКОПЛЕНОЧНЫХ МИКРОСХЕМ | 2011 |

|

RU2474004C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МИКРОПЛАТ С МНОГОУРОВНЕВОЙ ТОНКОПЛЕНОЧНОЙ КОММУТАЦИЕЙ | 2009 |

|

RU2398369C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ТОНКОПЛЕНОЧНОЙ МИКРОСХЕМЫ | 1991 |

|

RU2040131C1 |

| Способ изготовления СВЧ-гибридной интегральной микросхемы космического назначения с многоуровневой коммутацией | 2019 |

|

RU2713572C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ГИБРИДНЫХ ИНТЕГРАЛЬНЫХ СХЕМ | 1995 |

|

RU2079212C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МНОГОСЛОЙНЫХ ГИБКО-ЖЕСТКИХ ИНТЕГРАЛЬНЫХ ПЛАТ | 2012 |

|

RU2489814C1 |

| Способ изготовления микроэлектронного узла | 2016 |

|

RU2645151C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МНОГОУРОВНЕВОЙ КОММУТАЦИИ ИНТЕГРАЛЬНЫХ МИКРОСХЕМ | 1992 |

|

RU2017353C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ РАДИОЭЛЕКТРОННЫХ УЗЛОВ | 2014 |

|

RU2575641C2 |

Изобретение относится к микроэлектронике. Техническим результатом изобретения является повышение устойчивости работы устройств, повышение плотности компоновки, снижение габаритно-весовых характеристик, а также упрощение технологического процесса и обеспечение гарантированной сварки готовых плат при монтаже навесных компонентов за счет расположения всех контактных площадок в первом проводящем слое. Сущность изобретения: в способе изготовления тонкопленочных многоуровневых плат для многокристальных модулей, микросборок и гибридных интегральных схем, включающем подготовку базовой платы, на которой формируются уровни коммутации последовательным нанесением слоев металлизации и формированием топологии первого и последующих уровней коммутации, согласно изобретению все контактные площадки схемы как для последующего соединения их с выводами активных компонентов, так и контактные площадки для электрического соединения к внешним выводам располагают в первом проводящем уровне, выполненном в виде многослойного покрытия V-Cu-Ni + химический Ni, где химический Ni используют в качестве стоп-слоя при формировании последующих уровней коммутации, разведение проводниковых слоев «сигнальный» и потенциальных - «питание» и «земля» осуществляют в индивидуальных уровнях. 1 з.п.ф-лы, 1 табл., 10 ил.

1. Способ изготовления тонкопленочных многоуровневых плат для многокристальных модулей, гибридных интегральных схем и микросборок, включающий подготовку базовой платы, на которой формируются уровни коммутации последовательным нанесением слоев металлизации в вакууме и формированием топологии первого и последующих уровней коммутации в виде заданного токопроводящего контура методом фотолитографии в сочетании с чередованием последовательного нанесения слоев межуровневой изоляции в виде органического диэлектрика центрифугированием и последующим формированием топологии слоев изоляции с образованием контактных окон, контактных площадок и участков пересечения проводников, разведение уровней коммутации с использованием контактных окон, отличающийся тем, что все контактные площадки схемы как для последующего соединения их с выводами активных компонентов ГИС, или МКМ, или микросборок, так и контактные площадки для электрического соединения к внешним выводам ГИС, или МКМ, или микросборок располагают в первом проводящем уровне, выполненном в виде многослойного покрытия V-Cu-Ni + химический Ni, где химический Ni используют в качестве стоп-слоя при формировании последующих уровней коммутации, разведение проводниковых слоев «сигнальный» и потенциальных - «питание» и «земля» осуществляют в индивидуальных уровнях, применяют принцип «ступенчатости» чередующихся слоев металлизации и изоляции для мест расположения пересечения проводников разных уровней коммутации и мест расположения межуровневых соединений, для чего выполняют межуровневые переходы в виде ступенчатонисходящих размеров отверстий (контактные окна) в каждом слое, а формирование межуровневых соединений и слоев металлизации осуществляют в одном технологическом цикле путем напыления на внутренние поверхности указанных отверстий слоя металлизации с последующим формированием их топологии, формирование последовательно наносимых слоев межуровневой многослойной изоляции осуществляют в каждом уровне коммутации из светочувствительного органического диэлектрика методом фотолитографии.

2. Способ по п.1, отличающийся тем, что в качестве изоляционного материала используют полиимидный лак АД9103, формирование топологии изоляционных слоев производят плазмохимическим травлением в среде кислорода через контактные металлизированные защитные маски.

| СПОСОБ ИЗГОТОВЛЕНИЯ ГИБРИДНЫХ ИНТЕГРАЛЬНЫХ СХЕМ | 1995 |

|

RU2079212C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МНОГОУРОВНЕВЫХ ТОНКОПЛЕНОЧНЫХ МИКРОСХЕМ | 2004 |

|

RU2264676C1 |

| МНОГОСЛОЙНАЯ КОММУТАЦИОННАЯ ПЛАТА (ВАРИАНТЫ) | 1998 |

|

RU2133081C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ДВУХУРОВНЕВОЙ ТОНКОПЛЕНОЧНОЙ КОММУТАЦИОННОЙ ПЛАТЫ | 1988 |

|

SU1614739A1 |

| SU 1358777 A1, 20.06.1996 | |||

| JP 2010016143 A, 21.01.2010 | |||

| JP 2009289850 A, 10.12.2009 | |||

| JP 2008147235 A, 26.06.2008 | |||

| JP 2005294674 A, 20.10.2005 | |||

| JP 2005109188 A, 21.04.2005. | |||

Авторы

Даты

2012-08-20—Публикация

2011-04-06—Подача