Предлагаемые технические решения объединены единым изобретательским замыслом, относится к области радиотехники, а именно автоматики и могут быть использованы в системах и устройствах обработки цифровой информации с резервированием.

Известны способы управления резервированными системами, описанные, например, в книге: Кейджян Г.А. Прогнозирование надежности микроэлектронной аппаратуры на основе БИС. - М.: Радио и связь, 1987, 152 с., заключающиеся в приеме информационной последовательности импульсов, ее обработке в трех каналах системы в соответствии с установленной функцией, оценке работоспособности каналов мажоритарным способом и подключении на выход системы исправного канала. Однако известные аналоги имеют недостатки, заключающиеся в низкой надежности принятия решения при больших затратах аппаратно-программных средств.

Наиболее близком по своей технической сущности к заявленному способу является способ, реализованный в устройстве дублированной системы с задержкой по А. с. N 1660231 СССР, МПК6 H 05 K 10/00, заявленному 03.04.89, опубликованному 30.06.91, бюллетень N 24. Способ-прототип заключается в приеме информационной последовательности импульсов, ее обработке в основном и резервном канале системы в соответствии с установленной функцией, задержке обработанных информационных последовательностях импульсов, сравнении информационных последовательностей импульсов после преобразования и при их совпадении подключении к каналу связи задержанной информационной последовательности импульсов с выхода основного канала. При несовпадении информационных последовательностей импульсов формируют сигнал соответствующий логической "1", записывают его, разрешая формирование управляющего сигнала блокировки. Выявляют работоспособность резервного канала по наличию чередования "1" и "0". Формируют управляющий сигнал на блокировку задержанной информационной последовательности импульсов с выхода основного канала и подключают задержанную информационную последовательность импульсов с выхода резервного канала в канал связи, если канал работоспособен. При отсутствии чередования управляющий сигнал не формируется и задержанная информационная последовательность импульсов с выхода основного канала остается подключенной к каналу связи.

Однако способ-прототип имеет недостаток: низкая вероятность точного определения состояния резервируемых устройств. Это объясняется тем, что при возникновении нарушений в работе резервируемых устройств не представляется возможным оценка с высокой вероятностью причин этих нарушений, т.е. является это следствием отказов (отказ - событие, заключающееся в нарушении работоспособного состояния объекта - ГОСТ 27.002-89. Надежность в технике. Основные понятия. Термины и определения) или сбоев (сбой - самоустраняющийся отказ, устраняемый незначительным вмешательством оператора - ГОСТ 27.002-89) в их работе и в каком из устройств это конкретно происходит. Следовательно в 50% случаев на выход резервируемой системы поступает искаженная информационная последовательность импульсов. Причем если эта информационная последовательность импульсов управляет другими объектами, то такая ситуация может привести к ошибочной команде.

Из известных наиболее близким к заявленному по своей технической сущности является устройство дублированной системы с задержкой по А.с. N 1660231 СССР, МПК6 H 05 K 10/00, заявленному 03.04.89. опубликованному 30.06.91, бюллетень N 24. Устройство прототип состоит из двух резервируемых устройств, двух регистров сдвига, сумматора по модулю 2, двух JK-триггеров, трех элементов И, одновибратора, элемента ИЛИ, D -триггера, элемента ИЛИ-НЕ, блока установки, входа дискретных устройств, шины синхронизации, двух выходных шин.

Входы двух резервируемых дискретных устройств объединены и соединены с входной шиной, а выходы соединены соответственно с управляющими входами первого и второго регистров сдвига, выходы которых подключены к первым входам соответственно первого и второго ключей реализованных на элементах И, выходы которых соединены соответственно с первым и вторым входом элемента ИЛИ, выход которого является выходом устройства, выходы первого и второго резервируемых дискретных устройств подключены соответственно к первому и второму входам сумматора по модулю 2, выход которого подключен к J-входу первого JK-триггера, прямой выход которого соединен с первым входом третьего элемента И, выход которого подключен к J-входу второго JK-тригера, прямой и инверсный выходы последнего соединены с вторыми входами соответственно первого и второго элементов И, К-входы обоих JK-триггеров подключены к общей шине, шина синхронизации соединена с синхронизирующими входами С первого и второго регистров сдвига и первого и второго JK-триггеров, синхронизирующий вход CD-триггера подключен к выходу первого дискретного устройства, а D-вход соединен с выходом одновибратора, вход которого подключен к выходу сумматора по модулю 2, прямой выход D-триггера соединен с вторым входом третьего элемента И, первый выход блока установки соединен с инверсными S-установочными входами всех трех триггеров, установочные инверсные R-входы которых подключены к второму выходу блока установки, прямой и инверсный выходы второго JK-триггера соединены соответственно с первым и вторым входами элемента ИЛИ-НЕ, выход которого являются выходом сигнализации устройства.

При такой схеме построения в прототипе повышается устойчивость функционирования резервируемой системы, по сравнению с устройствами-аналогами, за счет дополнительной возможности определения отказа типа "короткое замыкание" дискретного устройства.

Однако устройство-прототип имеет недостаток: низкая вероятность точного принятия решения на подключение резервного устройства. Это объясняется тем, что в прототипе могут быть определены только отказы, а сбои в работе устройств не могут быть выявлены, а, следовательно, отсутствует возможность запрета передачи искаженной информационной последовательности импульсов с выхода резервируемой системы в канал связи.

Целью изобретения заявленных технических решений является разработка способа управления дублированной системой с задержкой и дублированной системы, его реализующей, позволяющих повысить вероятность точного определения состояния резервируемых устройств за счет выявления как отказов, так и сбоев различной кратности и исключения возможности передачи искаженной информационной последовательности импульсов в канал связи.

Поставленная цель достигается тем, что в известном способе управления дублированной системой с задержкой, заключающемся в приеме информационной последовательности импульсов, ее обработке в основном и резервном каналах системы в соответствии с установленной функцией, задержке обработанных информационных последовательностей импульсов, оценке работоспособности каналов, блокировке неисправного канала и подключении на выход системы исправного канала, для оценки работоспособности основного и резервного каналов вычисляют параметры усечения этих каналов. Затем формируют сигналы усечения, соответствующие вычисленным параметрам усечения этих каналов. Сравнивают сигналы усечения с их заданными пороговыми значениями. При совпадении хотя бы одного сигнала с заданным пороговым значением в каждом из каналов производят блокировку обоих каналов и формируют сигнал полного отказа системы. При совпадении хотя бы одного сигнала с заданным пороговым значением только в одном из каналов, его блокируют и формируют сигнал отказа этого канала, а второй канал подключают к выходу системы. При несовпадении сигналов с заданными пороговыми значениями в обоих каналах, сравнивают полученные значения сигналов усечения между собой. При их совпадении на выход системы подключают основной канал. При их несовпадении блокируют оба канала и на их входы подключают тестовую последовательность импульсов. Обрабатывают ее в основном и резервном каналах в соответствии с установленной функцией и по обработанным тестовым последовательностям импульсов вычисляют параметры усечения для каждого канала. Формируют тестовые сигналы усечения соответствующие этим параметрам. Сравнивают тестовые сигналы усечения с эталонными значениями тестовых сигналов. При несовпадении тестовых сигналов усечения обоих каналов, формируют сигнал полного отказа системы. При несовпадении тестовых сигналов усечения в одном из каналов этот канал сохраняют заблокированным и формируют сигнал отказа этого канала, а второй канал подключают к выходу системы.

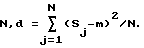

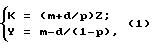

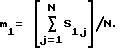

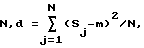

Для вычисления параметров усечения из обработанных информационных последовательностей импульсов на выходах основного и резервного каналов выделяют по NZ-разрядных сегментов, где N ≥ 10, Z ≥ 20 - число импульсов в каждом сегменте. Определяют число Sj единичных символов в каждом j-м Z-разрядном сегменте, где j = 1,2,...N и запоминают его. Вычисляют общую сумму Sn единичных символов в NZ-разрядных сегментах. Делят ее на N, m = SN/N, а затем на произведение N • Z, p = SN/N • Z. Из каждого ранее запомненного числа Sj единичных импульсов вычитают m. Полученные разности суммируют, предварительно умножив каждую саму на себя, а полученную сумму делят на

По результатам вычислений определяют параметры усечения Y и K основного и резервного каналов. Перечисленные действия повторяют для последующих NZ-разрядных сегментов из обработанных информационных последовательностей импульсов на выходах основного и резервного каналов.

Для формирования сигналов, соответствующих вычисленным параметрам усечения, полученные значения квантуют и затем формируют соответствующие им двоичные числа.

Сравнивают сформированные сигналы усечения, соответствующие вычисленным параметрам усечения путем их компарирования.

Сравнивают сформированные тестовые сигналы усечения, соответствующие вычисленным тестовым параметрам усечения путем их компарирования.

При такой новой совокупности существенных признаков, повышается вероятность определения состояния резервируемых устройств за счет выявления как отказов, так и сбоев различной кратности. Это достигается путем вычисления параметров усечения информационных последовательностей импульсов, их сравнения между собой и определения состояния резервируемых устройств.

В заявленном устройстве поставленная цель достигается тем, что в известной дублированной системе с задержкой, содержащей два резервируемых дискретных устройств, выходы которых подключены к входам соответственно первого и второго регистров сдвига, вход синхронизации системы подключен к вторым входам первого и второго регистров сдвига, выходы которых подключены к информационным входам соответственно первого и второго электронных ключей, выходы которых соединены соответственно с первым и вторым входами элемента ИЛИ выход которого является информационным выходом, дополнительно введены третий электронный ключ, первый вход которого является информационным входом устройства, а второй подключен к выходу генератора. Выход третьего электронного ключа подключен к входам резервируемых дискретных устройств. Блок анализа, первый и второй информационные входы которого подключены к выходам соответственно первого и второго резервируемых дискретных устройств, а его информационный выход подключен к первому информационному входу блока памяти. Второй и третий информационные входы блока памяти подключены к первому и второму информационным выходам блока определения параметров. Вход логический "1" блока определения параметров подключен к выходу логической "1" блока управления. Информационный вход блока определения параметров подключен к первому информационному выходу блока памяти. Выходная информационная шина блока памяти подключена к входным информационным шинам блока определения отказов, блока определения сбоев и блока сравнения. Управляющий выход блока сравнения подключен к третьему входу блока управления, а его управляющий вход к пятому выходу блока управления. Шестой выход блока управления подключен к управляющему входу блока определения сбоев. Первый и второй управляющие выходы блока определения сбоев подключены соответственно к четвертому и пятому входам блока управления. Первый и второй входы блока управления подключены соответственно к второму и первому управляющим выходам блока определения отказов. Первый, третий и седьмой выходы блока управления подключены к управляющим входам соответственно первого, второго и третьего электронных ключей. Второй и четвертый выходы блока управления подключены соответственно к первому и второму входам блока индикации.

Блок анализа состоит из первого, второго счетчиков единичных импульсов и электронного ключа. Входы счетчиков единичных импульсов являются соответственно первым и вторым информационными входами блока анализа. Первый и второй входы электронного ключа подключены к выходам соответственно первого и второго счетчиков единичных импульсов. Выход электронного ключа является информационным выходом блока анализа.

Блок определения параметров состоит из регистра сдвига м первого сумматора первые входы которых соединены и являются информационным входом блока. Выход регистра сдвига подключен к первому входу первого вычитателя. Выход первого вычитателя подключен к первому и второму входам умножителя. Выход умножителя подключен к первому входу второго сумматора. Второй вход второго сумматора подключен к его выходу и соединен с входом третьего делителя с постоянным коэффициентом деления. Выход третьего делителя с постоянным коэффициентом деления подключен к первым входам первого и второго делителя. Выход первого делителя подключен к первому входу третьего сумматора. Выход третьего сумматора подключен к входу четвертого делителя с постоянным коэффициентом деления. Второй вход первого сумматора подключен к его выходу и соединен с входом первого делителя с постоянным коэффициентом деления. Выход первого делителя с постоянным коэффициентом деления подключен к входу второго делителя с постоянным коэффициентом деления, к вторым входам первого вычитателя, третьего сумматора и к первому входу второго вычитателя. Выход второго делителя с постоянным коэффициентом деления подключен к второму входу третьего вычитателя и к второму входу первого делителя. Выход третьего вычитателя подключен к второму входу второго делителя. Выход второго делителя подключен к второму входу второго вычитателя. Выходы второго вычитателя и четвертого делителя с постоянным коэффициентом деления являются соответственно первым и вторым информационными выходами блока. Кроме того, первый вход третьего вычитателя является входом логический "1" блока определения параметров.

Блок определения отказов состоит из первого и второго L-входовых элементов ИЛИ-НЕ, первого и второго L-входовых элементов И, где L ≥ 2i, i ∈ 1,2,.... Выходы первых элементов ИЛИ-НЕ и И подключены соответственно к первому и второму входам первого элемента ИЛИ. Выходы вторых элементов ИЛИ-НЕ и И подключены соответственно к первому и второму входам второго элемента ИЛИ. Выходы первого и второго элементов ИЛИ являются соответственно первым и вторым управляющими выходами блока. Причем L-входы первых элементов И, ИЛИ-НЕ и вторых элементов И, ИЛИ-НЕ являются входной информационной шиной блока.

Блок определения сбоев состоит из первого, второго, третьего и четвертого цифровых компараторов, каждый из которых снабжен двумя группами входов по L входов в каждой группе. Вторая группа L входов второго цифрового компаратора соединена с соответствующей второй группой L входов первого цифрового компаратора. Вторая группа L входов третьего цифрового компаратора соединена с соответствующей второй группой L входов четвертого цифрового компаратора. Выходы первого и третьего цифровых компараторов подключены соответственно к первому и второму входам первого элемента И-НЕ. Выходы второго и четвертого цифровых компараторов подключены соответственно к первому и второму входам второго элемента И-НЕ. Выходы первого и второго элемента И-НЕ подключены к первым входам соответственно первого и второго элементов И. Вторые входы первого и второго элементов И соединены и являются управляющим входом блока. Выходы первого и второго элементов И являются соответственно вторым и первым управляющими выходами блока определения сбоев. Причем первые группы L входов первого, второго, третьего, четвертого цифровых компараторов и вторые группы L входом второго и третьего цифровых компараторов являются входной информационной шиной блока.

Блок сравнения состоит из первого и второго цифровых компараторов, каждый из которых снабжен двумя группами входов по L входов в каждой группе. Выходы первого и второго цифровых компараторов подключены соответственно к первому и второму входам элемента И-НЕ. Выход элемента И-НЕ подключен к первому входу элемента И. Вторым входом и выходом элемента И являются соответственно управляющий вход и управляющий выход блока. Причем первые и вторые группы L входов первого и второго цифровых компараторов являются входной информационной шиной блока.

Блок управления состоит из первого и второго JK-триггеров, второй и третий входы которых соединены и являются соответственно четвертым и пятым входами блока управления. Первый, инверсный, вход первого JK-триггера соединен с первым, инверсным, входов второго JK-триггера и подключен к второму выходу блока установки являющегося выходом логической "1" блока управления. Пятый, инверсный, вход первого JK-триггера соединен с пятым, инверсным, входом второго JK-триггера и подключен к первому выходу блока установки. Четвертый вход первого и второго JK-триггеров соединен с корпусом. Первый элемент И-НЕ второй вход которого соединен с вторым входом третьего элемента ИЛИ, вторым входом шестого элемента ИЛИ, первым входом второго элемента ИЛИ-НЕ и подключен к выходу первого JK-триггера. Первый вход первого элемента И-НЕ соединен с вторым входом первого и второго элементов И, первым входом второго элемента И-НЕ, первым входом третьего и четвертого элементов И и является третьим входом блока управления. Выход первого элемента И-НЕ подключен к первому входу первого элемента ИЛИ. Выход первого элемента ИЛИ подключен к первому входу первого элемента И. Выход первого элемента И подключен к второму входу второго элемента ИЛИ. Четвертый элемент ИЛИ, второй вход которого соединен с вторым входом первого элемента ИЛИ, вторым входом второго элемента ИЛИ-НЕ, вторым входом второго элемента И-НЕ и подключен к выходу второго JK-триггера. Первый вход четвертого элемента ИЛИ соединен с первым входом второго элемента ИЛИ, первым входом первого элемента ИЛИ-НЕ и является вторым входом блока. Пятый элемент ИЛИ первый вход которого соединен с первым входом шестого элемента ИЛИ, вторым входом первого элемента ИЛИ-НЕ и является первым входом блока управления. Второй вход пятого элемента ИЛИ подключен к выходу второго элемента И. Первый вход второго элемента И подключен к выходу третьего элемента ИЛИ. Первый вход третьего элемента ИЛИ подключен к выходу второго элемента И-НЕ. Выход второго элемента ИЛИ-НЕ подключен к второму входу четвертого элемента И. Выход четвертого элемента И подключен к второму входу третьего элемента И и является седьмым выходом блока управления. Выходы второго, четвертого, пятого и шестого элементов ИЛИ, первого элемента ИЛИ-НЕ, третьего элемента И являются соответственно первым, вторым, третьим, четвертым, пятым и шестым выходами блока управления.

Благодаря новой совокупности существенных признаков, за счет введения новых элементов и связей между ними, повышается вероятность определения состояния резервируемых устройств. Новые элементы позволяют определять параметры усечения, сравнивать их между собой, а также с заданными пороговыми и эталонными значениями. Результаты сравнения позволяют выявлять не только отказы, но и сбои в работе резервируемых устройств, что дает возможность произвести реконфигурацию резервируемой системы и исключить прохождение искаженной информационной последовательности импульсов в канал связи.

Проведенный заявителем анализ уровня техники позволил установить, что аналоги, характеризующиеся совокупностями признаков, тождественным всем признакам заявленных способа и устройства диагностики состояния устройств цифровых систем передачи, отсутствуют. Следовательно, каждое из заявленных изобретений соответствует условно патентоспособности "Новизна".

Результаты поиска известных решений в данной и смежной областях техники с целью выявления признаков, совпадающих с отличительными от прототипов признаками каждого заявленного изобретения, показали, что они не следуют явным образом из уровня техники. Из определенного заявителем уровня техники не выявлена известность влияния предусматриваемых существенными признаками каждого из заявленных изобретений на достижение указанного технического результата. Следовательно, каждое из заявленных изобретений соответствует условию патентоспособности "Изобретательский уровень".

Заявленные объекты изобретения поясняются чертежами, на которых показаны:

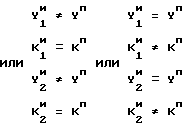

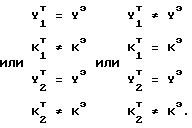

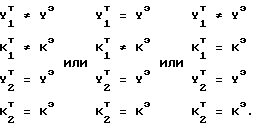

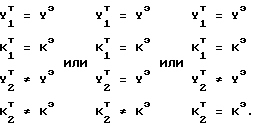

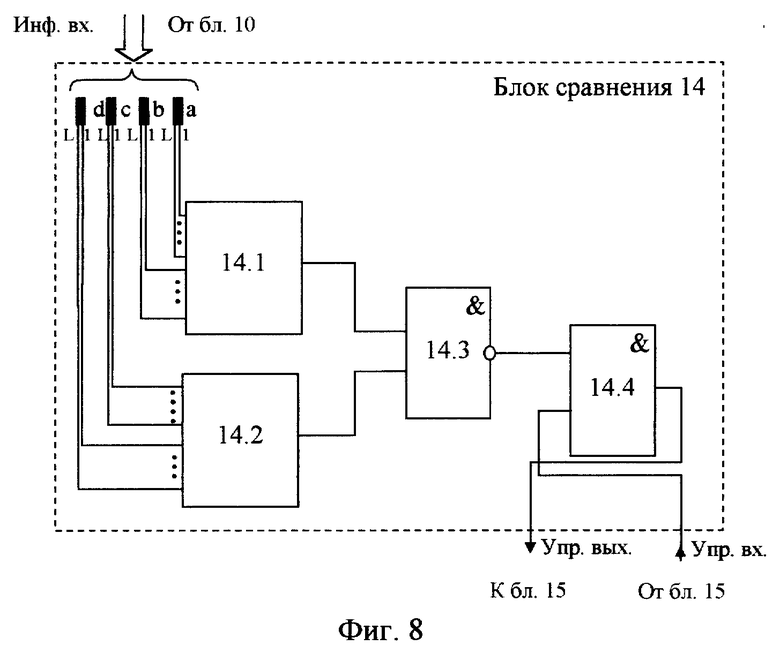

на фиг. 1 - структура информационной последовательности импульсов на выходах резервируемых устройств;

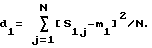

на фиг. 2 - структурная схема устройства дублированной системы с задержкой;

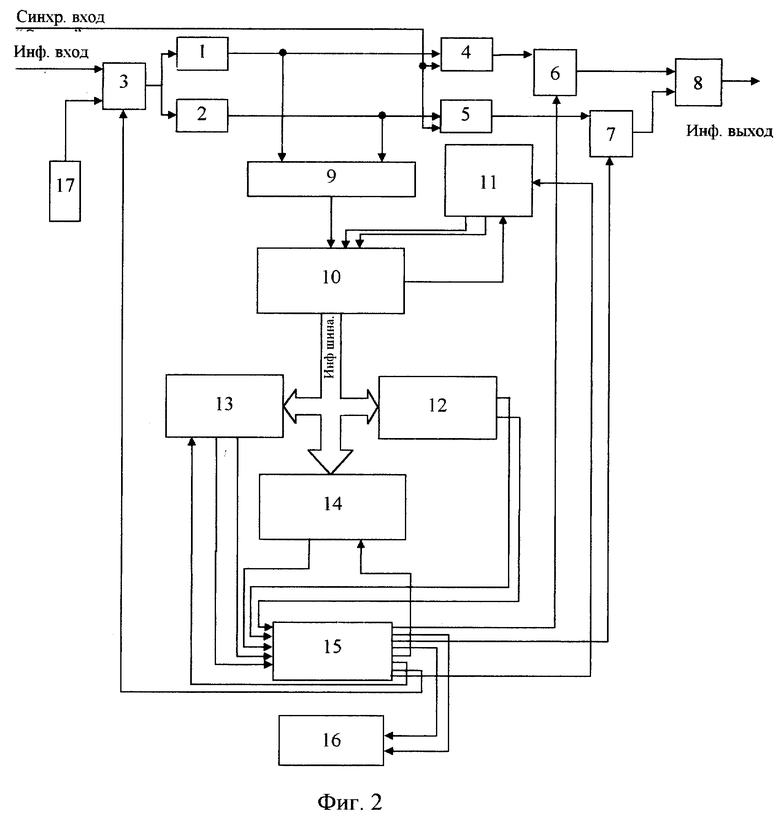

на фиг. 3 - структурная схема информационной шины;

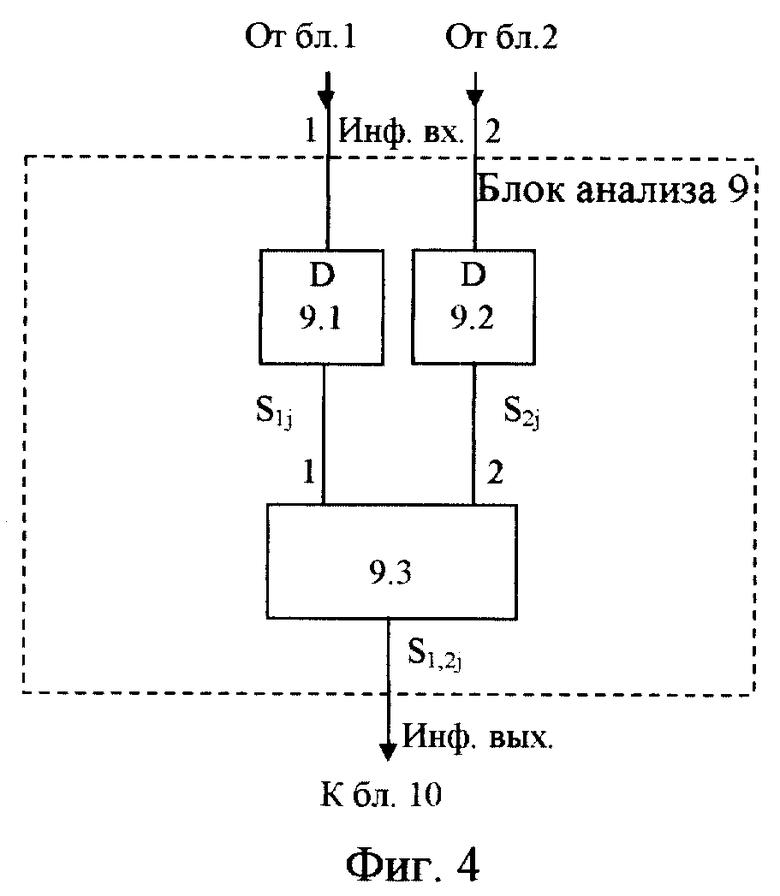

на фиг. 4 - структурная схема блока анализа;

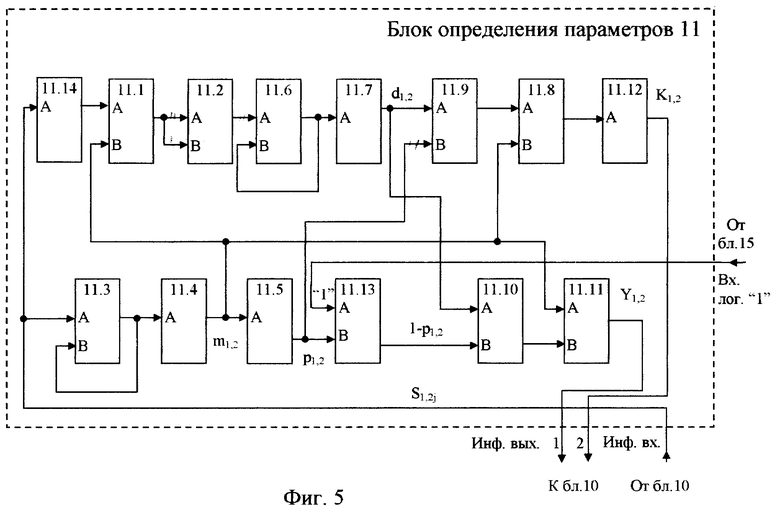

на фиг. 5 - структурная схема блока определения параметров;

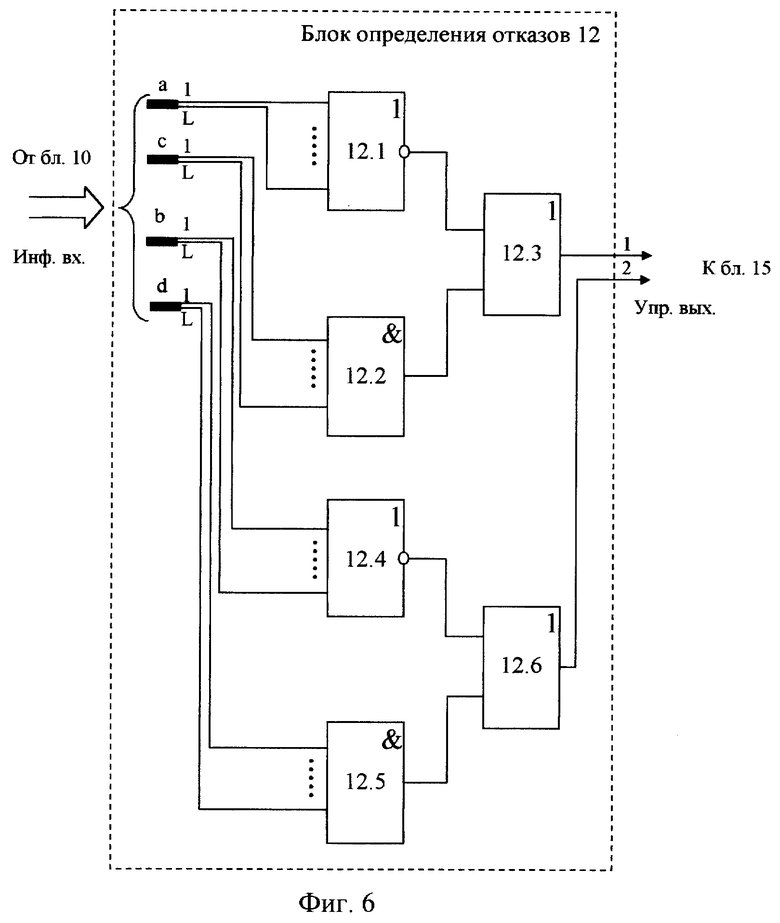

на фиг. 6 - структурная схема блока определения отказов;

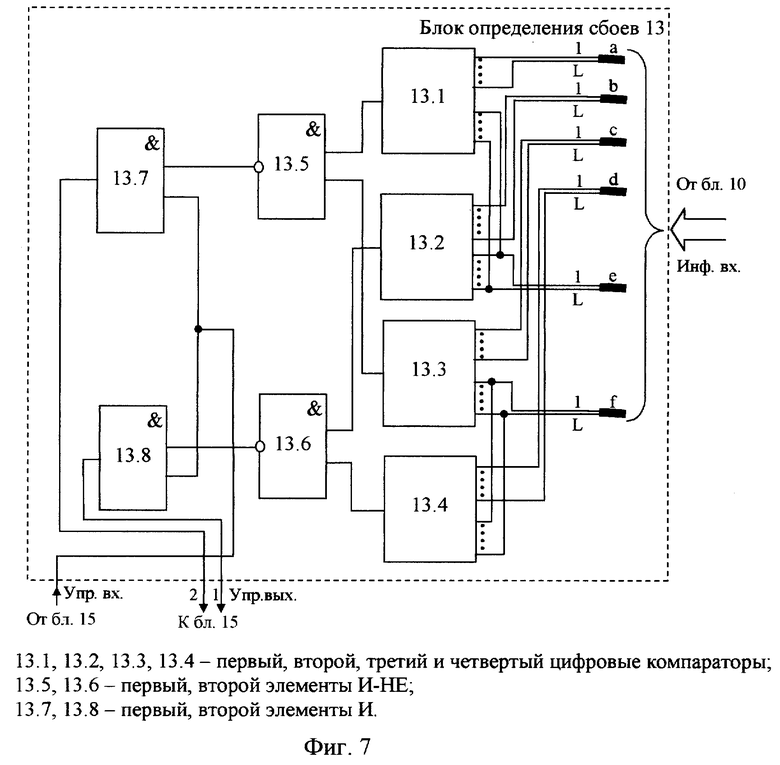

на фиг. 7 - структурная схема блока определения сбоев;

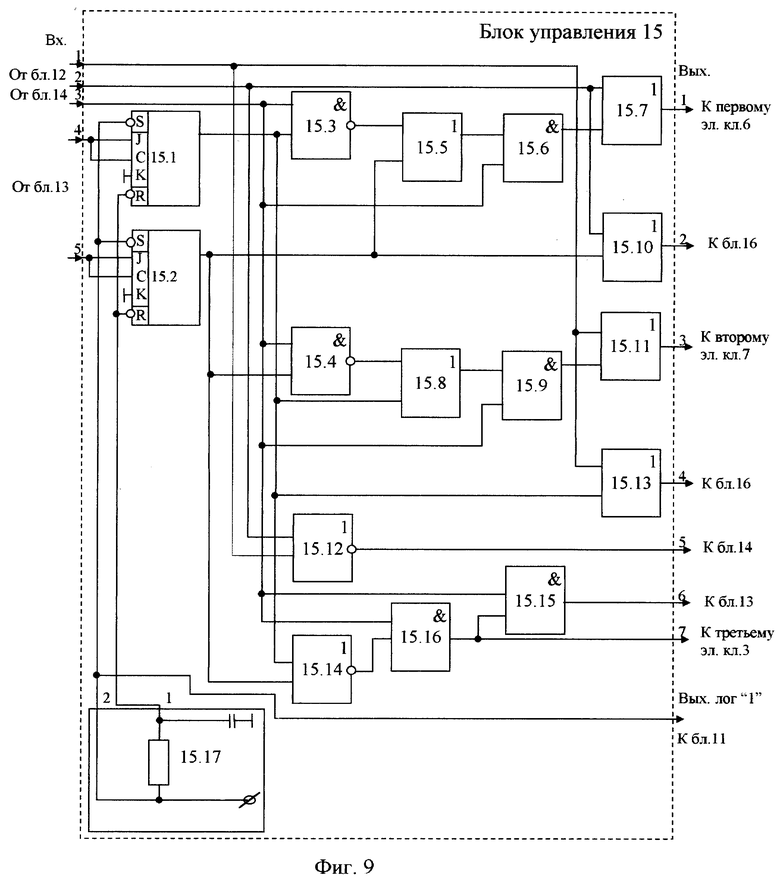

на фиг. 8 - структурная схема блока сравнения;

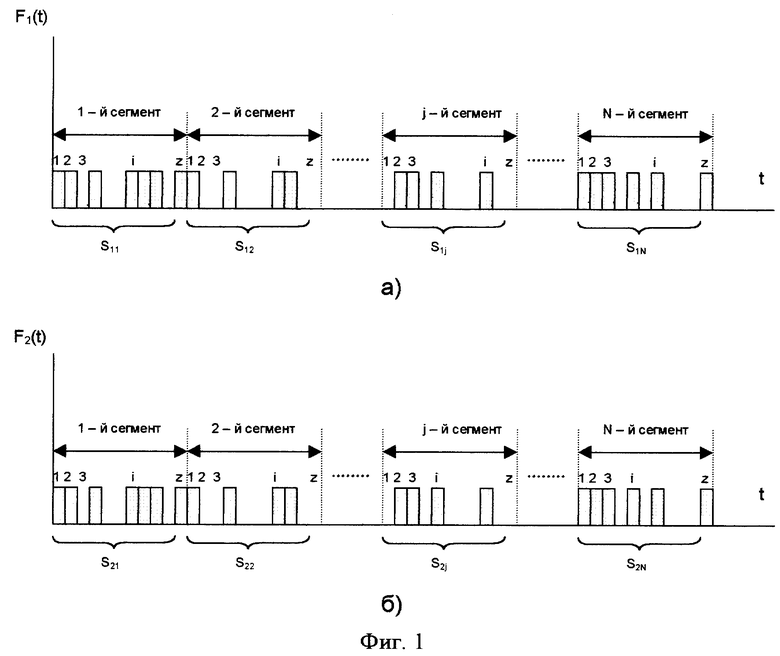

на фиг. 9 - структурная схема блока управления.

Возможность реализации заявленного способа заключается в следующем.

Известно, что для формирования команд с высокой точностью принятия решения в системах управления используют различные методы резервирования, в том числе дублированные системы с задержкой, правильное выполнение функций которых возможно лишь при выявлении не только отказов, но и сбоев в резервируемых элементах. С этой целью, после обработки сигналов в резервируемых устройствах по установленной функции (например, в дублированных сигнальных процессорах), оценивают правильность обработанных информационных последовательностей импульсов на выходах резервируемых устройств. Затем производят параметрическую оценку наличия отказов или сбоев в резервируемых устройствах. Если в одном из резервируемых устройств произошел отказ или сбой, то его выход блокируют. Для оценки правильности обработанных информационных последовательностей импульсов, необходимо иметь интервал времени, в течение которого выполняют этот анализ. Задача различения причин нарушения правильности обработки информационной последовательности импульсов фактически сводится к точному определению причин этих нарушений, т.е. вызваны они отказом или сбоем в резервируемых устройствах.

Определение причины нарушения работы резервируемых устройств может быть достигнуто путем вычисления и оценки параметров K и Y усеченного биноминального распределения, характеризующими закон вероятности появления количества единичных сигналов при повторе определенных комбинаций единичных и нулевых сигналов во всех реализациях последовательности длиной Z:

где m - математическое ожидание числа единичных символов в последовательности длиной Z; d - дисперсия числа единичных символов в последовательности длиной Z; p - вероятность появления единичного символа в каждой временной позиции последовательности длинной Z.

Данные параметры рассчитывают по NZ-разрядным сегментам информационных последовательностей импульсов, обработанных в резервируемых каналах. Параметры усечения являются функциями, зависящими от первого начального и второго центрального моментов усеченного биноминального распределения. Таким образом, в основу точного определения причин нарушения работы резервируемых каналов, положен расчет параметров усечения и последующее их сравнение с заданными пороговыми и эталонными значениями. При этом заданные пороговые значения параметров усечения Kп и Yп представляют собой NZ-разрядную последовательность, которая состоит из нулевых символов, т.е. Kп = 0 или NZ-разрядную последовательность, которая состоит из единичных символов, т.е. Yп = Z. Эталонные значения параметров усечения Kэ и Yэ определяют путем обработки в заведомо исправных резервируемых каналах тестовой последовательности импульсов. В качестве тестовой последовательности импульсов может быть использована псевдослучайная последовательность сгенерированная генератором, построенным на рекуррентной линии задержки (описан, например, в кн. Бобнев И. П. Генерирование случайных сигналов. Изд. 2-е перераб. и доп. - М.: Энергия, 1971, 240 с.). Причем длительность псевдослучайной последовательности должна быть равна N•Z, т.е. соответствовать длительности информационной последовательности импульсов для оценки параметров K и Y.

Таким образом, в заявленном способе после приема информационной последовательности импульсов в основном и резервном каналах одновременно происходит обработка этих последовательностей по установленной функции, а на выходах эти последовательности принимают соответственно значения F1 и(t) и F2 и(t). Затем обработанные последовательности задерживают на время tз, определяемое временем, необходимым для оценки состояния каналов и принятия решения на реконфигурацию дублированной системы. Величина tз = N•Z• τ, где N - число сегментов в обработанной информационной последовательности импульсов, Z - число единичных и нулевых символов в j-м сегменте, τ - длительность временного интервала передачи одного единичного или нулевого символа.

Обработанные информационные последовательности импульсов дают основание для оценки состояния каждого из каналов, путем вычисления значений параметров усечения K1,2 и, Y1,2 и по формуле (1). Индекс "и" означает, что параметры рассчитаны по информационной последовательности импульсов. Индексы 1,2 означают, что рассчитанные параметры относятся соответственно к основному и резервному каналам. Порядок определения параметров усечения в заявленном способе следующий. Из обработанных информационных последовательностей импульсов F1 и(t) и F2 и(t), на выходах основного и резервного каналов выделяют по NZ-разрядных сегментов (см. фиг. 1). (Далее, с целью упрощения в приводимых параметрах указан только индекс 1). В каждом j-м Z- разрядном сегменте определяют число S1j единичных символов. Затем вычисляют общую сумму S1N единичных символов в NZ-разрядных сегментах и делят их на N, m1=S1N/N, а также на произведение N•Z, p1= S1N/N•Z. После этого из каждого ранее запомненного числа S1j единичных символов вычитают m1 и полученные разности суммируют, предварительно умножив каждую саму на себя. Полученную сумму делят на

Таким образом, получают значения m1, d1, p1 по которым вычисляют (по формуле 1) параметры усечения K1 и, Y1 и. Аналогично рассчитывают K2 и, Y2 и.

Полученные сигналы, соответствующие параметрам усечения, затем квантуют и формируют сигналы в двоичном коде. Причем при квантовании каждого из сигналов определяют его наибольшее значение, при котором Y и произведение K на Z будут целыми числами.

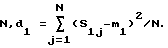

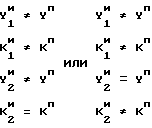

Полученные значения K1 и, Y1 и, K2 и, Y2 и дают основания для первого этапа оценки работоспособности резервируемых каналов. С этой целью их сравнивают с заданными пороговыми значениями Kп, Yп. При этом возможны четыре ситуации:

1. В обоих каналах произошел отказ, т.е.:

2. Отказ основного канала, резервный исправен, т.е.:

3. Отказ резервного канала, основной исправен, т.е.:

4. В обоих каналах отсутствует отказ, т.е.:

Y1 и ≠ Yп

K1 и ≠ Kп

Y2 и ≠ Yп

K2 и ≠ Kп

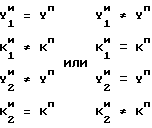

В первом случае формируют сигнал на блокировку обоих каналов и сигнал об отказе системы. В частности, сигнал на блокировку и сигнал об отказе системы может представлять собой логическую "1". Во втором случае вырабатывают сигнал на блокировку основного канала, и выход системы подключают на выход резервного канала. Одновременно формируют сигнал об отказе основного канала. В третьем случае блокируют резервный канал, а выход системы остается подключенным к выходу основного канала. Одновременно формируют сигнал об отказе резервного канала. В четвертом случае для окончательной оценки работоспособности каналов, выявляют, дополнительно, вероятность наличия в них сбоев, путем сравнения параметров усечения, полученных для информационной последовательности импульсов основного и резервного каналов. При этом, если K1 и = K2 и и Y1 и = Y2 и, отказов и сбоев в каналах нет и, следовательно, реконфигурацию системы не производят. Она продолжает работать в том же режиме. Неравенство хотя бы одного из сравнимых параметров свидетельствует о наличии в одном из каналов сбоев. В этом случае формируют сигнал на блокировку обоих каналов. Однако на этом этапе не представляется возможным оценить, в каком из каналов происходят сбои. Для определения канала, в котором происходят сбои, в заявленном способе переходят ко второму этапу оценки состояния системы. С этой целью на входы резервируемых каналов подают тестовую последовательность импульсов и обрабатывают по принятой функции, получая на выходах каналов соответствующие информационные последовательности F1 т (t) и F2 т (t). Затем аналогично, как и для информационных последовательностей импульсов, вычисляют параметры усечения для основного и резервного каналов K1 т, Y1 т, K2 т, Y2 т. Полученные значения параметров усечения, сравнивают с эталонными значениями Kэ, Yэ, которые определяют предварительно путем обработки тестовой последовательности импульсов в заведомо исправной резервируемой системе. В результате сравнения могут быть следующие ситуации.

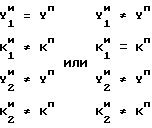

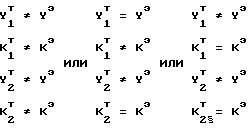

1 Наличие сбоев в обоих каналах, т.е.:

2. Наличие сбоев в основном канале, т.е.:

3. Наличие сбоев в резервном канале, т.е.:

В первом случае формируют сигнал об отказе системы. Во втором и третьем случае формируют сигнал на разблокировку исправного канала, т.е. канала у которого тестовые последовательности равны эталонным. Соответственно второй канал, в котором хотя бы один из параметров не совпадает, оставляют заблокированным и формируют сигнал о его неисправности. При этом подключают выход исправного канала к выходу системы.

Таким образом, благодаря новой совокупности существенных признаков и возможности однозначного определения причины нарушения работоспособности соответствующего канала (выявление отказа или сбоя), обеспечивается высокая вероятность принятия правильного решения на реконфигурацию системы или ее блокировку и, следовательно, исключение передачи в канал информации, обработанной с ошибками.

Дублированная система с задержкой, показанная на фиг. 2, состоит из первого 1 и второго 2 резервируемых устройств, выходы которых подключены к входам соответственно первого 4 и второго 5 регистров сдвига. Синхронизирующий вход устройства подключен к вторым входам первого 4 и второго 5 регистров сдвига. Выходы первого 4 и второго 5 регистров сдвига подключены к информационным входам соответственно первого 6 и второго 7 электронных ключей. Выходы первого 6 и второго 7 электронных ключей соединены соответственно с первым и вторым входами элемента ИЛИ 8. Выход элемента ИЛИ 8 является информационным выходом. Информационным входом устройства дублированной системы с задержкой является первый вход третьего электронного ключа 3. Второй вход третьего электронного ключа 3 подключен к выходу генератора 17. Генератор 17 предназначен для генерирования тестовой псевдослучайной последовательности с известными параметрами Z и N. Выход третьего электронного ключа 3 подключен к входам резервируемых дискретных устройств 1 и 2. Блока анализа 9, первый и второй информационные входы которого подключены к выходам соответственно первого 1 и второго 2 резервируемых дискретных устройств. Информационный выход блока анализа 9 подключен к первому информационному входу блока памяти 10. Блок памяти 10 предназначен для записи полученных значений, хранения их и выдачи требуемых значений. Второй и третий информационные входы блока памяти 10 подключены соответственно к первому и второму информационным выходам блока определения параметров 11. Вход логической "1" блока определения параметров 11 подключен к выходу логической "1" блока управления 15. Информационный вход блока определения параметров 11 подключен к первому информационному выходу блока памяти 10. Выходная информационная шина блока памяти 10 подключена к входным информационным шинам блоков определения отказов 12, определения сбоев 13 и блока сравнения 14. Управляющий выход блока сравнения 14 подключен к третьему входу блока управления 15. Управляющий вход блока сравнения 14 подключен к пятому выходу блока управления 15. Шестой выход блока управления 15 подключен к управляющему входу блока определения сбоев 13. Первый и второй управляющие выходы блока определения сбоев 13 подключены соответственно к четвертому и пятому входам блока управления 15. Первый и второй входы блока управления 15 подключены соответственно к второму и первому управляющим выходам блока определения отказов 12. Первый, третий и седьмой выходы блока управления 15 подключены к управляющим входам соответственно первого 6, второго 7 и третьего 3 электронных ключей. Второй и четвертый выходы блока управления 15 подключены соответственно к первому и второму входам блока индикации 16.

Информационная шина дублированной системы с задержкой, показанная на фиг. 3, содержит шесть групп "a", "b", "c", "d", "e", "f" по L выходов в каждой, где L ≥ 2i, i ∈ 1,2,... Она состоит из нескольких жгутов, количество которых определяется количеством параметров. Каждый жгут имеет несколько физических проводников, число которых определяется значением L.

Блок анализа 9, показанный на фиг. 4, предназначен для выделения информационной последовательности импульсов на выходах резервируемых устройств и состоит из первого 9.1, второго 9.2 счетчиков единичных символов (счетчиков "1") и электронного ключа 9.3. Информационные входы 1 и 2 являются входами блока анализа 9 и подключены соответственно к входам счетчиков "1" 9.1 и 9.2. Выходы счетчиков "1" 9.1 и 9.2 подключены соответственно к 1 и 2 входам электронного ключа 9.3 Выход электронного ключа 9.3 является информационным выходом блока анализа 9.

Блок определения параметров 11, показанный на фиг. 5, предназначен для вычисления параметров усечения из обработанных информационных последовательностей импульсов на выходах первого 1 и второго 2 резервируемых устройств, согласно описанному способу, и состоит из регистра сдвига 11.14, вычитателей 11.1, 11.11, 11.13, сумматоров 11.3, 11.6, 11.8, умножителя 11.2, делителей 11.9, 11.10, делителей с постоянным коэффициентом деления 11.4, 11.5, 11.7, 11.12. Информационный вход является входом блока определения параметров 11 и подключен к первым входам регистра сдвига 11.14 и первого сумматора 11.3. Выход регистра сдвига 11.14 подключен к первому входу первого вычитателя. Выход первого вычитателя 11.1 подключен к первому и второму входам умножителя 11.2. Выход умножителя 11.2 подключен к первому входу второго сумматора 11.6. Второй вход второго сумматора 11.6 подключен к его выходу и входу третьего делителя с постоянным коэффициентом деления 11.7. Выход третьего делителя с постоянным коэффициентом деления 11.7 подключен к первым входам первого 11.9 и второго 11.10 делителей. Выход первого делителя 11.9 подключен к первому входу третьего сумматора 11.8. Выход третьего сумматора 11.8 подключен к входу четвертого делителя с постоянным коэффициентом деления 11.12. Второй вход первого сумматора 11.3 подключен к его выходу и входу первого делителя с постоянным коэффициентом деления 11.4. Выход первого делителя с постоянным коэффициентом деления 11.4 подключен к входу второго делителя с постоянным коэффициентом деления 11.5, к вторым входам первого вычитателя 11.1, третьего сумматора 11.8 и к первому входу второго вычитателя 11.11. Выход второго делителя с постоянным коэффициентом деления 11.5 подключен к вторым входам третьего вычитателя 11.13 и первого делителя 11.9. Выход третьего вычитателя 11.13 подключен к второму входу второго делителя 11.10. Выход второго делителя 11.10 подключен к второму входу второго вычитателя 11.11. Выходы второго вычитателя 11.11 и четвертого делителя с постоянным коэффициентом деления 11.12 являются соответственно первым и вторым информационными выходами блока определения параметров 11. Кроме того, первый вход третьего вычитателя 11.13 является входом логической "1" блока определения параметров 11.

Блок определения отказов 12, показанный на фиг. 6, предназначен для выявления отказов первого 1 и второго 2 резервируемых устройств и состоит из первого 12.1 и второго 12.4 L-входовых элементов ИЛИ-НЕ, первого 12.2 и второго 12.5 L-входовых элементов И, где L≥ 2i, i ∈ 1,2,..., первого 12.3 и второго 12.6 элементов ИЛИ. Шина информационного входа, содержащая четыре группа "a", "b", "c", "d" по L выходов в каждой, является входом блока определения отказов 12. L входов первого элемента ИЛИ-НЕ 12.1 подключены к входу "a" блока определения отказов 12. L входов первого элемента И 12.2 подключены к входу "c" блока определения отказов 12. L входов второго элемента ИЛИ-НЕ 12.4 подключены к входу "b" блока определения отказов 12. L входов второго элемента И 12.5 подключены к входу "d" блока определения отказов 12. Выходы первых элементов ИЛИ-НЕ 12.1 и И 12.2 подключены соответственно к первому и второму входам первого элемента ИЛИ 12.3. Выходы вторых элементов ИЛИ-НЕ 12.4 и 12.5 подключены соответственно в первому и второму входам второго элемента ИЛИ 12.6. Выходы первого 12.3 и второго 12.6 элементов ИЛИ являются соответственно первым и вторым управляющими выходами блока определения отказов 12.

Блок определения сбоев 13, показанный на фиг. 7, предназначен для определения сбоев с резервируемых устройствах, выдачи сигналов блокировки резервируемого устройства, в котором произошел сбой и состоит из первого 13.1, второго 13.2, третьего 13.3, четвертого 13.4 цифровых компараторов, первого 13.5, второго 13.6 элементов И-НЕ, первого 13.7, второго 13.8 элементов И. Шина информационного входа, содержащая шесть групп "a", "b", "c", "d", "e", "f" по L выходов в каждой, является входом блока определения сбоев 13. Каждый из цифровых компараторов 13.1...13.4 снабжен двумя группами входов по L входов в каждой группе. Первые группы L входов цифровых компараторов 13.1... 13.4 подключены соответственно к группам "a", "b", "c", "d" входа блока определения сбоев 13. Вторая группа L входов второго цифрового компаратора 13.2 соединена с соответствующей второй группой L входов первого цифрового компаратора 13.1 и подключена к группе "e" входа блока определения сбоев 13. Вторая группа L входов третьего цифрового компаратора 13.3 соединена с соответствующей второй группой L входов четвертого цифрового компаратора 13.4 и подключена к группе "f" входа блока определения сбоев 13. Выходы первого 13.1 и третьего 13.3 цифровых компараторов подключены соответственно к первому и второму входам первого элемента И-НЕ 13.5. Выходы второго 13.2 и четвертого 13.4 цифровых компараторов подключены соответственно к первому и второму входам второго элемента И-НЕ 13.6. Выходы первого 13.5 и второго 13.6 элементов И-НЕ подключены к первым входам соответственно первого 13.7 и 13.8 элементов И. Вторые входы первого 137 и второго 13.8 элементов И соединены и являются управляющим входом блока определения сбоев 13. Выходы первого 13.7 и второго 13.8 элементов И являются соответственно вторым и первым управляющими выходами блока определения сбоев 13.

Блок сравнения 14, показанный на фиг. 8, предназначен для определения сбоев в резервируемых устройствах и выдачи управляющего сигнала на запуск тестовой последовательности и состоит из первого 14.1, второго 14.2 цифровых компараторов, элемента И-НЕ 14.3 и элемента И 14.4. Шина информационного входа, содержащая четыре группы "a", "b", "c", "d" по L выходов в каждой, является входом блока сравнения 14. Первый 14.1 и второй 14.2 цифровые компараторы, снабжены двумя группами входов по L входов в каждой группе. Первая и вторая группы первого цифрового компаратора 14.1 подключены соответственно к группам "a" и "b" входа блока сравнения 14. Первая и вторая группы второго цифрового компаратора 14.2 подключены соответственно к группам "c" и "d" входа блока сравнения 14. Выходы первого 14.1 и второго 14.2 цифровых компараторов подключены соответственно в первому и второму входам элемента И-НЕ 14.3. Выход элемента И-НЕ 14.3 подключен к первому входу элемента И 14.4. Второй вход и выход элемента И 14.4 являются соответственно управляющим входом и управляющим выходом блока сравнения 14.

Блок управления 15, показанный на фиг. 9, предназначен для выработки управляющих сигналов и состоит из первого 15.1 и второго 15.2 JK-триггеров, первого 15.3, второго 15.4 элементов И-НЕ, первого 15.5, второго 15.7, третьего 15.8, четвертого 15.10, пятого 15.11, шестого 15.13 элементов ИЛИ, первого 15.6, второго 15.9, третьего 15.15, четвертого 15.16 элементов И, первого 15.12, второго 15.14 элементов ИЛИ-НЕ, блока установки 15.17. Второй и третий входы первого JK-триггера 15.1 соединены и являются четвертым входом блока управления 15. Второй и третий входы второго JK-триггера 15.2 соединены и являются пятым входом блока управления 15. Первый, инверсный, вход первого JK-триггера 15.1 соединен с первым, инверсным, входом второго JK-триггера 15.2, подключен к второму выходу блока установки 15.17 и является выходом логической "1! блока управления 15. Пятый, инверсный, вход первого JK-триггера 15.1 соединен с пятым, инверсным, входом второго JK-триггера 15.2 и подключен к первому выходу блока установки 15.17. Четвертые входы первого 15.1 и второго 15.2 JK-триггеров подключены к корпусу. Второй вход первого элемента И-НЕ 15.3 соединен с вторым входом третьего элемента ИЛИ 15.8, вторым входом шестого элемента ИЛИ 15.13, первым входом второго элемента ИЛИ-НЕ 15.14 и подключен к выходу первого JK-триггера 15.1. Первый вход первого элемента И-НЕ 15.3 соединен с вторым входом первого 15.6 и второго 15.9 элементов И, первым входом второго элемента И-НЕ 15.4, первым входом третьего 15.15 и четвертого 15.16 элементов И и является третьим входом блока управления 15. Выход первого элемента И-НЕ 15.3 подключен в к первому входу первого элемента ИЛИ 15.5. Выход первого элемента ИЛИ 15.5 подключен к первому входу первого элемента И 15.6. Выход первого элемента И 15.6 подключен к второму входу второго элемента ИЛИ 15.7. Второй вход четвертого элемента ИЛИ 15.10 соединен с вторым входом первого элемента ИЛИ 15.5, вторым входом второго элемента И-НЕ 15.4, вторым входом второго элемента ИЛИ-НЕ 15.14 и подключен к выходу второго JK-триггера 15.2. Первый вход четвертого элемента ИЛИ 15.10 соединен с первым входом второго элемента ИЛИ 15.7, первым входом первого элемента ИЛИ-НЕ 15.12 и является вторым входом блока управления 15. Первый вход пятого элемента ИЛИ 15.11 соединен с первым входом шестого элемента ИЛИ 15.13, вторым входом первого элемента ИЛИ-НЕ 15.12 и является первым входом блока управления 15. Второй вход пятого элемента или 15.11 подключен к выходу второго элемента И 15.9. Первый вход второго элемента И 15.9 подключен к выходу третьего элемента ИЛИ 15.8. Первый вход третьего элемента ИЛИ 15.8 подключен к выходу второго элемента И-НЕ 15.4. Выход второго элемента ИЛИ-НЕ 15.14 подключен к второму входу четвертого элемента И 15.16. Выход четвертого элемента И 15.16 подключен к второму входу третьего элемента И 15.15 и является седьмым выходом блока управления 15. Выходы второго 15.7, четвертого 15.10, пятого 15.11 и шестого 15.13 элементов ИЛИ, первого элемента ИЛИ-НЕ 15.12, третьего элемента И 15.15 являются соответственно первым, вторым, третьим, четвертым, пятым и шестым выходами блока управления 15.

Блок установки 15.17, показанный на фиг. 9, представляет собой RC - цепочку, в которой первый вывод резистора R соединен с первой обкладкой конденсатора C и является первым выходом блока установки 15.17, при этом вторая обкладка конденсатора C соединена с корпусом. Второй вывод резистора R соединен с шиной питания (блок питания не показан) и является вторым выходом блока установки 15.17. Параметры элементов R и C определяются временем задержки, которое зависит от конкретного типа выбранных интегральных микросхем. Порядок выбора времени задержки известен и описан, например, в справочнике В.Л.Шило. Популярные цифровые микросхемы, с.13-15.

Блок отображения состояния 16, показанный на фиг. 2, предназначен для индикации состояния основного и резервного каналов и состоит из двух световых индикаторов. Первый и второй входы блока отображения состояния 16 подключены к первым контактам световых индикаторов, вторые контакты которых подключены на корпусную шину. Используемые в схеме световые индикаторы, известны и описаны в книге: В.Н.Вениаминов, О.Н.Лебедев, А.И.Мирошниченко. Микросхемы и их применение: Справочное издание; 3-е издание перераб. и доп. - М.: Радио и связь, 1989, с.197, рис. 7.1.

Входящие в общую структуру устройства дублированной системы с задержкой элементы являются типовыми и могут быть технически реализованы в настоящее время при использовании имеющейся элементной базы.

В качестве блока памяти может быть использовано устройство, схема построения которого известна и приведена, например, в книге: В.А.Батушев, В. Н. Вениаминов и др. Микросхемы и их применение: Справочное пособие. - М.: Радио и связь, 1983, с. 175, рис. 5.12.

Генератор 17 может быть реализован на основе рекуррентной линии задержки. Такие схемы известны и описаны, например, в книге: Бобнев М.П. Генерирование случайных сигналов. Изд. 2-е перераб. и доп. - М.: Энергия, 1971, с. 175, и могут быть реализованы, например, на регистрах сдвига К155ИР13 (см. В.Л.Шило. Популярные цифровые микросхемы. - М.: Радио и связь, 1987, с. 110-112, рис. 1.78).

Схемы счетчиков известны и приведены, например, в книге: А.А.Сикарев, О. Н. Лебедев. Микроэлектронные устройства формирования и обработки сложных сигналов. - М.: Радио и связь, 1983, с. 128, рис. 518, и могут быть реализованы, например, на микросхеме К176ИЕ2 (см. В.Л.Шило. Популярные цифровые микросхемы. - М.: Радио и связь, 1987, с. 235-236, рис. 2.36,a).

Используемые в заявленном устройстве элементы И-НЕ, ИЛИ, ИЛИ-НЕ JK-триггеры, регистры сдвига известны и описаны, например, в справочнике: В.Л. Шило. Популярные цифровые микросхемы: элементы И-НЕ - с. 43, рис. 1.24,в, и могут быть выполнены на микросхемах К155ЛАЗ; элементы ИЛИ - с. 48, рис. 1.27, з, и могут быть выполнены на микросхемах К155ЛЛ1; элемент ИЛ-НЕ - С. 48, рис. 1.27,б, и может быть выполнен на микросхемах К155ЛЕ1; JK-триггеры - с. 83, рис. 1.60,в, и могут быть выполнены на микросхемах К155ТВ9; регистры сдвига - с. 106, рис. 1.75, и могут быть выполнены на микросхемах К155ИР1. Схемы элементов И известны и описаны, например, в книге: Микросхемы и их применение /Батушев В.А., Вениаминов В.Н., Ковалев В.Г. и др. - М.: Энергия, 1978, c. 142-147.

Схемы сумматоров, вычитателей описаны, например, в книге: Токхейм Р. Основы цифровой электроники: Пер. с анг. -М.: Мир, 1988, с. 231-232, рис. 9.18, и могут быть реализованы, например, на микросхеме К155ИП4 (см. В.А. Батушев, В. Н.Вениаминов и др. Микросхемы и их применение: Справочное пособие. - М.: Радио и связь, 1983, с. 129 -130).

Схема умножителя известна, приведена, например, в книге: Токхейм Р. Основы цифровой электроники: Пер. с англ. - М.: Мир, 1988, с. 236-240 рис. 9.26, и может быть реализована, например, на микросхеме К155ИП4 (см. В.А.Батушев, В.Н. Вениаминов и др. Микросхемы и их применение: Справочное пособие. - М.: Радио и связь, 1983, с.129 -130).

Схема делителя, делителя с постоянным коэффициентом деления известна, описана, например, в книге: В.С.Гутников, В.В.Лопатин и др. Электронные устройства информационно-измерительной техники: Учебное пособие. - Л.: ЛПИ им. Калинина, 1980, с. 44-46, 4-50, рис. 21,а, 24, и может быть реализованы, например, на микросхемах К155ИК8, К155ИЕ2 (см. В.Л.Шило. Популярные цифровые микросхемы. - М.: Радио и связь, 1987, с. 94-97, рис. 1.69).

Схема цифрового компаратора известна, приведена, например, в книге: В.Н. Вениаминов, О. Н. Лебедев, А. И. Мирошниченко. Микросхемы и их применение: Справочное издание; 3-е издание перераб. и доп. - М.: Радио и связь, 1986, с. 113-114, рис. 4.12,а.

Схема электронного ключа известна и приведена, например, в книге: В.Л. Шило. Популярные микросхемы КМОП. Справочник. - М.: Ягуар, 1993, с. 22.

Заявленное устройство дублированной системы с задержкой работает следующим образом.

В исходном состоянии при включении питания первый 15.1 и второй 15.2 JK-триггеры блока управления 15 устанавливаются в "0" состояние по выходу, благодаря подаче на инверсные входы S уровня сигнала соответствующего уровню логической "1", а на инверсные входы R уровня сигнала соответствующего уровню логического "0", так как конденсатор блока установки 15.17 разряжен. По мере заряда конденсатора через резистор блока установки 15.17, JK-триггеры 15.1, 15.2 подготавливаются к работе по управляющим объединенным входам J и C (на установочных инверсных входах S=R=1). С выхода логической "1" блока управления 15 сигнал, соответствующий уровню логической "1", поступает на первый вход третьего вычитателя 11.13 блока определения параметров 11. Причем в блок памяти 10, в соответствующие ячейки памяти, записаны при вводе в эксплуатацию параметры усечения Kэ, Yэ, которые получают путем обработки в заведомо исправных резервируемых устройствах тестовой последовательности импульсов.

Информационная последовательность импульсов через электронный ключ 3 поступает на выходы резервируемых устройств 1 и 2. Преобразованные в резервируемых устройствах 1, 2 информационные последовательности импульсов F1 и(t) и F2 и(t) записываются в регистры сдвига 4, 5 по заднему фронту импульсов с синхронизирующего входа. Одновременно осуществляется состояния резервируемых устройств 1 и 2 и принятие решения на реконфигурацию дублированной системы в случае отказа или сбоя в их работе. Время оценки и принятия решения не превышает время задержки информационной последовательности импульсов в регистрах сдвига 4, 5. Оценка состояния производится следующим образом. Информационные последовательности импульсов F1 и(t) и F2 и(t) с выходов резервируемых устройств 1, 2 подаются на соответствующие входы первого 9.1 и второго 9.2 счетчиков единичных символов (счетчиков "1") блока анализа 9, показанного на фиг. 4. В счетчиках "1" 9.1, 9.2 начинается подсчет числа единичных символов ("1") S1j и S2j в каждом j-м Z-разрядном сегменте, где 1,2 - первое и второе резервируемые устройства. После поступления каждого Z-го символа сегмента производится считывание значений счетчиков "1" 9.1, 9.2 и их обнуление.

Единичные символы S1j и S2j, представленные в двоичном коде, с выходов счетчиков "1" 9.1 и 9.2 поступают на первый и второй входы электронного ключа 9.3 и поочередно коммутируются на выход электронного ключа 9.3.

С выхода электронного ключа 9.3 S1j и S2j поступают на первый информационный вход блока памяти 10, показанного на фиг. 2, где производится запись их значений в соответствующие ячейки памяти блока памяти 10 в следующей последовательности: S11, S21, S12, S22,...S1j, S2j,..., S1N, S2N.

После занесения в блок памяти 10 всех чисел S1j и S2j выделенных N Z - разрядных сегментов, в блоке определения параметров 11 вначале производится вычисление значений математического ожидания m1, дисперсии d2 числа "1" в Z-разрядном сегменте и вероятности появления "1" p1 в каждой позиции Z-разрядных сегментов и по результатам вычислений m1, d1 и p1 определяют значения параметров усечения K1 и и Y1 и. Затем производится вычисление математического ожидания m2, дисперсии d1 числа "1" в Z-разрядном сегменте и вероятности появления "1" p2 в каждой позиции Z-разрядеых сегментов и по результатам вычислений m2, d2 и p2 определяют значения параметров усечения K2 и Y2 и. Эти вычисления производятся в выделенных N Z-разрядных сегментах информационной последовательности импульсов резервируемых устройств 1, 2.

С выхода блока пяти 10 производится последовательное считывание значений S1j и S2j. Эти значения подаются на первый вход первого сумматора 11.3 и вход регистра сдвига 11.14 блока определения параметров 11, показанного на фиг. 5. В первом сумматоре 11.3 производится суммирование всех j-х значений S1j выделенных N Z-разрядных сегментов, путем сложения каждого j-го значения S1j с суммой предыдущих, поступающих с выхода первого сумматора 11.3 на его второй вход:

При подаче на первый вход первого сумматора 11.3 последнего значения S1j и получения на его выходе суммарного значения единичных символов S1N в выделенных N Z-разрядных сегментах, это значение считывают, в первый сумматор 11.3 обнуляют.

Сигнал с выхода сумматора 11.3 подается на вход делителя с постоянным коэффициентом деления 11.4. В делителе выполняется операция деления на число N, то есть производится вычисление:

Значение m1 с выхода делителя с постоянным коэффициентом деления 11.4 подается на первый вход делителя с постоянным коэффициентом деления 11.5, второй вход первого вычитателя 11.1, второй вход третьего сумматора 11.8 и первый вход второго вычитателя 11.11. В делителе с постоянным коэффициентом деления 11.5 выполняется операция деления на число Z, то есть производится вычисление вероятности появления "1" p1 в каждой позиции Z-разрядных сегментов:

после чего, производится подача ее на второй вход третьего вычитателя 11.13 и второй вход первого делителя 11.9. В третьем вычитателе 11.13, на первый вход которого подается число "один" представленное в двоичном коде, производится вычисление: 1 - p1.

Значение 1 - p1 считывается и подается на второй вход второго делителя.

После вычисления значения m1 и подачи его на второй вход первого вычитателя 11.1, производится вычисление значения дисперсии d1. С выхода регистра сдвига 11.14, время задержки которого определяется временем необходимым для вычисления значения m1, производится последовательное считывание j-х значений S1j выделенных N Z-разрядных сегментов, и подача этих значений на первый вход первого вычитателя 11.1. В вычитателе 11.1 производится вычисление: S1j - m1.

Сигнал с выхода первого вычитателя 11.1 подается на первый и второй входы умножителя 11.2, в котором производится вычисление: [S1j - m1]2, результат которого подается на первый вход второго сумматора 11.6.

После этого производится обнуление первого вычитателя 11.1 и умножителя 11.2.

Во втором сумматоре 11.6 производится сложение [S1j - m1]2 N раз, путем добавления каждого значения [S1j - m1]2 к сумме предыдущих, поступающих с выхода второго сумматора 11.6 на его второй вход. При подаче на первый вход второго сумматора 11.6 N-го значения [S1j - m1]2 и вычисления, на его выходе суммарного значения  [S1j - m1]2 производится считывание этого значения на вход третьего делителя с постоянным коэффициентом деления 11.7 и обнуление второго сумматора 11.6.

[S1j - m1]2 производится считывание этого значения на вход третьего делителя с постоянным коэффициентом деления 11.7 и обнуление второго сумматора 11.6.

В третьем делителе с постоянным коэффициентом деления 11.7 производится вычисление:

После вычисления d1 производится считывание значения d1.

Значение d1 подается на первые входы первого 11.9 и второго 11.10 делителей. На второй вход делителя 11.9 подано значение p1. В делителе 11.9 производится вычисление: d1/p1, результат которого подается на первый вход третьего сумматора 11.8.

В третьем сумматоре 11.8, на второй вход которого подано значение m1, производится вычисление: m1+d1/p1.

Результат суммирования подается на вход четвертого делителя с постоянным коэффициентом деления 11.12, в котором производится вычисление и

квантование параметра усечения K1 и: K1 и = (m1 + d1/p1/Z. После вычисления и квантования производится считывание значение K1 и и подача этого значения на третий информационный вход блока памяти 10, в котором производится запись значений K1 и в соответствующие ячейки памяти.

Параллельно с вычислением значения K1 и производится вычисление значение Y1 и. На второй вход делителя 11.10 подается значение 1-p1, а на его первый вход подано значение d1. В делителе 11.10 производится вычисление: d1/(1-p1), результат которого подается на второй вход второго вычитателя 11.1. Во втором вычитателе 11.11, на первый вход которого подано значение m1 производится вычисление и квантование параметра усечения Y1 и: Y1 и = m1 - d1/(1 - p1). После вычисления и квантовая производится считывание значения Y1 и и подача этого значения на второй информационный вход блока памяти 10, в котором производится запись значений Y1 и в соответствующие ячейки памяти. После вычисления значений m1, p1 и d1 и параметров усечения K1 и и Y1 и производится вычисление значений m2, p2 и d2 и параметров усечения K2 и и Y2 и. Вычисление значений m2, p2, d2 и параметров усечения K2 и и Y2 и производится аналогично вычислениям значений m1, p1, d1 и параметров усечения K1 и и Y1 и.

Вычисления в блоке определения параметров 11, производятся непрерывно для каждой N Z-разрядной последовательности сегментов.

На втором этапе, по полученным значениям K1 и, Y1 и, K2 и, Y2 и, производится определение состояния резервируемых устройств 1, 2 и принятые решения на реконфигурацию дублированной системы.

В нормальном режиме работы, когда оба резервируемых устройства 1, 2 исправны (K1 и ≠ K2 и Kп и Y1 = Y2 ≠ Yп) параметры усечения K1 и, Y1 и, K2 и, Y2 и с блока памяти 10 в параллельном двоичном коде подаются соответственно на первый L-входовой элемент ИЛИ-НЕ 12.1, первый L-входовый элемент И 12.2, второй L-входовый элемент ИЛИ-НЕ 12.4 и второй L-входовой элемент И 12.5 блока определения отказов 12. На 1 и 2 управляющих выходах блока определения отказов 12 формируются сигналы с уровнем логического "0". Одновременно параметры усечения K1 и, Y1 и, K2 и, Y2 и в параллельном двоичном коде подаются на первые и вторые группы L-входов цифровых компараторов 14.1, 14.2, блока сравнения 14, и первые группы L-входов цифровых компараторов 13.1...13.4 блока определения сбоев 13. На управляющем выходе блока сравнения 14 и на 1, 2 управляющих выходах блока определения сбоев 13 формируется сигнал с уровнем логического "0". С управляющих выходов блоков определения отказов 12, сравнения 14 и определения сбоев 13 сигналы с уровнем логического "0" подаются на входы 1...5 блока управления 15. Сигналы с уровнем логического "0" с управляющих выходов блока определения сбоев обеспечивают поддержание JK-триггеров 15.1, 15.2 в нулевом состоянии. В результате логических преобразований на выходах 1...4, 6, 7 блока управления 15 формируются сигналы логического "0", а на выходе 5 формируется сигнал логической "1". Сигналы с уровнем логического "0" с выходов 1 и 3 блока управления 15 подаются на управляющие входы соответственно первого и второго электронных ключей 6, 7, оставляя ключи открытыми. После заполнения регистров сдвига 4, 5 информационная последовательность импульсов на информационный выход будет поступать с выходов регистров сдвига 4, 5 через открытые электронные ключи и элемент ИЛИ 8. Сигнал с уровнем логической "1" с выхода 5 подается на второй вход элемента И 14.4 блока сравнения 14, разрешая прохождение сигналов на его управляющий выход.

В случае отказа резервируемого устройства 1 (K1 и = Kп и (или) Y1 и = Yп, K2 и≠Kп, Y2 и≠Yп) на первые L-входовые элементы ИЛИ-НЕ 12.1, 12.2 блока определения отказов 12 подаются логические "0", при K1 и=Kп или логические "1", при Y1 и=Yп. На выходах ИЛИ-НЕ 12.1 или И 12.2 формируется сигнал логической "1", который через элемент ИЛИ 12.3 подается на первые входы второго 15.7 и четвертого 15.10 элементов ИЛИ и первый вход первого элемента ИЛИ-НЕ 15.12 блока управления 15. С выхода второго элемента ИЛИ 15.7 сигнал логической "1" подается на управляющий вход электронного ключа 6. Электронный ключ 6 закрывается и информационная последовательность импульсов на информационный выход и выхода регистра сдвига 4 не поступает. С выхода четвертого элемента ИЛИ 15.10 сигнал логической "1" подается на первый вход блока индикации 16, сигнализируя о неисправности резервируемого устройства 1. С выхода первого элемента ИЛИ-НЕ 15.12 сигнал логического "0" подается на второй вход элемента И 14.4 блока сравнения 14 и запрещает прохождение сигналов на его управляющий выход. При этом на управляющих выходах блока сравнения 13 и блока определения сбоев 14 формируются сигналы логического "0".

В случае отказа резервируемого устройства 2 (K2 и=Kп и (или) Y2 и=Yп, K1 и≠Kп, Y1 и≠Yп на вторые L-входовые элементы ИЛИ-НЕ 12.4, И 12.5 блока определения отказов 12 подаются логические "0", при K2 и=Kп или логические "1", при Y2 и= Yп, На выходах ИЛИ-НЕ 12.4 или 12.5 формируется сигнал логической "1", который через элемент ИЛИ 12.3 подается на первые входы пятого 15.11 и шестого 15.13 элементов ИЛИ и второй вход первого элемента ИЛИ-НЕ 15.12 блока управления 15. С выхода пятого элемента ИЛИ 15.11 сигнал логической "1" подается на управляющий вход электронного ключа 7. Электронный ключ 7 закрывается и информационная последовательность импульсов на информационный выход с выхода регистра сдвига 5 не поступает. С выхода шестого элемента ИЛИ 15.13 сигнал логической "1" подается на второй вход блок индикации 16, сигнализируя о неисправности резервируемого устройства 2. С выхода первого элемента ИЛИ-НЕ 15.12 сигнал логического "0" подается на второй вход элемента И 14.4 блока сравнения 14 и запрещает прохождение сигналов на его управляющий выход. При этом на управляющих выходах блока сравнения 13 и блока определения сбоев 14 формируются сигналы логического "0".

В случае отказа обоих резервируемых устройств 1,2 (K1 и=Kп и (или) Y1 и= Yп, K2 и= Kп и (или) Y2 и=Yп) работа схемы происходит параллельно по аналогии со случаями, описанными для отказа первого 1 и второго 2 резервируемых устройств. В результате электронные ключи 6, 7 отключают информационную последовательность импульсов с выходов первого 4 и второго 5 регистров сдвига от информационного выхода системы. Блок индикации 16 сигнализируется об отказе системы путем подачи на его первый и второй входы сигналов логической "1" соответственно с выходов 4 и 2 блока управления.

В случае в работе резервируемых устройств 1, 2 (K1 и≠K2 и≠Kп и (или) Y1 и≠Y2 и≠Yп) на выходах цифровых компараторов 14.1 при K1 и≠K2 и и(или) 14.2 при Y1 и≠Y2 и блока сравнения 14 формируются сигналы с уровнем логического "0". В результате логических преобразователей на выходе элемента И 14.4 формируетя сигнал с уровнем логической "1", который подается на выходы первого 15.3 и второго 15.4 элементов И-НЕ, первого 15.6, второго 15.9, третьего 15.15, четвертого 15.16 элементов И блока управления 15. На выходах первого 15.3 и второго 15.4 элементов И-НЕ формируются сигналы логических "1". С выхода первого элемента И-НЕ 15.3 через первые элементы ИЛИ 15.5, И 15.6, второй элемент ИЛИ 15.7 сформированный сигнал логической "1" подается на управляющий вход электронного ключа 6. Одновременно с выхода второго элемента И-НЕ 15.4 через третий элемент ИЛИ 15.8, второй элемент И 15,9, пятый элемент ИЛИ 15.11 сформированный сигнал логической "1" подается на управляющий вход электронного ключа 7. Электронные ключи 6, 7 закрываются, запрещая прохождение задержанной информационной последовательности импульсов с выходов регистров сдвига 4, 5 на информационный выход. На выходе четвертого элемента И 15.16 формируется сигнал логической "1", который подается на управляющий вход третьего электронного ключа 3 и второй вход элемента И 15.15. На выходе элемента И 15.15 формируется сигнал логической "1", который подается на вторые входы первого 13.7 и второго 13.8 элементов И блока определения сбоев 13. Третий электронный ключ 3 своими контактами подключает выход генератора 17. С выхода генератора 17 тестовая последовательность импульсов подается на входы резервируемых устройств 1, 2. Преобразование в резервируемых устройствах 1, 2 тестовые последовательности импульсов F1 т(t) и F2 т(t) подаются на первый и второй информационные входы блока анализа 9. В блоке анализа 9 осуществляется подсчет числа единичных символов ("1") S1jт и S2jт в каждом j-м Z-разрядном сегменте, аналогично подсчету для информационной последовательности импульсов.

После занесения в блок памяти 10 всех чисел S1jт и S2jт, выделенных N Z-разрядных сегментов для тестовой последовательности импульсов, в блоке определения параметров 11 вычисляют значения параметров усечения K1 т, Y1 т, K2 т, Y2 т аналогично вычислениям K1 и, Y1 и, K2 и, Y2 и. Значения параметров усечения K1 т, Y1 т, K2 т, Y2 т записывают в соответствующие ячейки блока памяти 10. Параметры усечения K1 т, Y1 т, K2 т, Y2 т в параллельном двоичном коде подаются на первые группы L-входов цифровых компараторов 13.1...13.4 блока определения сбоев 13. С блока памяти 10 на вторые группы L-входов цифровых компараторов 13.1, 13.2 подается эталонное значение параметра усечения Kэ, на вторые группы L-входов цифровых компараторов 13.3, 13.4 подается эталонное значение параметра усечения Yэ. При сбоях в первом 1 резервируемом устройстве (K1 т≠Kэ и (или) Y1 т≠Yэ) на выходах первого 13.1 и (или) третьего 13.3 цифровые компараторов формируется сигнал логического "0". При подаче на один (оба) входа элемента И-НЕ 13.5 сигнала логического "0" на его выходе формируется сигнал логической "1", который через элемент И 13.7 подается на второй вход триггера 15.2 и по переднему фронту импульса на третьем входе переводит триггер в единичное состояние. С выхода триггера 15.2 сигнал логической "1" подается на вторые входы элементов И-НЕ 15.4, ИЛИ-НЕ 15.14, ИЛИ 15.5 и через элемент ИЛИ 15.10 на первый вход блока индикации 16, сигнализируя о неисправности первого 1 резервируемого устройства. На выходе элемента ИЛИ-НЕ 15.14 формируется сигнал логического "0", который запрещает подачу логической "1" с выхода четвертого 15.16 элемента И на управляющий вход третьего 3 электронного ключа. Третий 3 электронный ключ своими контактами отключает генератор 17 и подключает информационный вход к входам резервируемых устройств 1, 2. На выходе элемента И-НЕ 15.4 формируется сигнал логического "0". В результате на выходе элемента ИЛИ 15.8 появляется сигнал логического "0", который запрещает подачу логической "1" с выхода элемента И 15.9. На выходе элемента И 15.9 формируется сигнал логического "0", который через элемент ИЛИ 15.11 подается на управляющий вход второго 7 электронного ключа. Электронный ключ 7 осуществляет коммутацию информационного выхода на выход второго 2 резервируемого устройства. Выход первого 1 резервируемого устройства остается заблокированным, так как первый 6 электронный ключ остается закрытым сигналом логической "1", который подается на его управляющий вход с выхода элемента ИЛИ 15.7 блока управления 15. При сбоях во втором 2 резервируемом устройстве (K2 т≠Kэ и (или) Y2 т≠Yэ) на выходах второго 13.2 и (или) четвертого 13.4 цифровых компараторов формируется сигнал логического "0". При подаче на один (оба) входа элемента И-НЕ 13.6 сигнала логического "0" на его выходе формируется сигнал логической "1", который через элемент И 13.8 подается на второй вход триггера 15.1 и по переднему фронту импульса на третьем входе переводит триггер в единичное состояние. Сигнал логической "1" подается на вторые входы элементов И-НЕ 15.3, ИЛИ 15.8, первый вход элемента ИЛИ-НЕ 15.14 и через элемент ИЛИ 15.13 на второй вход блока индикации 16, сигнализируя о неисправности второго 2 резервируемого устройства. На выходе элемента ИЛИ-НЕ 15.14 формируется сигнал логического "0", который запрещает подачу логической "1" с выхода четвертого 15.16 элемента И на управляющий вход третьего 3 электронного ключа. Третий 3 электронный ключ своими контактами отключает генератор 17 и подключает информационный вход к входам резервируемых устройств 1, 2. На выходе элемента И-НЕ 15.3 формируется сигнал логического "0". В результате на выходе элемента ИЛИ 15.5 появляется сигнал логического "0", который запрещает подачу логической "1" с выхода элемента И 15.6. На выходе элемента И 15.6 формируется сигнал логического "0", который через элемент ИЛИ 15.7 подается на управляющий вход первого 6 электронного ключа. Электронный ключ 6 осуществляет коммутацию информационного выхода на выход первого 1 резервируемого устройства. Выход второго 2 резервируемого устройства остается заблокированным, так как второй 7 электронный ключ остается закрытым сигналом логической "1", который подается на его управляющий выход с выхода элемента ИЛИ 15.11 блока управления 15.

В случае сбоев в работе обоих резервируемых устройств 1,2 (K1 т≠Kэ и (или) Y1 т≠Yэ K2 т≠Kэ и (или) Y2 т≠Yэ) работа схемы происходит параллельно по аналогии со случаями, описанными для себя в работе первого 1 и второго 2 резервируемых устройств. В результате электронные ключи 6, 7 оставляются закрытыми и информационная последовательность импульсов с выходов первого 4 и второго 5 регистров сдвига не подается на информационный вход системы. Блок индикации 16 сигнализирует об отказе системы путем подачи на его первый и второй входы сигналов логической "1" соответственно с выходов 2, 4 блока управления 15.

Благодаря новой совокупности существенных признаков в заявленной дублированной системе с задержкой, повышается вероятность определения состояния резервируемых устройств. Применение дублированной системы при резервировании управляющих устройств в сложных радиоэлектронных системах, позволяет повысить их устойчивость работы за счет снижения вероятности ошибочных решений при кратных отказах и сбоях.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДУБЛИРОВАННАЯ СИСТЕМА С ДИНАМИЧЕСКОЙ ЗАДЕРЖКОЙ | 1999 |

|

RU2153786C1 |

| ТРЕХЭЛЕМЕНТНОЕ МАЖОРИТАРНОЕ УСТРОЙСТВО РЕЗЕРВИРОВАНИЯ | 2007 |

|

RU2336670C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1999 |

|

RU2149446C1 |

| УСТРОЙСТВО КОНТРОЛЯ ЭНЕРГИИ, ПЕРЕДАВАЕМОЙ ПО ВОЛОКОННО-ОПТИЧЕСКИМ ЛИНИЯМ СВЯЗИ (ВАРИАНТЫ) | 1999 |

|

RU2152133C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА КАНАЛА СВЯЗИ | 2002 |

|

RU2216865C1 |

| УСТРОЙСТВО КОНТРОЛЯ ОШИБОК В ЦИФРОВЫХ СИСТЕМАХ ПЕРЕДАЧИ НА БАЗЕ ТЕХНОЛОГИИ АТМ | 2009 |

|

RU2408985C2 |

| УСТРОЙСТВО КОНТРОЛЯ ОШИБОК В ЦИФРОВЫХ СИСТЕМАХ ПЕРЕДАЧИ НА БАЗЕ ТЕХНОЛОГИИ Ethernet | 2014 |

|

RU2546560C1 |

| ЦИФРОВОЙ РАДИОПЕЛЕНГАТОР | 1999 |

|

RU2149419C1 |

| СПОСОБ И УСТРОЙСТВО СЖАТИЯ КОДИРУЕМОЙ ПОСЛЕДОВАТЕЛЬНОСТИ ИЗ СИМВОЛОВ УПОРЯДОЧЕННОГО m-ИЧНОГО АЛФАВИТА В КОДИРОВАННУЮ ПОСЛЕДОВАТЕЛЬНОСТЬ ДВОИЧНЫХ СИМВОЛОВ | 2000 |

|

RU2168857C1 |

| СПОСОБ И УСТРОЙСТВО СЖАТИЯ КОДИРУЕМОЙ ПОСЛЕДОВАТЕЛЬНОСТИ ИЗ СИМВОЛОВ БЕСКОНЕЧНОГО АЛФАВИТА В КОДИРОВАННУЮ ПОСЛЕДОВАТЕЛЬНОСТЬ ДВОИЧНЫХ СИМВОЛОВ | 2000 |

|

RU2176129C1 |

Предлагаемые технические решения объединены единым изобретательским замыслом, относятся к области радиотехники, а именно к автоматике, и могут быть использованы в системах и устройствах обработки цифровой информации с резервированием. Технический результат заключается в повышении вероятности точного определения состояния резервируемых устройств за счет выявления как отказов, так и сбоев различной кратности. Способ управления дублированной системой с задержкой предусматривает дополнительные выделения информационных последовательностей импульсов на выходах резервируемых устройств, которые дают основание для оценки состояния каждого из устройств, путем вычисления параметров усечения, их сравнений между собой, а также с пороговыми и эталонными значениями, в результате которых с высокой вероятностью определяют не только отказы, но и сбои в работе этих устройств. Дублированная система с задержкой состоит из первого и второго резервируемых устройств, первого и второго регистров сдвига, первого и второго электронных ключей, элемента ИЛИ. Благодаря тому, что дополнительно введены третий электронный ключ, генератор, блок анализа, блок памяти, блок определения параметров, блок определения отказов, блок определения сбоев, блок сравнения, блок управления, блок индикации, обеспечивается в совокупности с другими признаками высокая вероятность определения состояния и принятия решения на реконфигурацию дублированной системы с задержкой. 2 с. и 10 з.п. ф-лы, 9 ил.

для каждого канала, формируют тестовые сигналы усечения, соответствующие этим параметрам, сравнивают тестовые сигналы усечения с эталонными значениями тестовых сигналов, при несовпадении тестовых сигналов усечения обоих каналов формируют сигнал полного отказа системы, при несовпадении тестовых сигналов усечения в одном из каналов этот канал сохраняют заблокированным и формируют сигнал отказа этого канала, а второй канал подключают к выходу системы.

затем по результатам вычислений определяют параметры усечения Y и K основного и резервного каналов, причем перечисленные действия повторяют для последующих NZ-разрядных сегментов из обработанных информационных последовательностей импульсов на выходах основного и резервного каналов.

ИЛИ - НЕ подключен к второму входу четвертого элемента И, выход которого подключен к второму входу третьего элемента И и является седьмым выходом блока управления, выходы второго, четвертого, пятого и шестого элементов ИЛИ, первого элемента ИЛИ - НЕ, третьего элемента И являются соответственно первым - шестым выходами блока управления.

| Дублированная система с задержкой | 1989 |

|

SU1660231A1 |

| Устройство для управления переключением резервных блоков | 1989 |

|

SU1635186A1 |

| US 4358823 A, 09.11.1982 | |||

| Кейджян Г.А | |||

| Прогнозирование надежности микроэлектронной аппаратуры на основе БИС | |||

| - М.: Радио и связь, 1987, с.152. | |||

Авторы

Даты

2000-03-27—Публикация

1999-04-13—Подача