Данное изобретение относится к устройствам и структурам интегральной полупроводниковой микроэлектроники и кремниевой наноэлектронике, в частности, к интегральным нейроподобным структурам нейро-БИС и нейро-ЭВМ.

Фундаментальной проблемой разработки перспективных нейро-УБИС является увеличение уровня интеграции логических элементов (ЛЭ), сложных многофункциональных пороговых и нейроподобных ЛЭ, их плотности упаковки за счет уменьшения геометрических размеров в области сотен нанометров, увеличения "интеллектуальных возможностей кристалла" при малых мощностях потребления и высоком системном быстродействии в компоновочном пространстве системы в кристалле.

Одним из эффективных путей повышения степени интеграции является переход к конструкции функционально-интегрированных логических элементов на вертикальных и планарных совмещенных структурах, где в рабочих объемах полупроводника интегрируются и совмещаются многие функции переноса подвижных носителей разного знака. Развитием данного подхода является увеличение функциональных возможностей более сложных и гибких пороговых элементов, реализующих в минимальном трехмерном объеме полупроводника большее количество необходимых универсальных логических функций.

Известны трехмерные двухзатворные МОП-структуры с вертикальным каналом [1] . Такая структура-аналог содержит полупроводниковую подложку определенного типа проводимости со столбиком, боковая поверхность которого покрыта слоем диэлектрика, на боковых сторонах которого размещены два затвора, содержит также области противоположного типа проводимости, одну, расположенную в нижней части столбика - исток, а также другую на вершине столбика - сток. Рассмотренная структура относится к чисто приборным структурам, которая имеет существенные недостатки и принципиальные ограничения при организации более сложных логических элементов и существенном расширении функциональных возможностей. Это связано с тем, что даже для построения простейшего инвертора или двухвходового ЛЭ И-НЕ требуется дополнительная площадь на кристалле и соответственно дополнительные структуры и элементы.

Известен трехмерный ЛЭ на совмещенной МОП-структуре с вертикальным каналом [2] . Для расширения функциональных возможностей двухзатворной МОП-структуры, содержащей подложку определенного типа проводимости со столбиком, боковая поверхность которого покрыта слоем диэлектрика, на противоположных сторонах которого размещены два затвора, и содержащей сток на вершине столбика и исток, причем проводимость столбика близка к собственной проводимости полупроводника, а сток изготовлен в виде перехода металл - туннельный диэлектрик - полупроводник.

Недостатком данной структуры является ограниченные функциональные возможности, очень малая гибкость реализованного в единице объема кристалла элементарных логических функций, резкое увеличение межэлементных линий связи для формирования сложных логических функций и функционально-совершенных архитектур УБИС. К ограничениям данной структуры следует отнести также невысокое ее быстродействие из-за использования подложки и связанной с ней повышенной емкости.

Критический анализ перспективного класса трехмерных вертикальных совмещенных МОП (ВСМОП) структур может быть дополнен по прежнему актуальным фактором разработки планарных интегральных функционально-интегрированных, совмещенных структур и многофункциональных ЛЭ, изготовляемых традиционными технологическими методами (в отличие от нетрадиционного, и даже экзотического технологического воплощения ВСМОП). Особенно планарная конструкция элементов плотноупакованных многофункциональных УБИС приобретает первостепенное значение, когда плотность размещения элементов ограничивается сложностью нерегулярной разводки в логических. При этом требуется сток и затвор МОП-структур размещать в одной плоскости для сохранения планарности элементов УБИС. Первые планарные простейшие совмещенные МОП (ПСМОП) структуры и ЛЭ были предложены недавно в России [3].

Планарная совмещенная МОП-структура, используемая нами в качестве прототипа, содержит в основании подложку n-типа, в которой сформирована центральная сильнолегированная p+-область, поверх которой расположен p-слой с проводимостью, близкой к собственной проводимости полупроводника, и разделенных этим слоем приповерхностную p+-область и смежные с ней n+-области общего центрального комбинированного стока с соответствующим электродом, а также p+-области первого и второго истока с соответствующими электродами, и содержащая также первый и второй затворы, нанесенные на подзатворные слои диэлектрика, сформированных на соответствующих разделяющих низколегированных p-областях между p+-областями истока и n+-областями стока.

Недостатком данной структуры-прототипа являются ограниченные функциональные возможности, очень малая гибкость реализованного в единице объема кристалла элементарных логических функций, резкое увеличение межэлементных линий связи для формирования сложных логических функций и функционально-совершенных архитектур УБИС, а также недостаточно высокое быстродействие вследствие значительных барьерных емкостей структуры при использовании подложки (n-типа).

Для расширения функциональных возможностей структуры, кардинального уменьшения межэлементных линий связи, увеличения плотности упаковки и быстродействия предлагается планарная совмещенная нейроструктура для УБИС КНИ, содержащая в основании центральную сильнолегированную p+-область, поверх которой расположен p-слой с проводимостью, близкой к собственной проводимости полупроводника, и разделенных этим слоем приповерхностную p+-область и смежные с ней n+-области общего центрального комбинированного стока с соответствующим электродом, а также p+-области первого и второго истока с соответствующими электродами, и содержащая также первый и второй затворы, нанесенные на подзатворные слои диэлектрика, сформированных на соответствующих разделяющих низколегированных p-областях между p+-областями истока и n+-областями стока; центральная p+-область в основании структуры окружена с двух сторон смежными сильнолегированными n+-областями и размещена на нижнем диэлектрическом слое, а первый и второй затворы выполнены в виде плавающих затворов, на каждый из которых нанесен второй тонкий слой диэлектрика, на котором сформированы изолированные друг от друга и поглощающего центрального электрода стока n входных контактов с соответствующими площадями и емкостями входных контактов относительно плавающего затвора, определяющими весовые значения и формирующими функцию взвешенного суммирования путем сложения зарядов на плавающем затворе нейроструктуры и соответствующую пороговую функцию, причем соответствующие входные контакты попарно соединены друг с другом.

Предлагается также аналогичная структура, в которой сток выполнен в виде двух смежных разнородных контактов Шоттки n- и p-типа, а соответствующие попарные входные контакты к плавающим затворам разомкнуты.

Предлагаемая конструкция нейроструктуры будет отличаться от прототипа тем, что в зависимости от напряжения на плавающих затворах при реализации функции взвешенного суммирования путем сложения зарядов на плавающих затворах, когда веса будут определяться емкостями соответствующих входных контактов относительно этого затвора, в совмещенных слаболегированных каналах могут перемещаться от основания структуры к его комбинированному центральному стоку либо основные, либо неосновные носители, передающие информацию на общий для нейроструктуры выход-контакт истока. В итоге, потенциал стока предлагаемой нейроструктуры будет являться пороговой логической функцией от взвешенного суммирования на плавающих затворах и порогового значения, то есть нейроструктура реализует сложную логическую функцию, что увеличивает функциональные возможности и логическую гибкость по сравнению с прототипом. Кроме того для предлагаемой нейроструктуры достигается более высокая степень упаковки и интеграции вследствие использования принципа формирования кремний на изоляторе (КНИ), а также более высокого быстродействия ЛЭ. Более того планарная сущность нейроструктуры позволяет упростить попарное соединение входных контактов на поверхности структуры а также более просто и эффективно производить межэлементные соединения (и все это в рамках традиционных методов изготовления УБИС КНИ).

Таким образом, предлагаемая конструкция нейроструктуры обеспечивает достижение нового технического результата - получение сложной пороговой функции нейроподобного элемента в минимальном объеме кристалла без дополнительных межэлементных линий связи, необходимых при реализации сложных функциональных устройств на элементарных двухвходовых вентилях 2 И-НЕ, при более высокой плотности упаковки ЛЭ и их быстродействия. В рамках нанотехнологий и разрабатываемых наноэлектронных архитектур использование трехмерной нейроструктуры обеспечивает не только высочайшую плотность размещения, более высокое системное быстродействие нейро-УБИС, но позволяет устранить и/или ослабить влияние "тирании соединений" для сверхинтегрированных систем при использовании шинных архитектур для адаптивных гибких самоорганизующихся нейросетей.

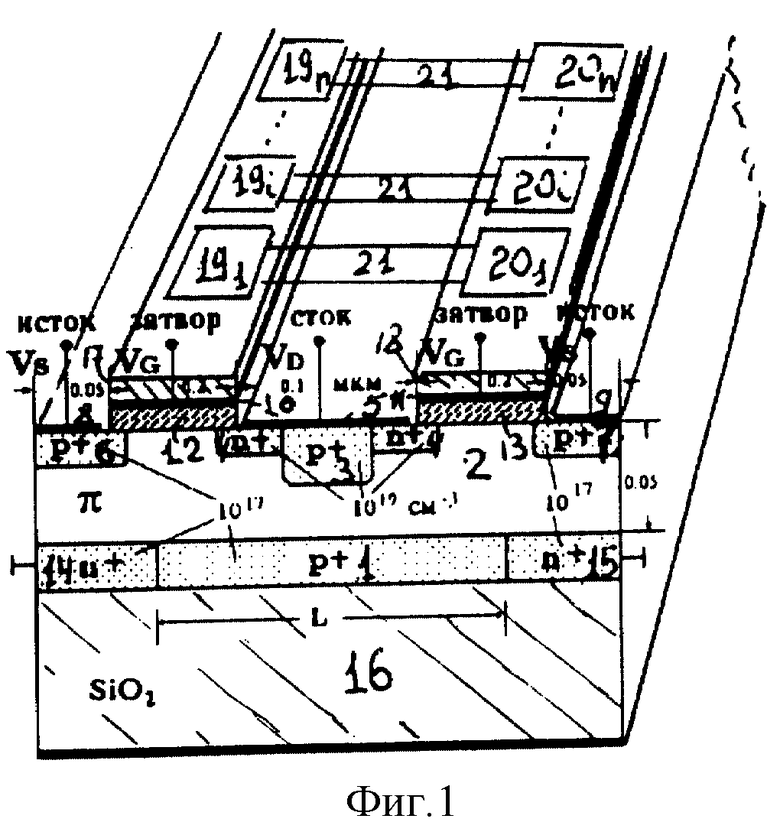

Фиг. 1 иллюстрирует предлагаемую конструкцию планарной совмещенной нейроструктуры для УБИС КНИ. Нейроструктура, содержащая в основании центральную сильнолегированную p+-область 1. Поверх нее расположен p-слой 2 с проводимостью, близкой к собственной проводимости полупроводника. В структуре имеются отделенные слоем 2 приповерхностная p+-область 3 и прилегающие к ней n+-области 4 общего центрального комбинированного стока с соответствующим электродом 5, а также p+-области 6, 7 первого и второго истока с соответствующими электродами 8, 9. Структура содержит также первый 10 и второй 11 затворы, нанесенные на подзатворные слои диэлектрика 12 и 13, сформированных на соответствующих разделяющих низколегированных p-областях 2 между p+-областями 6, 7 истока и n+-областями 4 стока.

Центральная p+-область 1 в основании структуры окружена с двух сторон смежными сильнолегированными n+-областями 14, 15 и размещена на нижнем диэлектрическом слое 16. Первый и второй затворы 10, 11 выполнены в виде плавающих затворов, на каждый из которых нанесен второй тонкий слой диэлектрика 17 и 18. На этих слоях сформированы изолированные друг от друга и поглощающего центрального электрода 6 стока n входных попарных контактов 191, 19i, 19n, 201, 20i, 20n с требуемыми площадями и емкостями входных контактов относительно плавающего затвора, а также определяющими весовые значения и формирующими функцию взвешенного суммирования путем сложения зарядов на плавающем затворе нейроструктуры и соответствующую пороговую функцию. Соответствующие входные контакты попарно соединены друг с другом внутренними соединениями 21.

Структура по п.2 предлагаемой заявки содержит сток 5, который выполнен в виде двух смежных разнородных контактов Шоттки n- и p-типа 51, 52.

Фиг. 1 иллюстрирует также особенности и параметры конструкции и топологии нейроструктуры. Нейроструктура содержит полупроводниковую p-область 1 и p-области истоков 8, 9 с концентрацией легирующей p-область 1 и p-область 1 и p-области истоков 8, 9 с концентрацией легирующей примеси 1017 см-3. Аналогичная концентрация выбрана и для смежных с p-областью 1 n-областей 14 и 15. В верхней части структуры сформированы n-слои 4 комбинированного истока с концентрацией легирующей примеси 1019 см-3. В аналогичной части структуры сформирован p слой 3 с концентрацией легирующей примеси 1019 см-3. Над центральной p-областью 1 и смежными n- областями сформирована главная совмещенная p-область 2, заполненная кремнием p-типа проводимости, причем проводимость совмещенной области близка к собственной проводимости полупроводника, например 1011 - 1014 см-3.

Сток структуры может быть изготовлен как поглощающий контакт, выполненный в виде двух смежных разнородных контактов Шоттки n- и p-типа 51, 52, причем для создания эффективных контактов Шоттки могут быть использованы n-слой 3 и p-слой 4 с концентрацией легирующей примеси около 1015 - 1018 см-3.

Предлагаемая нейроструктура работает следующим образом. При подаче хотя бы на один затвор обедняющего напряжения вследствие низколегированного или нелегированного p-слоя 2 с низкой проводимостью происходит обеднение всего слоя, а под соответствующим затвором образуется канал для неосновных носителей. Если же на оба затвора подается обогащающее напряжение, то под затвором формируются основные носители. Причем источником неосновных носителей является n-слой 14, 15 а источником основных носителей является p-слой 1 (а также слои 6, 7). При прямом смещении соответствующего p-n-перехода неосновные носители двигаются к поверхности слоя 2 и формируют индуцированный канал. Поглощающий стоковый контакт обеспечивает протекание тока основных носителей при потенциале электрода стока, соответствующего обогащению столбика, также аналогично обеспечивается протекание тока неосновных носителей при потенциале, соответствующего обеднению столбика. Структура при управлении первым и вторым затворами выполняет логическую функцию 2 ИЛИ-НЕ, поскольку потенциал на верхнем электроде будет обогащающем, если хотя бы на один затвор будет подано обедняющее напряжение, и будет обедняющим, если на оба затвора будет подано обогащающее напряжение.

Специфика нейроструктуры с плавающими затворами такова, что происходит воздействие на каналы слаболегированного слоя 2 напряжениями сигналов, поданных на входы 19, 20. Объединением необходимого количества входов 1...n справа и слева с соответствующими напряжениями U1, U2, Un обеспечивается соответствующее управление затворами 8 и 9 через емкостные связи к плавающему затвору Ci, Cn. Аккумулируемые фиксированные веса, определяемые емкостями входных контактов, будут управлять токами основных и неосновных носителей от истока к стоку.

Изолированные друг от друга n входных контактов с соответствующими площадями и их барьерными емкостями входных контактов относительно плавающего затвора будут определять весовые значения и формировать целевую функцию взвешенного суммирования путем сложения зарядов на плавающем затворе нейроструктуры и, в конечном итоге, пороговую функцию нейроэлемента, Y=1 при сумме XiWi > hi и Y=0 при других значениях суммы согласно формуле для пороговой функции Y=f(WiXi-Hi), где Wi - весовые значения, Xi - входные значения, Hi - пороговые значения.

Плавающий потенциал Ф определяется величиной

Ф = (C1V1...+CiVi+... +CnVn)/(C1...+Ci...+Cn+Cc),

где в полной емкости структуры Ct=(C1...+Ci...+Cn+Cc), Cc - емкость собственно канала, а компоненты емкостей плавающего затвора Ci образованы емкостями контактов 11 и 12, Vi = XiVdd, Vdd - напряжение на стоке. Другими словами, напряжение на плавающем электроде есть взвешенная сумма зарядов на затворе (взвешенная сумма входных напряжений с коэффициентом Ci/Ct). Как только потенциал Ф превышает пороговое напряжение Vt, симметричное для "виртуальных" МОП-транзисторов в структуре, канал становится проводящим. Более того, пороговое напряжение Vt в значительной мере управляется потенциалом Ф.

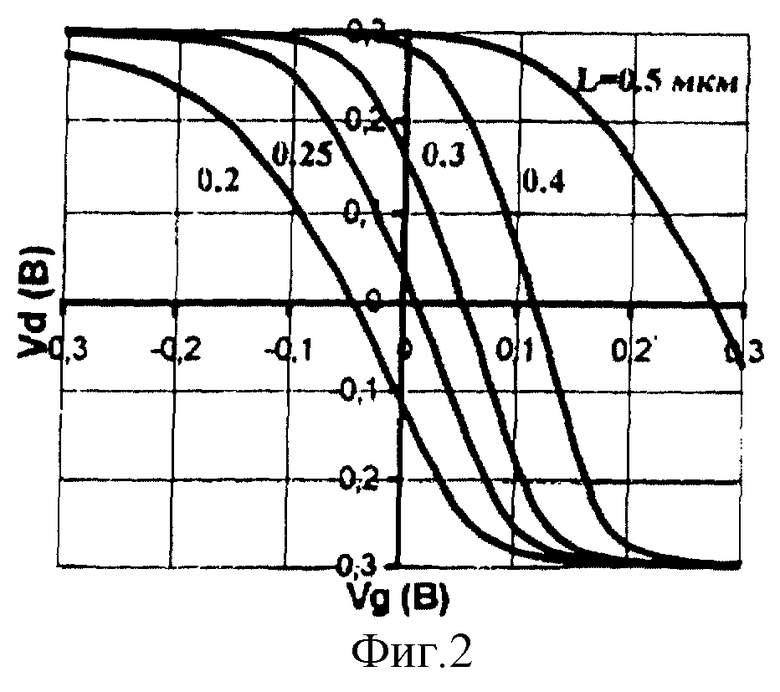

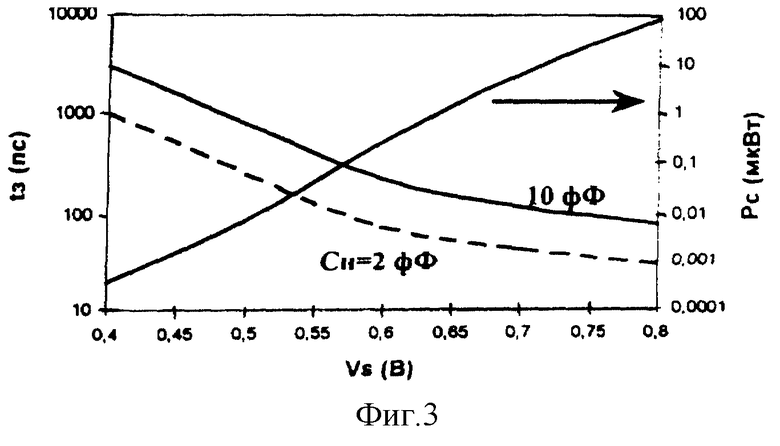

На фиг. 2 представлены расчетные передаточные характеристики инвертора, представленного на фиг. 1, при различных значениях длины слоя 1 L с помощью программы численного приборно-схематехнического моделирования DCSIM-98. Рассчитанный коэффициент усиления по напряжению лежит в переделах 4-12 для разных величин L, что обеспечивает достаточный запас помехоустойчивости инвертора. На фиг. 3 представлены расчетные зависимости статической мощности, а также времен задержек нейроструктуры в режиме инвертора при емкостях нагрузки 2 фФ и 10 фФ, показывающие реальную возможность получения высокого технологического (50 пс при Vs=0.55-0.8 В) и системного быстродействия (100-150 пс при Vs=0.6-0.8 В). В специфических режимах нейроструктур, когда нецелесообразно гнаться за высоким системным быстродействием и можно работать на невысоких тактовых частотах около 1 МГц, имеет смысл ограничиться меньшими логическими перепадами порядка 0.4 В при статических мощностях менее 0.3 нВт.

Многофункциональные нейроэлементы с минимальными топологическими размерами от 0.2 мкм до 0.02 мкм позволят получить плотность упаковки процессорных УБИС на эквивалентных двухвходовых вентилях от 108 до 1011 элементов/см2 соответственно. В то же время использование нейроэлементов позволяет за счет гибкой внутренней структуры резко сократить количество внешних межэлементных связей. Рассчитанные приведенные выше характеристики собственно инвертора и нейроструктуры с соответствующими входами и попарно соединенными друг с другом входными контактами (фиг. 1) характеризует прекрасное сочетание производительности настраиваемой под определенную задачу для искусственного интеллекта с плотностью размещения. Это открывает широчайшие возможности создания сверхплотноупакованных интеллектуальных систем и устройств в режиме реального времени, встраивания цифровых устройств в многоэлементные телеметрические, фотоприемные интегральные схемы, создания телекоммуникационной наземной и космической аппаратуры новейших поколений.

Для технологической реализации стандартных логических УБИС требуется от 20 до 28 литографических операций, причем на приборную часть надо около 12-17 литографий и на каждый слой металла в многоуровневых УБИС по две литографии (одна на контакты, другая на металл), имея в виду, что современные и перспективные микропроцессорные УБИС используют уже от 4 до 7 слоев металлизации. В заявляемом изобретении приборная структура может быть изготовлена всего с помощью одной литографии. Поскольку плотность упаковки в ней реализуется высочайшая, для того чтобы минимизировать количество металлических слоев, целесообразно ограничиться всего одним или двумя слоями металлизации. Как для однослойных и даже двухслойных УБИС на предложенных планарных нейроструктурах можно ограничиться всего одной литографией. Это резко уменьшит стоимость технологического воплощения нейрочипа, цикл изготовления, увеличит его надежность, резко улучшит технологичность, выход годных.

Таким образом, в планарной совмещенной нейроструктуре реализуются более высокие функциональные возможности, высочайшая логическая гибкость при высокой плотности упаковки, с соответствующим сокращением межэлементных линий связи. Технико-экономический эффект от предлагаемого изобретения заключается в увеличении логической гибкости в минимальном объеме кристалла без потери системного быстродействия в субсистемах УБИС по мере увеличения их степени интеграции. Для предлагаемой планарной нейроструктуры достигается более высокая степень упаковки и интеграции вследствие использования принципа формирования кремний на изоляторе (КНИ), а также более высокого системного быстродействия ЛЭ. Планарная конструкция нейроструктуры позволяет упростить попарное соединение входных контактов на поверхности структуры, а также более просто и эффективно производить межэлементные соединения (и все это в рамках традиционных методов изготовления УБИС КНИ). Именно планарный вариант субмикронных нейроструктур допускает изготовление нейро-УБИС с использованием всего одной литографической операции на собственно приборную часть, что позволяет удешевить производство подобных нейро-УБИС и увеличить его рентабельность при обеспечении высочайших технико- эксплуатационных параметров.

Источники информации

1. Заявка EP 0149390.

2. Микроэлектроника, 1996, т. 25, N 2, с. 112-115.

3. Ракитин В.В., Филиппов Е.И. Планарные элементы на совмещенных МОП-транзисторах // Микроэлектроника. 1998. Т. 27. N 3, с. 190-193 (с. 191, рис. 1 - прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| ТРЕХМЕРНАЯ НЕЙРОСТРУКТУРА | 1999 |

|

RU2173006C2 |

| НИЗКОВОЛЬТНЫЙ БЫСТРОДЕЙСТВУЮЩИЙ БИПОЛЯРНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА КОМПЛЕМЕНТАРНЫХ СТРУКТУРАХ | 1999 |

|

RU2173915C2 |

| СВЕРХБЫСТРОДЕЙСТВУЮЩЕЕ СВЕРХИНТЕГРИРОВАННОЕ БИМОП ОЗУ НА ЛАВИННЫХ ТРАНЗИСТОРАХ | 1999 |

|

RU2200351C2 |

| МИКРОМОЩНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ С ВЫСОКОЙ НАГРУЗОЧНОЙ СПОСОБНОСТЬЮ | 1999 |

|

RU2172064C2 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ТРАНЗИСТОРА С НЕЗАВИСИМЫМ КОНТАКТОМ К ПОДЛОЖКЕ | 2020 |

|

RU2739861C1 |

| КМОП-ТРАНЗИСТОР С ВЕРТИКАЛЬНЫМИ КАНАЛАМИ И ОБЩИМ ЗАТВОРОМ | 2012 |

|

RU2504865C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПЛАНАРНОГО СИЛОВОГО МОП ТРАНЗИСТОРА | 2002 |

|

RU2239912C2 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ТУНЕЛЬНОГО МНОГОЗАТВОРНОГО ПОЛЕВОГО НАНОТРАНЗИСТОРА С КОНТАКТАМИ ШОТТКИ | 2018 |

|

RU2717157C2 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МДП НАНОТРАНЗИСТОРА С ЛОКАЛЬНЫМ УЧАСТКОМ ЗАХОРОНЕННОГО ИЗОЛЯТОРА | 2012 |

|

RU2498447C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МДП ТРАНЗИСТОРА С ЛОКАЛЬНЫМИ УЧАСТКАМИ ЗАХОРОНЕННОГО ИЗОЛЯТОРА | 2002 |

|

RU2235388C2 |

Использование: при конструировании устройств и структур интегральной полупроводниковой микроэлектроники и кремниевой наноэлектроники, в частности интегральных нейроподобных структур нейро-БИС и нейро-ЭВМ. Сущность изобретения: предлагается планарная совмещенная нейроструктура для УБИС КНИ, содержащая в основании центральную сильнолегированную p+-область, поверх которой расположен p-слой с проводимостью, близкой к собственной проводимости полупроводника, и отделенные этим слоем приповерхностную р+-область и n+-области общего центрального комбинированного стока с соответствующим электродом, а также р+-области первого и второго истока с соответствующими электродами, и содержащая также первый и второй затворы, нанесенные на подзатворные слои диэлектрика, сформированные на соответствующих разделяющих низколегированных р-областях между р+-областями истока и n+-областями стока; центральная р+-область в основании структуры окружена с двух сторон смежными сильнолегированными n+-областями и размещена на нижнем диэлектрическом слое, а первый и второй затворы выполнены в виде плавающих затворов, на каждый из которых нанесен второй тонкий слой диэлектрика, на котором сформированы изолированные друг от друга и поглощающего центрального электрода стока n входных контактов с соответствующими площадями и емкостями входных контактов относительно плавающего затвора, определяющими весовые значения и формирующими функцию взвешенного суммирования путем сложения зарядов на плавающем затворе нейроструктуры и соответствующую пороговую функцию, причем соответствующие входные контакты попарно соединены друг с другом. Кроме того, в зависимости от напряжения на плавающих затворах при реализации функции взвешенного суммирования путем сложения зарядов на плавающих затворах, когда веса будут определяться емкостями соответствующих входных контактов относительно этого затвора, в совмещенных слаболегированных каналах могут перемещаться от основания структуры к его комбинированному центральному стоку либо основные, либо неосновные носители, передающие информацию на общий для нейроструктуры выход-контакт истока. Техническим результатом изобретения является расширение функциональных возможностей структуры, кардинальное уменьшение межэлементных линий связи, увеличение плотности упаковки и быстродействия. 1 з.п. ф-лы, 3 ил. .

| РАКИТИН В.В | |||

| и др | |||

| Планарные элементы на совмещенных МОП-транзисторах | |||

| Микроэлектроника, т.27, N 3, 1998, с.190-193 | |||

| Бесколесный шариковый ход для железнодорожных вагонов | 1917 |

|

SU97A1 |

| Прибор для очистки паром от сажи дымогарных трубок в паровозных котлах | 1913 |

|

SU95A1 |

| Прибор для очистки паром от сажи дымогарных трубок в паровозных котлах | 1913 |

|

SU95A1 |

| Экономайзер | 0 |

|

SU94A1 |

| Домовый номерной фонарь, служащий одновременно для указания названия улицы и номера дома и для освещения прилежащего участка улицы | 1917 |

|

SU93A1 |

| US 5530275 A, 25.06.1996. | |||

Авторы

Даты

2001-10-27—Публикация

1999-11-15—Подача