Данное изобретение относится к устройствам и структурам интегральной микроэлектроники, в частности к интегральным ячейкам статической памяти и оперативным запоминающим устройствам (ОЗУ) БИС и ЭВМ.

Фундаментальной проблемой разработки элементной базы БИС и ЭВМ является увеличение уровня интеграции устройств динамической и статической памяти, увеличения плотности упаковки бистабильных ячеек (БЯ), уменьшения размеров БЯ, количества рабочих шин, а также снижение мощности потребления БЯ ОЗУ, увеличения их нагрузочной способности и соответствующего системного быстродействия в компоновочном пространстве БИС. Переход к субмикронным и глубокосубмикронным технологиям позволяет резко снизить размеры и рабочие площади БЯ, однако проблема увеличения рабочих частот при дальнейшем снижении и мощности потребления остается критической для перспективных ультраБИС (УБИС).

Увеличение рабочих частот микропроцессорных (МП) КМОП УБИС до 300-600 МГц, правда, ценой увеличения потребляемой мощности вплоть до 30-80 Вт/кристалл обострило проблематику разрыва в производительности логических МП систем и систем динамических запоминающих устройств (ДОЗУ, DRAM), рабочая частота которых определяется как F(ДОЗУ)=1/время выборки. Чтобы избежать потерь системного быстродействия перспективных процессорных глубокосубмикронных и наноэлектронных КБИ-КБИКМОП/КМОП УБИС для широкого класса ЭВМ от персональных до суперкомпьютеров с рабочими гигагерцовыми частотами, возможны две альтернативы развития. Во-первых, использование значительно более быстродействующих архитектур ДОЗУ - SDRAM, RAMBUS, SYNC LINK, реализованных по технологиям глубокого субмикрона. Во-вторых, использование стандартных экономичных по мощности и занимаемой площади глубоко субмикронных реализаций статической кэш-памяти ОЗУ (SRAM) для перспективных КМОП УБИС. В-третьих, поиск новых экономичных по мощности и занимаемой площади глубоко субмикронных реализаций сверхскоростной статической кэш-памяти ОЗУ (SRAM) для перспективных МП УБИС на новых физических принципах, например на (БЯ) с лавинными транзисторами и с управляющими МОП ключами.

Несмотря на значительно меньшее внимание, уделяемое в литературе и потоке НИОКР по созданию сверхбыстродействующих МП систем, третья альтернатива развития нам представляется весьма перспективной, открывающей новые колоссальные возможности плотноупакованной кэш-памяти для технологий глубокого субмикрона при создании новейших типов ЭВМ широкого назначения с субгигагерцовыми рабочими частотами.

Таким образом, известны типовые двухмерные и трехмерные БЯ ДОЗУ на одном МОП-приборе и одном конденсаторе, запоминающем один бит информации, которые характеризуются очень высокой плотностью компоновки, однако невысоким быстродействием и использованием нежелательных циклов регенерации хранимой информации. Известны статические ОЗУ на триггерных БЯ с перекрестными связями, выполненных на двух транзисторах с высокоомными коллекторными нагрузками, или четырех МОП транзисторах (двух КМОП инверторах), содержащие, как еще два ключа - МОП транзистора выборки, соединенных со входами инверторов. Данные БЯ и собственно ОЗУ имеют невысокую плотность компоновки при достаточно высоком быстродействии.

Для того чтобы попытаться реализовать сверхвысокую плотность компоновки статических схем памяти, в [2] предложена БЯ на одном лавинном транзисторе с управляющим МОП-ключом. Фрагмент ОЗУ, выбранного нами в качестве прототипа, наиболее близкого к заявляемому объекту конструкционного решения. содержит бистабильную ячейку на лавинном транзисторе, база которого соединена со стоком управляющего р-МОП транзистора, исток которого соединен с битовой шиной, а затвор - со словной шиной, причем эмиттер лавинного транзистора соединен с общей шиной, а коллектор - с источником коллекторного напряжения.

Потенциальные возможности данного типа БЯ достаточно велики: 1) при хранении информации в них в отличие от БЯ ДОЗУ практически отсутствуют помехи от токов утечек МОП-приборов, 2) реализуется сверхвысокая плотность компоновки, для 1 мкм - технологии БЯ занимала площадь на кристалле всего 8.58 мкм2 [1] . В то же время данные БЯ характеризуются низким системным быстродействием и значительной мощностью потребления в режиме хранения "1", около 0.45 мВт. Вопросы снижения статической мощности потребления БЯ и системной организации SRAM кэш-памяти при сохранении высокого потенциального быстродействия остаются открытыми.

Для повышения степени интеграции и быстродействия перспективных статических ОЗУ на лавинных транзисторах, конкурентных по всей совокупности параметров стандартным статическим КМОП-ОЗУ, требуются БИМОП БЯ с минимальным количеством рабочих шин, обеспечивающие высокую нагрузочную способность и малую потребляемую мощность для микромощных быстродействующих УБИС ОЗУ.

Задачей изобретения является создание БЯ и фрагментов ОЗУ на лавинных транзисторах, обеспечивающих микромощный режим потребления статических мощностей (единицы - десятки нановатт), приемлемую помехоустойчивость работы, высокие рабочие частоты, уменьшение рабочей площади малокомпонентной БЯ для плотноупакованных УБИС. Дополнительными целями, ставящими достижение сверхинтеграции и сверхбыстродействия УБИС на заявляемых ОЗУ, являются: дополнительное значительное уменьшения площади кристалла при реализации совмещенных функционально-интегрированных БИКМОП структур, а также обеспечивающих сокращение площади кристалла, затрачиваемой на шинное соединение приборов и ячеек и на разводку питания.

Указанная задача достигается тем, что: 1) сверхбыстродействующее сверхинтегрированное БИМОП ОЗУ на лавинных транзисторах, содержащее бистабильные ячейки на лавинных транзисторах, база каждого из которых в ячейке соединена со стоком управляющего р-МОП транзистора, исток которого соединен с битовой шиной, а затвор - со словной шиной, отличающийся тем, что лавинный транзистор выполнен в виде двухэмиттерного транзистора, коллектор которого соединен с источником напряжения и каналом управляющего р-МОП транзистора, первый эмиттер соединен с битовой шиной, выходом ячейки и стоком общего для группы ячеек первого n-МОП транзистора считывания с соответствующими цепями смещающих напряжений на истоке и затворе, а второй эмиттер лавинного транзистора соединен с шиной первого генератора тока и стоком общего для группы ячеек второго n-МОП транзистора первого генератора тока с соответствующими цепями смещающих напряжений на затворе и истоке; 2) сверхбыстродействующее сверхинтегрированное БИМОП ОЗУ на лавинных транзисторах, содержащее бистабильные ячейки на лавинных транзисторах, база каждого из которых в ячейке соединена со стоком управляющего р-МОП транзистора, отличающийся тем, что лавинный транзистор выполнен в виде двухэмиттерного транзистора, коллектор которого соединен со словной шиной и затвором управляющего р-МОП транзистора, канал которого изолирован от других областей активных приборов, первый эмиттер соединен с битовой шиной, выходом ячейки и стоком общего для группы ячеек первого n-МОП транзистора считывания с соответствующими цепями смещающих напряжений на истоке и затворе, а второй эмиттер лавинного транзистора соединен с шиной первого генератора тока и стоком общего для группы ячеек второго п- МОП транзистора первого генератора тока с соответствующими цепями смещающих напряжений на затворе и истоке; 3) устройство по пп.1,2, отличающееся тем, что битовая шина соединена с базой входного транзистора переключателя тока, эмиттер которого соединен со вторым генератором тока и эмиттером опорного транзистора, коллектор которого соединен с выходом и через резистор с общей шиной, соединенной с коллектором входного транзистора, а база опорного транзистора - с источником варьируемого опорного напряжения.

Сущность изобретения и его отличительные от прототипа признаки заключаются в уникальной возможности обеспечения сверхбыстродействия в микромощном режиме, высокой помехоустойчивости и работоспособности БЯ на биполярных двухэмиттерных лавинных транзисторах в используемой схемотехнике эмиттерного повторителя, где в силу эффективного обнуления базового тока и связанного с этим увеличения коэффициента передачи тока В базовое сопротивление ни дает никакого вклада в потери системного быстродействия; при этом происходит максимально быстрая перезарядка нагрузочной емкости (битовой шины и др.). Реализуемый в БЯ и всем ОЗУ принцип функциональной интеграции - совмещения рабочих областей приборов и шин: битовой и выходной, словной и напряжения питания позволяет достичь сверхплотной упаковки БЯ, сравнимой с плотностью, достигаемой в ДОЗУ. Этому же способствует использование для многих БЯ единых генераторов тока и n-МОП транзистора разрядки, что при обеспечении малых площадей в статическом ОЗУ позволяет реализовать высокую работоспособность на высоких частотах в режиме нескольких единиц ГГЦ в микромощном режиме единиц ватт БЯ. Компромисс обеспечения требуемой помехоустойчивости в диапазоне высоких рабочих частот, реализуемый с помощью вводимого в ОЗУ порогового устройства на переключателе тока с переменным порогом в виде варьируемого опорного напряжения позволяет максимально реализовать высокий потенциал системного быстродействия, помехоустойчивости и надежности статических сверхинтегрированных ОЗУ.

Рассмотрим перечень фигур графического изображения и примеры конкретного выполнения заявленного ОЗУ согласно пунктам изобретения в виде функционально-интегрированного конструктивного воплощения БЯ в кристалле пунктам формулы изобретения.

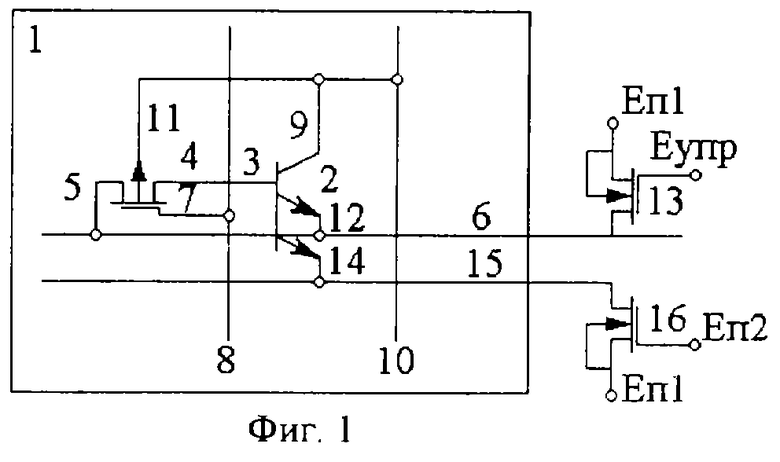

На фиг.1 приведена принципиальная обобщенная схема главного фрагмента БЯ 1 сверхбыстродействующего сверхинтегрированного БИМОП ОЗУ на лавинном двухэмиттерном транзисторе 2, его база 3 соединена со стоком управляющего р-МОП транзистора 4, исток 5 которого соединен с битовой шиной 6, а затвор 7 - со словной шиной 8. Коллектор 9 двухэмиттерного транзистора 2 соединен с источником напряжения 10 и каналом 11 р-МОП транзистора 4. Первый эмиттер 12 лавинного транзистора 2 соединен с битовой шиной 6, выходом ячейки и стоком первого n-МОП транзистора считывания 13 с соответствующими цепями смещающих напряжений на истоке и затворе, а второй эмиттер 14 транзистора 2 соединен с шиной 15 общего для группы ячеек первого генератора тока и стоком второго n-МОП транзистора 16 с соответствующими цепями смещающих напряжений на затворе и истоке.

На фиг.2 приведена модифицированная схема главного фрагмента БЯ 1 сверхбыстродействующего сверхинтегрированного БИМОП ОЗУ на лавинном двухэмиттерном транзисторе 2. Коллектор 9 двухэмиттерного транзистора 2 в каждой ячейке соединен со словной шиной 8 ( совмещенной с шиной источника напряжения 10), затвором управляющего р-МОП транзистора 7, канал которого 11 изолирован от других областей активных приборов. Первый эмиттер 12 лавинного транзистора 2 соединен с битовой шиной 6, выходом ячейки и стоком общего для группы ячеек n-МОП транзистора разрядки 13 с соответствующими цепями смещающих напряжений на истоке и затворе, а второй эмиттер 14 транзистора 2 соединен с шиной 15 общего для группы ячеек первого генератора тока и стоком второго n-МОП транзистора 16 с соответствующими цепями смещающих напряжений на затворе и истоке.

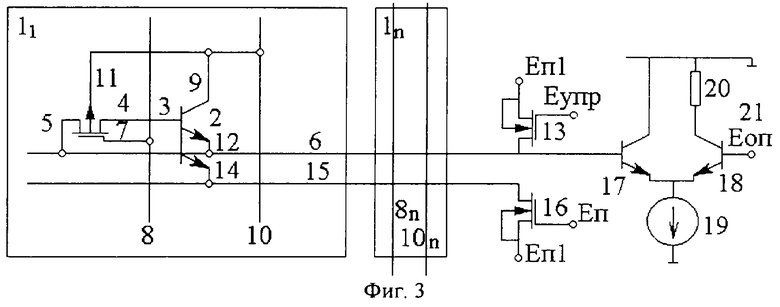

На фиг. 3 приведена обобщенная схема сверхбыстродействующего сверхинтегрированного БИМОП ОЗУ на базе технического решения БЯ (фиг.1) с использованием порогового устройства на переключателе тока. Битовая шина 6 соединена с базой входного транзистора 17 переключателя тока, эмиттер которого соединен с генератором тока 19 и эмиттером опорного транзистора 18, коллектор которого соединен с выходом и через резистор 20 с общей шиной, соединенной с коллектором входного транзистора 17, а база - с источником варьируемого опорного напряжения 21.

На фиг. 4 приведена обобщенная схема сверхбыстродействующго сверхинтегрированного БИМОП ОЗУ на базе технического решения БЯ (фиг.2) с использованием порогового устройства на переключателе тока. Битовая шина 6 соединена с базой входного транзистора 17 переключателя тока, эмиттер которого соединен с генератором тока 19 и эмиттером опорного транзистора 18, коллектор которого соединен с выходом и через резистор 20 с общей шиной, соединенной с коллектором входного транзистора, а база - с источником варьируемого опорного напряжения 21.

Устройство на фиг. 1 работает следующим образом. При помощи МОП 4 и 13 ключей производится режим выбора БЯ для записи и считывания соответственно. В обратно смещенном коллекторном переходе транзистора 2 происходит лавинное умножение коллекторного тока. При некотором обратном коллекторном напряжении Ua добавочный лавинный коллекторный ток компенсирует компоненту диффузионного тока рекомбинации базы транзистора 2, что приводит к нулевому базовому току транзистора. Этому режиму соответствует хранение "1" БЯ. Хранение "0" происходит в режиме полного запирания транзистора 2. В первом случае потенциал базы равен Up-Ua, а протекающий сквозной ток определяется разностью этого потенциала и потенциала эмиттера; во втором случае потенциал базы равен нулю и сквозной ток равен нулю (за исключением утечек). В отличие от чисто динамических элементов памяти рассматриваемая БЯ (фиг.1) при хранении способна компенсировать постоянные помехи типа утечек тем большей величины, чем больше сквозной ток в режиме хранения "1".

В режиме записи в БЯ осуществляется отпирание входного ключа на МОП-приборе и установка на информационной шине логического уровня, соответствующего стационарному напряжению на базе транзистора 2. При этом происходит перезарядка в основном коллекторной барьерной емкости через сопротивление входного ключа на МОП-приборе. Причем в отличие от динамического элемента, где для долговременного хранения необходимо использовать большую запоминающую емкость, здесь емкость значительно меньше, что приводит, во-первых, к экономии места на кристалле и, во-вторых, уменьшению времени ее перезарядки. При считывании информации осуществляют отпирание выходного ключа на МОП-приборе. При этом по активному фронту БЯ осуществляет перезарядку нагрузочной емкости в режиме эмиттерного повторителя (ЭП) с очень большим эффективным коэффициентом усиления по току В, в режиме эффективного нулевого базового тока при лавинном пробое. При работе на большую емкость поведение как ЭП, так и рассматриваемой БЯ по отношению к напряжению U (отклонение напряжения эмиттер-база от стационарного) и выходному току I можно аппроксимировать соотношением:

I=I0[EXP(U/Uт)-1], (1)

где I0 - статический эмиттерный ток. Отклонение напряжения на нагрузочной емкости СL совпадает по абсолютной величине с U и имеет противоположный знак. Поэтому с учетом (1) для переходного процесса справедливо следующее соотношение:

CLdU/dt=-I=-I0[EXP(U/(Uт)-1]. (2)

При этом U(0) = ±Uл. Пусть время tk таково, что напряжение U опустилось до k-й части UЛ, т.е. U(tk)=kUЛ, тогда соотношение (2) может быть преобразовано к виду для времени переключения по уровню 1/2 логического перепада

t(1/2)=Т0 ЕХР(-m/2)/m=t0 EXP(-m/2). (3)

Это время оказывается экспоненциально мало с увеличением величины логического перепада. Например, при Uл, равном 0,4 В, m равно примерно 15 и ЕХР(-m/2) равно 4•6(10-4), т.е. наблюдается уменьшение t1/2 более чем на 4 порядка. Величину tk можно записать и по-другому:

tk=(T0EXP(-km)/m=CL(Uт/Ik). (4)

Следовательно, tk в (4) можно трактовать как характерное время перезарядки нагрузочной емкости на малом сигнале через дифференциальное сопротивление эмиттерного перехода при токе Ik. При больших величинах U и больших токах может оказаться, что главную роль играет не эмиттерный переход, а балластные сопротивления транзистора 2. В случае ЭП эти сопротивления складываются из сопротивления тела эмиттера и эффективного базового сопротивления, уменьшенного в В раз, которое в свою очередь складывается из собственно базового сопротивления и выходного сопротивления схемы задающей сигнал. В силу эффективного обнуления базового тока и связанного с этим увеличения В базовое сопротивление не дает никакого вклада.

Сформулируем ряд требований к сигналам на всех шинах фрагментов ОЗУ, представленных на фиг.1,3. В режимах хранения и записи на шине 10 установлено напряжение питания 3 В, в режиме считывания из ячеек, присоединенных к данной шине, на эту шину подается повышенное напряжение (увеличенное на 1.2 В). В режиме хранения и считывания столбца БЯ для закрытого ключа на затвор 7 р-МОП транзистора 4 подается высокое напряжение. В режиме записи столбца БЯ на затвор 7 р-МОП транзистора 4 подается низкое напряжение. Для битовой шины 6 в режиме хранения поддерживается напряжение Еп1, соответствующее логическому нулю при чтении. В режимах записи и считывания ключ на транзисторе 13 запирается, при записи на этой шине устанавливается напряжение на базе 3 лавинного транзистора 2 при хранении записываемого значения. Для битовой шины 6 при чтении записанного нуля на ней реализуется низкое напряжение менее Eon - при чтении будет большее напряжение, чем Еоп (фиг.3).

В схеме фрагментов ОЗУ, представленной на фиг.2, поз.4, достигнуто сокращение рабочих шин за счет совмещения шины 8 (на фиг.1) с шиной 10,что позволит увеличить интеграционный потенциал БЯ всего ОЗУ. В режиме хранения и чтения напряжения на шине 10 идентичны напряжениям на шине 10 схем на фиг.1, поз.3. В режиме записи на шину 10 подается низкое напряжение. Принцип работы схем на фиг.2, 4 идентичен принципу работы схемам на фиг.1, поз.3.

Включением порогового устройства (на битовую шину БЯ) на переключателе тока, выполненном на транзисторах 17 и 18, установкой опорного напряжения 21 мы задаем уровень детектирования считываемых сигналов на битовой шине. Этим достигается компромисс обеспечения требуемой помехоустойчивости и диапазоне высоких рабочих частот, что позволяет максимально реализовать высокий потенциал системного быстродействия, помехоустойчивости и надежности статических сверхинтегрированных ОЗУ.

На фиг.5 представлено сечение функционально-интегрированной интегральной конструкции из двух БЯ с диэлектрической изоляцией для схемотехнических решений 1,3. Область базы биполярного транзистора 2 совмещена с областью 4 стока, область коллектора 9 совмещена с областью канала 11 р-МОП ключа. Столбцы ячеек разделены вертикальными канавками, заполненными окислом 22, все ячейки столбца имеют общий коллектор 9 (сильнолегированная шина 10). В третьем направлении Z в области базы 3 сформированы две эмиттерные области, первая 12 (указана на фиг.5) и 14 ( не указана на фиг.5). Эмиттеры 14 подключены к шине 15. Все эмиттеры 12 строки БЯ подключены к битовой шине 5. Словная шина 8 формирует затвор 7 р-МОП ключа.

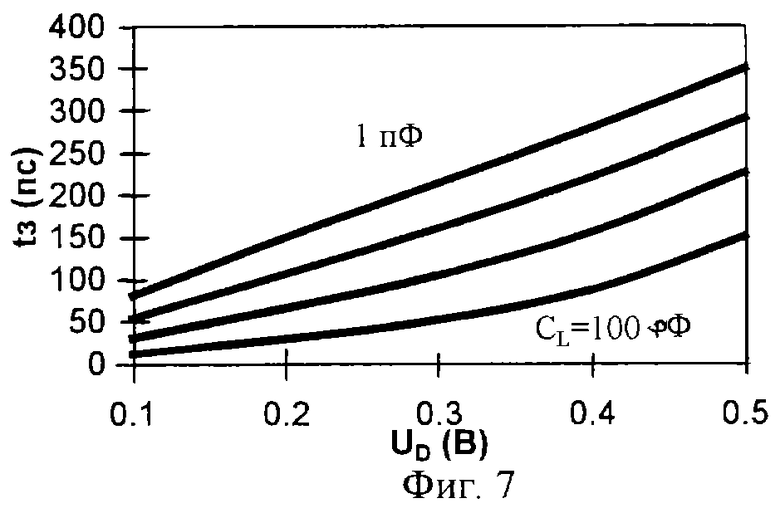

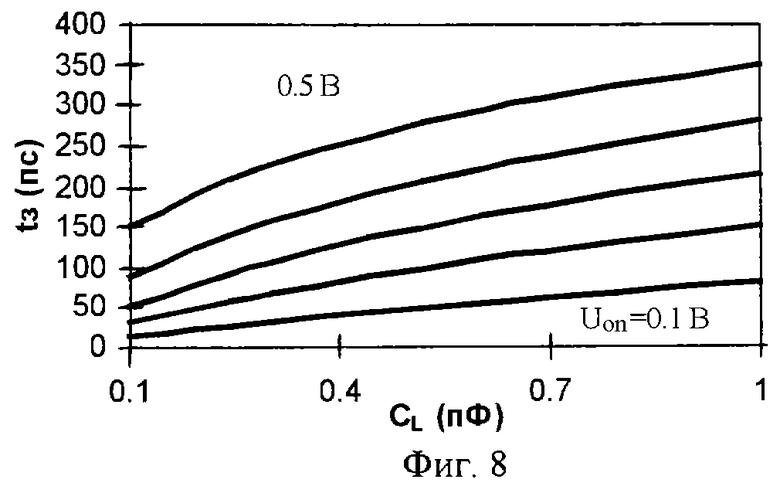

Предложеннная в заявке новая схемотехника сверхбыстродействующей, микромощной БЯ (фиг.1, 3) была промоделирована для технологии 0.15 мкм и функционально-интегрированной конструкции БЯ на двухэмит-терном транзисторе (фиг. 5). С помощью инструментария адекватного численного двумерного приборно-схемотехнического моделирования [2] проведен анализ возможностей по быстродействию и мощности, а также физических ограничений БЯ на масштабированных лавинных транзисторах в микромощном режиме Рс = 0.1-10 нВт. На фиг.6 представлены переходные процессы при считывании из БЯ при различных нагрузочных емкостях. На фиг.7, 8 представлены зависимости времени задержки от величины порога детектирования Еоп считываемого выходного потенциала (фиг.6) для различных емкостей и от нагрузочной емкости для различных пороговых напряжений Uon (и задаваемых уровней помехоустойчивости). Для увеличения интеграции УБИС ОЗУ необходимо максимально понижать статическую мощность БЯ. Уменьшения статического сквозного тока в БЯ осуществляется уменьшением тока генератора тока на n-МОП транзисторе 16. При этом можно избежать снижения быстродействия БЯ незначительным увеличением импульса коллекторного (а следовательно, и базового) напряжения, подаваемого при считывании. Снижение статического тока I0 ограничено токами утечек Iу, соответственно необходимо, чтобы I0>>Iу и не терялась информация в БЯ. При этом для статических мощностей БЯ менее 0.3-1 нВт, в рамках предлагаемых иерархических гигабитных архитектур статических ОЗУ реально достижимы f=1/Тдоступа свыше 3-5 ГГц, Рс(tд (БЯ))<2 •10-19 Дж.

Технико-экономический эффект изобретения заключается в значительном увеличении системного быстродействия микромощных вариантов сверхинтегрированных ячеек памяти статических ОЗУ УБИС, а также возможности работы фрагментов ОЗУ при приемлемой помехоустойчивости, что весьма важно при построении сверхскоростных УБИС для перспективных микропроцессорных, супер-ЭВМ высших поколений, работающих с рабочими частотами в единицы-десятки ГГц для интеллектуальных систем наземного и космического базирования.

Источники

1. Sakui К., Hasegawa Т. et. al. A New Static Memory Cell Based on the Reverse Base Current Effect of Bipolar Transistors.- IEEE Trans., V.ED-36, pp.125-127 (прототип).

2. Бубенников А.Н., Черняев А.В. Приборно-схемотехническое моделирование в САПР БИС. - Ассоциация разработчиков САПР БИС, ТРТИ, Таганрог, 1992.

| название | год | авторы | номер документа |

|---|---|---|---|

| МИКРОМОЩНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ С ВЫСОКОЙ НАГРУЗОЧНОЙ СПОСОБНОСТЬЮ | 1999 |

|

RU2172064C2 |

| НИЗКОВОЛЬТНЫЙ БЫСТРОДЕЙСТВУЮЩИЙ БИПОЛЯРНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА КОМПЛЕМЕНТАРНЫХ СТРУКТУРАХ | 1999 |

|

RU2173915C2 |

| ТРЕХМЕРНАЯ НЕЙРОСТРУКТУРА | 1999 |

|

RU2173006C2 |

| ПЛАНАРНАЯ СОВМЕЩЕННАЯ НЕЙРОСТРУКТУРА ДЛЯ УБИС КНИ | 1999 |

|

RU2175460C2 |

| Элемент памяти | 1990 |

|

SU1786508A1 |

| Быстродействующий микромощный логический элемент и-или/и-или-не | 1977 |

|

SU624369A1 |

| ЯЧЕЙКА ПАМЯТИ ДИНАМИЧЕСКОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 2001 |

|

RU2216795C2 |

| Авторегулируемый формирователь напряжения записи для электрически программируемых постоянных запоминающих устройств на КМОП-транзисторах | 1988 |

|

SU1631606A1 |

| Формирователь импульсов записи | 1985 |

|

SU1297114A1 |

| Ячейка оперативной памяти | 2024 |

|

RU2826859C1 |

Изобретение относится к устройствам и структурам интегральной микроэлектроники, в частности к интегральным ячейкам статической памяти и оперативным запоминающим устройствам БИС и ЭВМ. Техническим результатом является микромощный режим потребления статических мощностей (единицы-десятки нановатт), приемлемая помехоустойчивость работы, высокие рабочие частоты. Изобретение содержит бистабильные ячейки лавинных транзисторов, управляющий р-МОП транзистор, битовую и словную шины, n-МОП транзистор считывания, генератор тока. 2 с.п.ф-лы, 8 ил.

| SAKUI К., HASEGAWA Т | |||

| et al., A New Static Memory Cell Based on the Reverse Base Current Effect of Bipolar Transistors, IEEE Trans, 1989, v.ED-36, р.1215-1217 | |||

| Сверхбыстродействующие интегральные микросхемы оперативных запоминающих устройств/Под ред | |||

| ВЕРНЕРА В.Д | |||

| - М.: Радио и связь, 1991, с.91-93 | |||

| US 5324961 А, 28.06.1994 | |||

| DE 4121445 A1, 23.01.1992 | |||

| DE 4209364 A1, 22.10.1992 | |||

| Передвижная бетонорастворная установка | 1980 |

|

SU952614A2 |

| УСТРОЙСТВО ДЛЯ СБОРА И ПЕРЕДАЧИ ИНФОРМАЦИИ О ПАРАМЕТРАХ КОНТРОЛИРУЕМОГОИЗДЕЛИЯ | 1972 |

|

SU435457A1 |

Авторы

Даты

2003-03-10—Публикация

1999-10-29—Подача