Изобретение относится к устройствам импульсной и цифровой техники, в частпости к логическим элементам ЭВМ.

Известен двухъярусный логический элемент, в котором для создания логических функций И-ИЛИ/И-ИЛИ-НЕ прямой и инверсный выходы нижнего яруса соединены с соответствующими объединениями эмиттеров второго яруса 1.

Известен также логический элемент, содержащий генератор тока, переключатели тока в нижнем и верхнем ярусах, на входе переключателя тока нижнего яруса используются входные эмиттерные повторители, инверсный коллекторный выход переключателя тока нижнего яруса соединен с общей эмиттерной точкой переключателя тока верхнего яруса, а прямые коллекторные выходы переключателей тока объединены 2.

Недостатками известных устройств являются наличие двух опорных транзисторов и двух опорных напряжений, значительная величина напряжения питания вследствие последовательного включения ярусов, большая величина потребляемой мощности и невысокое быстродействие.

Цель изобретения - снижение потребляемой мощности и увеличения быстродействия логического элемента И-ИЛИ/И- ИЛИ-НЕ.

Для достижения поставлеииой цели в устройство, содержащее переключатели тока и входные эмиттерные повторители на транзисторах п-р-п-типа, эмиттеры транзисторов переключателя тока верхнего яруса подключены к коллектору транзистора переключателя тока нижнего яруса, эмиттеры транзисторов которого подключены к источнику тока, введен эмиттерный повторитель

на транзисторе р-п-р-типа, вход которого соединен с эмиттерами транзисторо входных эмиттерных повторителей, а выход - с базой транзистора нижнего яруса, причем опорные транзисторы обоих ярусов выполйены в виде многоэмиттерного транзистора, база которого подключена к источнику опорного напряжения.

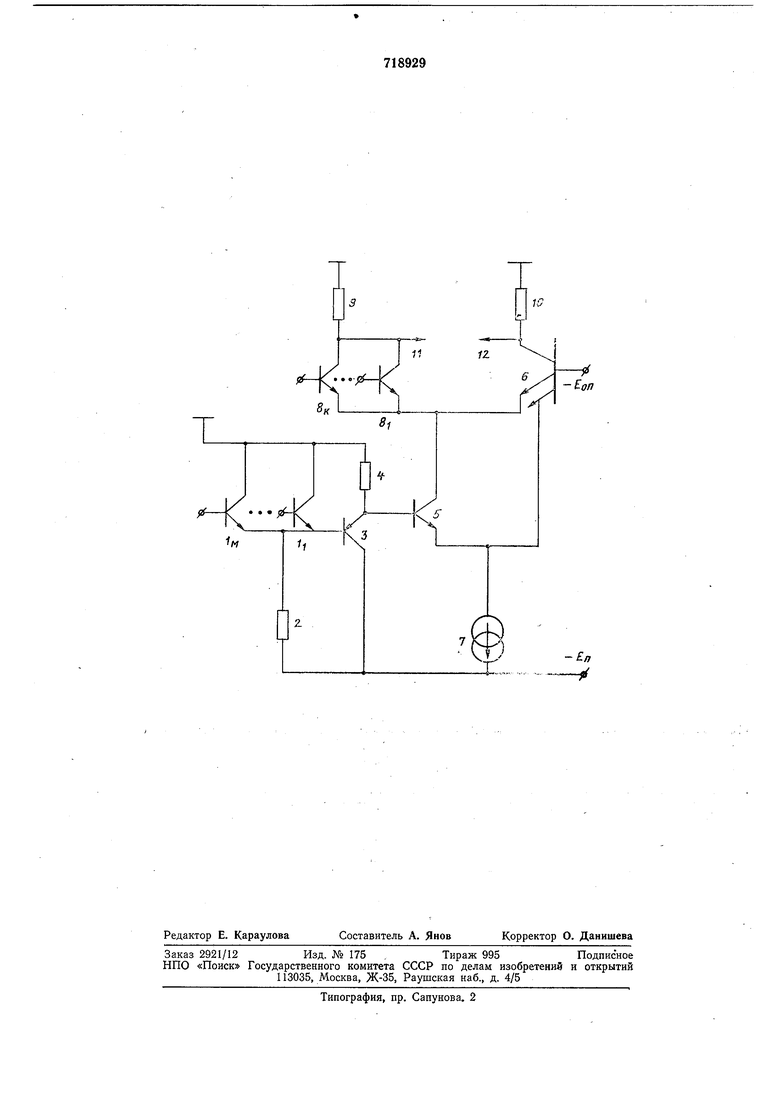

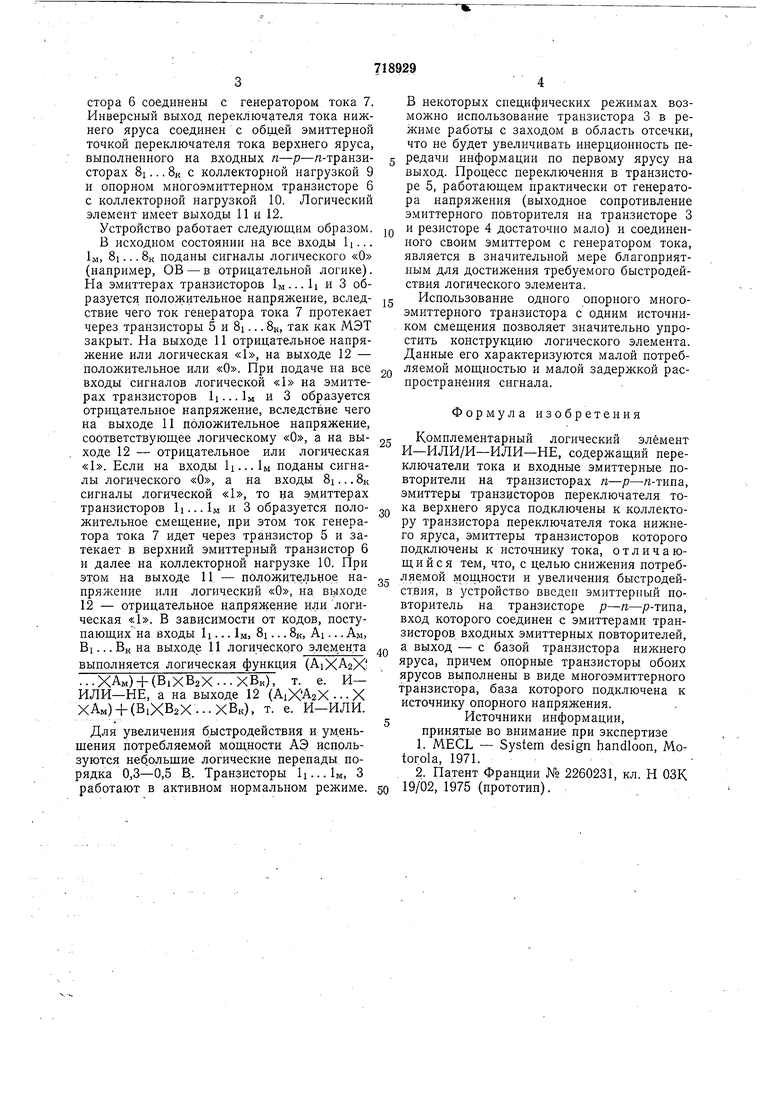

На чертеже приведена схема комплементарного логического элемента И-ИЛИ/И-

ИЛИ-НЕ. На входе нижнего яруса использовано М параллельно включенных входных эмиттерных повторителей li... IM на п р-п-траизисторах с нагрузочным резистором 2, выход которых соединен с базой

эмиттерного повторителя на р-п-р-транзисторе 3 с эмиттерной нагрузкой 4, эмиттер которого соединен с базой входного п-р-«-транзистора 5 переключателя тока нижнего яруса. Эмиттеры транзистора 5

опорного п-р-л-многоэмиттерного транзистора 6 соединены с генератором тока 7. Инверсный выход переключателя тока нижнего яруса соединен с общей эмнттерной точкой переключателя тока верхнего яруса, выполненного на входных п-р-п-транзисторах 8i...8к с коллекторной нагрузкой 9 и опорном многоэмиттерном транзисторе 6 с коллекторной нагрузкой 10. Логический элемент имеет выходы 11 и 12. Устройство работает следующим образом. В исходном состоянии па все входы li... 1ы, 8i... SK поданы сигналы логического «О (например, ОВ - в отрицательной логике). На эмиттерах транзисторов 1м... li и 3 образуется положительное напряжение, вследствие чего ток геператора тока 7 протекает через транзисторы 5 и 8i... 8к, так как МЭТ закрыт. На выходе 11 отрицательное напряжение или логическая «1, на выходе 12 - положительное или «О. При подаче иа все входы сигналов логической «1 на эмиттерах транзисторов h... 1м и 3 образуется отрицательное напряжение, вследствие чего на выходе 11 положительное напряжение, соответствующее логическому «О, а на выходе 12 - отрицательное или логическая «1. Если на входы II...IM поданы сигналы логического «О, а на входы 8i... 8к сигналы логической «1, то на эмиттерах транзисторов II...IM и 3 образуется положительное смещение, при этом ток генератора тока 7 идет через транзистор 5 и затекает в верхний эмиттерный транзистор 6 и далее на коллекторной нагрузке 10. При этом на выходе 11 - положительное напряжение или логический «О, на вь1ходе 12 - отрицательное напряжение цли логическая «1. В зависимости от кодов, поступающих на входы li... 1м, 8i... 8к, AI .. .AM, BI ... BK на выходе 11 логического элемента выполняется логическая функция (AiXA2X ...ХАм)4-(В1ХВ2Х...ХВ„), т. е. И- ИЛИ-НЕ, а на выходе 12 (AiXA2X ... X ХАм) + (В1ХВ2Х...ХВк), т. е. И-ИЛИ.

Для увеличения бьютродействия и уменьшения потребляемой мощности АЭ используются небольшие логические перепады порядка 0,3-0,5 В;. Транзисторы II...IM, 3 работают в активном нормальном режиме.

В некоторых специфических режимах возможно использование транзистора 3 в режиме работы с заходом в область отсечки, что не будет увеличивать инерционность передачи информации по первому ярусу на выход. Процесс переключения в транзисторе 5, работающем практически от генератора напряжения (выходное сонротивление эмнттерного повторителя на транзисторе 3

и резисторе 4 достаточно мало) и соединенного своим эмиттером с генератором тока, является в значительной мере благоприятным для достижения требуемого быстродействия логического элемента.

Использование одного опорного многоэмиттерного транзистора с одним источником смещения позволяет значительно упростить конструкцию логического элемента. Данные его характеризуются малой потребляемой мощностью и малой задержкой распространения сигнала.

Формула изобретения

Комплементарный логический элемент И-ИЛИ/И-ИЛИ-НЕ, содержащий переключатели тока и входные эмиттерные повторители на транзисторах п-р-п-типа, эмиттеры транзисторов переключателя тока верхнего яруса подключены к коллектору транзистора переключателя тока нижнего яруса, эмиттеры транзисторов которого подключены к источнику тока, отличающийся тем, что, с целью снижения нотребляемой мощности и увеличения быстродействия, в устройство введен эмиттерный повторитель на транзисторе р-п-р-тнпа, вход которого соединен с эмиттерами транзисторов входных эмиттерных повторителей,

а вь1ход - с базой транзистора нижнего яруса, причем опорные транзисторы обоих ярусов выполнены в виде многоэмиттерного транзистора, баз.а которого подключена к источнику опорного напряжения, Источники информации,

принятые во внимание при экспертизе

1.M.ECL - System design handloon. Motorola, 1971.

2.Патент Франции № 2260231, кл. Н ОЗК 19/02, 1975 (прототип).

M

ii

| название | год | авторы | номер документа |

|---|---|---|---|

| Быстродействующий микромощный логический элемент и-или/и-или-не | 1977 |

|

SU624369A1 |

| Быстродействующий помехоустойчивыйлОгичЕСКий элЕМЕНТ и-или/ и-или-HE | 1978 |

|

SU849488A1 |

| ФОРМАЛЬНЫЙ НЕЙРОН | 1973 |

|

SU375792A1 |

| Элемент для согласования насыщенных и ненасыщенных логических схем | 1972 |

|

SU438119A1 |

| Троичный логический элемент | 1974 |

|

SU516195A1 |

| Логический элемент | 1983 |

|

SU1166296A1 |

| RS-триггер | 1989 |

|

SU1626341A1 |

| Логический элемент и-или-и/и-или-и-не | 1980 |

|

SU907805A1 |

| Микромощный логический элементи-или/и-или-HE | 1979 |

|

SU832725A1 |

| Устройство для сравнения напряжений | 1976 |

|

SU657406A1 |

Авторы

Даты

1980-02-29—Публикация

1978-04-24—Подача