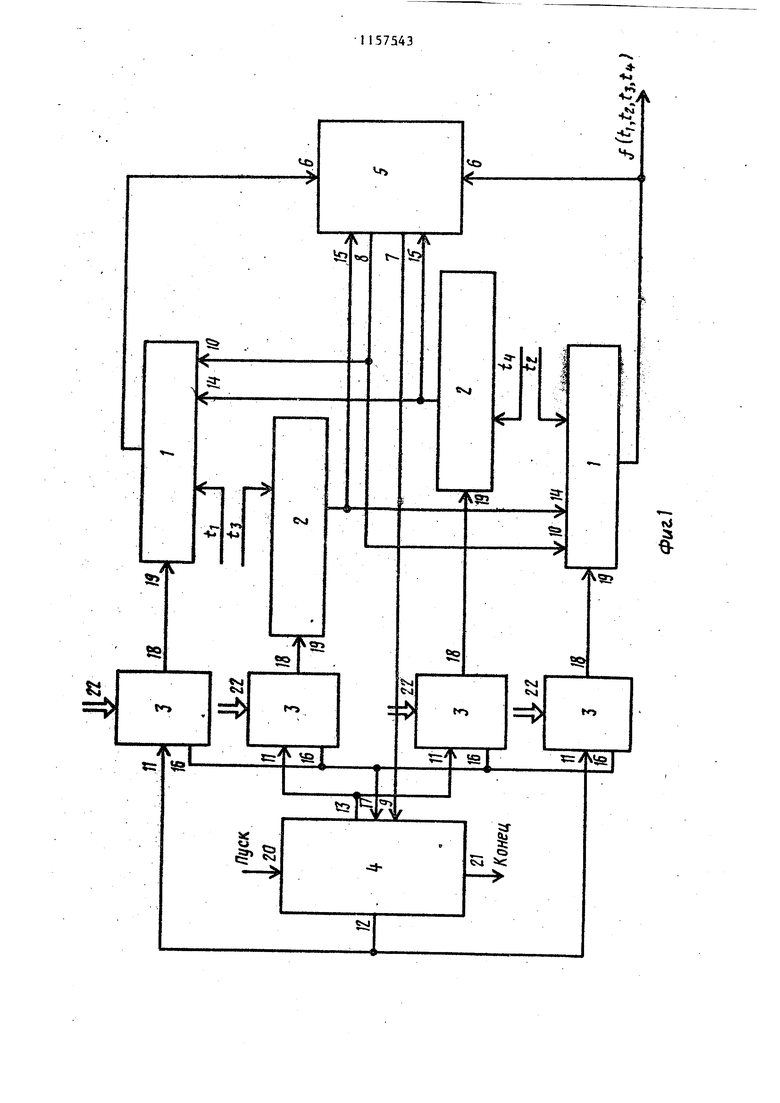

го тригтера, вход установки в О которого соединен с входом пуска преобразователя и через третий элемент задержки с первым входом т ретьего .триггера, вход установки в О которого соединен с входом пуска преобразователя и через третий элемент задержки с первым входом третьего элемента И, второй вход которого соединен с выходом генератора импульсов, прямые выходы второго и третьего триггеров соединены соответственно с вторым и третьим входами пятого и первого элементов И, инверсный выход третьего триггера соединен с вторьш входом четвертого элемента И, вход установки в О второго триггера соединен с выходом второго элемента ИЛИ, второй вход которого соединен через дешифратор нуля с выходом вычитающего счетчика, вход которого соединен с выходом пятого элемента И и входом четвертого элемента задержки, выходы первого, второго и четвертого элементов И соединены с управляющими входами второго и третьего формирователей операндов, выходы первого, второго, четвертого и пятого элементов И соединены с управляющими входами первого и четвертого формирователей импульсов, второй вход второго элемента ИЛИ соединен с вторым выходом блока анализа,

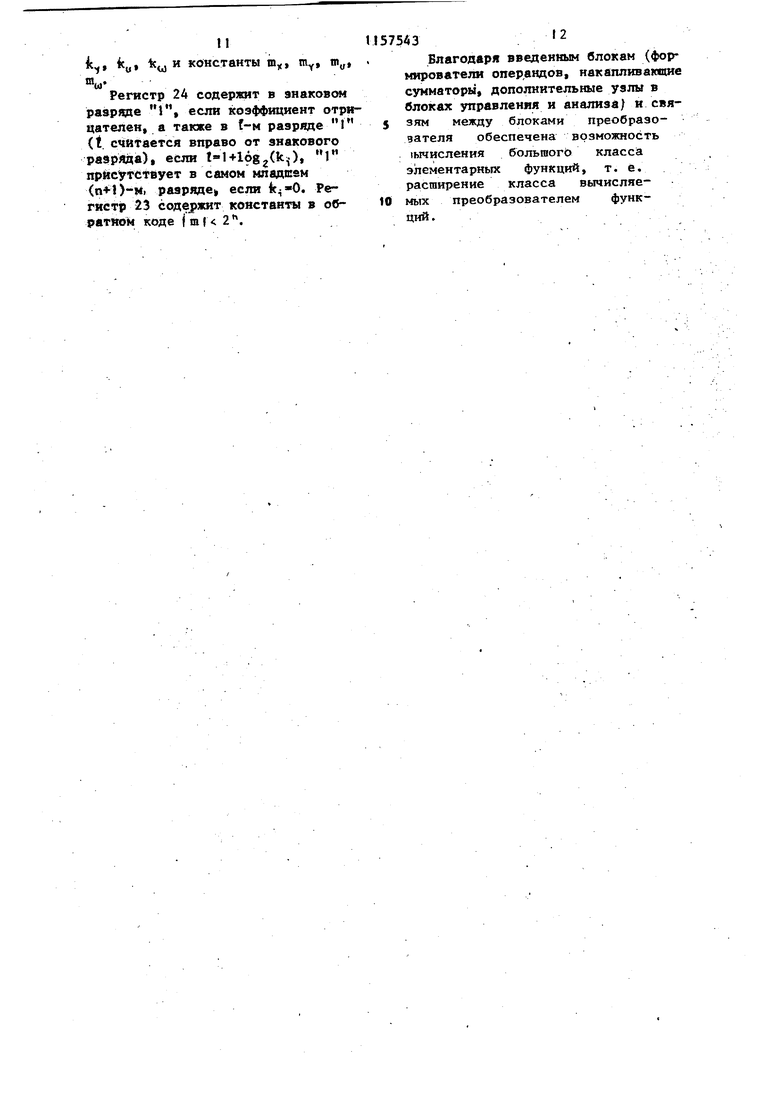

2. Преобразователь по п.. 1, о т л и ч а ющ и и с я тем, что каждый формирователь операндов содержит триггерj три элемента И, регистр сдвига, схему сравнения, группу элементов И и коэффициента и константы, входы которых соединены с информационным входом формирователя, вьЬсоды разрядов, начиная с второго регистра коэффициента, соединены с первым входом схемы сравнения, второй вход и выход которой содинены соответственно с выходом регистра сдвига и входом установки в 1 триггера, инверсный которого соединен с первым входом первог элемента И, выход которого подключен к входу регистра сдвига, выход младшего и второго разрядов регистра коэффициента соединены соответственно с первым и вторым входами второго и первого элементов И, выход знака регистра коэф идаента соединен с первым и BTopbW входами соответственно третьего и второго элементов И, выходы разрядов регистра констаит соединены первыми входами элементов И группы, вторые входы которых соединены с управляющим входом преобразователя, к которому подключены вторые входы первого и третьего и /ретий вход второго элементов И, выходы элементов И с первого по третий и выходы элементов И соединены с первьм выходом формирователя, инверсный выход триггера соединен с вторым выходом формирователя,

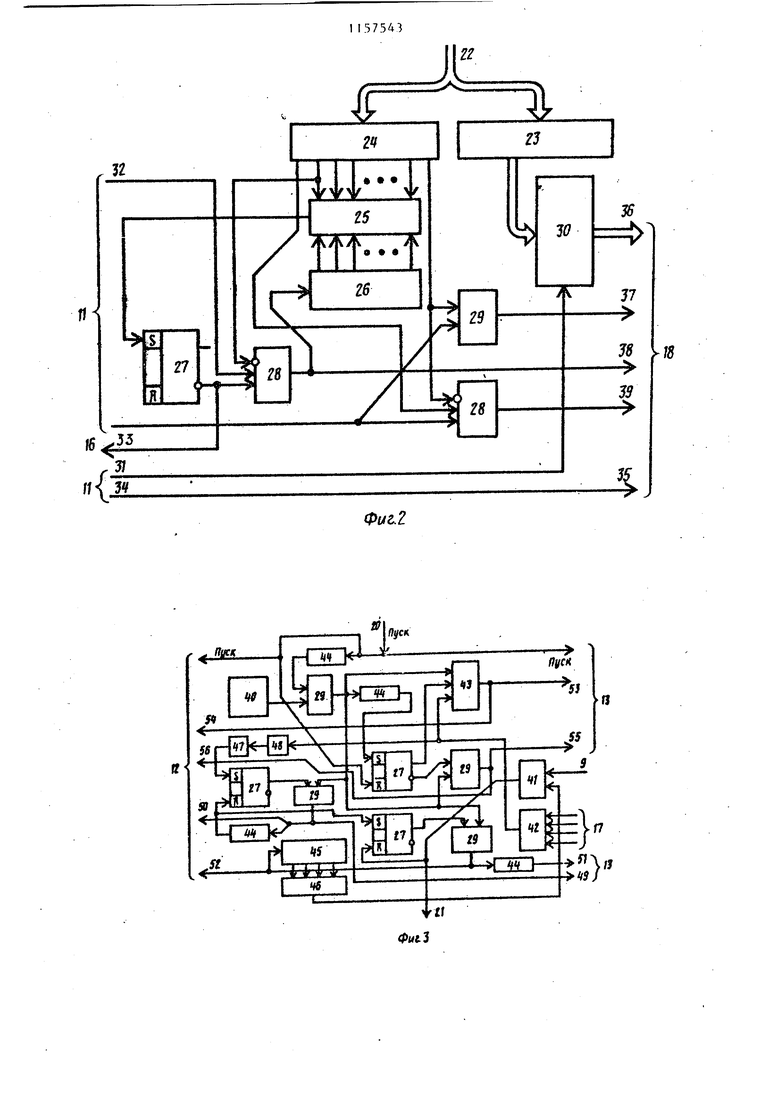

3. Преобразователь по п, 1, о т л и ч. а ю щ и и с. я тем, что блок анализа содержит схему сравнения, сумматор, два сумматора по модулю два, элемент ИЛИ и элемент НЕ,-первый и второй .выходы схемы сравнения соединены соответственно с входом элемента НЕ и первым входом первого сумматора по модулю два, второй вход и ВЫХ9Д которого соединены соответственно с выходом элемента ШШ и первым входом второго сумматора по модулю два, второй вход и выход которого соединены соответственно с выходе знака сумматора и первым выходом блока, второй выход которого соединен с выходом Элемента НЕ, пер вый и второй входы схемы сравнения соединены с первым и вторым информационнь1ми входами блока, знаковые разряды которых подключены к входам элемента ИЛИ, третий и четвертый информационные входы блока соединены с первьи и вторым входами сумма.тора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой функциональный преобразователь | 1984 |

|

SU1188750A1 |

| Устройство для вычисления функции @ ( @ - @ )/( @ + @ ) | 1982 |

|

SU1076911A1 |

| Устройство для извлечения квадратного корня | 1985 |

|

SU1259257A1 |

| Цифровой функциональный преобразователь | 1986 |

|

SU1339554A1 |

| Устройство для вычисления @ | 1983 |

|

SU1156067A1 |

| Цифровой функциональный преобразователь | 1980 |

|

SU926666A2 |

| Функциональный преобразователь | 1983 |

|

SU1136154A1 |

| Цифровой функциональный преобразователь (варианты) | 1981 |

|

SU1015375A1 |

| Конвейерное устройство для вычисления гиперболических функций | 1981 |

|

SU1026141A1 |

| Устройство для вычисления функции ( @ - @ )/ @ | 1982 |

|

SU1076912A1 |

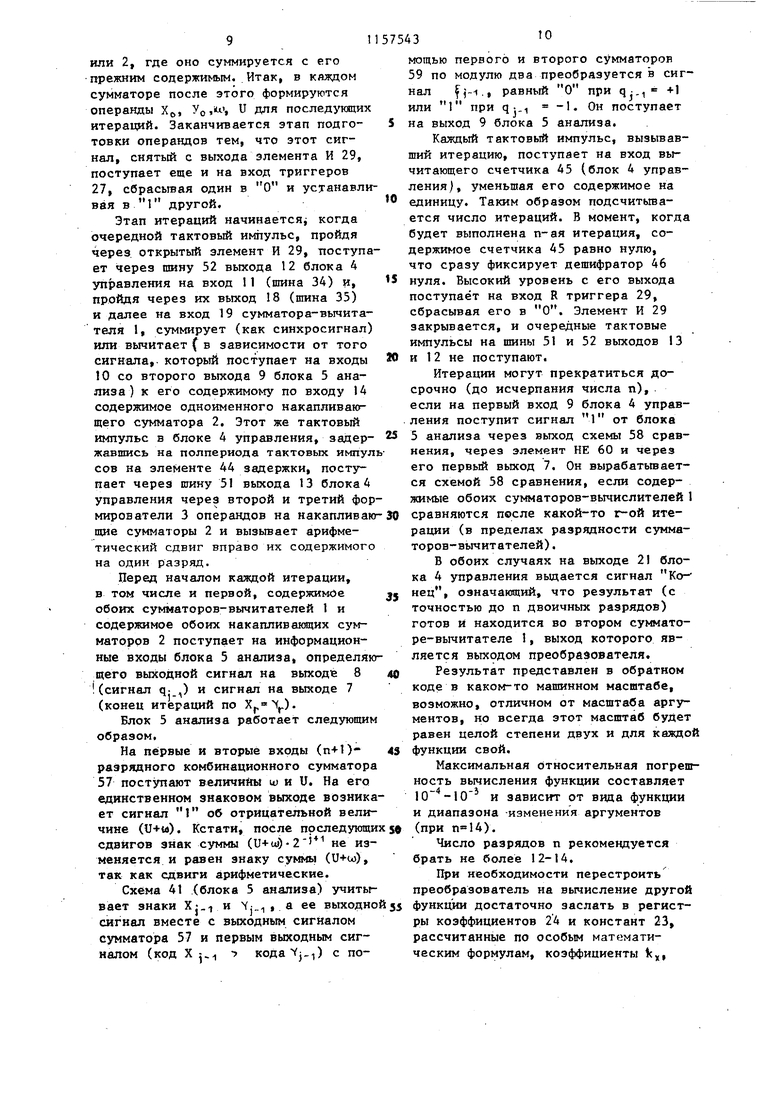

1. функциональный преобразователь, содержащий первый и второй сумматоры-вычитатели, блок аиалиэа и блок управления, выходы первого и второго сумматоров-вычитателей соединены с первым и вторым соответственно входами блока анализа, первый выход которого соединен с управляющими входами сумматоров-вычитателей, входы установки которых соединены с входом начальной установки преобразователя, выход ;второго сумматора-вычитателя соединен с выходом преобразователя, отличающийся тем, что, с целью расши1рения класса решаемых задач за счет возможности вычисления функций от нескольких переменных и возможности перенастра шания коэффициентов, в него введеныдва накапливающих сумматора и четыре формирователя операндов, информационные входы которых соединены с входом задания коэффициентов преобразователя, первые выходы формирователей операндов с первого по четвертый соединены с первыми информационными входами соответственно первого сумматора-вычитателя, первого и второго накапливающих сумматоров .и второго сумматора-вычитателя, второй информационный вход которого соединен с выходом первого накапливающего сумматора и третьим входом блока анализа, четвертый вход которого соединен с выходом второго накапливающего сумматора и вторым информационнь входом первого сумматор а- вычита теля, вторые информационные входы накапливающих сумматоров соединены с входом начальной установки преобразователя, причем блок управления содержит генератор импульсов, пять элементов И, два (Л элемента ИЛИ, четыре элемента задержки, три триггера, вычитающий счетчик, дещифратор нуля, формирователь импульсов и элемент НЕ, выходы формирователей операндов соединены с входами первого элемента ИЛИ, выход которого соединен с первым вхоел дом первого элемента И и через по-vj следовательно соединенные элемент НЕ ел и формирователь импульсов с входом установки в I первого триггера, 4 вход установки которого соедиСО нен с входом установки в 1 второго триггера.и через первый элемент задержки с выходом второго элемента И, первый вход которого соединен с выходом первого триггера, второй вход второго элемента И соединен с выходом третьего элемента И, вторым входом первого элемента И, первыми входами четвертого и пятого элементов И и через второй элемент задержки с входом установки в 1 третье

. 1 Изобретение относится к автоматике и вьгчислительной технике и предназначено для вычисления функций

от одного или нескольких аргументов, .представленных, как и сами значения функщ1й, в цифровом двоичном коде. Известен функциональный преобразователь, содержащий блок памяти, депшфратор генератор импульсов, двигатели, сумматоры, регистры flJ. Однако это устройство не позволяет производить перенастройку для вычисления различных функций Наиболее близким по технической сущности к предлагаемому является цифровой функциональный преобразователь, позволяющий вычислять частное от деления суммы квадратов двух аргументов на сумму этих аргументов и содержащий первые и вторые сумматоры-вычитатели и регистры сдви га, блок управления и блок анализа. .Причем выходы регистров соединены с информационным входом одноименньлс сумматоров-вычитателей, выходы которых связаны с входами блока анализа. Его первый и второй выходы при соединены к первому входу блока управления и к управлянхцим входам сумматоров-вычитателей соответственно. Входы преобразователя связаны с вхо дами занесения сумматоров-вычитателе и регистров сдвига. Выходом преобразов.ателя является выход одного иэ сумматоров-вычитателей L2. Недостатком известного преобразователя является узкий класс решаемых задач. Целью изобретения является расширение класса решаемых задач за счет возможности вычисления функции от нескольких переменных и возможности перенастраивания коэффициентов. Поставленная цель достигается тем что в цифровой функциональный преобразователь, содержащий первый и второй суьматоры-вычитатели, блок анализа и блок управления, выходы первого и второго сумматоров-вьмитателей соединены с первым и вторым соответственно входами блока анализ первый выход которого соединен с управляющими входами сумматоров-вычита телей, входы установки которых соеди нены с входом начальной установки преобразователя, выход второго сумматора-вычитателя соединен с выходом преобразователя, дополнительно введе ны два накапливающих сумматора и четыре формирователя операндов, информационные входы которых соединены с входом задания коэффициентов преоб разователя, первые выходы формирователей операндов с первого по четвер34 тый соединены с первыми информационньми входами соответственно первого сумматора-вычитателя, первого и второго накапливающих сумматоров и второго сумматора-вычитателя, второй информационный вход которого соединен с выходом первого накапливающего сумматора и-третьим входом блока анализа, четвертый вход которого соединен с выходом второго накапливаю Г(его суьгматора и вторым информационным входом первого сумматора-вычитателя, вторые информационные входы накапливающих сумматоров соединены с входом начальной УСТАНОВКИ преобразователя, причем блок управления содержит генератор импульсов., пять элементов И, два элемента ИЛ, четыре элемента задержки, три триггера, вычитающий счетчик, дешифратор нуля, формирователь импульсов и элемент НЕ, выходы формирователей операндов соединены с входами первого элемента ИГМ, выход которого соединен с первым входом первого элемента И и через последовательно соединенные элемент НЕ и формирователь импульсов с входом установки в I первого триггера, вход установки в О которого соединен с входом установки в 1 второго триггера и через первый элемент задержки с выходом второго элемента И, первый вход которого соединен с выходом первого триггера, второй вход второго элемента И соединен с вьпсодом третьего элемента И, вторым входом первого элемента И, первыми входами четвертого и пятого элементов И и через второй элемент задержки с входом установки в 1 третьего триггера, вход установки в О которого соединен с входом пуска преобразователя и через третий элемент задержки с первым входом третьего триггера, вход установки в О которого соединен с входом пуска преобразователя и через третий элемент задержки с первым входом третьего элемента И, второй вход которого соединен с В1|1ходом генератора импульсов, прямые выходы второго и третьего триггеров соединены соответственно с вторым и третьим входами пятого и первого элементов И, инверсный выход третьего триггера соединен с вторым входом четвертого элемента И, вход установки в О второго триггера соединен с выходом 51 Btoporo элемента ИЛИ, второй вход которого соединен через дешифратор нуля с выходом вычитающего счетчика, 1вход которого соединен с выходом . пятого элемента И и входом четвертого элемента задержки, выходы перво го, второго и четвертого элемелтов И соединены с управляющими входами вто рого и третьего формирователей операндов, выходы первого, второго, четвертого и пятого эленентов И соединены с управляющими входами первого и четвертого формирователей импульсов, второй вход второго элемента ИЛИ соединен с вторым входом блока анализа. Причем каждый формирователь операндов содержит Триггер, три элемента И, регистр сдвига, схему сравнения, группу элементов И и регистры коэффициента и константы, входы которых соединены с информационным входом формирователя, выходы разрядов, начиная с второго регистра коэффициента, I соединены с первым входом схемы сравнения, второй вход и выход которой, соединены соответственно с выходом регистра сдвига и входом установки в I триггера, инверсный выход которого соединен с первым входом первого элемента И, выход которого подключен к входу регистра сдвиг aj вьпсод младшего и второго разрядов регистра коэффициента соединены соответственно с первым и вторым входамм второго и первого элементов И, выход знака регистра коэффициент,а соединен с первым и вторый вход и соответственно третье го и второго элементов И, выходы раз рядов региетра констант соединены с первыми вкодами элементов И группы, вторые входы которых соединены с управляющим входом преобразователя, к которому п дклкте-ны вторые входы первого и третьего и третий вход вто рого элемёйтов И, выходы элементов И с первого ijp третий и вадходы группы элементов, И соединены с первым выходом 4|Оркирователя, инверсный выход триггера соединен с вторым выходом формирователя При этом блок анализа содержи- - схему сравнения, сумматор, два сумматора по модулю два элемент ИЛИ и эле1.ент НЕ, первь1й и второй выходы схемы сравнения соединены соответственно с входом элемента НЕ и пер3вым входом первого сумматора по моулю два, .второй вход и выход котоого соединены соответственно с выходом элемента ИЛИ и первым входом второго сумматора по модулю два, второй вход и выход которого соединены соответственно с выходом знака сумматора и первым выходом блока,. i второй выход которого соединен с вь ходом элемента HF,, первый и второй входы схемы сравнения соединены с первым и вторым информационными входами блока, знаковые разряды которых подключены к входам элемента ИЛИ, третий и четвертый информациоиm ie входы блока соединены с первым и вторым вхо;;ами сумматора. На фиг. 1 представл1вна блок-схема преобразователя; на фиг. 2-4 - блоксхемы соответственно формирователя операндов, блока управления и блока анализа. Цифровой функциональный преобразователь содержит сумматоры-вычитатели 1, накапливающие сумматоры 2, формирователи 3 операндов, блока 4 управления, блок 5 анализа, входы б и выходы 7 и 8 блока анализа, входы и выходы 9-22 сумматордв вычитателей, формирователей оперв1Щов и блока управления. Формирователи операндов содержат регистры 23 и 24 соответственно констаиты и коэффициента, схему 25 совпадения, регистр 26 сдвига, триггер 27, элементы И 28 и 29, группу элемёйтов И 30, выход 3f, входы 32-34 формирователей, выходы 35-39 формирователей. Блок управления содержит генератор 40 импульсов« элементы ШШ 41 и 42, элемент И 43, элементы.44 задержки, вычитагаций счетчик 45, дешифратор 46 нуля, формирователь 47 импульсов, элемент НЕ 48, выходы блока . Блок анализа содержит сумматор 57, схему 58 сравнения, сз мматоры 59 по модулю дв а и элемент НЕ 60, . Работа преобразователя осиована на итерационном алгорип ю и ряде вспомогательньсс соотношений () ) i VVrVi- v- . f()V . где , 2,..., n - номер итерации; разрядность аргументов, исключая знак;

г номер итерации ( - I), для которой Xf. Y в пределах сетки, или номер последней итерации

.Ло :,-,-, ,,

ц , , , Vj - коэффициенты, равные целым- (от О до ) степеням 1/2, взятым со знаком плюс или минус, или нулю; ffljj, ш, т,, Ищ- константы по модулю

меньшие 2

11(, S,) - аргументы или аргумент вычисляемой функдаи;

t -.вектор аргументов размерностью S(U )

i+1, если Z О -1, если Z О - функция знака стоп, если

Преобразователь работает следукг щим образом.

По сигналу Пуск, поступающему на вход 20 блока 4 управления, а из далее во все узлы преобразователя (не показаны), выполняются подготовительные операции: в элементы 1-4 заносятся аргументы t; (через входы 22); триггеры 27 в блоке 4 управления и формирователях 3 операндов устанавливаются в регистры 26 сдвига формирователей 3 операндов сбрасьшаются в О, а в их старший разряд заносится в вычитающий счетчик 45 заносится константап по входу 22 формирователя 3 операндов в регистры 24 и 23 заносятся коэффихщенты k и константы т (если изменяется вид вьтчисляемой функции).

Сигнал Пуск (потенциальный), поступающий на вход 20, задержавшись на линии 44 задержки на время вьтолг нения подготовительных операций, поступает на вход элемента И 29, отк)рывая его. Очередной тактовый импульс от генератора 40 поступает на шины 55 и 56 вьшодов 13 и 12 блока 4 управления, откуда оч передается во все формирователи 3 операндов (через пашу 33). Если в младшем разряде регистра 24 коэффициентов присутствует 1 (значит 0), то с помощью элекгнта И 29 вырабатывается сигнал (по шине 37) на сброс содержимого сумматора 1 или 2. Если 1 нет, а в

старшем разряде I (знак -), то с помощью элемента И 28 вырабатывается сигнал (по шине 39) на образование обратного кода от содержимого сумматоров 1 или 2. Спустя некоторое время, через элемент 44 задержки этот же первый тактовый импульс устанавливает триггер 27 в 1, закрывает элемент И 29 и открывает элемент И 43 при условии, что по входу 17 блока 4 управления через свои выходы 16 хотя бы один формирователь 3 операндов подает высокий сигнал I (о необходимости сдвига содержи юго сумматоров 1 и 2, если ic +}),

При этом условю второй и, возможно, последующие тактовые импульсы проходят через элемент 43 и по пшнам 53 и 54 (выход 13 и 12) передаются в формирователь 3 операндов (по шине 32 входа 11), где через открытые элементы И 28 поступают по шине 38 на сумматор 1 или 2 и вызывают арифметический сдвиг его содержимого на один разряд вправо.- Этим же сигналом в формирователе 3 операнд дов сдвигается вправо содержимое регистра 26 сдвига. В момент совпадения положения единицы в регистрах 24 и 26 схема совпадения пооолает сигнал на вход триггера 27, с инверсного выхода которого снимается сигнал (низкого уровня), запрещающий дальнейшие сдвиги сумматора 1 иАи 2, управляемого от

данного формирователя 3 операндов. Одновременно этот же сигнал О подается через выход 16 на вход 17 блока 4 управления.

В момент, когда от всех четырех формирователей 3, операндов поступают сигналы О, элемент ИЛИ 42 закрывает элемент И 43 и операции сдвигов (умножения k.-t.) на этом заканчивается.

Одновременно сигнал О элемента ИЛИ 42 поступает через элемент НЕ58 и формирователь 47 на вход триггера 27, устанавливая его в 1, С его прямого выхода снимается сигнал, открьшакяций элемент И 29. Очередной тактовый импульс, пройця через нее, поступает по шинам 49 и 50 выходов 13 и 12 блока 4 управления во все формирователи 3 операндов по шине 31 (входа 11) и, oткpывaя( )-разрядную группу 30 элементов И, заносит содержимое регистра 23 константы т. через шины 36 выхода 18 в су матор -1 или 2, где оно суммируется с его прежним содержимым,.Итак, в каждом сумматоре после этого формируются операнды Х,, УО А . U Для последугацих итераций. Заканчивается этап подготовки операндов тем, что этот сигнал, снятый с выхода элемента И 29, поступает еще и на вход триггеров 27, сбрасьгоая один в О и устанавли вая в 1 другой. Этап итераций начинается когда очередной тактовый импульс, пройдя через, открытый элемент И 29, поступа ет через шину 52 выхода 12 блока 4 управления на вход 11 (шина 34) и, пройдя через их выход 18 (пшна 35) и далее на вход 19 сумматора-вычитателя I, суммирует (как синхросигнал) или вычитает ( в зависимости от того сигнала, который поступает на входы 0 со второго выхода 9 блока 5 анализа) к его содержимому по входу 14 содержимое одноименного накапливающего сумматора 2. Этот же тактовый импульс в блоке 4 управления, задержавшись на полпериода тактовых импул сов на элементе 44 задержки, поступает через шину 51 выхода 13 блока 4 управления через второй и третий фор мирователи 3 операндов на накапливаю щие сумматоры 2 и вызьгоает арифметический сдвиг вправо их содержимого на один разряд. Перед началом каждой итерации, в том числе и первой, содержимое обоих сумматоров-вычитателей 1 и содержимое обоих накапливакяцих сумматоров 2 поступает на информационные входы блока 5 анализа, определяю щего выходной сигнал на выходе 8 (сигнал Ч: ,) и сигнал на выходе 7 (конец итераций по Х). Блок 5 анализа работает следующим образом. На первые и вторые входы ()разрядного комбинационного сумматор 57 поступают величины w и U, На его единственном знаковом выходе возник ет сигнал 1 об отрицательной вели чине (и+«). Кстати, после последующихs сдвигов знак суммы (U+w) не изменяется и равен знаку суммь1 (U+w), так как сдвиги арифметические. Схема 41 (блока 5 анализа) учиты J-T .. 4j , а ее выходной35 вает знаки X и сигнал вместе с выходным сигналом сумматора 57 и первым выходным сигналом (код X j ) с помощью первого и второго сумматоров 59 по модулю два преобразуется в сигнал fi-L, равный О при Я;-1 ° или 1 при q. 1 -1. Он поступает на выход 9 блока 5 анализа. Каждый тактовый импульс, вызывавший итерацию, поступает на вход вычитающего счетчика 45 (блок 4 управления), уменьшая его содержимое на единицу. Таким образом подсчитьгоается число итераций. В момент, когда будет выполнена п-ая итерация, содержимое счетчика 45 равно нулю, что сразу фиксирует дешифратор 46 нуля. Высокий уровень с его выхода поступает на вход R триггера 29, сбрасывая его в О. Элемент И 29 закрывается, и очередные тактовые импульсы на шины 51 и 52 выходов 13 и 12 не поступают. Итерации могут прекратиться досрочно (до исчерпания числа п), если на первый вход 9 блока 4 управления поступит сигнал 1 от блока 5 анализа через выход схемы 58 сравнения, через элемент НЕ 60 и через его первый выход 7. Он вырабатьгаается схемой 58 сравнения, если содержимые обоих сумматоров-вычислителей 1 сравняются после какой-то г-ой итерации (в пределах разрядности сумматоров-вычитателей). В обоих случаях на выходе 21 блока 4 управления вьздается сигнал Конец, означающий, что результат (с точностью до п двоичных разрядов) готов И находится во втором сумматоре-вычитателе 1, выход которого является выходом преобразователя. Результат представлен в обратном коде в каком-то мащинном масштабе, возможно, отличном от масштаба аргументов, но всегда этот масштаб будет равен целой степени двух и для каждой функции свой. Максимальная относительная погрешность вычисления функции составляет 10 -10 и зависит от вида функции и диапазона изменения аргументов (при ). Число разрядов п рекомевдуется брать не более 12-14. При необходимости перестроить преобразователь на вычисление другой функции достаточно заслать в регистры коэффициентов 24 и констант 23, рассчитанные по особым матсматическим формулам, коэффициенты 1с,,

II

ц, fcy, w и константы ш, m, т„,

w

Регистр 24 содержит в знаков(ж

разряде Г% если коэффициент отрицателен, а также в f-н разряде I (t. считается вправо от знакового раарада), если t-l+log(k), i присутствует в самом младшем )-м, разряде если . Регистр 23 содержит константы в обратном коде jm| 2.

1575432

Благодаря введенным блокам (формирователи операндов, накапливакщие сумматоры, дополнительные узлы в блоках управления и анализа| и связям между блоками преобразозателя обеспечена возможность 1ычисления большого класса элементарных функций, т. е. расширение класса вычисляемых преобразователем функций.

J.t

Фиг.Ц

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Вычислитель тригонометрических функций | 1978 |

|

SU746538A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Цифровой функциональный преобразователь | 1976 |

|

SU744595A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-05-23—Публикация

1983-03-11—Подача