Изобретение относится к вычислительной технике и может быть использовано для решения задач теории массового обслуживания, в частности при принятии решений в условиях нечеткой исходной информации, а также для нечеткого логического вывода в экспертных системах.

Известно устройство для обработки нечеткой исходной информации (см. авторское свидетельство СССР 1688260, м. кл. G06F 15/36, БИ 40, 1991 г.), содержащее генератор тактовых импульсов, группу из А дешифраторов (где А - количество альтернативных вариантов), первую группу из А элементов ИЛИ, две группы из А элементов И, первую группу из А формирователей импульсов, первую группу из А триггеров и первую группу из А счетчиков импульсов, причем выход К-го триггера первой группы (К= 1,..., А) подключен к первому входу К-го элемента И первой группы, выход которого подключен к суммирующему входу К-го счетчика первой группы, вход установлен в "0" которого подключен ко входу начальной установки устройства, вторую группу из А триггеров, вторую группу из Р элементов ИЛИ (где Р - разрядность представления кодов источников сообщений), первую группу из N регистров (где N - количество источников сообщений), вторую группу из А регистров, первую группу из N блоков элементов И, вторую группу из А блоков элементов И, группу из N блоков сравнения, третью группу из N элементов И, третью группу из N триггеров, вторую и третью группы из А счетчиков импульсов, третью группу из А элементов ИЛИ, четвертую группу из А элементов И, группу из А элементов НЕ, вторую группу из А формирователей импульсов, пять элементов ИЛИ и элемент И, причем информационный вход устройства подключен к информационным входам всех дешифраторов, Т-й разряд информационного выхода К-го дешифратора (Т=1,...,Р) подключен к К-му разряду Т-го элемента ИЛИ второй группы и к Т-му разряду К-го элемента ИЛИ первой группы, выход которого подключен к первому входу К-го элемента И второй группы, выход которого подключен ко входу К-го формирователя импульсов первой группы, выход которого подключен ко входу установки в "1" К-го триггера первой группы и ко входу установки в "0" К-го триггера второй группы, выход которого подключен ко входу блокировки К-го дешифратора группы, М-й вход задания допустимого кода источника сообщений устройства подключен к установочному входу М-го регистра первой группы, информационный выход которого подключен к информационному входу М-го блока элементов И первой группы, выход которого подключен к первому информационному входу М-го блока сравнения, выход Т-го элемента ИЛИ второй группы подключен к Т-му разряду вторых информационных входов всех блоков сравнения группы, выход признака равенства М-го из которых подключен к М-му входу первого элемента ИЛИ и к первому входу М-го элемента И третьей группы, выход которого подключен ко входу установки в "0" М-го триггера третьей группы, выход которого подключен к управляющему входу М-го блока элементов И первой группы, К-й вход задания допустимого кода альтернативного варианта устройства подключен к установочному входу К-го регистра второй группы, информационный вход которого подключен к информационному входу К-го блока элементов И второй группы, информационный выход которого подключен к установочному входу К-го счетчика второй группы, информационный выход которого подключен к информационному входу К-го элемента ИЛИ третьей группы, выход которого подключен ко входу К-го элемента НЕ группы и к первому входу К-го элемента И четвертой группы, выход которого подключен к вычитающему входу К-го счетчика второй группы, выход К-го элемента НЕ группы подключен ко второму входу (К+1)-го элемента И четвертой группы и ко входу К-го формирователя импульсов второй группы, выход которого подключен к К-му входу второго элемента ИЛИ, выход которого подключен ко входам установки в "0" всех триггеров первой группы, выход К-го из которых подключен к К-му входу третьего элемента ИЛИ, выход которого подключен к первому входу элемента И, выход которого подключен к третьим входам всех элементов И четвертой группы и ко вторым входам всех элементов И первой группы, выход К-го из которых подключен к суммирующему входу К-го счетчика третьей группы, выход генератора тактовых импульсов подключен ко второму входу элемента И, выход первого элемента ИЛИ подключен ко вторым входам всех элементов И второй группы, вход начальной установки устройства подключен к первому входу четвертого элемента ИЛИ и ко входам установки в "0" всех регистров первой и второй групп и счетчиков второй группы, вход пуска устройства подключен ко второму входу четвертого элемента ИЛИ, выход которого подключен к первому входу пятого элемента ИЛИ, к (А+1)-му входу второго элемента ИЛИ, ко входам установки в "0" счетчиков третьей группы и ко входам установки в "1" всех триггеров третьей группы, выход А-го формирователя импульсов второй группы подключен ко вторым входам всех элементов И третьей группы и ко второму входу пятого элемента ИЛИ, выход которого подключен ко входам установки в "1" всех триггеров второй группы и к управляющим входам всех блоков элементов И второй группы. (Признаки, присущие предмету изобретения, перечислить).

Недостатки известного устройства - не способность обрабатывать аналоговую информацию, не исключается плюральный вотум, значительная аппаратурная избыточность и, как следствие, низкая надежность в работе, значительная энергоемкость.

Известно устройство для обработки нечеткой информации (см. патент РФ 2075247, М. кл. G 06 F 7/00, 6, 7, 1997 г.), содержащее блок параллельного определения наименьшего или наибольшего числа, блок формирования промежуточных результатов, блок последовательного сравнения с порогом, коммутатор данных текущей ситуации, блок определения адреса эталонной ситуации, блок микропрограммного управления, операционный блок, группа информационных выходов которого соединена с первой группой информационных входов блока параллельного определения наименьшего или наибольшего числа, первая группа информационных выходов которого соединена с первой группой информационных входов блока последовательного сравнения с порогом и группой информационных входов блока формирования промежуточных результатов, группа информационных выходов которого соединена с второй группой информационных входов коммутатора данных текущей ситуации, причем первый, второй и третий управляющие входы устройства соединены соответственно с первым, вторым и третьим управляющими входами блока микропрограммного управления, первый управляющий выход устройства соединен с первым управляющим выходом блока микропрограммного управления, второй управляющий выход которого соединен с вторым управляющим входом блока формирования промежуточных результатов, третий управляющий выход - с третьим управляющим входом блока формирования промежуточных результатов, пятый и шестой управляющие выходы - с третьим и четвертым управляющими входами блока последовательного сравнения с порогом соответственно, одиннадцатый и двенадцатый управляющие выходы - с пятым и шестым управляющими входами операционного блока соответственно, четырнадцатый управляющий выход - с управляющим входом коммутатора данных текущей ситуации и семнадцатый и восемнадцатый управляющие выходы - с вторым и третьим управляющими входами блока определения адреса эталонной ситуации соответственно, отличающиеся тем, что в него введены коммутатор выходных данных, коммутатор адреса, оперативный запоминающий блок данных и регистр команд, причем группа информационных входов-выходов устройства соединена с первой группой информационных входов операционного блока, информационными выходами блока последовательного сравнения с порогом, первой группой информационных входов коммутатора данных текущей ситуации, информационными выходами коммутатора выходных данных, информационными входами регистра команд и блока определения адреса эталонной ситуации, а также с информационными входами-выходами оперативного запоминающего блока данных, а группа информационных входов устройства - с второй группой информационных входов блока параллельного определения наименьшего или наибольшего числа, группа информационных выходов устройства соединена с второй группой информационных выходов блока параллельного определения наименьшего или наибольшего числа, группа адресных входов устройства соединена с первой группой информационных входов коммутатора адреса, четвертый управляющий вход устройства соединен с четвертым управляющим входом блока микропрограммного управления и первым управляющим входом коммутатора адреса, пятый управляющий вход устройства - с пятым управляющим входом блока микропрограммного управления, а шестой управляющий вход устройства - с первым управляющим входом блока формирования промежуточных результатов, второй и третий управляющие выходы устройства соединены соответственно с первым и вторым управляющими выходами блока формирования промежуточных результатов, четвертый управляющий выход устройства - с первым выходом регистра команд, который соединен также с первым управляющим входом блока параллельного определения наименьшего или наибольшего числа, группа информационных выходов операционного блока соединена с первой группой информационных входов коммутатора выходных данных, группа информационных выходов блока формирования промежуточных результатов - с второй группой информационных входов коммутатора выходных данных, группа информационных выходов коммутатора данных текущей ситуации соединена с второй группой информационных входов операционного блока, второй, третий, четвертый и пятый выходы регистра команд соединены соответственно с первым, вторым, третьим и четвертым управляющими входами операционного блока, а шестой, седьмой, восьмой и девятый выходы регистра команд - с второй группой информационных входов блока последовательного сравнения с порогом, десятый выход регистра команд соединен с первым управляющим входом блока последовательного сравнения с порогом, а одиннадцатый выход регистра команд - с первым управляющим входом блока определения адреса эталонной ситуации, группа адресных выходов которого соединена с второй группой информационных входов коммутатора адреса, управляющий выход блока определения адреса эталонной ситуации соединен с вторым управляющим входом коммутатора адреса, информационные выходы которого соединены с группой адресных входов оперативного запоминающегося блока данных, четвертый, седьмой, восьмой и девятый управляющие выходы блока микропрограммного управления соединены соответственно с вторым, пятым, шестым и седьмым управляющими входами блока последовательного сравнения с порогом, десятый управляющий выход блока микропрограммного управления - с вторым управляющим входом блока параллельного определения наименьшего или наибольшего числа, тринадцатый управляющий выход блока микропрограммного управления - с седьмым управляющим входом операционного блока, пятнадцатый и шестнадцатый управляющие выходы блока микропрограммного управления - с первым и вторым управляющими входами соответственно коммутатора выходных данных, девятнадцатый управляющий выход блока микропрограммного управления - с управляющим входом регистра команд, управляющие выходы с двадцатого по тридцатый блоков микропрограммного управления соединены с третьей группой информационных входов коммутатора адреса, тридцать первый управляющий выход блока микропрограммного управления соединен с третьим управляющим входом коммутатора адреса, а тридцать второй управляющий выход блока микропрограммного управления - с входом выборки оперативного запоминающего блока данных, тридцать третий управляющий выход блока микропрограммного управления - с входом управления записью/чтением оперативного запоминающего блока данных, причем операционный блок состоит из четырех однородных ячеек, объединенных по входам управления и имеющих параллельные входы и выходы, блок последовательного сравнения с порогом состоит из схемы сравнения, двух коммутаторов, трех регистров, двоичного счетчика, элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, элемента И и буферных элементов, причем первая группа информационных входов блока соединена с первой группой информационных входов схемы сравнения и младшими четырьмя разрядами первой группы информационных входов первого коммутатора, к старшему пятому разряду первой группы информационных входов первого коммутатора подключен вход логического ноля блока, вторая группа информационных входов блока соединена с младшими четырьмя разрядами первой группы информационных входов второго коммутатора, к пятому старшему разряду первой группы информационных входов второго коммутатора подключен вход логической единицы блока, первый управляющий вход блока соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй управляющий вход блока соединен со счетным входом двоичного счетчика, третий управляющий вход блока соединен с входом сброса двоичного счетчика, четвертый управляющий вход блока соединен с управляющим входом второго коммутатора, пятый управляющий вход блока соединен с входом разрешения записи первого регистра, шестой управляющий вход блока соединен с входом разрешения записи второго регистра и первым входом элемента И, седьмой управляющий вход блока соединен с входами управления буферных элементов, выход схемы сравнения соединен с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с управляющим входом первого коммутатора и инверсным вторым входом элемента И, информационные выходы второго коммутатора соединены с информационными входами первого регистра, выходы которого соединены с второй группой информационных входов первого коммутатора, младшие четыре разряда информационных выходов первого регистра соединены с второй группой информационных входов схемы сравнения, информационные выходы первого коммутатора соединены с информационными входами второго регистра, выходы которого соединены с второй группой информационных входов второго коммутатора и через буферные элементы подключены к младшим пяти разрядам группы информационных выходов блока, выход элемента И соединен с входом разрешения записи третьего регистра, выходы двоичного счетчика соединены с информационными входами третьего регистра, выходы третьего регистра через буферные элементы подключены к старшим одиннадцати разрядам группы информационных выходов блока, блок определения адреса эталонной ситуации состоит из двух шестиразрядных регистров, сумматора, шести элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, элемента ИЛИ, элемента НЕ, схемы сравнения, причем группа информационных входов блока соединена с информационными входами первого и второго регистров, первый управляющий вход блока соединен с третьим разрядом второй группы информационных входов схемы сравнения, второй и третий управляющие входы блока соединены с входами разрешения записи первого и второго регистров соответственно, выходы первого регистра соединены с первой группой информационных входов сумматора, к старшему седьмому разряду первой группы информационных входов сумматора подключен вход логического ноля блока, инверсные выходы второго регистра соединены с второй группой информационных входов сумматора, к старшему седьмому разряду второй группы информационных входов и входу переноса сумматора подключен вход логической единицы блока, выходы шести младших разрядов сумматора соединены с первыми входами с первого по шестой элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соответственно, выход старшего седьмого разряда сумматора соединен с вторыми входами с первого по шестой элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и входом элемента НЕ, выходы первого, второго, третьего и седьмого разрядов сумматора подключены к группе адресных выходов блока, выходы с первого по третий элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены с тремя младшими разрядами первой группы информационных входов схемы сравнения соответственно, выходы остальных элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены с входами элемента ИЛИ, выход которого соединен с четвертым старшим разрядом первой группы информационных входов схемы сравнения, выход элемента НЕ соединен с младшим первым разрядом второй группы информационных входов схемы сравнения, к второму разряду второй группы информационных входов схемы сравнения подключен вход логической единицы блока, к четвертому разряду второй группы информационных входов схемы сравнения подключен вход логического ноля блока, выход схемы сравнения подключен к управляющему выходу блока, блок параллельного определения наименьшего или наибольшего числа состоит из четырех однородных ячеек и буферного регистра, причем первая группа информационных входов блока соединена с первыми и вторыми группами информационных входов двух ячеек первого уровня, первый управляющий вход блока соединен с управляющими входами всех ячеек, выходы двух ячеек первого уровня соединены с информационными входами первой и второй групп ячейки второго уровня соответственно, выходы ячейки второго уровня соединены с информационными входами буферного регистра, второй управляющий вход блока соединен с входом разрешения записи буферного регистра, выходы буферного регистра соединены с второй группой информационных входов четвертой ячейки и второй группой информационных выходов блока, вторая группа информационных входов блока соединена с первой группой информационных входов четвертой ячейки, выходы которой подключены к первой группе информационных выходов блока, блок формирования промежуточных результатов состоит из четырех параллельных регистров и одного последовательного регистра, причем группа информационных входов блока соединена с информационными входами с первого по четвертый параллельных регистров, выходы которых подключены к информационным выходам блока, первый управляющий вход блока соединен с информационным входом последовательного регистра, второй управляющий вход блока соединен с входом разрешения записи и сдвига последовательного регистра, третий управляющий вход блока соединен с входом установки в "0" последовательного регистра, выход первого (младшего) разряда которого соединен с входом разрешения записи первого параллельного регистра, выход второго разряда последовательного регистра соединен с входом разрешения записи второго параллельного регистра и первым управляющим выходом блока, выход третьего разряда последовательного регистра соединен с входом разрешения записи третьего параллельного регистра, выход четвертого (старшего) разряда последовательного регистра соединен с входом разрешения записи четвертого параллельного регистра и вторым управляющим выходом блока.

Недостатки известного устройства - не способность обрабатывать аналоговую информацию, не исключается плюральный вотум, значительная аппаратурная избыточность и, как следствие, низкая надежность в работе, значительная энергоемкость.

Наиболее близким по технической сущности к изобретению является устройство для обработки нечеткой информации (см. патент РФ 2018951, М.кл. G 06 F 15/36, БИ 16, 1994 г.), содержащее генератор тактовых импульсов, группу из А дешифраторов, первую группу из А регистров, вторую группу из К регистров, первую группу из А блоков элементов И, вторую группу из К блоков элементов И, первую группу из А триггеров, вторую группу из А триггеров, третью группу из К триггеров, первую группу из А элементов ИЛИ, вторую группу из А элементов ИЛИ, третью группу из А элементов ИЛИ, первую и вторую группы из А формирователей импульсов, первую и вторую группы из А счетчиков, первую и вторую группы из А элементов И, третью группу из К элементов И, четвертую группу из А элементов И, группу из А элементов НЕ, пять элементов ИЛИ, третью группу из А счетчиков импульсов, группу из К блоков сравнения, причем информационный вход устройства соединен поразрядно с информационными входами всех дешифраторов, выходы i-го (где i=1,...,А) дешифратора группы соединены соответственно со входами i-х элементов ИЛИ первой и второй групп, выход i-гo элемента ИЛИ первой группы соединен с первыми входами i-гo элемента И первой группы, выход которого соединен со входом i-гo формирователя импульсов первой группы, выход которого соединен со входом установки в "1" i-гo триггера первой группы и со входом установки в "0" i-гo триггера второй группы, выход которого соединен с управляющим входом i-го дешифратора группы, выход i-гo триггера первой группы соединен с первым входом i-гo элемента И второй группы, выход которого соединен со счетными входами i-х счетчиков первой и второй групп, входы установки в "0" всех счетчиков первой группы соединены с первым входом первого элемента ИЛИ и со входом начальной установки устройства, вход пуска которого соединен со вторым входом первого элемента ИЛИ, выход которого соединен со входом установки в "0" i-гo счетчика второй группы и первых входом второго элемента ИЛИ, выход которого соединен со входом установки в "1" i-гo триггера второй группы и с первым входом i-гo блока элементов И первой группы, входы со второго по n-й которого соединены соответственно с разрядными входами i-гo регистра первой группы, информационные входы которого соединены со входами задания альтернативных вариантов устройства, входы задания дополнительных кодов которого соединены со входами задания альтернативных вариантов устройства, входы задания дополнительных кодов которого соединены с информационными входами j-го (где j=1,...,К) регистра второй группы, выходы которого соединены со входами со второго по n-й j-гo блока элементов И второй группы, первый вход которого соединен с выходом j-го триггера третьей группы, вход установки в "0" которого соединен с выходом первого элемента ИЛИ и первым входом третьего элемента ИЛИ, выход которого соединен со входом установки в "0" j-гo триггера первой группы, выход которого соединен с j-м входом четвертого элемента ИЛИ, входы с первого по n-й третьего элемента ИЛИ соединены соответственно с выходами формирователей второй группы и первым входом - с первыми входами всех элементов И третьей группы, выход j-го элемента И третьей группы соединен со входом установки в "0" j-го триггера третьей группы, выходы j-го блока элементов И второй группы соединены с первой группой входов j-го блока сравнения, выход которого соединен со вторым входом j-гo элемента И третьей группы и с j-м входом пятого элемента ИЛИ, выход которого соединен со вторыми входами всех элементов И первой группы, выходы j-гo блока элементов И первой группы соединены с информационными входами i-го счетчика третьей группы, вход которого соединен со входом i-гo элемента ИЛИ третьей группы, выход которого соединен со вторым входом i-гo элемента И четвертой группы и входом i-гo элемента НЕ группы, выход которого соединен со входом i-гo формирователя импульсов второй группы, третий вход i-гo элемента И четвертой группы соединен с выходом генератора тактовых импульсов, четвертый вход i-гo элемента И четвертой группы соединен с выходом четвертого элемента ИЛИ, а первый вход i-гo элемента И четвертой группы соединен с выходом (i-l)-гo элемента НЕ группы, тактовые входы регистров первой и второй групп соединены со входом начальной установки устройства, а также четвертую группу из К триггеров, группу из К элементов ИЛИ-НЕ и третью группу из К блоков элементов И, причем выход i-гo элемента ИЛИ второй группы соединен с q-м (где q=1,..., n) входом блока элементов И третьей группы, выходы j-гo блока элементов И третьей группы соединены со второй группой входов j-гo блока сравнения группы, (n+1)-й вход j-гo блока элементов И третьей группы соединен с выходом j-гo элемента ИЛИ-НЕ группы, входы которого соединены соответственно с выходами триггеров четвертой группы, вход установки в "1" j-гo триггера четвертой группы соединен со входом j-гo блока сравнения группы, а вход установки в "0" j-гo триггера четвертой группы соединен с выходом f-го формирователя импульсов второй группы. (Признаки, общие с объектом изобретения - общие с аналогом по авторскому свидетельству СССР 1688260, М.кл. G 06 F 15/36, БИ 40, 1991 г.)

Недостатки известного устройства - неспособность обрабатывать аналоговую информацию, значительная аппаратная избыточность и, как следствие, низкая надежность в работе, значительная энергоемкость.

Задача изобретения - обеспечение возможности обрабатывать аналоговую информацию, сокращение аппаратурной избыточности и повышение надежности в работе.

Технический результат изобретения состоит в возможности обрабатывать аналоговую информацию, возможности сокращении аппаратурной избыточности и в повышении надежности в работе.

Технический результат изобретения достигается тем, что в устройство, содержащее генератор тактовых импульсов, группу триггеров, группу первых элементов И, соединенных первыми входами с единичными выходами одноименных триггеров, второй элемент И, элемент ИЛИ, соединенный первым входом со входом пуска устройства, а выходом с нулевыми входами триггеров, группу первых счетчиков импульсов, соединенных входами обнуления со входом пуска устройства, а счетными входами с выходами одноименных первых элементов И, и группу вторых счетчиков импульсов, соединенных счетными входами с выходами одноименных первых элементов И, а входами обнуления с выходом элемента ИЛИ, введены группа ключей, соединенных информационными входами устройства, группа пороговых элементов, соединенных информационными входами с выходами одноименных ключей, а сигнальными выходами с единичными входами одноименных триггеров, нулевые выходы которых соединены со входами управления одноименных ключей, регулятор порога срабатывания пороговых элементов соединенный управляющим входом с управляющими выходами пороговых элементов, а управляющим выходом с управляющими входами пороговых элементов, и задатчик напряжений, соединенный первым и вторым выходами с первым и вторым соответственно входами регулятора порога, а третьим выходом со входами ввода смещения пороговых элементов, причем второй элемент И соединен первым входом с выходом генератора импульсов, вторыми входами с единичными выходами триггеров, а выходом со вторым входом элемента ИЛИ, и вторые входы первых элементов И соединены с выходом генератора импульсов.

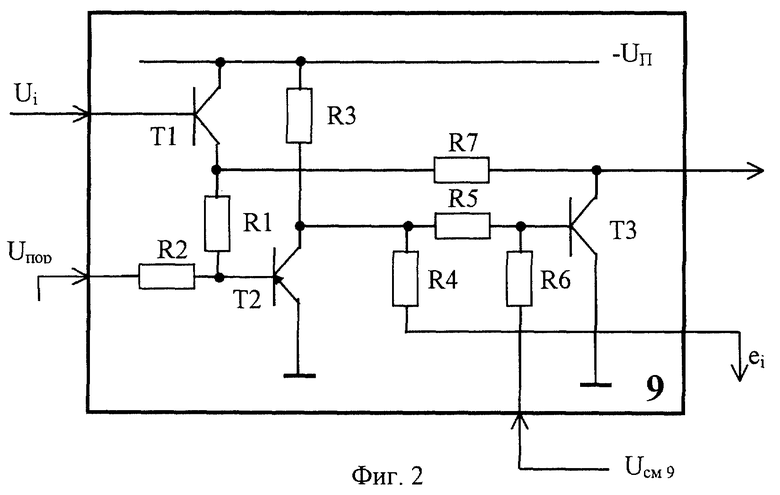

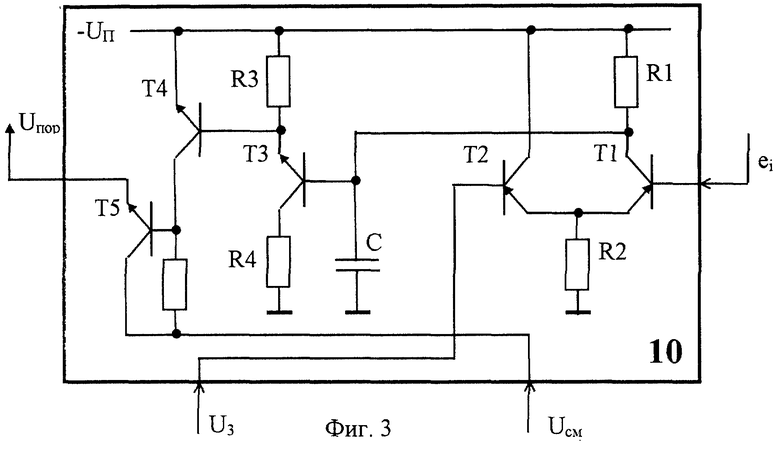

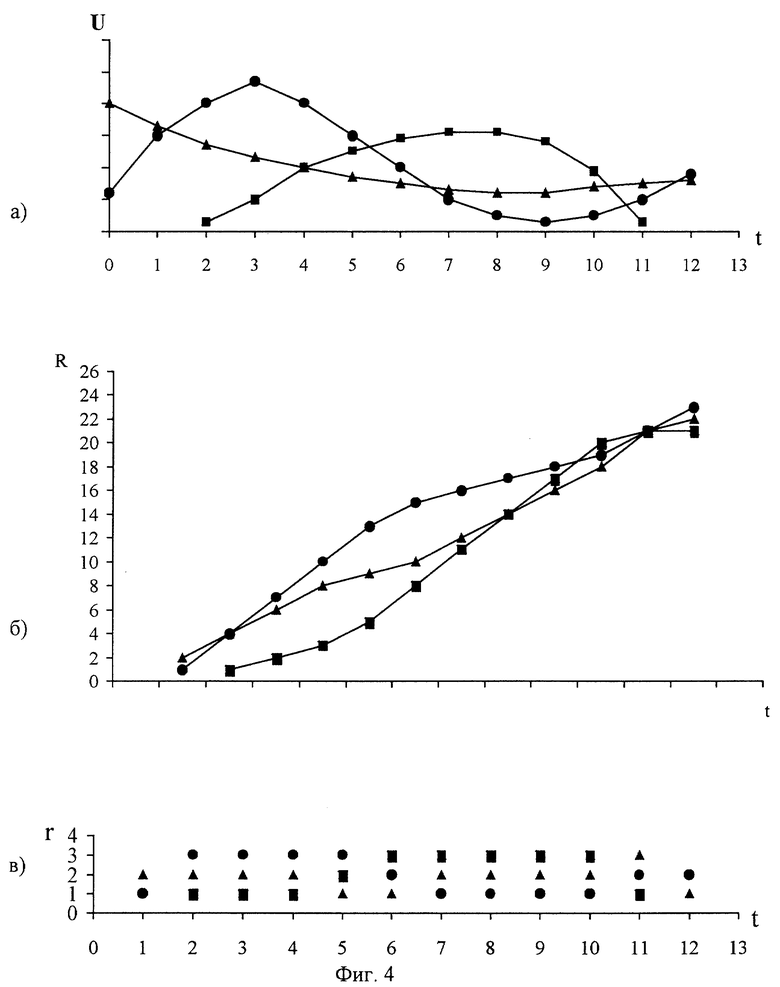

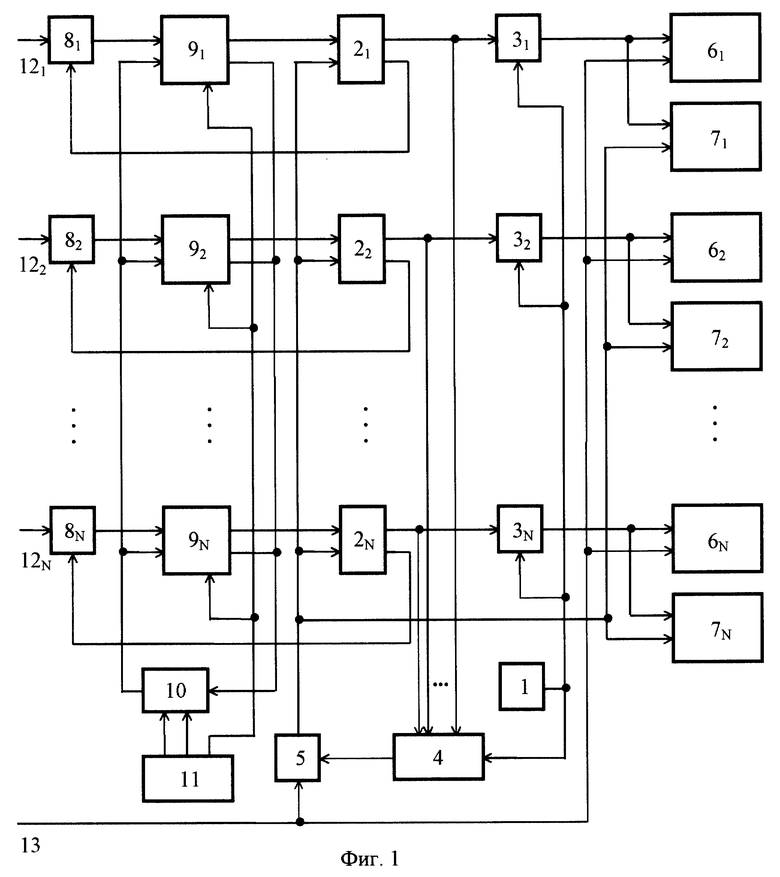

Схема устройства для обработки нечеткой информации приведена на фиг.1, на фиг.2 схема его порогового элемента, на фиг.3 схема регулятора порога, а на фиг. 4 пример диаграммы содержимого первых и вторых счетчиков импульсов.

Устройство содержит (см. фиг.1) генератор 1 тактовых импульсов, группу из N, где N≥числу альтернативных, анализируемых, вариантов, триггеров 2, группу из N первых элементов И 3, второй элемент И 4, элемент ИЛИ 5, группу из N первых счетчиков 6 импульсов, группу из N вторых счетчиков 7 импульсов, группу из N ключей 8, группу из N пороговых элементов 9, регулятор порога 10 и задатчик напряжений 11. Генератор 1 соединен выходом со входами элементов И 3 и И 4, каждый триггер 2 единичным выходом соединен со входом одноименного элемента И 3 и с одноименным входом элемента И 4, каждый элемент И 3 выходом соединен со счетными входами одноименных счетчиков 6 и 7, каждый ключ 8 выходом соединен с информационным входом одноименного порогового элемента 9, каждый из которых сигнальным выходом соединен с единичным входом одноименного триггера 2, регулятор порога 10 входом управления соединен с выходом управления каждого порогового элемента 9, а управляющим выходом с управляющим входом каждого порогового элемента 9, задатчик напряжений 11 соответствующими выходами соединен со входами смещения пороговых элементов 9 и регулятора порога 10, входы обнуления триггеров 2 и счетчиков 7 соединены с выходом элемента ИЛИ 5, один вход которого соединен с выходом элемента И 4, нулевые выходы триггеров 2 соединены со входами управления одноименных ключей 8, информационные входы которых соединены с информационными входами 12 устройства, а вход пуска 13 устройства соединен со входом элемента ИЛИ 5 и со входами обнуления счетчиков 6.

Устройство работает следующим образом.

Задатчиком напряжений 11 устанавливаются значения U3 по первому выходу, Uсм10 по второму выходу и Ucм9 по третьему выходу. По переднему фронту импульса пуска, подаваемому на вход 13 триггеры 2i (где i=1,....,N), счетчики 6, и 7i обнуляются, при этом на нулевых выходах триггеров 2 (21÷2N) устанавливаются единичные потенциалы, на выходах пороговых элементов нулевые потенциалы, а ключи 8 (81÷8N) открываются. Текущие значения альтернативных вариантов Ai, mi (mi÷mN) через информационные входы 12i (121÷12N) и ключи 8i (81÷8N) поступают на информационные входы пороговых элементов 9i (91÷9N) соответственно. Пороговый элемент 9i, на входе которого значение mi, максимально срабатывает, при этом на его сигнальном выходе устанавливается высокий (единичный) потенциал, а на выходе управления сигнал ei пропорциональный значению mi. Высоким потенциалом с выхода элемента 9i триггер 2i переводится в единичное состояние, его нулевой выход обнуляется, ключ 8i закрывается, а элемент И 3i, открывается, что обеспечивает прохождение импульса с выхода генератора 1 через элемент И 3i на счетные входы счетчиков 6i и 7i. С момента закрытия ключа 8i на входах пороговых элементов 9, исключая элемент 9i, находится значение mi+q с максимумом, процесс срабатывания одноименных пороговых элементов 9, триггеров 2, элементов И 3, счетчиков 6 и 7 и ключей 8 повторяется до полного перебора всех mN. К моменту завершения цикла опроса входов 12 все триггеры 2 обнулены, а в счетчиках 6 и 7 зафиксированы значения их рейтингов, т.е. в счетчике 7i, фиксируется текущее значение mi, рейтинга альтернативного варианта Аi, а в счетчике 6 - интегральное (суммарное, за время работы) значение Мi рейтинга альтернативного варианта. Последним по времени срабатывания триггеров 2 передним фронтом импульса открывается элемент И 4 и импульсом с выхода генератора 1 через элементы И 4 и ИЛИ 5 триггеры 2 и счетчики 7 обнуляются, а содержимое счетчиков 6 сохраняется. Так устройство работает неограниченно долго (при безразмерной емкости счетчиков 6 и 7). В счетчиках 6 за время анализа Δt (см. фиг.4) при поведении Аi как показано на фиг.4а, фиксируются интегральные значения Ri альтернативных вариантов Ai (см. фиг.4б), а в счетчиках 7 - их текущие значения - ri (см. фиг.4в).

Таким образом предлагаемое устройство по качественным характеристикам значений mi, (см. фиг. 4а) альтернативных вариантов Аiгенерирует по каждому циклу анализа их текущие рейтинги ri (см. фиг. 4в), выражение целочисленное, и интегральные рейтинги Ri (см. фиг. 4б) за весь период анализа (работы устройства), причем аппаратурные и энергетические затраты, по сравнению с известными устройствами аналогичного назначения, сокращены в несколько раз, надежность значительно повышена, а результаты анализа по содержимому счетчиков 6 и 7 в любой момент времени представимы в виде кортежей

<<Ai+k, Ai-k,....,Ai,...,Ai+k-1, Ai+8, AN>>3

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО УПРАВЛЕНИЯ РЕАБИЛИТАЦИЕЙ ФУНКЦИЙ МЫШЦ ЧЕЛОВЕКА | 1999 |

|

RU2153363C1 |

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ РИТМИЧНОСТИ ПРОЦЕССА | 1998 |

|

RU2133979C1 |

| СПЕКТРОФОТОМЕТР-АНАЛИЗАТОР | 2000 |

|

RU2165611C1 |

| МНОГОПОРОГОВОЕ УСТРОЙСТВО | 2000 |

|

RU2181926C2 |

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ УРОВНЯ СЫПУЧИХ МАТЕРИАЛОВ | 1998 |

|

RU2138027C1 |

| УСТРОЙСТВО ДЛЯ АНАЛИЗА РОДОВОЙ ДЕЯТЕЛЬНОСТИ | 1998 |

|

RU2130645C1 |

| УСТРОЙСТВО ДЛЯ СЕЙСМИЧЕСКОГО ЗОНДИРОВАНИЯ ДНА ВОДОЕМОВ | 2002 |

|

RU2212692C1 |

| СПОСОБ ЦЕНТРАЛИЗОВАННОГО КОНТРОЛЯ N ОБЪЕКТОВ | 2000 |

|

RU2198418C2 |

| УСТРОЙСТВО ДЛЯ ЭКСПРЕСС-КОНТРОЛЯ АРИТМИИ СЕРДЦА ЧЕЛОВЕКА | 1998 |

|

RU2138195C1 |

| УСТРОЙСТВО ДЛЯ УЧЕТА ЭЛЕКТРОЭНЕРГИИ | 1997 |

|

RU2125269C1 |

Изобретение относится к вычислительной технике и может быть использовано для решения задач теории массового обслуживания, контроля сложных технологических процессов в условиях нечеткой исходной информации, а также для нечеткого логического вывода в экспертных системах. Техническим результатом является обеспечение возможности обработки аналоговой информации, сокращение аппаратурной избыточности и повышение надежности в работе. Устройство содержит группы по числу информационных входов ключей, пороговых элементов, триггеров, элементов И и две группы счетчиков импульсов, а также задатчик эталонных потенциалов, регулятор порога, генератор тактовых импульсов, элемент И и элемент ИЛИ. 4 ил.

Устройство для обработки нечеткой информации, содержащее генератор тактовых импульсов, группу триггеров, группу первых элементов И, соединенных первыми входами с единичными выходами одноименных триггеров группы, второй элемент И, элемент ИЛИ, соединенный первым входом с входом пуска устройства, а выходом с нулевыми входами триггеров группы, группу первых счетчиков импульсов, соединенных входами обнуления с входом пуска устройства, а счетными входами с выходами одноименных первых элементов И группы, и группу вторых счетчиков импульсов, соединенных счетными входами с выходами одноименных первых элементов И группы, а входами обнуления с выходом элемента ИЛИ, отличающееся тем, что в него введены группа ключей, соединенных информационными входами с одноименными информационными входами устройства, а входами управления с нулевыми выходами одноименных триггеров группы, группа пороговых элементов, соединенных информационными входами с выходами одноименных ключей группы, а сигнальными выходами с единичными входами одноименных триггеров группы, регулятор порога срабатывания пороговых элементов, соединенный входом управления с выходами управления пороговых элементов группы, а выходом управления с входами управления пороговых элементов группы, и задатчик напряжений, соединенный первым и вторым выходами с первым и вторым соответственно входами ввода смещения регулятора порога, а третьим выходом с входами ввода смещения пороговых элементов группы, причем второй элемент И соединен первым входом с выходом генератора тактовых импульсов, вторыми входами с единичными выходами триггеров группы, а выходом с вторым входом элемента ИЛИ, и вторые входы первых элементов И группы соединены с выходом генератора тактовых импульсов.

| УСТРОЙСТВО ДЛЯ АНАЛИЗА АЛЬТЕРНАТИВНЫХ РЕШЕНИЙ | 1988 |

|

RU2018951C1 |

| ПРОЦЕССОР ДЛЯ РЕАЛИЗАЦИИ ОПЕРАЦИЙ НАД ЭЛЕМЕНТАМИ НЕЧЕТКИХ МНОЖЕСТВ | 1991 |

|

RU2012037C1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЙ | 1992 |

|

RU2042186C1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ЛОГИЧЕСКОЙ ИНФОРМАЦИИ | 1988 |

|

SU1826784A1 |

| US 3611309 А, 05.10.1971 | |||

| US 4538235 А, 27.08.1985. | |||

Авторы

Даты

2002-05-10—Публикация

2000-03-28—Подача