Изобретение относится к автоматике и вычислительной технике и предназначено для реализации нечетких логических выражений (формул).

Целью изобретения является повышение производительности.

Если а и b некоторые нечеткие высказывания, то составные нечеткие высказывания образуются из простых с помощью логических операций отрицание, конъюнкция, дизъюнкция, импликация, эквивалентность, которые в минимаксном базисе реализуются следующим образом:

отрицание

конъюнкция a&b = min(a,b) (2)

дизъюнкция a∨b= max(a,b) (3)

импликация a_→b= max (1-a,b) (4)

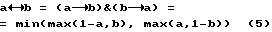

эквивалентность

Если заданы степени истинности простых нечетких высказываний, то, используя ( 1)-(5), можно найти степени истинности составного нечеткого высказывания, а также решать расплывчатые логические уравнения.

Нечеткой высказывательной переменной и называется нечеткое высказывание, степень истинности которого может принимать значения из интервала (⊘,1). Нечеткой логической формулой А(x1, хn) называется: а) любая логическая переменная или константа изО. 1} б) если А1(x1, хn) и An(x1, хn)- нечеткие формулы, то применение к ним конечного числа раз логических операций (∧, &, ∨, _→, ←→) приводит к получению нечеткой логической формулы. Других нечетких формул не существует.

На чертеже приведена функциональная схема предлагаемого устройства для обработки логической информации.

Устройство для обработки логической информации содержит три регистра 1-3, три коммутатора 4-6, элемент ИЛИ-НE 7, три схемы сравнения 8-10, две группы информационных входов 11-12, четыре настроечных входа 13-16, выход 17 схемы сравнения 10, выход 18 элемента ИЛИ-НЕ 7, выход 19 схемы сравнения 9, группу выходов 20.

Схема сравнения 10 предназначена для сравнения текущего значения и инверсного эталонного значения нечеткого высказывании и содержит два m-разрядных информационных входа и один выход. На выходе схемы сравнения 10 формируется сигнал единичного уровня, если текущее значение больше, чем инверсия эталонного и сигнал нулевого уровня в противном случае.

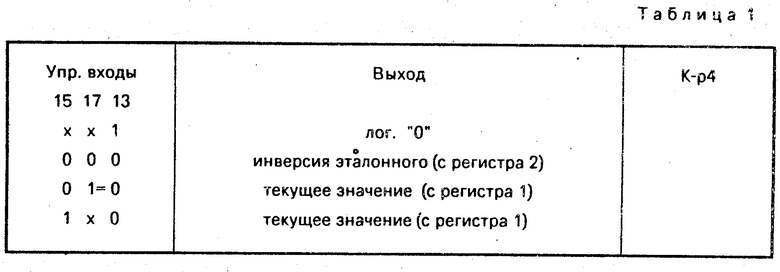

Коммутатор 4 предназначен для выделения текущего значения или инверсии эталонного значения в зависимости от кода операций и схемных условий. Коммутатор 4 имеет два m-разрядных информационных входа и три управляющих входа, m-разрядный выход. Коммутатор работает в соответствии с табл. 1, где х безразличное состояние.

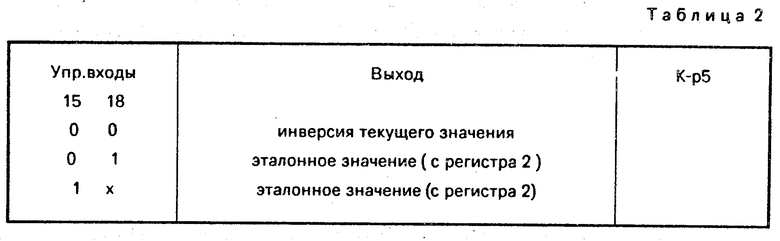

Коммутатор 5 предназначен для выделения инверсии текущего значения или эталонного значения. Коммутатор 5 работает в соответствии с табл. 2.

Схема сравнения 8 предназначена для сравнения инверсии текущего значения и эталонного значения нечеткого высказывания.

На выходе схемы сравнения 8 формируется сигнал единичного уровня, если инверсия текущего значения больше эталонного и сигнал лог. 0 в противном случае.

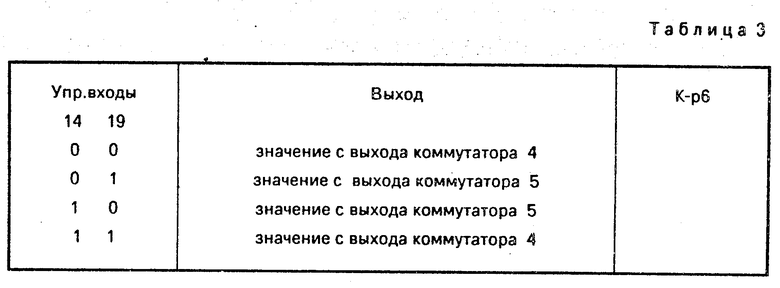

Коммутатор 6 предназначен для коммутации информации с выходов коммутатора 4 и выходов коммутатора 5. Коммутатор 6 работает в соответствии с табл. 3.

На схеме сравнения 9 формируется сигнал единичного уровня, если значение на выходах коммутатора 4 больше, чем значение на выходах коммутатора 5 и сигнал нулевого уровня в противном случае.

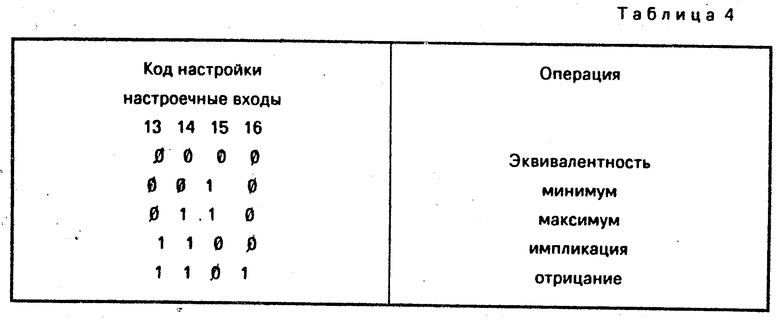

Коды настроек на реализацию заданной операции приведены в табл. 4.

Рассмотрим работу устройства на примере самой сложной операции операции эквивалентности.

В регистры 1 и 2 заносятся значения нечетких переменных, одновременно на входы 13-16 заносится код настройки, для операции эквивалентности код настройки 0000 (см.табл.4).

Предположим, что в регистры 1 и 2 были занесены значения нечетких переменных а 0,6 и b 0,7, соответственно. Тогда на входы схемы сравнения 10 и коммутатора поступят значения а 0,6 и b 0,3. Т.к. a >∧b, на выходе схемы сравнения 10 формируется сигнал лог. 1. Коммутатор 4 пропустит значение а 0,6, т. е. выполнится операция max (a, ∧b). Ha входы схемы сравнения 8 и коммутатора 5 поступят значения ∧a 0,4 и b 0,7, на выходе схемы сравнения 8 будет сформирован сигнал лог. О, а на выходе элемента ИЛИ-НЕ 7 будет сформирован сигнал лог. 1 и коммутатор 5 пропустит значение b, т.е. на выходе коммутатора 5 устанавливается результат операции ∧(a,b). Значения max (a, ∧b) и max (∧a,b), равные 0,6 и 0,7 соответственно, поступают на входы коммутатора 6 и схемы сравнения 9, на выходе которой формируется сигнал лог. 0 (т. к. 0,7>0,6). Тогда коммутатор 6 пропустит наименьшее число (см. табл. 3), т.е. 0,6 и на его выходе появится результат операции min(max(a, ∧b), max(∧a, b)) или min ((a_→b),(b_→a)). Полученный результат записывается в регистр 3.

Таким образом, устройство позволяет выполнять все логические операции за один такт работы. На основе аналогичных устройств, можно построить однородную вычислительную структуру для реализации нечетких алгоритмов управления трудноформализуемыми объектами. ТТТ1 ТТТ2 ТТТ3 ТТТ4

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРОЦЕССОР ДЛЯ РЕАЛИЗАЦИИ ОПЕРАЦИЙ НАД ЭЛЕМЕНТАМИ НЕЧЕТКИХ МНОЖЕСТВ | 1991 |

|

RU2012037C1 |

| ЯЧЕЙКА ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СТРУКТУРЫ | 1991 |

|

RU2010309C1 |

| Ячейка однородной структуры | 1987 |

|

SU1444746A1 |

| ЯЧЕЙКА ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СТРУКТУРЫ | 1993 |

|

RU2040038C1 |

| Ячейка однородной структуры | 1989 |

|

SU1674104A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЙ | 1992 |

|

RU2042186C1 |

| Ячейка однородной структуры | 1980 |

|

SU941994A1 |

| Ячейка однородной структуры | 1990 |

|

SU1805473A1 |

| Устройство для выполнения операций над расплывчатыми операндами | 1986 |

|

SU1451677A1 |

| Процессор для реализации операций над элементами расплывчатых множеств | 1985 |

|

SU1256010A1 |

Изобретение относится к автоматике и вычислительной технике и предназначено для реализации нечетких логических выражений (формул). Целью изобретения является повышение производительности. Устройство содержит три регистра 1-3, три коммутатора 4-6, элемент ИЛИ-НЕ 7, три схемы сравнения 8-10. Устройство позволяет выполнять за один такт операции: эквивалентность, минимум, максимум, импликация и отрицание. 4 табл., 1 ил.

Устройство для обработки логической информации, содержащее три коммутатора и схему сравнения, причем выход первого коммутатора соединен с первым входом схемы сравнения, второй вход которой соединен с выходом второго коммутатора, отличающееся тем, что, с целью повышения производительности, оно содержит элемент ИЛИ НЕ и вторую и третью схемы сравнения, причем прямые входы первых информационных входов группы соединены с первыми входами первого коммутатора и второй схемы сравнения, вторые входы которых соединены с инверсными входами вторых информационных входов группы, прямые входы которых соединены с первыми входами второго коммутатора и третьей схемы сравнения, вторые входы которых соединены с инверсными входами первых информационных входов группы, выход первой схемы сравнения соединен с первым управляющим входом третьего коммутатора, первый информационный вход которого соединен с выходом первого коммутатора, первый управляющий вход которого соединен с первым управляющим входом второго коммутатора и первым настроечным входом устройства, второй настроечный вход которого соединен с первым входом элемента ИЛИ НЕ, выход которого соединен с вторым управляющим входом второго коммутатора, выход которого соединен с вторым информационным анодом третьего коммутатора, второй управляющий вход которого соединен с третьим настроечным входом устройства, четвертый настроечный вход которого соединен с вторым управляющим входом первого коммутатора, третий управляющий вход которого соединен с выходом второй схемы сравнения, выход третьей схемы сравнения соединен с вторым входом элемента ИЛИ НЕ, выход третьего коммутатора является выходом устройства.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для сравнения чисел | 1984 |

|

SU1254464A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для регулирования толщины изоляции кабеля | 1980 |

|

SU941944A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1996-06-27—Публикация

1988-07-15—Подача