Изобретение относится к вычислительной технике и технической кибернетике и может быть использовано с специализированных процессорах для обработки нечеткой информации.

Устройство предназначено для обработки потоков n-разрядных двоичных чисел Ai и Bi, представленных в прямом коде, с индивидуальной функцией обработки для каждой пары чисел. Множество возможных функций обработки включает в себя C1Ai + Bi, C2 Ai Bi, C3 Bi Ai, C4 IAi + BiI C5 I Ai Bi I, C6

I Bi Ai I C7 min (1,  +

+  ), C8 max (0,

), C8 max (0,

), где

), где  ,

,  означает прямое либо инверсное представление значащей части двоичного кода числа. При этом функция D min (1, A + B) определяет дизъюнкцию нечетких переменных A и B, функция I1 min (1,

означает прямое либо инверсное представление значащей части двоичного кода числа. При этом функция D min (1, A + B) определяет дизъюнкцию нечетких переменных A и B, функция I1 min (1,  + B) импликацию (A _→ B), функция I2 min (1, A +

+ B) импликацию (A _→ B), функция I2 min (1, A +  ) импликацию (B _→ A), функция S min (1,

) импликацию (B _→ A), функция S min (1,  +

+  ) операцию штрих Шеффера, функция Q max (0, A B) операцию ограниченной разности нечетких переменных A, B, функция K max (0, A

) операцию штрих Шеффера, функция Q max (0, A B) операцию ограниченной разности нечетких переменных A, B, функция K max (0, A  ) операцию конъюнкции, функция P max (0,

) операцию конъюнкции, функция P max (0,  B) операцию стрелка Пирса. В этих формулах

B) операцию стрелка Пирса. В этих формулах  1 A,

1 A,  1 B. Нечеткие переменные

1 B. Нечеткие переменные  ,

,  входящие в функции С7, С8 и в производные от функций С7, С8: D, I1, I2, S, Q, K, P, принимают значения из интервала [0, 1] (Нечеткие множества в моделях управления и искусственного интеллекта. / Под ред. Д.А. Поспелова. М. Наука, 1986, с. 146).

входящие в функции С7, С8 и в производные от функций С7, С8: D, I1, I2, S, Q, K, P, принимают значения из интервала [0, 1] (Нечеткие множества в моделях управления и искусственного интеллекта. / Под ред. Д.А. Поспелова. М. Наука, 1986, с. 146).

Указанные логические операции над нечеткими переменными принадлежат нечеткой логике с ограниченными операциями. В устройстве результаты операции Cr, Cr+3, Cr+6 для r 1, 2 формулируются одновременно на выходных шинах устройства, то же и для результатов операций Сr, Cr+3 для r 3.

Известно устройство для выполнения операций над нечеткими переменными (авт. св. СССР N 1589268, кл. G 06 F 7/00, опублик. 1990), содержащее два сдвиговых регистра, элементы И, ИЛИ, НЕ, группу из 2m (m количество разрядов операндов) элементов И, входы операндов, тактовый вход, выход результата операции дизъюнкции, выход результата операции стрелка Пирса, выход результата операции конъюнкции, выход результата операции штрих Шеффера.

Известное устройство не позволяет получать результаты алгебраического сложения, алгебраического вычитания двух операндов, а также модули этих результатов, а кроме того, значения всех переменных должны представляться унитарным кодом.

Известно устройство для вычитания (авт. св. СССР N 1654813, кл. G 06 F 7/50, опублик. 1991), содержащее два регистра сдвига, два коммутатора, группу элементов И, группу элементов ИЛИ, элемент запрета, элементы И, ИЛИ, входы операндов, управляющие входы, тактовый вход, вход управления режимом работы, вход записи, две группы выходов.

Это устройство не позволяет получать результат алгебраического сложения и требует для представления всех переменных использования унитарного кода.

Наиболее близким к предложенному по технической сути является устройство для вычисления разности двух чисел (авт. св. СССР N 1444753, кл. G 06 F 7/50, опублик. 1988), содержащее первый и второй регистры операндов, сумматор, первый, второй и третий преобразователи прямого кода в дополнительный, два элемента НЕРАВНОЗНАЧНОСТЬ, входы операндов, вход разрешения записи операндов, входы управления знаком операндов, выход модуля результата, выход знака результата и выход результата, причем информационные входы регистров являются соответствующими входами операндов устройства, выходы сумматора соединены соответственно с управляющим и информационными входами первого преобразователя прямого кода в дополнительный, выход которого является выходом модуля результата устройства, вход разрешения записи операндов в регистры устройства, входы управления знаком первого и второго операндов устройства, выход знака результата устройства, выход результата устройства соединены соответственно с входами разрешения записи регистров, первыми входами первого и второго элементов НЕРАВНОЗНАЧНОСТЬ, знаковым выходом сумматора и выходом суммы сумматора, первый знаковый вход которого соединен с выходом первого элемента НЕРАВНОЗНАЧНОСТЬ и управляющим входом второго преобразователя прямого кода в дополнительный, информационный вход которого соединен с выходом значащих разрядов регистра первого операнда, выход знакового разряда которого соединен с вторым входом первого элемента НЕРАВНОЗНАЧНОСТЬ, второй знаковый вход сумматора соединен с выходом второго элемента НЕРАВНОЗНАЧНОСТЬ и управляющим входом третьего преобразователя прямого кода в дополнительный, информационный вход которого соединен с выходом значащих разрядов регистра второго операнда, выход знакового разряда которого соединен с вторым входом второго элемента НЕРАВНОЗНАЧНОСТЬ, первый и второй информационные входы сумматора соединены соответственно с выходами второго и третьего преобразователей прямого кода в дополнительный.

Такое устройство не позволяет получать результат операций нечеткой логики: дезъюнкции, конъюнкции, импликации, штрих Шеффера, стрелка Пирса, ограниченную разность.

Задачей изобретения является реализация наряду с функциями С1 A + B, C2 A B, C3 B A, C4 I A + B I C5 I A B I C6I B A I дополнительно базовых функций C7 min (1,  +

+  ), C8 max (0,

), C8 max (0,  -

- ), где

), где  ,

,  означают использование либо прямого значения аргументов A, B, либо инверсного значения

означают использование либо прямого значения аргументов A, B, либо инверсного значения  1 A и

1 A и  1 B. При этом в зависимости от значения аргументов устройство позволяет вычислить дополнительно следующие операции нечеткой логики с ограниченными операциями: дизъюнкцию D min (1, A + B), импликацию I1 min (1,

1 B. При этом в зависимости от значения аргументов устройство позволяет вычислить дополнительно следующие операции нечеткой логики с ограниченными операциями: дизъюнкцию D min (1, A + B), импликацию I1 min (1,  + B), импликацию I2 min (1, A +

+ B), импликацию I2 min (1, A +  ) min (1, A + 1 B), штрих Шеффера S min (1, 1 -A + 1 B), конъюнкцию K max (0, A

) min (1, A + 1 B), штрих Шеффера S min (1, 1 -A + 1 B), конъюнкцию K max (0, A  )max (0, A + B 1), стрелку Пирса P max (0, 1 A B) max (0,

)max (0, A + B 1), стрелку Пирса P max (0, 1 A B) max (0,  B), ограниченную разность Q max (0, A B), в результате чего расширяются функциональные возможности устройства.

B), ограниченную разность Q max (0, A B), в результате чего расширяются функциональные возможности устройства.

Поставленная задача реализуется тем, что устройство для вычислений, содержащее первый и второй регистры операндов, три преобразователя прямого кода в дополнительный, два элемента НЕРАВНОЗНАЧНОСТЬ, сумматор, причем информационные входы регистров являются соответствующими входами операндов устройства, вход разрешения записи операндов в регистры устройства, входы управления знаком первого и второго операндов устройства, выход знака результата устройства, выход результата устройства соединены соответственно с входами разрешения записи регистров, первыми входами первого и второго элементов НЕРАВНОЗНАЧНОСТЬ, знаковым выходом сумматора и выходом суммы сумматора, первый знаковый вход которого соединен с выходом первого элемента НЕРАВНОЗНАЧНОСТЬ и управляющим входом первого преобразователя прямого кода в дополнительный, второй знаковый вход сумматора соединен с выходом второго элемента НЕРАВНОЗНАЧНОСТЬ и управляющим входом второго преобразователя прямого кода в дополнительный, выходы знакового разряда регистров первого и второго операндов соединены соответственно с вторым входом первого и вторым входом второго элементов НЕРАВНОЗНАЧНОСТЬ, первый и второй информационные входы сумматора соединены соответственно с выходами первого и второго преобразователей прямого кода в дополнительный, выходы сумматора соединены соответственно с управляющим и информационным входами третьего преобразователя прямого кода в дополнительный, выход которого является выходом модуля результата устройства, дополнительно содержит три коммутатора, элемент НЕ, группу из n (n число разрядов двоичного кода операндов) элементов И, группу из n элементов ИЛИ, причем выходы первого и второго коммутаторов соединены с информационными входами соответственно первого и второго преобразователей, первые и вторые входы первого и второго коммутаторов соединены соответственно с прямыми выходами и с инверсными выходами значащих разрядов соответственно регистров первого и второго операндов, управляющие входы первого и второго коммутаторов являются входами управления видом соответственно первого и второго операндов, знаковый выход сумматора соединен с первым входом каждого из n элементов ИЛИ группы устройства и с входом элемента НЕ, выход которого соединен с первым входом каждого из n элементов И группы устройства, второй вход i-го элемента И, где i 1, 2, n, группы устройства соединен с выходом i-го разряда двоичного кода суммы сумматора, а выход i-го элемента И группы устройства соединен с вторым входом i-го элемента ИЛИ группы устройства, выходы элементов ИЛИ группы устройства и выходы элементов И группы устройства соединены соответственно с первой и второй группами входов третьего коммутатора, управляющий вход которого соединен с входом управления знаком второго операнда устройства, выход третьего коммутатора является выходом логических операций устройства.

Новыми признаками заявляемого технического решения по сравнению с прототипом являются три коммутатора, элемент НЕ, группа из n элементов ИЛИ, группа из n элементов И, новые связи, соединяющие прямые и инверсные выходы значащих разрядов регистров первого и второго операндов с первыми и вторыми входами соответственно первого и второго коммутаторов, выходы первого и второго коммутаторов с информационными входами соответственно первого и второго преобразователей прямого кода а дополнительный, знаковый выход сумматора с первым входом каждого из n элементов ИЛИ группы устройства и с входом элемента НЕ, выход элемента НЕ с первым входом каждого из n элементов И группы устройства, второй вход i-го элемента И, где i 1, 2, n, группы устройства с выходом i-го разряда двоичного кода суммы сумматора, выход i-го элемента И группы устройства с вторым входом соответствующего i-го элемента ИЛИ группы устройства, выходы элементов ИЛИ с первой группой входов, а выходы элементов И с второй группой входов третьего коммутатора, управляющий вход третьего коммутатора с входом управления знаком второго операнда устройства.

Наличие признаков, отличающих заявляемое техническое решение от прототипа, позволяет сделать вывод о соответствии заявляемого устройства для вычислений критерию "новизна".

Поскольку в устройствах аналогичного назначения признаки, отличающие заявляемое техническое решение от прототипа, не встречаются, а предложенное решение не следует явным образом из существующего уровня техники, можно утверждать, что заявляемое устройство для вычислений соответствует критерию "изобретательский уровень".

Предлагаемое устройство для вычислений может быть использовано в спецпроцессах для обработки нечеткой информации, в устройствах, реализующих нечеткий вывод и принятие решений на основе сравнения текущей ситуации с эталонными, при построении систем классификации и распознавания образов, при построении технических средств, использующих нечеткие алгоритмы. Поэтому изобретение отвечает критерию "промышленная применимость" (Мелихов А.Н. Берштейн Л.С. Коровин С.Я. Ситуационные советующие системы с нечеткой логикой. М. Наука, 1990; Мелихов А.Н. Баронец В.Д. Проектирование микропроцессорных средств обработки нечеткой информации. Ростов-на-Дону: Изд. Ростовского университета, 1990).

При решении задач классификации и распознавания образов, принятия решений на основе сходства текущей ситуации с эталонной операции сравнения и определения сходства векторов являются наиболее массовыми. Они требуют частого выполнения операций алгебраического суммирования и получения модуля разности двух чисел. Так, сходство векторов A и B может быть определено через эвклидово расстояние ρE между ними на формуле ρE(A,B)

Ai Bi

Ai Bi где Ai, Bi элементы векторов. Если ситуации (объекты) описываются нечеткими множествами A и B, то степень С их нечеткого равенства (сходства) может быть определена как C 1 (

где Ai, Bi элементы векторов. Если ситуации (объекты) описываются нечеткими множествами A и B, то степень С их нечеткого равенства (сходства) может быть определена как C 1 (

Ai B

Ai B ) / k или С 1 m

) / k или С 1 m x

x  Ai Bi

Ai Bi .

.

В предлагаемом устройстве возможно без перекоммутации потоков чисел Ai и Bi формировать как поток результатов Сi Ai Bi, так и поток результатов Ci Bi Ai. Это обеспечивается наличием первого и второго преобразователей, позволяющих формировать для каждого операнда его дополнительный код, и двух элементов НЕРАВНОЗНАЧНОСТЬ, позволяющих менять знак любого из операндов на противоположный. Наличие третьего преобразователя позволяет из дополнительного кода результата операции вычитания или суммирования, полученного на выходе сумматора, формировать на выходе преобразователя модуль полученной разности или суммы.

Наряду с этими возможностями устройства перечисленные новые признаки позволяют обеспечить вычисление результата операций: дезъюнкции D min (1, Ai + Bi), импликации I1 min (1,1 Ai + Bi) min (1,  + Bi), импликации I2 min (1,1 Bi + Ai)min (1, Ai +

+ Bi), импликации I2 min (1,1 Bi + Ai)min (1, Ai +  ), штриха Шеффера S min (1,

), штриха Шеффера S min (1,  +

+  ) min (1,1 Ai + 1 Bi). Эти операции описываются формулой C7 min (1,

) min (1,1 Ai + 1 Bi). Эти операции описываются формулой C7 min (1,  +

+  ), где переменные

), где переменные  ,

,  означают либо прямое значение A, B, либо инверсное

означают либо прямое значение A, B, либо инверсное  1 A,

1 A,  1 B. Кроме этих операций вычисляются также операции, описывающиеся формулой C8 max (0,

1 B. Кроме этих операций вычисляются также операции, описывающиеся формулой C8 max (0,

). В зависимости от прямого или инверсного значений переменных A, B или

). В зависимости от прямого или инверсного значений переменных A, B или  ,

,  вычисляется результат операций: конъюнкции Kmax (0, Ai + Bi 1) max (0, Ai

вычисляется результат операций: конъюнкции Kmax (0, Ai + Bi 1) max (0, Ai ), стрелки Пирса P max (0, 1 Ai Bi) max (0,

), стрелки Пирса P max (0, 1 Ai Bi) max (0,  Bi), ограниченной разности Q max (0, Ai Bi).

Bi), ограниченной разности Q max (0, Ai Bi).

Действительно организация связей между введенными элементами позволяет вычислить значение максимума (функцию С8) или минимума (функцию С7) без использования в устройстве блоков сравнения, а лишь за счет учета логики формирования значения "0" или "1" в знаковом разряде на выходе сумматора. Так, для функции С8max (0,

) значение разности r

) значение разности r -

-  может быть как положительным, так и отрицательным. В нечеткой логике и значения всех переменных, и значения функций принадлежат интервалу [0, 1] В отличие от арифметических операций, которые чаще выполняются с целыми числами, операции нечеткой логики выполняются всегда с числами, значение которых не превышает единичное и всегда положительно.

может быть как положительным, так и отрицательным. В нечеткой логике и значения всех переменных, и значения функций принадлежат интервалу [0, 1] В отличие от арифметических операций, которые чаще выполняются с целыми числами, операции нечеткой логики выполняются всегда с числами, значение которых не превышает единичное и всегда положительно.

Пусть значение r (

) > 0. Дополнительный код числа r в этом случае совпадает с прямым кодом, а в знаковом разряде на выходе сумматора будет ноль, который поступает на вход элемента НЕ.

) > 0. Дополнительный код числа r в этом случае совпадает с прямым кодом, а в знаковом разряде на выходе сумматора будет ноль, который поступает на вход элемента НЕ.

Единичный сигнал с выхода элемента НЕ, поступая на первый вход каждого элемента И группы, обусловливает прохождение через элементы И двоичного кода числа r на второй вход коммутатора, откуда под действием управляющего сигнала y4 1 значение r поступает на вход результата логических операций устройства. Если значение r (

) < 0, то в знаковом разряде дополнительного кода на выходе сумматора будет единица, которая обусловливает нулевой сигнал с выхода элемента НЕ, запрещающий передачу кода с выхода сумматора через элементы И группы. На выходах элементов И будет нулевой сигнал, который, проходя через второй вход коммутатора на его выход, обусловливает значение C8 max (0,

) < 0, то в знаковом разряде дополнительного кода на выходе сумматора будет единица, которая обусловливает нулевой сигнал с выхода элемента НЕ, запрещающий передачу кода с выхода сумматора через элементы И группы. На выходах элементов И будет нулевой сигнал, который, проходя через второй вход коммутатора на его выход, обусловливает значение C8 max (0,

) 0.

) 0.

Введение первого и второго коммутаторов позволяет в зависимости от того, какую из логических функций необходимо вычислять, использовать либо прямые значения аргументов A, B, либо инверсные значения  ,

,  , которые с погрешностью, равной весу единицы младшего разряда двоичного представления этих чисел, представляют дополнения

, которые с погрешностью, равной весу единицы младшего разряда двоичного представления этих чисел, представляют дополнения  1 A и

1 A и  1 B. Если регистры операндов восьмиразрядные, то с учетом одного знакового разряда остальные семь будут значащими и, следовательно, погрешность представления дополнения

1 B. Если регистры операндов восьмиразрядные, то с учетом одного знакового разряда остальные семь будут значащими и, следовательно, погрешность представления дополнения  составит 1/27 1/128, что при оперировании с нечеткими данными вполне допустимо. Таким образом, введение первых двух коммутаторов позволяет расширить класс вычисляемых в устройстве логических операций.

составит 1/27 1/128, что при оперировании с нечеткими данными вполне допустимо. Таким образом, введение первых двух коммутаторов позволяет расширить класс вычисляемых в устройстве логических операций.

Рассмотрим формирование в устройстве функции C7 min (1,  +

+  ). Результат С7 формируется на выходах элементов ИЛИ группы устройства и поступает на выход результата логических операций через первую группу входов третьего коммутатора. Это обусловлено наличием нулевого сигнала y4 0 на управляющем входе третьего коммутатора. Если величина S (

). Результат С7 формируется на выходах элементов ИЛИ группы устройства и поступает на выход результата логических операций через первую группу входов третьего коммутатора. Это обусловлено наличием нулевого сигнала y4 0 на управляющем входе третьего коммутатора. Если величина S ( +

+  ) < 1, то признак знака суммы на выходе сумматора равен нулю. Поэтому на выходе элемента НЕ этот признак обусловит единичный сигнал, разрешающий прохождение кода суммы с выхода сумматора через элементы И группы устройства и далее через вторые входы элементов ИЛИ группы устройства на первую группу входов третьего коммутатора, а затем на его выход, обусловив результат С7 min (1,

) < 1, то признак знака суммы на выходе сумматора равен нулю. Поэтому на выходе элемента НЕ этот признак обусловит единичный сигнал, разрешающий прохождение кода суммы с выхода сумматора через элементы И группы устройства и далее через вторые входы элементов ИЛИ группы устройства на первую группу входов третьего коммутатора, а затем на его выход, обусловив результат С7 min (1,  +

+  ) A + B. Если S (A + B) > 1, то за счет переноса в сумматоре в его знаковом разряде будет единица, которая, инвертируясь, обусловит нулевой сигнал на выходах элементов И группы устройства. Однако, поступая на первые входы всех элементов ИЛИ группы устройства, этот единичный сигнал обусловит на выходах код 11 1, что соответствует единице. Это значение, проходя с первых входов третьего коммутатора на его выход, обусловит результат C7 min (1, A + B) 1.

) A + B. Если S (A + B) > 1, то за счет переноса в сумматоре в его знаковом разряде будет единица, которая, инвертируясь, обусловит нулевой сигнал на выходах элементов И группы устройства. Однако, поступая на первые входы всех элементов ИЛИ группы устройства, этот единичный сигнал обусловит на выходах код 11 1, что соответствует единице. Это значение, проходя с первых входов третьего коммутатора на его выход, обусловит результат C7 min (1, A + B) 1.

Введение третьего коммутатора также влияет на логику получения результата операций С7 и С8. Так, результат С7 поступает всегда на первые входы третьего коммутатора, а результат С8 на вторые входы, что обусловливает разделение этих результатов и правильное их формирование.

Таким образом, введенные новые признаки позволяют реализовать в устройстве все операции нечеткой логики с ограниченными операциями. Эти операции составляют несколько функционально полных базисов логических операций, что расширяет функциональные возможности и область использования устройства по сравнению с прототипом.

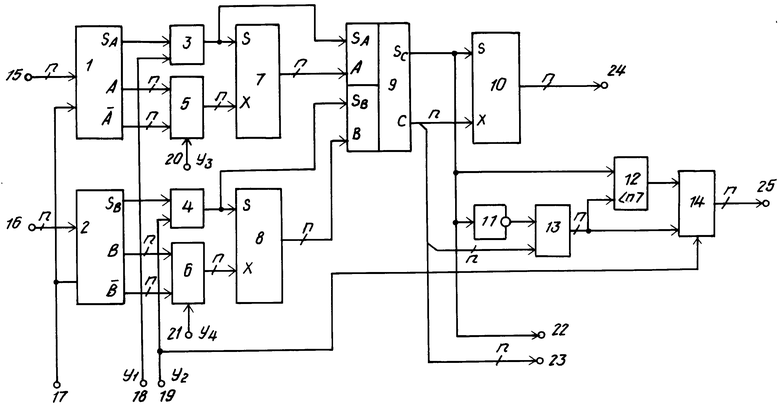

На чертеже представлена структурная схема устройства для вычислений.

Устройство содержит регистры 1 и 2 операндов A и B, элементы НЕРАВНОЗНАЧНОСТЬ 3 и 4, коммутаторы 5 и 6, преобразователи 7 и 8 прямого кода в дополнительный, сумматор 9, двусторонний преобразователь 10 прямого кода в дополнительный, элемент НЕ 11, группу из n элементов ИЛИ 121-12n, группу из n элементов И 131-13n, коммутатор 14, входы 15 и 16 операндов, вход 17 разрешения записи операндов, входы 18 и 19 управления знаком первого и второго операндов, управляющие входы 20 и 21 коммутаторов, выход 22 знака результата, выход 23 результата, выход 24 модуля результата, выход 25 результата логических операций. Выходы знаковых разрядов SA и SB регистров 1 и 2 соединены с первыми входами соответственно элементов НЕРАВНОЗНАЧНОСТЬ 3 и 4. Прямые информационные выходы A и B регистров 1 и 2 соединены с первыми входами соответственно коммутаторов 5 и 6, а инверсные информационные выходы  и

и  с вторыми входами соответственно коммутаторов 5 и 6, выходы которых соединены с информационными входами Х соответственно преобразователей 7 и 8. Выходы элементов НЕРАВНОЗНАЧНОСТЬ 3 и 4 соединены со знаковым входом S соответственно преобразователей 7 и 8 и с знаковыми входами соответственно SA и SB сумматора 9. Выходы преобразователей 7 и 8 соединены соответственно с информационными входами A и B сумматора 9, информационный выход С которого соединен с входом Х преобразователя 10, а знаковый выход Sc с входом S преобразователя 10, с входом элемента НЕ 11 и с первым входом каждого из n элементов ИЛИ 121-12n. Выход элемента НЕ 11 соединен с первым входом каждого из n элементов И 131-13n, второй вход i-го элемента И 13, где i 1, 2, n, соединен с выходом i-го разряда результата С сумматора 9, а выход с вторым входом i-го элемента ИЛИ 12. Выходы элементов ИЛИ 121-12n соединены с первой группой входов, а выходы элементов И 131-13n с второй группой входов коммутатора 14. Информационные входы 15 и 16 соответственно регистров 1 и 2 являются входами операндов A и B устройства, вход 17 разрешения записи операндов соединен с входами разрешения записи регистров 1, 2. Входы 18 и 19 управления знаком соответственно первого и второго операндов устройства соединены с вторыми входами соответственно элементов НЕРАВНОЗНАЧНОСТЬ 3 и 4. Входы 20 и 21 являются управляющими входами соответственно коммутаторов 5 и 6. Знаковый выход сумматора 9 соединен с выходом 22 знака результата, а выход С суммы сумматора 9 соединен с выходом 23 результата устройства. Выход преобразователя 10 является выходом 24 модуля результата, а выход коммутатора 14 является выходом 25 результата логических операций устройства.

с вторыми входами соответственно коммутаторов 5 и 6, выходы которых соединены с информационными входами Х соответственно преобразователей 7 и 8. Выходы элементов НЕРАВНОЗНАЧНОСТЬ 3 и 4 соединены со знаковым входом S соответственно преобразователей 7 и 8 и с знаковыми входами соответственно SA и SB сумматора 9. Выходы преобразователей 7 и 8 соединены соответственно с информационными входами A и B сумматора 9, информационный выход С которого соединен с входом Х преобразователя 10, а знаковый выход Sc с входом S преобразователя 10, с входом элемента НЕ 11 и с первым входом каждого из n элементов ИЛИ 121-12n. Выход элемента НЕ 11 соединен с первым входом каждого из n элементов И 131-13n, второй вход i-го элемента И 13, где i 1, 2, n, соединен с выходом i-го разряда результата С сумматора 9, а выход с вторым входом i-го элемента ИЛИ 12. Выходы элементов ИЛИ 121-12n соединены с первой группой входов, а выходы элементов И 131-13n с второй группой входов коммутатора 14. Информационные входы 15 и 16 соответственно регистров 1 и 2 являются входами операндов A и B устройства, вход 17 разрешения записи операндов соединен с входами разрешения записи регистров 1, 2. Входы 18 и 19 управления знаком соответственно первого и второго операндов устройства соединены с вторыми входами соответственно элементов НЕРАВНОЗНАЧНОСТЬ 3 и 4. Входы 20 и 21 являются управляющими входами соответственно коммутаторов 5 и 6. Знаковый выход сумматора 9 соединен с выходом 22 знака результата, а выход С суммы сумматора 9 соединен с выходом 23 результата устройства. Выход преобразователя 10 является выходом 24 модуля результата, а выход коммутатора 14 является выходом 25 результата логических операций устройства.

Назначение элементов НЕРАВНОЗНАЧНОСТЬ 3, 4 состоит в том, чтобы при необходимости менять знак любого из операндов на противоположный. Назначение преобразователей 7, 8, 10 прямого кода в дополнительный состоит в формировании дополнительного кода любого из операндов аппаратным путем за один такт, что обеспечивает экономию времени и оборудования. Функциональная схема двустороннего преобразователя прямого кода в дополнительный (или наоборот) приведена на фиг. 2 описания изобретения к авт. св. СССР N 1444753, кл. G 06 F 7/50, 1983. Назначение коммутаторов 5, 6 состоит в формировании в зависимости от выполняемой операции нечеткой логики либо прямого, либо инверсного значения операндов A, B. Назначение коммутатора 14 состоит в разделении результатов логических операций, подаваемых на выход 25 устройства. Коммутаторы 5, 6, 14 могут быть реализованы на стандартных микросхемах типа 531КП11; 555КП11.

Алгоритм работы устройства следующий. Исходные операции A и B, представленные в прямом коде, поступают в буферные регистры со своими знаками SA и SB. В зависимости от типа операции, задаваемого признаками y1 и y2, в устройстве выполняется модификация знаков операндов по правилу SA' SA⊕ y1; SB' SB⊕y2. Признаки y1, y2 задают следующие типы операций:

если (y1, y2) (0, 0), то C A + B, I C I=I A + B I, знаки операндов не изменяются;

если (y1, y2) (0, 1), то C A B, I C I= I A B I, знак операнда B инвертируется;

если (y1, y2) (1, 0), то C B A, IC I=IB A I, знак операнда A инвертируется.

При выполнении указанных операций на управляющие входы первого и второго коммутаторов подаются соответственно сигналы y3 0 и y4 0, что и обусловливает работу с прямыми значениями операндов A и B.

Операнды A и B с учетом произведенной модификации знаков преобразуются в дополнительный код, и на выходе сумматора получается результат С произведенной операции со своим знаком SC. После преобразования полученного дополнительного кода результата на выходе модуля результата устройства формируется прямой код модуля результата.

В основе выполнения операций нечеткой логики в базисе с ограниченными операциями лежат две базовые операции: C7 min (1,  +

+  ) и C8 max (0,

) и C8 max (0,

). Выбор базовой операции определяется совокупностью признаков y1, y2, а набор признаков y3, y4 определяет уже конкретный вид логической операции. Так, совокупность признаков (y1, y2) (0, 0) задает базовую операцию С7. Причем, если (y3, y4) (0, 0), то реализуется дизъюнкция D min (1, A + B);

). Выбор базовой операции определяется совокупностью признаков y1, y2, а набор признаков y3, y4 определяет уже конкретный вид логической операции. Так, совокупность признаков (y1, y2) (0, 0) задает базовую операцию С7. Причем, если (y3, y4) (0, 0), то реализуется дизъюнкция D min (1, A + B);

если (y3, y4) (1, 0), то реализуется импликация I1 min (1,  + B) min (1,1 A + B);

+ B) min (1,1 A + B);

если (y3, y4) (0, 1), реализуется импликация I2 min (1, A +  ) min (1,1 B + A);

) min (1,1 B + A);

если (y3, y4) (1, 1), то реализуется штрих Шеффера S min (1,  +

+  ) min (1- A + 1 B).

) min (1- A + 1 B).

Совокупность признаков (y1, y2) (0, 1) задает базовую операцию С8= max (0,

). Причем, если (y3, y4) (0, 0), то реализуется ограниченная разность Qmax (0, A B);

). Причем, если (y3, y4) (0, 0), то реализуется ограниченная разность Qmax (0, A B);

если (y3, y4) (0, 1), то реализуется конъюнкция K max (0, A  ) max (0, A (1 B));

) max (0, A (1 B));

если (y3, y4) (1, 0), то реализуется стрелка Пирса P max (0,  B) max (0, 1 A B).

B) max (0, 1 A B).

Результат операций нечеткой логики формируется на выходе третьего коммутатора устройства, являющемся выходом результата логических операций устройства.

Алгоритм работы преобразователя прямого двоичного кода числа в дополнительный (или наоборот) заключается в том, что все разряды исходного кода отрицательного числа разбиваются на два поля. Поле, содержащее крайнюю младшую единицу и следующие за ней младшие разряды, при преобразовании не изменяется. Поле, содержащее старшие по отношению к выделенной младшей единице разряды, при преобразовании изменяется путем инвертирования значений всех разрядов. В результате на выходе преобразователя формируется дополнительный (прямой) код, полученный из исходного (прямого дополнительного). При двустороннем преобразовании кода положительного числа все его разряды сохраняются без изменения.

Устройство работает следующим образом.

При необходимости реализации операций C2 A B, C5 I A B I на входы 18 и 19 подается двоичный код (0, 1), а на входы 20, 21 двоичный код (0, 0). На входы 15 и 16 подаются операнды A и B в прямом коде со своими знаками. При поступлении единичного сигнала на вход 17, разрешения записи происходит занесение исходных кодов операндов в регистры 1 и 2, после чего значащие разряды кодов операндов A и B через первые входы коммутаторов 5 и 6 соответственно поступают на выход коммутаторов и затем на информационные входы Х преобразователей 7 и 8. Знаковые разряды SA и SB операндов A и B поступают на первые входы соответствующих элементов НЕРАВНОЗНАЧНОСТЬ 3, 4. Так как y1 0 и y2 1, то знак SA проходит через элемент НЕРАВНОЗНАЧНОСТЬ 3 без изменения и поступает на знаковые входы S и SA соответственно преобразователя 7 и сумматора 9, а знак SB инвертируется элементом НЕРАВНОЗНАЧНОСТЬ 4 и поступает на знаковые входы S и SB соответственно преобразователя 8 и сумматора 9. Тем самым происходит настройка устройства на операцию С A B. На выходах преобразователей 7, 8 формируются значащие разряды дополнительных кодов операндов, которые поступают на информационные входы A и B сумматора 9. На выходах сумматора 9 формируются значащие разряды С и знак SС результата произведенной операции, которые подаются на выходы 23 и 22 устройства и на входы Х и S преобразователя 10, в результате чего на выходах преобразователя 10 формируются значащие разряды модуля I С I результата произведенной операции, которые подаются на выход 24 модуля результата.

При необходимости реализации операции C3 B A и C6 I B A I на входы 18 и 19 подается двоичный код (y1, y2) (1, 0). При этом знак SA инвертируется элементом НЕРАВНОЗНАЧНОСТЬ 3, а знак SB проходит через элемент НЕРАВНОЗНАЧНОСТЬ 4 без изменения, что и приводит к настройке устройства на требуемую операцию.

При необходимости реализация операций C1 A + B и C4 I A + B I на входы 18 и 19 подается двоичный код (0, 0). При этом знаки операндов SA и SB не изменяются.

При выполнении операций нечеткой логики, таких как дизъюнкия D min (1, A + B), импликация I1 min (1,  + B), импликация I2 min (1, A +

+ B), импликация I2 min (1, A +  ), штрих Шеффера S min (1,

), штрих Шеффера S min (1,  +

+  ), где базовой формулой является функция C7 min (1,

), где базовой формулой является функция C7 min (1,  +

+  ), на входы 18, 19 подается двоичный код (0, 0). Прямое или инверсное значение аргументов A и B на выходах коммутаторов 5 и 6 формируется подачей на входы 20, 21 соответствующих управляющих сигналов "0" или "1". Так, при реализации операции дизъюнкции D min (1, A + B) на входы 20 и 21 подается код (0, 0), что определяет прохождение через коммутаторы 5 и 6 и преобразователи 7 и 8 прямых кодов операндов A и B на соответствующие входы сумматора 9. Знаки операндов A и B при выполнении операций нечеткой логики всегда положительны, а значение операндов всегда не более единицы.

), на входы 18, 19 подается двоичный код (0, 0). Прямое или инверсное значение аргументов A и B на выходах коммутаторов 5 и 6 формируется подачей на входы 20, 21 соответствующих управляющих сигналов "0" или "1". Так, при реализации операции дизъюнкции D min (1, A + B) на входы 20 и 21 подается код (0, 0), что определяет прохождение через коммутаторы 5 и 6 и преобразователи 7 и 8 прямых кодов операндов A и B на соответствующие входы сумматора 9. Знаки операндов A и B при выполнении операций нечеткой логики всегда положительны, а значение операндов всегда не более единицы.

Знаковые разряды SA 0, SB 0 поступают без изменения на соответствующие знаковые входы сумматора 9. На выходах сумматора формируется сумма операндов C A + B. Возможны два варианта: С < 1 и С≥1.

Если С < 1, то на выходе SC сумматора 9 будет нулевой сигнал, который, инвертируясь элементом НЕ 11, разрешает прохождение результата C A + B с выхода С сумматора 9 через элементы И 131-13n и через элементы ИЛИ 121-12n группы устройства на первый вход коммутатора 14. Последний открывается по первому входу нулевым сигналом управления с входа 19, поэтому результат D C min (1, A + B)A + B поступает на вход 25 результата логических операций устройства.

Если С≥1, то в результате переполнения в знаковом разряде сумматора появляется единица, которая, инвертируясь, закрывает элементы И 131-13n, но поступает на первые входы элементов ИЛИ 121-12n, обусловливая на их выходах также единичный сигнал. В результате на выходе 25 коммутатора 14, открытом по первому входу сигналом y2 0, формируется код 0.11 1, соответствующий с точностью до младшего разряда значению результата D min (1, A + B) 1.

При выполнении операций импликации I1 min (1,  + B), импликации I2 min (1, A +

+ B), импликации I2 min (1, A +  ), штриха Шеффера S min (1,

), штриха Шеффера S min (1,  +

+  ) алгоритм работы устройства аналогичен, как и при выполнении рассмотренной выше операции дизъюнкции. Отличие состоит лишь в том, что для формирования на входах A и B сумматора 9 значения аргумента A или B при вычислении указанных операций на управляющие входы 20 и 21 коммутаторов 5 и 6 подаются соответственно коды (1, 0), (0, 1), (1, 1). При этом на входы сумматора 9 поступают соответственно наборы аргументов (

) алгоритм работы устройства аналогичен, как и при выполнении рассмотренной выше операции дизъюнкции. Отличие состоит лишь в том, что для формирования на входах A и B сумматора 9 значения аргумента A или B при вычислении указанных операций на управляющие входы 20 и 21 коммутаторов 5 и 6 подаются соответственно коды (1, 0), (0, 1), (1, 1). При этом на входы сумматора 9 поступают соответственно наборы аргументов ( , B), (A,

, B), (A,  ), (

), ( ,

,  ), что определяет на выходе 25 устройства результат соответственно I1, I2 или S.

), что определяет на выходе 25 устройства результат соответственно I1, I2 или S.

В основе следующих операций нечеткой логики: ограниченная разность Q max (0, A B), конъюнкции K max (0, A  ), стрелка Пирса P max (0,

), стрелка Пирса P max (0,  B) лежит вычисление базовой функции С8 max (0,

B) лежит вычисление базовой функции С8 max (0,

). Для ее реализации на входы 18, 19 подается двоичный код (0, 1), что определяет настройку устройства на операцию R

). Для ее реализации на входы 18, 19 подается двоичный код (0, 1), что определяет настройку устройства на операцию R

При этом работа устройства происходит как и в случае вычисления операций C2 A B и C5 I A B I. Если для реализации операции ограниченной разности на входы 20, 21 подается код (0, 0), что и определяет прямое значение аргументов A и B в функции С8, то для выполнения операции конъюнкции Kmax (0, A

При этом работа устройства происходит как и в случае вычисления операций C2 A B и C5 I A B I. Если для реализации операции ограниченной разности на входы 20, 21 подается код (0, 0), что и определяет прямое значение аргументов A и B в функции С8, то для выполнения операции конъюнкции Kmax (0, A  ) на входы 20, 21 подается код (0, 1), а для выполнения операции стрелки Пирса P max (0,

) на входы 20, 21 подается код (0, 1), а для выполнения операции стрелки Пирса P max (0,  B) на входы 20, 21 подается код (1, 0). При вычислении разности R

B) на входы 20, 21 подается код (1, 0). При вычислении разности R

возможны два варианта: R≥0 и R < 0.

возможны два варианта: R≥0 и R < 0.

Если R≥0, то на выходе SC сумматора 9 будет нулевой сигнал, который, инвертируясь элементом НЕ 11, обусловливает прохождение значащих разрядов кода числа R с выхода С сумматора 9 через элементы И 131-13n группы и через открытый по второму входу сигналов y2 1 коммутатор 14 на выход 25 устройства. На выходе 25 сформирован код числа C8 max (0, R) R. Если R < <0, то на выходе SC сумматора 9 будет единичный сигнал, который, инвертируясь элементом НЕ 11, запрещает прохождение через элементы 131-13n кода результата с выхода С сумматора 9 и обусловливает нулевое значение на выходах элементов И 131-13nгруппы, которое через коммутатор 14, открытый по второму входу сигналом y2 1, поступает на выход 25 устройства. В результате на выходе 25 устройства сформирован код числа C max (0, R) 0.

Задачей изобретения является реализация в устройстве наряду с вычислением функций C1 A + B, C2 A B, C3 B A, C4I A + BI, C5 I A B I C6 I B A I также дополнительно вычисления следующих функций нечеткой логики: дизъюнкции D min (1, A + B), импликации I1 min (1,1 A + B), импликации I2 min (1,1 B + A), штриха Шеффера S min (1,1 A + 1 B), ограниченной разности Q max (0, A B), конъюнкции K max (0, A + B 1) max (0, A (1 B)), стрелки Пирса P max (0,1 A B) max (0,  B), в результате чего расширяются функциональные возможности устройства.

B), в результате чего расширяются функциональные возможности устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сравнения | 1988 |

|

SU1541593A1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ЛОГИЧЕСКОЙ ИНФОРМАЦИИ | 1988 |

|

SU1826784A1 |

| Устройство для вычисления разности двух чисел | 1987 |

|

SU1444753A1 |

| Устройство для сравнения множеств | 1988 |

|

SU1525699A1 |

| Сумматор логарифмических кодов | 1990 |

|

SU1730619A1 |

| УСТРОЙСТВО ПРИНЯТИЯ НЕЧЕТКИХ РЕШЕНИЙ | 1993 |

|

RU2054708C1 |

| Устройство для вычитания | 1989 |

|

SU1654813A1 |

| Многовходовой знакоразрядный сумматор | 1982 |

|

SU1027716A1 |

| Устройство для обработки нечеткой информации | 1989 |

|

SU1619252A1 |

| Устройство для выполнения операций над расплывчатыми операндами | 1986 |

|

SU1451677A1 |

Изобретение относится к вычислительной технике и технической кибернетике и может быть использовано в специализированных процессорах для обработки нечеткой информации, при построении технических средств моделирования рассуждений и автоматизации принятия решений в нечетких условиях, при построении систем классификации и поиска информации. Технический результат достигается за счет расширения функциональных возможностей путем реализации дополнительно к функциям C1= A+B, C2= A-B, C3= B-A, C4= A+B, C5= A-B, C6= B-A следующих функций нечеткой логики: дизъюнкции D min(1, A + B), импликации I1= min(1,1-A+B) импликации I2= min(1,1-B+A) штриха Шеффера S min(1,1 A + 1 B) разности Q max(0, A B), конъюнкции K max(0, A + B 1), стрелки Пирса p max(0,1 A B). Устройство содержит два регистра 1 и 2, два элемента НЕРАВНОЗНАЧНОСТЬ 3 И 4, КОММУТАТОРЫ 5 И 6, ПРЕОБРАЗОВАТЕЛИ 7, 8 И 10 ПРЯМОГО КОДА В ДОПОЛНИТЕЛЬНЫЙ, СУММАТОР 9, ЭЛЕМЕНТ НЕ 11, группу из n элементов ИЛИ 121-12n, группу из элементов И 131-13n (n число разрядов операндов), коммутатор 14, входы 15, 16 операндов, вход 17 разрешения записи операндов, управляющие входы 18 21, выход 22 знака результата, выход 23 результата устройства, выход 24 модуля результата устройства, выход 25 результата логических операций устройства. 1 ил.

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЙ, содержащее первый и второй регистры операндов, три преобразователя прямого кода в дополнительный, два элемента НЕРАВНОЗНАЧНОСТЬ и сумматор, причем информационные входы регистров являются входами первого и второго операндов устройства, а вход разрешения записи операндов, входы управления знаком первого и второго операндов устройства, выход знака результата устройства, выход результата устройства соединены соответственно с входами разрешения записи регистров, первыми входами первого и второго элементов НЕРАВНОЗНАЧНОСТЬ, знаковым выходом сумматора и выходом суммы сумматора, первый знаковый вход которого соединен с выходом первого элемента НЕРАВНОЗНАЧНОСТЬ и управляющим входом первого преобразователя прямого кода в дополнительный, второй знаковый вход сумматора соединен с выходом второго элемента НЕРАВНОЗНАЧНОСТЬ и управляющим входом второго преобразователя прямого кода в дополнительный, выходы знакового разряда регистров первого и второго операндов соединены соответственно с вторыми входами первого и второго элементов НЕРАВНОЗНАЧНОСТЬ, первый и второй информационные входы сумматора соединены соответственно с выходами первого и второго преобразователей прямого кода в дополнительный, знаковый выход и выход суммы сумматора соединены соответственно с управляющим и информационным входами третьего преобразователя прямого кода в дополнительный, выход которого является выходом модуля результата устройства, отличающееся тем, что оно содержит три коммутатора, элемент НЕ, группу из n (где n число разрядов двоичного кода операндов) элементов И и группу из n элементов ИЛИ, причем выходы первого и второго коммутаторов соединены с информационными входами соответственно первого и второго преобразователей прямого кода в дополнительный, первые информационные входы и вторые информационные входы первого и второго коммутаторов соединены соответственно с прямыми и инверсными выходами значащих разрядов соответственно регистров первого и второго операндов, управляющие входы первого и второго коммутаторов являются входами управления видом соответственно первого и второго операндов устройства, знаковый выход сумматора соединен с первыми входами элементов ИЛИ группы и входом элемента НЕ, выход которого соединен с первыми входами элементов И группы устройства, второй вход i-го элемента И (где i=1,2,n) группы соединен с выходом i-го разряда выхода суммы сумматора, а выход i-го элемента И группы устройства соединен с вторым входом i-го элемента ИЛИ группы, выходы элементов ИЛИ группы и выходы элементов И группы соединены соответственно с информационными входами первой и второй групп третьего коммутатора, управляющий вход которого соединен с входом управления знаком второго операнда устройства, выход третьего коммутатора является выходом результата логических операций устройства.

| Устройство для вычисления разности двух чисел | 1987 |

|

SU1444753A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1995-08-20—Публикация

1992-08-28—Подача