Изобретение относится к вычислительной технике и может быть использовано для решения задач теории массового обслуживания.

Целью изобретения является расширение функциональных возможностей и повышение достоверности результатов анализа за счет исключения плюрального вотума при общем информационном входе.

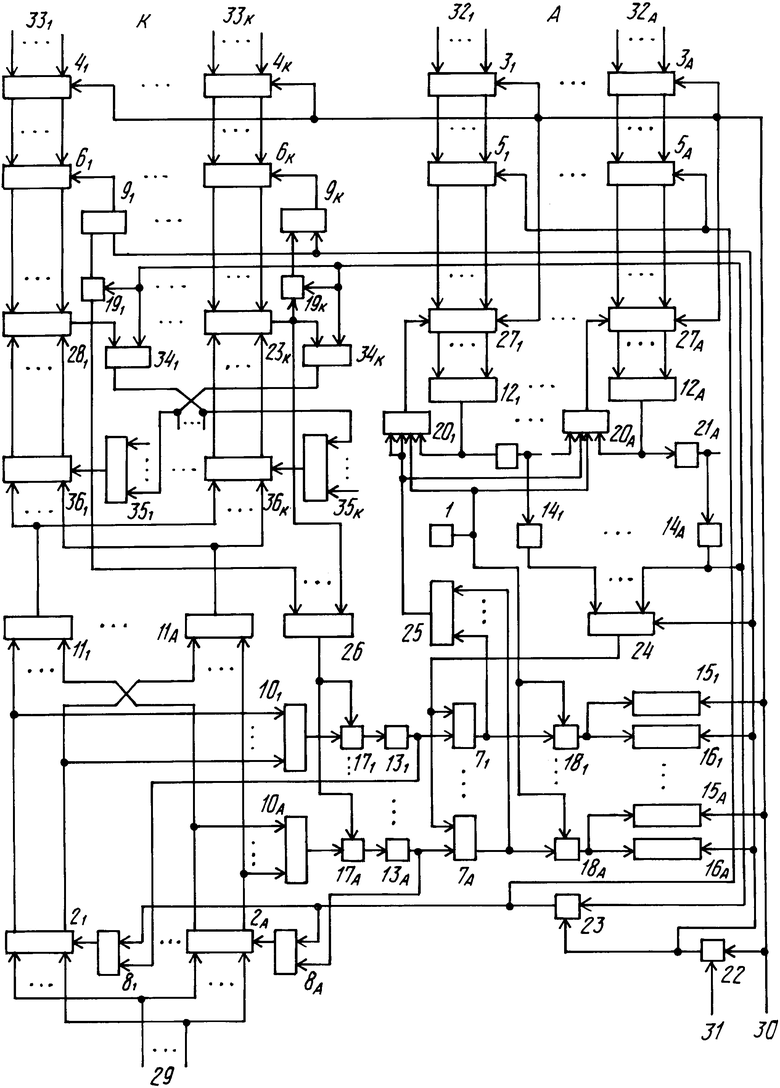

На чертеже представлена функциональная схема устройства.

Устройство содержит генератор 1 тактовых импульсов, группу из А дешифраторов 2, где А - количество альтернативных решений, первую группу из А регистров 3, вторую группу из К регистров 4, первую группу из А блоков элементов И 5, вторую группу из К блоков элементов И 6, первую группу из А триггеров 7, вторую группу из А триггеров 8, третью группу из К триггеров 9, первую группу из А элементов ИЛИ 10, вторую группу из А элементов ИЛИ 11, третью группу из А элементов ИЛИ 12, первую группу из А формирователей 13 импульсов, вторую группу из А формирователей 14 импульсов, первую группу из А счетчиков 15 импульсов, вторую группу из А счетчиков 16 импульсов, первую группу из А элементов И 17, вторую группу из А элементов И 18, третью группу из К элементов И 19, четвертую группу из А элементов И 20, группу из А элементов НЕ 21, первый 22, второй 23, третий 24, четвертый 25 и пятый 26 элементы ИЛИ, третью группу из А счетчиков 27 импульсов, группу из К блоков 28 сравнения, информационный вход 29, вход 30 начальной установки, вход 31 пуска, входы 32 задания альтернативных решений, входы 33 задания дополнительных кодов, четвертую группу из К триггеров 34 (К - число входов задания дополнительных кодов), группу из К элементов ИЛИ - НЕ 35 и третью группу из К блоков элементов И 36.

Устройство работает следующим образом.

Импульсом высокого потенциала по входу 30 устройство устанавливается в исходное состояние, при этом высокий потенциал с входа 30 поступает непосредственно на установочные входы (входы обнуления) счетчиков 15, регистров 3 и 4 и счетчиков 27. Через элемент ИЛИ 22 высокий потенциал с входа 30 поступает на входы обнуления счетчиков 16 и на входы установки в "1" триггеров 9 и через элементы ИЛИ 22 и 23 - на входы установки в "1" триггеров 8. В результате счетчики 15, 16 и 27 и регистры 3 и 4 оказываются обнуленными, а триггеры 8 и 9 - в единичном состоянии. Дополнительные коды (коды источников альтернатив) через соответствующие входы 33 фиксируются регистрами 4, а коды задания альтернативных решений через соответствующие входы 32 фиксируются регистрами 3.

После загрузки регистров 3 и 4 устройство готово к работе. Импульсом по входу 31 содержимое регистров 3 переписывается в счетчики 27. Альтернативные решения в (p+n)-разрядных кодах, где p - разрядность дополнительных кодов; n - разрядность альтернативных кодов, через входы 29 устройства поступают на информационные входы дешифраторов 2. Все дешифраторы, исключая тот, код срабатывания которого соответствует одному из кодов текущего альтернативного решения, сохраняют на своих выходах низкие нулевые потенциалы, а на выходе сработавшего дешифратора устанавливает код j-го источника сообщений (j = 1,...,K).

Код j-го источника с выхода дешифратора 2 генерирует на выходе i-го (i= 1,...,A) элемента ИЛИ 10 высокий потенциал и через элемент ИЛИ 11 поступает через блоки элементов И 36 на вторые входы всех блоков 28 сравнения. Так как на выходах триггеров 9 установлены высокие потенциалы, дополнительные коды с выходов регистров 4 через блоки элементов И 6 поступают на первые входы блоков 28 сравнения. Блоки 28 сравнения сравнивают коды регистров 4 с кодом на выходах элементов ИЛИ 11. По результатам сравнения на выходах блоков 28 сравнения сохраняются нулевые потенциалы при неравенстве кодов на их входах и устанавливаются высокие потенциалы в противном случае. Так как код j-го источника зафиксирован только в одном регистре 4, то высокий потенциал устанавливается только на выходе соответствующего ему блока 28 сравнения.

Единичный потенциал с выхода j-го блока 28 через элемент ИЛИ 26 поступает на вторые входы элементов И 17. Так как на первом входе i=го элемента И 17 с выхода i-го элемента ИЛИ 10 уже имеется высокий потенциал, то и на выходе i-го элемента И 17 устанавливается высокий потенциал, которым через i-й формирователь 13 i-й триггер 7 переводится в единичное состояние, а i-й триггер 8 - в нулевое. При содержимом любого счетчика 27, равном нулю, на всех его разрядных выходах присутствуют нулевые потенциалы, а при содержимом, отличном от нуля, хотя бы один из его прямых разрядных выходов оказывается под высоким потенциалом, тогда на выходе элемента ИЛИ 12 в зависимости от содержимого счетчика 27 может быть нулевой или единичный потенциал. Так как в состоянии готовности устройства к работе содержимое всех счетчиков 27 отличается от нуля, то на выходах всех элементов ИЛИ 12 устанавливаются высокие потенциалы, тогда и вторые входы элементов И 20 и входы элементов НЕ 21 оказываются под высоким потенциалом, а на выходах элементов НЕ 21 присутствуют низкие нулевые потенциалы.

Высоким потенциалом с единичного выхода i-го триггера 7 через элемент ИЛИ 25 открывается элемент И 20. По первой в порядке поступления альтернативе открываются i-й элементы И 18 и первый элемент И 20 и импульсы генератора 1 поступают на счетный вход i-х счетчиков 15 и 16 и первого счетчика 27. При этом с каждым импульсом содержимое i-х счетчиков 15 и 16 увеличивается на единицу, а содержимое первого счетчика 27 уменьшается на единицу. В момент обнуления первого счетчика 27 на выходе первого элемента ИЛИ 12 устанавливается низкий потенциал, при этом первый элемент И 20 закрывается, на выходе первого элемента НЕ 21 устанавливается высокий потенциал, передним фронтом которого открывается второй элемент И 20. Через первый формирователь 14 и элемент ИЛИ 24 i-й триггер 7 обнуляется, на его единичном выходе устанавливается нулевой потенциал, i-й элемент И 18 закрывается, а i-е счетчики 15 и 16 затормаживаются. Параллельно со срабатыванием первого элемента И 20 и i-го элемента И 17 через j-й элемент И 19 j-й триггер 9 обнуляется и содержимое j-го регистра 4 на входы j-го блока 28 не поступает. Высоким потенциалом с выхода j-го блока 28 j-й триггер 34 устанавливается в единичное состояние, на выходах всех, кроме j-го, элементов ИЛИ-НЕ 35 устанавливаются низкие потенциалы, на выходе j-го элемента ИЛИ-НЕ 35 сохраняется высокий потенциал, что в дальнейшем препятствует обработке решений от источников с кодами, отличными от кода j-го источника. Высоким единичным потенциалом с выхода i-го формирователя 13 обнуляется i-й триггер 8, чем достигается невозможность повтоpной реакции устройства на i-е решение от j-го источника информации.

При поступлении второго в порядке следования альтернативного решения работа устройства повторяется. С прибытием последнего (А-го) решения срабатывает А-й формирователь 14, импульсом высокого потенциала с его выхода все триггеры 8 вновь устанавливаются в единичное состояние и через блоки элементов И 5 содержимое регистров 3 фиксируется счетчиками 27. После обработки альтернативных решений содержимое счетчиков 15 и 16 отражает интегральные оценки по сумме всех решений, поступивших на информационные входы устройства.

Если альтернативные решения принимаются по нескольким критериям или возникает необходимость в неоднократных оценках, то повторно пуск устройства осуществляется по входу 31, при этом содержимое счетчиков 15 и регистров 3 и 4 сохраняется, счетчики 16 обнуляются, триггеры 8 и 9 устанавливаются в единичное состояние, элементы И 5 и 6 открываются и содержимое регистров 3 и 4 поступает на входы блоков 28 и счетчиков 27. В счетчиках 15 фиксируются интегральные оценки по всем критериям альтернативных решений, а в счетчиках 16 - дифференциальные по анализируемому критерию оценки альтернативных решений.

Таким образом, устройство обеспечивает ввод информации через общий вход, исключает плюральный вотум как по источникам информации, так и по альтернативным решениям, что обеспечивает ему расширение функциональных возможностей и повышение достоверности результатов анализа.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сортировки двоичных чисел | 1982 |

|

SU1049900A1 |

| Устройство для анализа альтернативных решений | 1988 |

|

SU1688260A1 |

| Устройство для моделирования каналов передачи дискретной информации | 1982 |

|

SU1049915A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Устройство для моделирования марковских потоков сигналов | 1983 |

|

SU1088004A1 |

| Устройство для контроля логических блоков | 1983 |

|

SU1160414A1 |

| Устройство для моделирования распределения приоритетов | 1986 |

|

SU1352499A1 |

| Устройство для сопряжения дискретных датчиков с электронной вычислительной машиной | 1982 |

|

SU1024898A2 |

| Устройство для моделирования канала передачи дискретной информации | 1983 |

|

SU1088006A1 |

| Устройство для контроля физического состояния биологических объектов | 1986 |

|

SU1336034A1 |

Изобретение относится к вычислительной технике и может быть использовано для решения задач теории массового обслуживания. Устройство содержит генератор тактовых импульсов, группу из А дешифраторов, группу из А регистров, вторую группу из K регистров, первую группу из А блоков элементов И, вторую группу из K блоков элементов И, первую группу из А триггеров, вторую группу А триггеров, третью группу из K триггеров, первую, вторую и третью группы из А элементов ИЛИ, первую и вторую группы из А формирователей импульсов, первую и вторую группы из А счетчиков импульсов, первую и вторую группы из А элементов И, третью группу из K элементов И, четвертую группу из А элементов И, группу из А элементов НЕ, с первого по пятый элементы ИЛИ, третью группу из А счетчиков импульсов, группу из K блоков сравнения, информационный вход, вход начальной установки, вход пуска, входы задания альтернативных решений, входы задания дополнительных кодов, четвертую группу из K триггеров, группу их K элементов ИЛИ-НЕ, третью группу из K блоков элементов И. 1 ил.

УСТРОЙСТВО ДЛЯ АНАЛИЗА АЛЬТЕРНАТИВНЫХ РЕШЕНИЙ, содержащее генератор тактовых импульсов, группу из A дешифраторов, первую группу из A регистров, вторую группу из K регистров, первую группу из A блоков элементов И, вторую группу из K блоков элементов И, первую группу из A триггеров, вторую группу из A триггеров, третью группу из K триггеров, первую группу из A элементов ИЛИ, вторую группу из A элементов ИЛИ, третью группу из A элементов ИЛИ, первую и вторую группы из A формирователей импульсов, первую и вторую группы из A счетчиков, первую и вторую группы из A элементов И, третью группу из K элементов И, четвертую группу из A элементов И, группу из A элементов НЕ, пять элементов ИЛИ, третью группу из A счетчиков импульсов, группу из K блоков сравнения, причем информационный вход устройства соединен поразрядно с информационными входами всех дешифраторов, выходы i-го (где i=1,...,A) дешифратора группы соединены соответственно с входами i-х элементов ИЛИ первой и второй групп, выход i-го элемента ИЛИ первой группы соединен с первым входом i-го элемента И первой группы, выход которого соединен с входом i-го формирователя импульсов первой группы, выход которого соединен с входом установки в "1" i-го триггера первой группы и с входом установки в "0" i-го триггера второй группы, выход которого соединен с управляющим входом i-го дешифратора группы, выход i-го триггера первой группы соединен с первым входом i-го элемента И второй группы, выход которого соединен со счетными входами i-х счетчиков первой и второй групп, входы установки всех счетчиков первой группы соединены с первым входом первого элемента ИЛИ и с входом начальной установки устройства, вход пуска которого соединен с вторым входом первого элемента ИЛИ, выход которого соединен с входом установки i-го счетчика второй группы и первым входом второго элемента ИЛИ, выход которого соединен с входом установки в "1" i-го триггера второй группы и с первым входом i-го блока элементов И первой группы, входы с второго по n-й которого соединены соответственно с разрядными выходами i-го регистра первой группы, информационные входы которого соединены с входами задания альтернативных решений устройства, входы задания дополнительных кодов которого соединены с информационными входами j-го (где j=1,...,K) регистра второй группы, выходы которого соединены с входами с второго по n-й j-го блока элементов И второй группы, первый вход которого соединен с выходом j-го триггера третьей группы, вход установки в "0" которого соединен с выходом первого элемента ИЛИ и первым входом третьего элемента ИЛИ, выход которого соединен с входом установки в "0" j-го триггера первой группы, выход которого соединен с j-м входом четвертого элемента ИЛИ, выходы с второго по n-й третьего элемента ИЛИ соединены соответственно с выходами формирователей второй группы и первым входом - с первыми входами всех элементов И третьей группы, выход j-го элемента И третьей группы соединен с входом установки в "0" j-го триггера третьей группы, выходы j-го блока элементов И второй группы соединены с первой группой входов j-го блока сравнения, выход которого соединен с вторым входом j-го элемента И третьей группы и с j-м входом пятого элемента ИЛИ, выход которого соединен с вторыми входами всех элементов И первой группы, выходы J-го блока элементов И первой группы соединены с информированными входами i-го счетчика третьей группы, входы которого соединены с входами i-го элемента ИЛИ третьей группы, выход которого соединен с вторым входом i-го элемента И четвертой группы и входом i-го элемента НЕ группы, выход которого соединен с входом i-го формирователя импульсов второй группы, третий вход i-го элемента И четвертой группы соединен с выходом генератора тактовых импульсов, четвертый вход i-го элемента И четвертой группы соединен с выходом четвертого элемента ИЛИ, а первый вход i-го элемента И четвертой группы соединен с выходом (i-1)-го элемента НЕ группы, тактовые входы регистров первой и второй групп соединены с входом начальной установки устройства, отличающееся тем, что в устройстве введены четвертая группа из K триггеров, группа из K элементов ИЛИ - НЕ и третья группа из K блоков элементов И, причем выход i-го элемента ИЛИ второй группы соединен с a-м (где a= 1, ...,n) входом блока элементов И третьей группы, выходы j-го блока элементов И третьей группы соединены с второй группой входов j-го блока сравнения группы, (n+1)-й вход j-го блока элементов И третьей группы соединен с выходом j-го элемента ИЛИ - НЕ группы, входы которого соединены соответственно с выходами триггеров четвертой группы, вход установки в "1" j-го триггера четвертой группы соединен с входом j-го блока сравнения группы, а вход установки в "0" j-го триггера четвертой группы соединен с выходом A-го формирователя импульсов второй группы.

| Устройство для анализа альтернативных решений | 1988 |

|

SU1688260A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Пуговица для прикрепления ее к материи без пришивки | 1921 |

|

SU1992A1 |

Авторы

Даты

1994-08-30—Публикация

1988-07-11—Подача