Изобретение относится к области электроники (в том числе микроэлектроники), более конкретно - к цифровым логическим устройствам, использующим принцип термодинамической обратимости (реверсивности), и может быть использовано в логических блоках вычислительных, измерительных и других устройств обработки информации.

В реверсивных логических устройствах достигается резкое снижение потребляемой энергии за счет использования принципа термодинамической обратимости. Их действие основано на использовании управляемых напряжений питания. При повышении питающего напряжения группа логических вентилей, подключенных к данной шине питания, потребляет энергию от источника питания, запасая ее в нагрузочной емкости. При снижении питающего напряжения большая часть запасенной энергии возвращается в источник питания. Эффективная работа реверсивных логических вентилей возможна при условии, что процессы перезаряда нагрузочной емкости близки к термодинамически равновесным. Это условие обеспечивается достаточно медленным (по сравнению с собственной постоянной времени вентиля) изменением питающих напряжений. Наиболее просты по конструкции логические устройства динамического типа, в которых в течение части рабочего цикла информация сохраняется на некоторых емкостях (запоминающих емкостях). Обычно в качестве запоминающей емкости используется нагрузочная емкость вентиля. Динамические устройства синхронизируются тактовыми импульсами, которые поступают по тактовым шинам. В реверсивных логических устройствах тактовые импульсы одновременно являются импульсами питания.

Известны реверсивные логические устройства динамического тина на полевых транзисторах с изолированным затвором, содержащие n тактовых шин и матрицу базовых логических вентилей, каждый из которых включает блок логических транзисторов с входными электродами (затворами), выходным электродом и электродом питания и запоминающий конденсатор, включенный между выходным электродом и областью нулевого потенциала - "землей"[1-3].

Недостатком устройства, предложенного в [1] , является необходимость использования в базовых логических вентилях внутренних запоминающих элементов (триггеров) на основе комплементарных (n- и р-канальных) транзисторов. Это усложняет конструкцию вентилей (N-входовой вентиль содержит 2N+2 транзисторов) и технологический процесс их изготовления, в результате чего снижается плотность компоновки вентилей на кристалле интеральной микросхемы (ИМС), а в конечном счете повышается стоимость устройства. Кроме того, для управления триггером требуются парафазные логические сигналы, что вдвое увеличивает число сигнальных шин.

Устройство, предложенное в [2], использует в базовых вентилях транзисторы с каналом одного типа проводимости, однако в логической цепи необходимо чередовать вентили на основе n-канальных и р-канальных транзисторов. Поэтому в устройстве, содержащем такие вентили, также необходимо использование комплементарных транзисторов. Кроме того, для выполнения операции инверсии необходимо введение в базовый вентиль дополнительного каскада, что существенно снижает энергетическую эффективность вентиля и усложняет его конструкцию (N-входовые вентили НЕ-ИЛИ и НЕ-И содержат 3N+3 и 4N транзисторов).

Необходимость использования комплементарных транзисторов в указанных логических устройствах снижает их быстродействие, поскольку р-канальные транзисторы обладают меньшим быстродействием, чем n-канальные.

Реверсивное логическое устройство, предложенное в [3], не требует использования комплементарных транзисторов, однако также является сравнительно сложным (3N+2 элементов в N-входовом вентиле), так как для выполнения операции инверсии необходимо введение в базовый вентиль дополнительного каскада. При этом внутренняя емкость вентиля перезаряжается нереверсивным образом, что снижает его энергетическую эффективность. Кроме того, базовые вентили недостаточно надежны, т.к. требуют соблюдения жестких соотношений для паразитных емкостей.

Наиболее близким по технической сущности и достигаемому эффекту является реверсивное логическое устройство динамического типа на полевых транзисторах с изолированным затвором, например, МДП-транзисторах, содержащее четыре тактовых шины 1 и матрицу базовых логических вентилей 2, каждый из которых включает блок логических транзисторов 3 с входными электродами затворов 4, выходным электродом 5 и электродом питания 6, выпрямляющий элемент 7, включенный между выходным электродом блока логических транзисторов и тактовой шиной, и запоминающий конденсатор 8, включенный между выходным электродом и областью нулевого потенциала -"землей" [4]. На фиг.1а показана структурная схема устройства. Базовые логические вентили i-го, n+i-го, 2n+i-го и т.д., где 1≤i≤n-1, столбцов матрицы соединены с i-й тактовой шиной, а выходные электроды вентилей j-го столбца матрицы соединены с входными электродами вентилей j+1-го или j+1+k-го столбца матрицы, где k>1 - целое число. Для правильной работы в логической цепи должны чередоваться вентили n- и р-типов, выполненные на n-канальных и р-канальных транзисторах соответственно.

Принципиальные электрические схемы базовых логических вентилей n- и р-типов представлены на фиг.1а и 1б. Если, например, к i-й тактовой шине подключен вентиль n-типа, то к i+1-й тактовой шине должен быть подключен вентиль n-типа.

Работа устройства поясняется временными диаграммами на фиг.2. По тактовым шинам 1 со сдвигом на 1/4 периода поступают 4-фазные тактовые импульсы φi (штриховые линии). Сплошными линиями показаны логические сигналы V2 и V3 на выходах логических вентилей р- и n-типов, подключенных к 2-й, 3-й тактовым шинам. Предполагается, что к 3-й тактовой шине подключен простой логический инвертор. При повышении питающего напряжения φ3 напряжение V3, повышается током через выпрямляющий элемент до уровня VH=Vdd-VD, где Vdd - амплитуда тактовых импульсов, VD - падение напряжения на выпрямляющем элементе 7 (фиг.1б). Если на выходе предыдущего вентиля р-типа установлено напряжение V2 низкого уровня (логический 0), то при снижении питающего напряжения φ3 логический транзистор в инверторе n-типа остается закрытым, и выходное напряжение V3 на накопительном конденсаторе сохраняется на высоком уровне VH (логическая 1). В противном случае при снижении питающего напряжения выходное напряжение V3 через открытый логический транзистор устанавливается на низком уровне vL=0. Аналогично работают вентили р-типа, где предзаряд нагрузочной емкости до напряжения низкого уровня vL=VD происходит при снижении питающего напряжения φ2, а повышение выходного напряжения V2 через открытый логический транзистор до высокого уровня VH=Vdd - при повышении питающего напряжения φ2.

Описанное логическое устройство имеет следующие недостатки.

1. Понижение быстродействия, обусловленное необходимостью использования р-канальных транзисторов.

2. Усложнение технологического процесса изготовления вентилей, понижение плотности их компоновки на кристалле ИМС и, в конечном счете, повышение стоимости изделия, обусловленные необходимостью использования комплементарных (n- и р-канальных) транзисторов и создания специальных "карманов" n-типа на р-подложке для размещения р-канальных транзисторов.

3. Снижение помехоустойчивости, обусловленное чередованием вентилей на n- и р-канальных транзисторах в логической цепи. Закрытое состояние логического транзистора в вентиле n-типа поддерживается низким уровнем выходного напряжения вентиля р-типа VL= VD. При этом запас по напряжению запирания логического транзистора составляет Vtn=VD, где Vtn - пороговое напряжение n-канального транзистора. Аналогично закрытое состояние логического транзистора в вентиле р-типа обеспечивается с запасом |Vtp|_VD, где Vtp - пороговое напряжение р-канального транзистора. Таким образом, помехоустойчивость вентилей оказывается сниженной на величину VD.

Целью изобретения является повышение быстродействия и помехоустойчивости логического устройства, а также упрощение технологического процесса его изготовления в микроэлектронном исполнении, повышение плотности компоновки элементов в матрице базовых логических вентилей и, в конечном счете, - снижение стоимости устройства.

Поставленная цель достигается за счет того, что в реверсивное логическое устройство динамического типа на полевых транзисторах с изолированным затвором, содержащее n тактовых шин, по которым со сдвигом на 1/n периода поступают n-фазные тактовые импульсы, и матрицу базовых логических вентилей, каждый из которых включает блок логических транзисторов с входными электродами затворов, выходным электродом и электродом питания, выпрямляющий элемент, включенный между выходным электродом блока логических транзисторов и тактовой шиной, и запоминающий конденсатор, включенный между выходным электродом и областью нулевого потенциала - "землей", причем базовые логические вентили i-го, n+i-го, 2n+i-го и т.д., где 1≤i≤n-1, столбцов матрицы соединены с i-й тактовой шиной, а выходные электроды вентилей j-го столбца матрицы соединены с входными электродами вентилей j+1-го или j+1+k-го, где k>1 целое число, столбца матрицы, введены n вспомогательных тактовых шин, причем на i-ю вспомогательную тактовую шину поступают вспомогательные тактовые импульсы, сдвинутые по фазе относительно тактовых импульсов на i-й тактовой шине, а в каждый из базовых логических вентилей i-го, n+i-гo, 2n+i-го и т.д. , где 1≤i≤n-1, столбцов матрицы введен изолирующий транзистор, включенный между электродом питания блока логических транзисторов и i-й тактовой шиной, затвор которого соединен с i-й вспомогательной тактовой шиной.

Новизна заявляемого изобретения обусловлена тем, что в логическое устройство динамического типа на полевых транзисторах с изолированным затвором введены вспомогательные тактовые шины и изолирующие транзисторы, включенные между электродом питания логических транзисторов базовых логических вентилей и тактовыми шинами, затворы которого соединены со вспомогательными тактовыми шинами.

Введение вспомогательных тактовых шин и изолирующих транзисторов позволяет повысить быстродействие и помехоустойчивость логического устройства, а также упростить технологический процесс его изготовления в микроэлектронном исполнении, повысить плотность компоновки элементов в матрице базовых логических вентилей и, в конечном счете, снизить стоимость устройства по сравнению с прототипом.

Это обусловлено возможностью использования в последовательно соединенных базовых вентилях только одного типа полевых транзисторов - n-канальных, в результате чего быстродействие повышается за счет более высокого быстродействия n-канальных транзисторов по сравнению с р-канальными, технологический процесс изготовления устройства упрощается за счет исключения дополнительных операций, необходимых для создания р-канальных транзисторов, плотность компоновки элементов повышается за счет исключения специальных "карманов" n-типа на р-подложке, в которых располагаются р-канальные транзисторы, а помехоустойчивость устройства повышается за счет увеличения запаса по напряжению запирания логических транзисторов в базовых вентилях.

В заявляемом решении изолирующие транзисторы, подключенные к блокам логических транзисторов, и вспомогательные тактовые шины используются совместно. Только их взаимосвязь обеспечивает получение положительного эффекта - возможности использования в реверсивном логическом устройстве динамического типа на полевых транзисторах с изолированным затвором только вентилей на n-канальных транзисторах. В науке и технике совместного использования данных отличительных признаков не выявлено. Поэтому можно сделать вывод о соответствии заявляемого решения критерию "изобретательский уровень".

Сущность изобретения поясняется чертежами.

На фиг. 1 представлено реверсивное логическое устройство динамического типа с на полевых транзисторах с изолированным затвором (прототип): а - структурная схема; б - принципиальная электрическая схема базового логического вентиля n-типа; в - принципиальная электрическая схема базового логического вентиля р-типа, где 1 - тактовые шины, 2 - базовые логические вентили, 3 - блоки логических транзисторов, 4 - входные электроды затворов, 5 - выходные электроды, 6 - электроды питания, 7 - выпрямляющие элементы, 8 - запоминающие конденсаторы.

На фиг. 2 представлены временные диаграммы тактовых импульсов φi (штриховые линии) и логических сигналов V2, V3 (сплошные линии) на выходах логических вентилей р- и n-типов, подключенных к 2-й и 3-й тактовым шинам, для реверсивного логического устройства-прототипа.

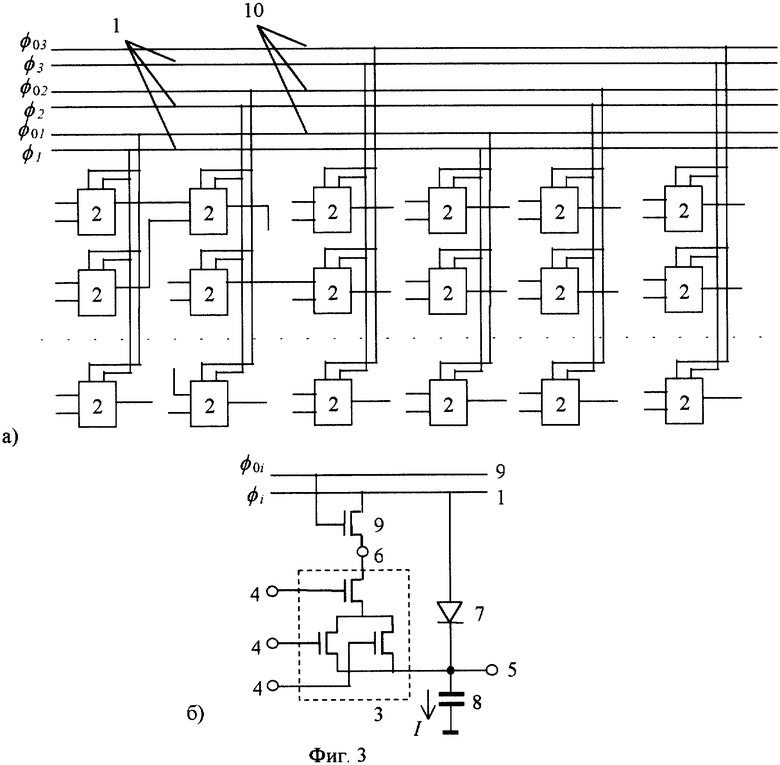

На фиг. 3 представлено заявляемое реверсивное логическое устройство динамического типа на полевых транзисторах с изолированным затвором: а - структурная схема; б - принципиальная электрическая схема базового логического вентиля, где 1 - тактовые шины, 2 - базовые логические вентили, 3 - блок логических транзисторов, 4 - входные электроды затворов, 5 - выходной электрод, 6 - электрод питания, 7 - выпрямляющий элемент, 8 - запоминающий конденсатор, 9 - вспомогательные тактовые шины, 10 - изолирующий транзистор.

На фиг.4 представлены временные диаграммы тактовых импульсов φi на тактовых шинах 1 (сплошные линии) и вспомогательных тактовых импульсов φ0i на вспомогательных тактовых шинах 9 (штриховые линии) для заявляемого реверсивного логического устройства с 3-фазным (а) и 2-фазным (б) питанием.

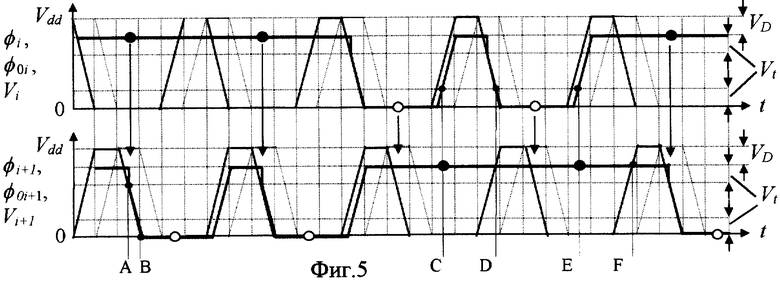

На фиг.5 представлены временные диаграммы тактовых импульсов φ0i, φ0i+1 (штриховые линии), вспомогательных тактовых импульсов φ0i, φ0i+1 (штриховые линии) и выходных сигналов V1, V2 (жирные линии) базовых вентилей, подключенных к 1-й и 2-й тактовым шинам, для 3-фазного питания.

На фиг.6 представлена принципиальная электрическая схема базового логического вентиля с дополнительным инверсным выходом.

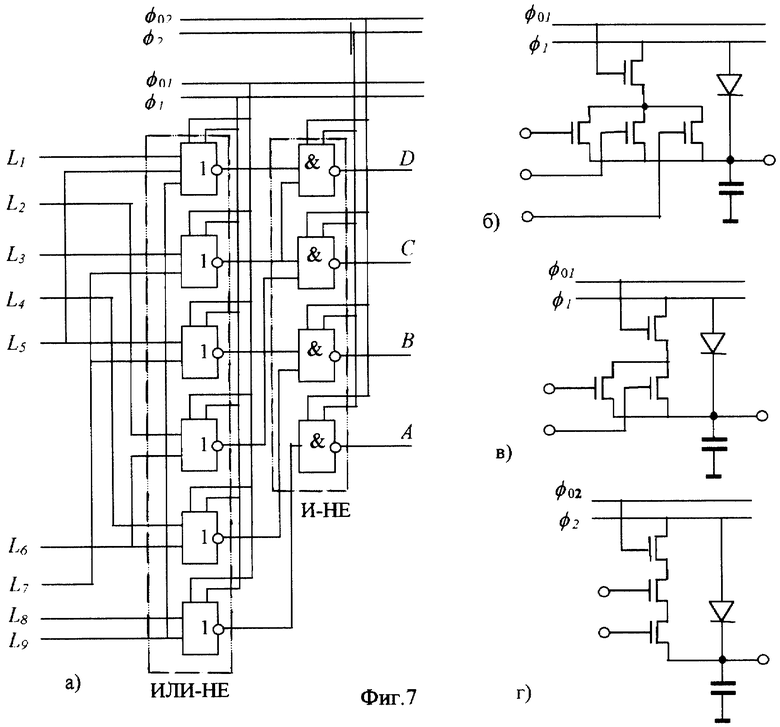

На фиг.7 представлено заявляемое реверсивное логическое устройство динамического типа на полевых транзисторах с изолированным затвором, выполняющее функции преобразователя десятичного кода в десятичный бинарный код: а - структурная схема; б, в, г - принципиальные электрические схемы вентилей 3ИЛИ-НЕ (б), 2ИЛИ-НЕ (в) и 2И-НЕ (г).

Заявляемое реверсивное логическое устройство динамического типа на полевых транзисторах с изолированным затвором (фиг.1) содержит n тактовых шин 1, матрицу базовых логических вентилей 2, каждый из которых включает блок логических транзисторов 3 с входными электродами затворов 4, выходным электродом 5 и электродом питания 6, выпрямляющий элемент 7, запоминающий конденсатор 8 и изолирующие транзисторы 9, а также n вспомогательных тактовых шин 10, причем каждой 1-й тактовой шине соответствует i-я вспомогательная тактовая шина. В каждом базовом логическом вентиле 2 запоминающий конденсатор 8 включен между выходным электродом 5 и областью нулевого потенциала - "землей". Базовые логические вентили i-го, n+i-го, 2n+i-го и т.д. столбцов матрицы, где 1≤i≤n-1, соединены с i-й тактовой шиной 1 и i-й вспомогательной тактовой шиной 10 таким образом, что выпрямляющий элемент 7 включен между выходным электродом 5 блока логических транзисторов 3 и тактовой шиной 1, изолирующий транзистор 9 включен между выходным электродом 5 и тактовой шиной 1, а его затвор соединен со вспомогательной тактовой шиной 10. Выходные электроды 5 вентилей j-го столбца матрицы соединены с входными электродами 4 вентилей j+1-го или j+1+k-го столбца матрицы, где k>1 - целое число.

По тактовым шинам 1 поступают n-фазные тактовые импульсы, причем тактовые импульсы на каждой i+1-й шине отстают по фазе на l/n периода от тактовых импульсов на i-й шине. По вспомогательным тактовым шинам 10 поступают n-фазные вспомогательные тактовые импульсы, причем вспомогательные тактовые импульсы на i-й вспомогательной тактовой шине 10 отстают по фазе от тактовых импульсов на i-й тактовой шине 1 примерно на время фронта.

В качестве логических транзисторов могут использоваться любые полевые транзисторы с изолированным затвором и индуцированным каналом (для n-канальных транзисторов пороговое напряжение Vt>0, для р-канальных транзисторов пороговое напряжение Vt<0). При использовании вентиля в составе кремниевой ИМС целесообразно использовать n-канальные МДП-транзисторы. В случае использования n-канальных логических транзисторов катод выпрямляющего элемента 7 соединен с выходным электродом 5, а анод - с тактовой шиной 1; в случае использования р-канальных логических транзисторов полярность включения выпрямляющего элемента 7 обратная. Соединение логических транзисторов внутри блока 3 соответствует логическому дереву, реализующему заданную логическую функцию. Например, параллельное соединение логических транзисторов реализует логическую функцию ИЛИ-НЕ, последовательное - логическую функцию И-НЕ, а параллельно-последовательное, показанное на фиг. 3б, - логическую функцию И-2ИЛИ-НЕ.

В качестве выпрямляющего элемента 7 может быть использован диод на основе полупроводникового р-n перехода, выпрямляющий контакт металл-полупроводник (диод Шоттки) или МДП-транзистор с объединенными электродами стока и затвора. При использовании вентиля в составе кремниевой ИМС целесообразно использовать диод Шоттки или n-канальный МДП-транзистор, идентичный логическим транзисторам. В последнем случае остаточное прямое напряжение VD на выпрямляющем элементе 7 равно абсолютной величине порогового напряжения транзистора Vt.

В качестве запоминающего конденсатора 8 может быть использован конденсатор любой конструкции, либо паразитная емкость, включающая собственную выходную емкость вентиля и емкости соединительных трактов между выходным электродом вентиля 5 и входными электродами 4 следующих вентилей в логической цепи. При использовании вентиля в составе кремниевой ИМС в качестве запоминающего конденсатора 8 может быть использована суммарная емкость сток-подложка логических транзисторов и емкости соединительных трактов. В этом случае отпадает необходимость создания специальной шины нулевого потенциала - "земли".

В заявляемом логическом устройстве могут быть использованы трехфазные (n= 3) или двухфазные (n=2) сдвоенные тактовые импульсы - основные тактовые импульсы φi (импульсы питания) и вспомогательные тактовые импульсы φ0i. Временные диаграммы тактовых импульсов φi на тактовых шинах 1 (сплошные линии) и φ0i на вспомогательных тактовых шинах 10 (штриховые линии) для трех- и двухфазного питания представлены на фиг 4а и 4б. Период импульсов питания φ включает фазу предзаряда а запоминающей емкости С (нарастание питающего напряжения φ от нулевого уровня до максимального значения Vdd), фазу покоя b (φ=Vdd), фазу операции с (спад питающего напряжения до нуля) и фазу хранения d (φ = 0). Вспомогательные тактовые импульсы имеют ту же форму, что и импульсы питания, и задержаны относительно них на 1/6 периода (для трехфазного питания) или на 1/8 периода (для двухфазного питания).

Работу вентиля на примере цепи инверторов поясняет фиг.5.

На фиг. 5 представлены временные диаграммы выходных напряжений Vi, Vi+1 двух последовательных вентилей, подключенных к i-й и i+1-й тактовым шинам, на которые подаются тактовые импульсы φi φ0i и φi+1 φ0i+1 соответственно. На временных диаграммах фиг.5 предполагается, что длительности фронтов и срезов тактовых импульсов велики по сравнению с собственной постоянной времени вентиля (это допущение является необходимым условием работы всех реверсивных логических вентилей).

В фазе предзаряда а независимо от входного сигнала запоминающий конденсатор емкостью С заряжается током через выпрямляющий элемент 7 (фиг.3б) до максимального напряжения Vdd - VD, соответствующего уровню логической 1:

VH=Vdd-VD

Это значение напряжения Vi+1 сохраняется на емкости С в течение фазы покоя b. Если в фазе операции с на вход поступил сигнал логической 1 (Vi= VH), то после снижения питающего напряжения до уровня φ2 = Vdd-Vt-VD открывается логический транзистор вентиля, подключенного к i+1-м шинам, и его выходное напряжение Vi+1 скачком снижается до этого же уровня. Далее емкость С разряжается через открытый логический транзистор и открытый изолирующий транзистор до напряжения логического 0

VL=0,

которое сохраняется на емкости С в фазе хранения до начала следующего цикла. При этом большая часть энергии, накопленной в емкости С, возвращается в источник питания.

Если в фазе операции с на вход поступил сигнал логического 0 (V1=VL), то высокий уровень напряжения Vi+1=VH сохраняется на емкости С в течение фаз операции и хранения до начала следующего цикла.

Таким образом, входная информация воспринимается вентилем в фазе операции, передается на следующий вентиль в фазе хранения и сохраняется до начала фазы предзаряда. На фиг. 5 направление потока информации показано стрелками, а светлые и темные кружки соответствуют логическим состояниям 0 и 1 в период передачи информации следующему вентилю.

Для правильной работы вентилей необходимо, чтобы изолирующий транзистор находился в нужном (открытом или закрытом) состоянии во всех рабочих фазах. Для i+1-го вентиля в логической цепи это обеспечивается выполнением следующих требований к тактовым напряжениям:

1. В фазе операции с при входном сигнале логической 1 (Vi=VH), когда φi+1<Vdd-Vt-VD и Vi+1 = φi+1 (участок АВ на фиг.5), напряжение φ0i+1 должно обеспечить протекание тока l<0 (фиг.3б):

φi0>φi+Vt. (1)

2. При логических переходах 1-1 в фазах хранения и предзаряда протекание тока l<0 должно быть исключено во время действия импульса входного напряжения Vi>Vt, (участок CD на фиг.5), т.к. оно приведет к нереверсивному разряду емкости С и термализации накопленной в ней энергии:

φ0i+1<Vi+Vt. (2)

3. По той же причине при логических переходах 1-1 в фазах хранения и предзаряда протекание тока l<0 должно быть исключено до момента нарастания выходного напряжения Vi+1 до уровня Vdd-Vt (участок EF на фиг.5):

φ0i+1<Vi+Vt. (3)

Как видно из временных диаграмм на фиг.5, условия (1)-(3) оказываются выполненными. Таким образом, введение в заявляемый логический вентиль новых элементов - вспомогательной тактовой шины 10 и изолирующего транзистора 9 (фиг. 3) - обеспечивает функционирование логического вентиля в реверсивном режиме без использования комплементарных полевых транзисторов.

Как и в вентиле-прототипе [4], функциональные возможности заявляемого логического вентиля могут быть расширены путем введения дополнительного каскада, осуществляющего инверсию выходного сигнала. Такая возможность иллюстрируется фиг.6. Дополнительный каскад работает аналогично основному каскаду логического вентиля синхронно с ним, формируя на дополнительном выходе сигнал  , который является логической инверсией сигнала Y на основном выходном электроде. Основной и дополнительный каскады подключены к одной и той же тактовой шине, поэтому в дополнительный каскад не требуется вводить изолирующий транзистор.

, который является логической инверсией сигнала Y на основном выходном электроде. Основной и дополнительный каскады подключены к одной и той же тактовой шине, поэтому в дополнительный каскад не требуется вводить изолирующий транзистор.

Заявляемый вентиль может быть использован в качестве базового логического вентиля в цифровых устройствах обработки информации со сверхмалым энергопотреблением.

Для реализации таких устройств средствами микроэлектроники, например, в виде ИМС, могут быть использованы стандартные технологические маршруты, применяемые в производстве цифровых микросхем на МДП-транзисторах. При этом исключается ряд технологических операций, связанных с изготовлением р-канальных транзисторов: формирование "карманов" р-типа для их размещения, формирование р+-областей стока и истока, подгонка их пороговых напряжений.

Заявляемый вентиль не нуждается в шинах "земли" и смещения подложек р-канальных транзисторов, в то время как в прототипе, реализуемом в КМДП базисе, емкости между стоками р-канальных транзисторов и "карманами" могут использоваться в качестве запоминающих только при подключении "карманов" к дополнительной шине постоянного потенциала Vdd.

Работоспособность заявляемых логических вентилей проверялась компьютерным моделированием с использованием программы схемотехнического моделирования P-SPICE и модели n-канальных МДП-транзисторов 1-го уровня.

Компьютерный анализ подтвердил правильное функционирование логических вентилей И-НЕ и ИЛИ-НЕ при всех комбинациях входных сигналов вплоть до тактовой частоты, составляющей 1/6 предельной частоты транзисторов.

На фиг. 7 показан пример реализации преобразователя десятичного кода в десятичный бинарный код на основе реверсивного логического вентиля динамического типа на полевых транзисторах с изолированным затвором. Структурная схема преобразователя (фиг.7а) содержит 3-х и 2-входовые логические вентили ИЛИ-НЕ (3ИЛИ-НЕ и 2ИЛИ-НЕ), а также и 2-входовые логические вентили И-НЕ (2И-НЕ). Электрические схемы этих вентилей представлены на фиг.7б, в, г. Такие преобразователи применяются, например, в устройствах отображения информации цифровых вольтметров, калькуляторов, аппаратуры цифропечати.

Источники информации

1. Moon Y., Jeong D.-K. An efficient charge recovery logic circuit. IEEE J. SSC, Apr. 1996, v,31, N4, p.p. 514-522.

2. Himman R.T., Schlecht M.F. Recovered energy logic: a single clock AC logic. IWLPD'94 Workshop Proceedings, 1994, p.p. 153-158.

3. Seitz C. L., Frey A.H., Mattisson S., Rabin S.D., Speck DA., van de Snepscheut J.L.A. Hot-clock nMOS. 1985 Chapel Hill Conf. on VLSI. Rockville, MD. Computer Science Press, 1985, p.p. 1-17.

4. Dickinson G., Denker J.S. Adiabatic dinamic logic. IEEE J. of Solid St. Circ., 1995, v.30, 3, p.p. 311-315 - прототип.

| название | год | авторы | номер документа |

|---|---|---|---|

| ШИРОКОПОЛОСНАЯ ИНТЕГРАЛЬНАЯ МИКРОСХЕМА УСТРОЙСТВА ВЫБОРКИ И ХРАНЕНИЯ | 2003 |

|

RU2244374C2 |

| УСИЛИТЕЛЬНЫЙ КАСКАД | 1994 |

|

RU2099856C1 |

| Формирователь импульсов | 1988 |

|

SU1674361A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ПАРАМЕТРОВ ФЛУКТУИРУЮЩИХ ВИДЕОИМПУЛЬСОВ | 1990 |

|

RU2007854C1 |

| УСТРОЙСТВО ПРИЕМА КОМАНД УПРАВЛЕНИЯ | 2002 |

|

RU2237287C2 |

| СПОСОБ ПРИЕМА И ПЕРЕДАЧИ ИНФОРМАЦИИ ОПТИЧЕСКИМ СИГНАЛОМ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1999 |

|

RU2154906C1 |

| УСТРОЙСТВО ВЫБОРКИ И ХРАНЕНИЯ АНАЛОГОВОЙ ИНФОРМАЦИИ | 2006 |

|

RU2314580C1 |

| СПОСОБ ПРИЕМА И ПЕРЕДАЧИ ИНФОРМАЦИИ ОПТИЧЕСКИМ СИГНАЛОМ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2192710C2 |

| ТРИГГЕР, РЕГИСТР СДВИГА, СХЕМА ВОЗБУЖДЕНИЯ УСТРОЙСТВА ОТОБРАЖЕНИЯ, УСТРОЙСТВО ОТОБРАЖЕНИЯ И ПАНЕЛЬ УСТРОЙСТВА ОТОБРАЖЕНИЯ | 2010 |

|

RU2507680C2 |

| СЕНСОР ВЕКТОРА МАГНИТНОГО ПОЛЯ | 1997 |

|

RU2122258C1 |

Предметом изобретения является реверсивное логическое устройство динамического типа на полевых транзисторах с изолированным затвором, в котором большая часть энергии, затраченной на выполнение логических операций, возвращается в источник питания. В логическое устройство введены вспомогательные тактовые шины, а также введены в базовые логические вентили дополнительные изолирующие транзисторы, что позволяет использовать только n-канальные полевые транзисторы и повысить помехоустойчивость устройства за счет увеличения запаса по напряжению запирания логических транзисторов в базовых вентилях. Технический результат: повышение быстродействия и помехоустойчивости логического устройства, а также упрощение технологического процесса его изготовления в микроэлектронном исполнении, повышение плотности компоновки и, в конечном счете, снижение стоимости. 7 ил.

Реверсивное логическое устройство динамического типа на полевых транзисторах с изолированным затвором, содержащее n тактовых шин, по которым со сдвигом на 1/n-ю периода поступают n-фазные тактовые импульсы, и матрицу базовых логических вентилей, каждый из которых включает блок логических транзисторов с входными электродами затворов, выходным электродом и электродом питания, выпрямляющий элемент, включенный между выходным электродом блока логических транзисторов и тактовой шиной, и запоминающий конденсатор, включенный между выходным электродом и областью нулевого потенциала - "землей", причем базовые логические вентили i-гo, n+i-гo, 2n+i-гo и т. д. , где 1≤i≤n-1, столбцов матрицы соединены с i-й тактовой шиной, а выходные электроды вентилей j-го столбца матрицы соединены с входными электродами вентилей j+1-го или j+1+k-го, где k>1 - целое число, столбца матрицы, отличающееся тем, что в него введены n вспомогательных тактовых шин, причем на i-ю вспомогательную тактовую шину поступают вспомогательные тактовые импульсы, сдвинутые по фазе относительно тактовых импульсов на i-й тактовой шине, а в каждый из базовых логических вентилей i-гo, n+i-гo, 2n+i-гo и т. д. , где 1≤i≤n-1, столбцов матрицы введен изолирующий транзистор, включенный между электродом питания блока логических транзисторов и i-й тактовой шиной, затвор которого соединен с i-й вспомогательной тактовой шиной.

| DICKINSON G | |||

| et al Adiabatic dinamic logic | |||

| IEEE J | |||

| of Solid St | |||

| Circ., 1995, v.30, №3, p.p | |||

| Способ приготовления массы для карандашей | 1921 |

|

SU311A1 |

| СПОСОБ КОМПОНОВКИ ИНДИВИДУАЛЬНО ПРОЕКТИРУЕМЫХ ЛОГИЧЕСКИХ СХЕМ В ЗАКАЗНОЙ БИС | 1996 |

|

RU2137295C1 |

| СТЕНД ДЛЯ ИСПЫТАНИЯ АБСОРБЦИОННО-КОМПРЕССИОННОГО ХОЛОДИЛЬНОГО АГРЕГАТА | 1996 |

|

RU2105938C1 |

| Отопительная панель | 1987 |

|

SU1523859A1 |

Авторы

Даты

2002-06-27—Публикация

2001-07-19—Подача