Изобретение относится к цифровой технике и может быть использовано в интегральных схемах устройств обработки и хранения информации для быстрого формирования выходных логических уровней при наличии емкостной нагрузки.

Цель изобретения - повышение быстродействия путем обеспечения предварительной установки в высокоимпедансном состоянии.

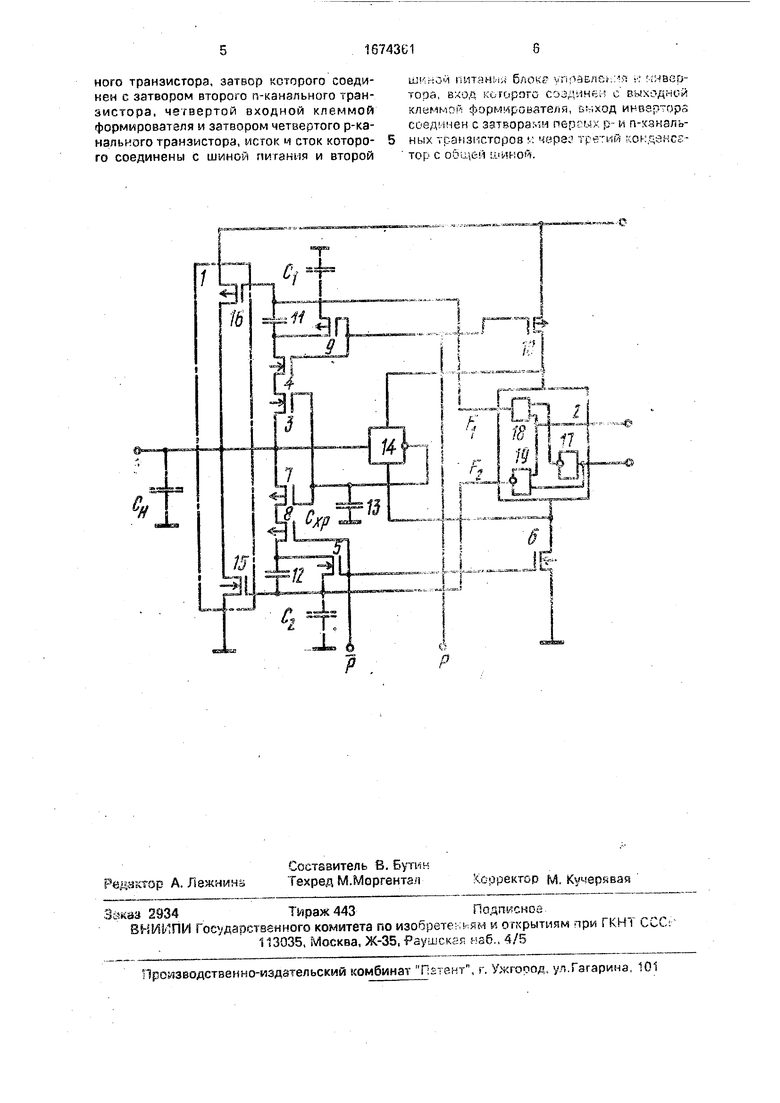

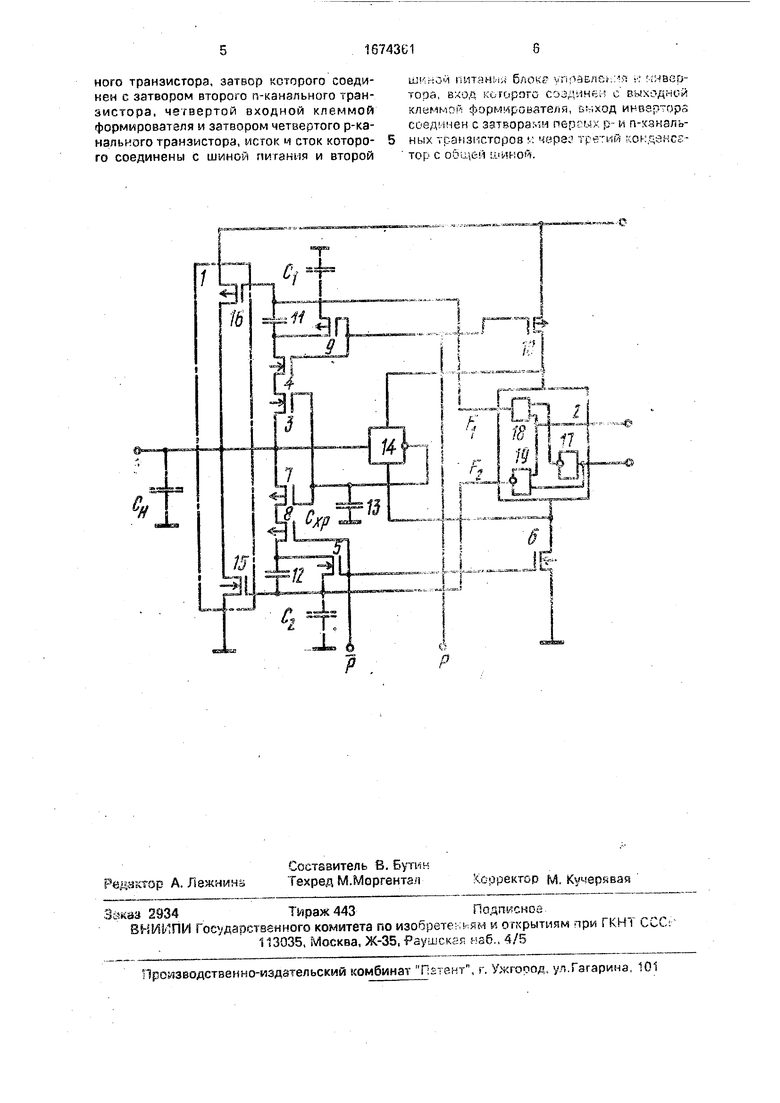

На чертеже приведена принципиальная схема формирователя.

Формирователь импульсов содержит выходной инвертор 1, блок 2 управления, n-канальные транзисторы 3-6, р-канальные транзисторы 7-10, конденсаторы 11-13, инвертор 14, в выходном инверторе 1 -п-каналь- ный транзистор 15 и р-канальный транзистор 16, а в блоке 2 управления - инвертор 17, элемент ИЛИ 18, и элемент ИЛИ-НЕ 19.

Вход и выход инвертора 17 блока 2 управления соединены с соответствующими входами элемента ИЛИ 18 и элемента ИЛИ- НЕ 19, другие входы которых и вход инвертора 17 соединены с входными клеммами формирователя. Выходы элементов ИЛИ 18 и ИЛИ-НЕ 19 соединены с затворами п- и р-канальных транзисторов 15 и 16 выходного инвертора 1, истоки которых соединены с шиной питания и общей шиной, стоки - с выходной клеммой формирователя, входом инвертора 14 и стоками п- и р-канальных транзисторов 3 и 7, затворы которых соединены с выходом инвертора 14 и через конденсатор 13 с общей шиной, истоки - со стоками соответствующих п- и р-канальных транзисторов 4 и 8, истоки которых соединены со стоками р- и n-канальных транзисторов 9 и 5 и через конденсаторы 11 и 12 соответственно с затворами р- и п-кэнальных транзисторов 16 и 15 выходного инвертора 1 и истоками р- и n-канэльных транзисторов 9 и 5, затворы которых соединены с затворами соответствующих п и р-канальных транзисторов 4, 10 и 5, 6 соответственно и входными клеммами формирователя. Шина питания через р-канальный транзистор 10 соединена с шинами питания инвертора 14 и блока

со

с

сь

VJ

N

со сь

2 управления, другие шины питания кою рых через n-канальный транзистор б соединены с общей тиной

Формирователь импульс ом работает следующим образом.

При подаче сигналов высоюго уров ы на затворы транзисторов 5 6 у 8 и вход инвертора 17 при низком уроин сигнапа на затворах транзисторов 4, 9 / 10 на выхола блока 2 управления устанавливаются cooreei ствующие логические уровни, закрывающие транзисторы 15 и 16 выходного инвертора 1. На выходной клемме фпватоля третье состояние. Открыты транзисторы 5 м 9 разряда конденсаторов 11 и 12 оЬраыои связи и ранзисторы 6 и 10 На кон ДРНСЭГО ре 13 через инвертор 14 устанавливается логический уровень противопст J-WHKIUT w который сохраняется на выходг t} орм фовэтр- ля благодапя значительной РМКОСТНСИ нпгру ки

Предположим что на выходе был сформирован высокий логический уртппчь и вых и ип Тогда конденсатор 13 разря жен. Из транзисторов 7и8открыттрчнэистоп 7 Транзисторы 4 и 8 закрыты В пжимр работы Предустановка закрываются трэчэч сторыЬ, б 9 и 10 и открываются транзистор) 4 и 8 Так как из транзисторов 7 и 3 оп рыт только трлнзисгор 7 то иапрпж- ние с выхода через цепь обратной подается на затвор транчьчтср Ь Fi г. чальный момент перелодногп процес я HJ затворе транзистора 15 yticm -впираете

напряжение (1 ьС2/С п) Ь резупьга те открывается выходной трчнзисгор 15 Напряжение на выходе формировать а также и на затворе транзигтооа 15 m нижается. Если будет выполнено условие Cn/C2 2Uon/(Unn-2Uon) где U ,i-пороговое напряжение n-канального вы/од «ого трзн зистора; С2 - суммарная паразитная емкость на подложку, приведенная к атвору транзистора 15, то транзистор 15 закроется к моменту, когда на выходе формирователя установится напряжение поедустпновки ип(1) вых+и0Вых)/2 «Unn/2 Сслипродустэ- новке предшествовал на выходе гЬормиро вателя низкий логический уровень U°Bi,x -О В, то предустановка будет псо/одигь за сче обратной связи через цепь транзисюры 3 и 4, конденсатор 11. Для того чтобы F ОУОД ное напряжение также устанасл псзл кь в

ЛИЧИНОЙ Unn/2, ДОЛЖНО ВЫПОЛНЯТЬСЯ уСЛОР И1

Cn/Ci 2Uop(Uun-2Uoi). где игр-порогово -г пряжение р-канапьного выходного трччпи стора 1; Ci - суммарная пара ,итная CMKGCTI на подложку, приведенная к за вооу rpin зистора 1

Hoi ле лрсиедения предустановки вы кодного напряления носстанавливаются исх-гдниг. 3Hd ения логических уровней на 1но,,ач управления предустановкой формиpOBjT6 i i Окончательное формирование ло- уровней О или 1 на выходе Формирователя в соответствии со значени ем входною информационного сигнала на, входах элемент ИЛИ-НЕ 18 и инвертора 17f

блока упр -вления сопровождается умет. iuenh,iM вдвое перепадом напряжеичи имесге с тем и временем переключения. Формула изобретения Формирователь импульсов содьржаi иi,i и блок управления, выходной инвертор, i. м eiopon р канальные трииисторы парный 1/1 вюрой n-L 3-ian1 ние транзисторы, t) управ 1еиия - инре.ртор, элемент ИЛИ и элемент IIJHI-HE, вход инвертора и

О героый вход элемента ИЛИ-НЕ блока управления соединен У с первой входной t геммой форм -рователя, выход инвертора юединен с иергым Е-идом элемента ИЛИ, второй в/од зпемента ИЛИ и ргорой вход

тементэ ИЛИ hiоедине ы с второй вы)дной клеммой формирователя, выход эле- српа ИЛИ и выход элемента ИЛИ-Н1 блока управленич соединены соотьетствен- io г затворами р и п канальных транзисто 1 i о.з ЙЫУСДНОГО инвертора, истоки которых co flvinenbi с тиной питания и общей ши- i-ipn ч стоки с выходной клемпой форми- } гчмтеля и . чжами первый р- и п-кьнальных i раняпс ого1;, затворы которых соединены,

ч з истоки оедпнены со стоками вторых р- и п чнэчьчых транзисторов соответствонно, о п и ч а ю щ и и с я тем, что с цепью not .тк.ния быстродействия путем обеспе- |еьия предварительной установки в выссчсоj импе/, зчсном состоянии, в него введены Tfjeiiv/i /(четвертый р-канальные транзисторы и третий v четвертый n-канальные транзисторы инвертор первый, втсрой и третий конденсаторы, исток второго р-канального

5. транзистора соединен со стоком третьего п-канапьипго транзистора и через первый чондоматор с затвором п-канального гоаьчистора гшуоднО|0 инвертора и истоком третьего п канального транзистора, за- j твор . строго соединен с затвором второго р к jHaHbiioro грамзис.ора, третьей входной КЛРММОИ формирователя и затвором четвертого п-к п иЬьного транзисюра исток и сток от opi t с соеяи -.РЧЫ с общей шиной и первой тиной .итаи и блокаупразлеиияиинЗортора, исто- второго ,ального транзистора сое цинен го стоком третьего р-кзнальвогг транзистора и через ьторой конденсатор - о затвором р канчпьнгго транзистора Bnixiv

, «.о;о инй ртопа 11 сгоном третьегс с-канального транзистора, затьор которого соел i- НРН с затвором второ.о rs-каизльного ipan зистора, ченэертой входной клеммой формирователя и затвором четьертого р-ка

L | -.j l I и т-ж „ б; .г, ML -, . . в.и

.U )ci ,й | ( , jr ,14 , nt MM-4 - фурМЦ :ОЬЛТО/1И -л. -Д И1-0 р-Ор%

f седмчен с ззтора .. г ип-Чтнагю

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговый переключатель | 1986 |

|

SU1385288A1 |

| Генератор прямоугольных импульсов | 1986 |

|

SU1411929A1 |

| Элемент с тремя состояниями | 1978 |

|

SU743200A1 |

| Формирователь импульсов | 1988 |

|

SU1626347A1 |

| Формирователь парафазных импульсов | 1981 |

|

SU984013A1 |

| Логический элемент "не" | 1976 |

|

SU573884A1 |

| Формирователь сигнала начальной установки делителя частоты кварцевых наручных часов | 1986 |

|

SU1365041A1 |

| Стабилизатор напряжения питания часовой интегральной схемы | 1985 |

|

SU1345165A1 |

| Формирователь с тремя состояниями на выходе | 1983 |

|

SU1149399A1 |

| Усилитель считывания на дополняющих МДП-транзисторах | 1982 |

|

SU1062785A1 |

Изобретение относится к цифровой технике и может быть использовано в интегральных схемах устройств обработки и хранения информации для быстрого формирования выходных логических уровней при наличии емкостной нагрузки. Цель изобретения - повышение быстродействия за счет обеспечения предварительной установки в высокоимпедансном состоянии. По сигналу предустановки на выходе формирователя устанавливается промежуточный уровень выходного напряжения, в связи с чем укорачивается процесс установления логического уровня при изменении информационного сигнала. 1 ил.

НЭЛЬРОГО транзистора, исток и сток которо 5 иых-. санзигторов ч-ре1 го соединены с шине i гнпэннч и второй тп( с . (ей nh ол

ч,Г ot г, ч Г

| Манометр | 1941 |

|

SU72686A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Кармазинский А | |||

| Н | |||

| Синтез принципиальных схем цифровых элементов на МДП -транзисторах, М.: Радио и связь, 1983, с | |||

| Катодное реле | 1918 |

|

SU159A1 |

Авторы

Даты

1991-08-30—Публикация

1988-11-15—Подача