Изобретение относится к области связи, в частности к построению сетей связи для передачи информации и вычислительным сетям.

Известны сети связи, содержащие коммутационные узлы различного уровня, соединенные через соответствующие интерфейсы между собой и позволяющие передавать информацию от вычислительных машин (патент 5499290, кл. Н 04 М 3/00, 1996). Однако время передачи информации в таких сетях значительно, что не позволяет передавать большие объемы информации.

Известны также сети связи, в которых путем создания определенного трафика уменьшается время передачи информации (патент Великобритании 2299485, кл. Н 04 М 3/00, 1996). Однако такие сети не могут быть построены по иерархическому принципу.

Наиболее близкой к предлагаемому изобретению является иерархическая сеть связи, содержащая сети связи высшего, среднего и низшего уровня, узлы перехода, абонентские блоки, передающие и приемные сетевые интерфейсы и узлы управления трансляцией, содержащие регистр сдвига, выделитель адреса (патент РФ 2004946, кл. Н 04 Q 11/06,1993).

Однако наличие лишь одного пути между двумя узлами сети снижает ее надежность, так как при выходе из строя линии связи в локальных сетях используется специальный протокол 802.lq, который активизирует резервные линии связи, но это требует довольно продолжительного времени, что недопустимо в сетях связи.

Кроме того, существующие коммутаторы, являясь по сути многопортовыми мостами, размножают широковещательные кадры (адрес назначения у которых состоит из одних "1"), то есть широковещательный кадр, поступивший на один из портов коммутатора, автоматически ретранслируется во все остальные порты, что приводит к "широковещательному шторму", блокирующему работу всей сети, ввиду переполнения буферной памяти в портах коммутаторов. Поэтому невозможно построить большие сети на базе существующих коммутаторов, а необходимо использовать коммутаторы 3-го уровня (маршрутизаторы), сложные и дорогие аппаратно-программные устройства, использующие специальные протоколы для обмена информацией между собой с целью построения и обновления маршрутно-адресных таблиц, что сильно перегружает сеть.

Предлагаемое изобретение исключает эти недостатки.

Для этого в иерархическую сеть, содержащую (к+1)+(к х к) узлов коммутации (где к - любое целое число, удовлетворяющее соотношению 2≤ к ≤12), соединенных по пирамидальной схеме, и абонентские блоки, соединенные с соответствующими узлами коммутации, при этом каждый коммутационный узел содержит (к+1) узлов перехода, каждая из которых содержит приемный интерфейс, выход которого соединен с входом блока обработки адреса и входом блока доступа, выход которого соединен с внутренней шиной, а второй вход - с выходом блока обработки адреса, а также блок фильтрации, вход которого соединен с внутренней шиной, и выходной интерфейс, выход которого соединен со входом приемного интерфейса, а также узлы управления и обработки, причем узлы коммутации соответствующих уровней соединены по кольцевой схеме, в каждый узел коммутации, кроме верхнего в пирамидальной схеме, введены по два узла перехода, при этом в каждый узел перехода введены блок резервного переключения и буферное запоминающее устройство (ЗУ), выход которого соединен с входом выходного интерфейса, а вход соединен с первым выходом блока резервного переключения, первый вход которого соединен с выходом блока фильтрации, а второй вход - со вторым выходом приемного интерфейса, при этом к узлов перехода соединены по кольцевой схеме с третьим и четвертым входами и вторым и третьим выходами блоков резервного переключения, а (к+2)-ой узел перехода соединен с (к+1)-ым и (к+3)-им узлами перехода, при этом каждый блок резервного переключения содержит первый триггер, вход которого является вторым входом блока резервного переключения, первым входом которого являются объединенные входы первой, второй и третьей схем И, вторые входы первой и второй схем И соединены соответственно с первым и вторым выходами первого триггера, второй триггер, первый и второй выходы которого соединены соответственно с третьим входом второй схемы И и вторым входом третьей схемы И, при этом вход второго триггера соединен с выходом четвертой схемы И, входы которой являются соответствующими входами блока резервного переключения, как и первый и второй входы схемы ИЛИ, третий вход которой соединен с выходом первой схемы И, причем блок обработки адреса содержит последовательно соединенные выделитель адреса и первый регистр адреса, выход которого соединен с входами выделителя широковещательного адреса и первого, второго и третьего компараторов, вторые входы первого, второго и третьего компараторов соединены соответственно с выходами выделителя тетрады адреса порта, второго регистра адреса и третьего регистра адреса, а выходы первого, второго и третьего компараторов соединены соответственно с входами схемы формирования адреса порта, второго регистра адреса порта и третьего регистра адреса порта, причем второй выход выделителя тетрады адреса порта соединен со вторым входом схемы формирования адреса порта, первый и второй выходы которого соединены с первыми входами второй схемы ИЛИ и схемы НЕ, выходы второго и третьего регистров адреса порта соединены соответственно с первым входом третьей схемы ИЛИ и вторым входом второй схемы ИЛИ, и вторым входом третьей схемы ИЛИ, и третьим входом второй схемы ИЛИ, выход выделителя широковещательного адреса через регистр порта нулевого сигнала соединен со вторым входом схемы НЕ и четвертым входом второй схемы ИЛИ, пятый вход которой соединен с выходом схемы НЕ, третий вход которой соединен с выходом третьей схемы ИЛИ, а выход второй схемы ИЛИ соединен со входом первого регистра адреса порта, при этом введено (к+1)+(к х к) сдвоенных блоков обработки и обеспечения передачи широковещательного трафика, подключенных к внутренней шине узлов коммутации.

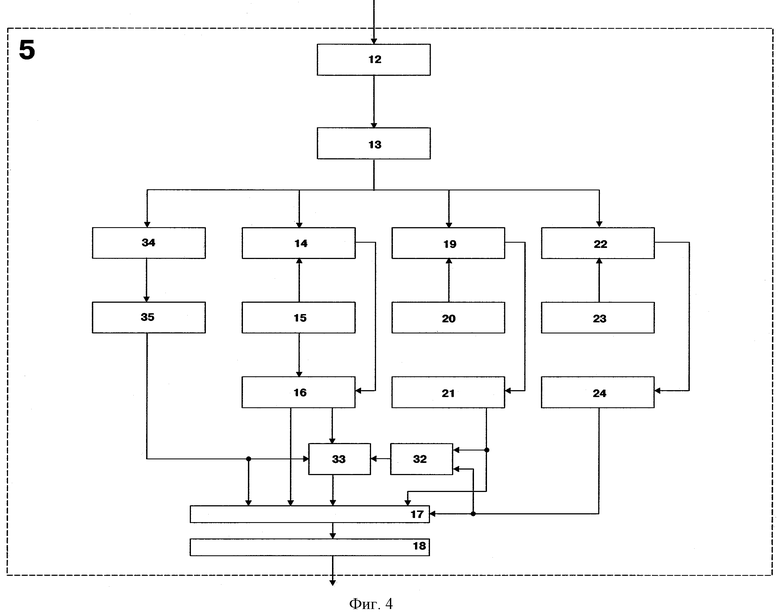

На фиг. 1 приведена структурная электрическая схема многоярусной иерархической радиально-кольцевой сети связи.

На фиг.2 приведена структурная электрическая схема узла коммутации.

На фиг.3 приведена структурная электрическая схема блока резервного переключения.

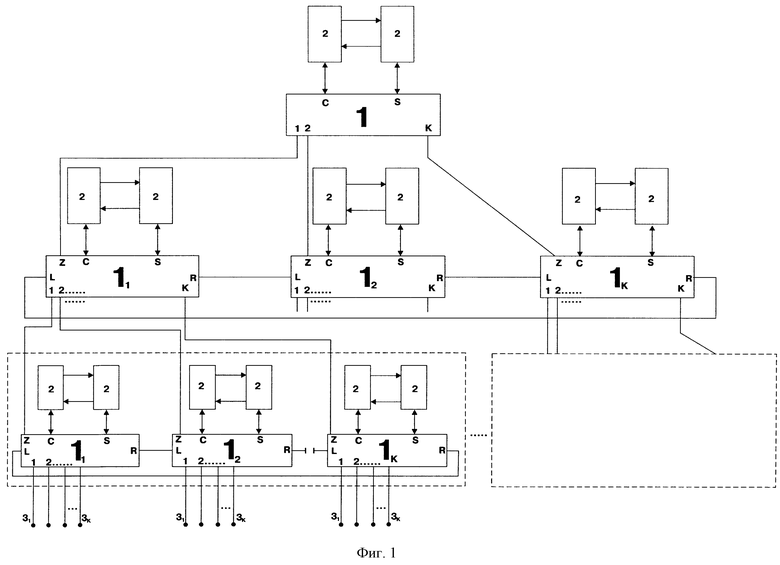

На фиг. 4 приведена структурная электрическая схема блока обработки адреса.

Многоярусная иерархическая радиально-кольцевая сеть связи содержит узлы коммутации 1, сдвоенные блоки обработки и обеспечения передачи широковещательного трафика 2, абонентские блоки 31-3к.

Узлы коммутации 1 содержат узлы перехода la1-laк+3, приемный интерфейс 4, блок обработки адреса 5, блок доступа 6, внутреннюю шину 7, блок фильтрации 8, блок резервного переключения 9, буферное запоминающее устройство (ЗУ) 10 и выходной интерфейс 11.

Блок обработки адреса 5 содержит выделитель адреса 12, первый регистр адреса 13, первый компаратор 14, выделитель тетрады адреса порта 15, схему формирования адреса порта 16, вторую схему ИЛИ 17, первый регистр адреса порта 18, второй компаратор 19, второй регистр адреса 20, второй регистр адреса порта 21, третий компаратор 22, третий регистр адреса 23, третий регистр адреса порта 24, третью схему ИЛИ 32, схему НЕ 33, выделитель широковещательного адреса 34 и регистр порта блока обработки (С) 35.

Блок резервного переключения 9 содержит первый триггер 25, первую схему ИЛИ 26, первую, вторую, третью и четвертую схемы И 27, 28, 29 и 30 соответственно и второй триггер 31.

Иерархическая радиально-кольцевая сеть связи работает следующим образом.

Узлы коммутации 1 обеспечивают обработку 48-битного адреса назначения (АН), который является MAC-адресом кадра информации по стандартам Ethernet.

Каждый АН состоит из 12-ти тетрад, состоящих из 4 бит каждая.

Каждый узел коммутации 1 имеет составной адрес, состоящий из старшей части префикса Р (значащей части) и младшей части, все тетрады которой равны 0.

При этом число нулевых тетрад соответствует уровню иерархии, на котором размещается данный узел коммутации 1.

Кадр информации Ethernet из канала связи через приемный интерфейс 4 поступает на блок обработки адреса 5, где выделитель адреса 12 обеспечивает выделение из заголовка кадра адрес назначения (АН) и передачу его на первый регистр адреса 13, на первом компараторе 14 производится его сравнение с префиксом Р адреса коммутатора, находящимся на регистре адреса 16. В случае несравнения в схему формирования адреса порта 18 через схему НЕ 33 и вторую схему ИЛИ 17 заносится код порта (Z) для последующей передачи на верхние уровни сети. В случае сравнения префикса с соответствующей частью адреса назначения следующая по порядку за префексом Р тетрада адреса назначения передается на схему формирования адреса порта 16 и далее через вторую схему ИЛИ 17 передается на первый регистр адреса порта 18.

В случае, если на втором компараторе 19 или третьем компараторе 22 обеспечивается сравнение АН приходящего кадра с адресом коммутатора, находящегося слева по кольцевой сети (формирование кода порта L), либо с адресом коммутатора, находящегося справа по кольцевой сети (формирование кода порта R) соответственно, сигналы сравнения через третью схему ИЛИ 32 и схему НЕ 33 обеспечат запрет передачи кода порта Z. В случае получения широковещательного кадра выделитель 34 обеспечивает формирование кода на регистре порта блока обработки (С) и передачу его через вторую схему ИЛИ 17 на регистр адреса порта 18 и одновременно через схему НЕ 33 запрещает формирование кода порта Z.

С выхода первого регистра адреса порта 18 информация поступает в блок доступа 6, где формируется адресуемое слово из m бит для высокоскоростной передачи по внутренней шине 7 всем блокам фильтрации 8, которые фильтруют только адресуемые ему слова и через блок резервного переключения 9 передают в буферное ЗУ 10 и далее через передающий интерфейс 11 направляют в канал связи.

Блок резервного подключения 9 в штатном режиме (приемный интерфейс 4) выдает на первый триггер ТГ 25 сигнал "активности", устанавливает его в состояние "1" и обеспечивает передачу данных из блока фильтрации 8 через первую схему И 27 и первую схему ИЛИ 26 в буферное ЗУ 10.

В случае выхода из строя канала связи первый триггер ТГ 25 сбрасывается в состояние "0", этим обеспечивается закрытие первой схемы И 27 и открытие второй схемы И 28, что обеспечивает прохождение данных из блока фильтрации 8 через вторую схему И 28 и вход 1 первой схемы ИЛИ 26 в буферное ЗУ 10 и передающий интерфейс соседнего (правого) порта (резерв 1-й очереди).

В том случае, если два канала вышли из строя, первые триггеры ТГ 25 центрального и правого канала сбрасываются в "0" и через четвертую схему И 30 устанавливают второй триггер ТГ 31 в состояние "1", что обеспечивает прохождение данных из блока фильтрации 8 центрального канала через третью схему И 29 и вход первой схемы ИЛИ 26 в буферное ЗУ 10 и передающий интерфейс 11 соседнего (левого) канала (резерв 2-й очереди).

После восстановления каналов система автоматически возвращается в исходное сотояние.

Предлагаемое изобретение позволяет подключить резервный путь за время переключения логического элемента (триггера).

Использование сдвоенных блоков обработки и обеспечение передачи широковещательного трафика 2, выполненных в виде ЭВМ, обеспечивает предварительное резервирование пропускной способности портов коммутатора для передачи приоритетной информации с использованием протокола IEEE 802.1р, а вся неприоритетная передается на ЭВМ для промежуточного хранения и передачи в свободное от приоритетного трафика время, и, таким образом, обеспечивается необходимое качество обслуживания (QoS).

| название | год | авторы | номер документа |

|---|---|---|---|

| ИЕРАРХИЧЕСКАЯ СЕТЬ СВЯЗИ | 1997 |

|

RU2118069C1 |

| ДЕКАДНЫЙ МУЛЬТИПЛЕКСОР ЛОКАЛЬНОЙ СЕТИ | 1999 |

|

RU2159511C1 |

| РАДИОСЕТЬ ETHERNET С ДОСТУПОМ ПО ТРЕБОВАНИЮ | 2001 |

|

RU2211546C2 |

| ИЕРАРХИЧЕСКАЯ СЕТЬ СВЯЗИ | 2003 |

|

RU2265967C2 |

| Многоканальное регистрирующее устройство | 1988 |

|

SU1698899A1 |

| СПОСОБ ДВУХТАКТНОЙ АССОЦИАТИВНОЙ МАРШРУТИЗАЦИИ | 1999 |

|

RU2140132C1 |

| Двухдвигательный электропривод постоянного тока и способ управления им | 1990 |

|

SU1802394A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ГРАФИЧЕСКОЙ ИНФОРМАЦИИ | 1993 |

|

RU2069012C1 |

| МИКРОКОНТРОЛЛЕРНАЯ СЕТЬ | 2007 |

|

RU2336556C1 |

| МУЛЬТИПЛЕКСОР ТЕЛЕКОММУНИКАЦИОННЫЙ МНОГОФУНКЦИОНАЛЬНЫЙ | 2004 |

|

RU2269154C1 |

Изобретение относится к построению сетей связи для передачи информации по вычислительным сетям. Техническим результатом является повышение надежности передачи информации путем обеспечения обходных путей. Результат достигается выполнением ярусного закольцевания узлов коммутации, выполнением узлов коммутации и выполнением блоков обработки адреса и блока резервного переключения, а также использованием сдвоенных блоков обработки и обеспечения передачи широкополосного трафика. 4 ил.

Многоярусная иерархическая радиально-кольцевая сеть связи, содержащая (к+1)+(кxк) узлов коммутации, (где к - любое целое число, удовлетворяющее соотношению 2 ≤ к ≤ 12), соединенных по пирамидальной схеме, и абонентские блоки, соединенные с соответствующими узлами коммутации, при этом каждый коммутационный узел содержит к+1 узлов перехода, каждый из которых содержит приемный интерфейс, выход которого соединен с входом блока обработки адреса и входом блока доступа, выход которого соединен с внутренней шиной, а второй вход - с выходом блока обработки адреса, а также блок фильтрации, вход которого соединен с внутренней шиной, и выходной интерфейс, выход которого соединен со входом приемного интерфейса, а также узлы управления и обработки, отличающаяся тем, что узлы коммутации соответствующих уровней соединены по кольцевой схеме, при этом в каждый узел коммутации, кроме верхнего в пирамидальной схеме, введены по два узла перехода, при этом в каждый узел перехода введены блок резервного переключения и буферное запоминающее устройство, выход которого соединен с входом выходного интерфейса, а вход соединен с первым выходом блока резервного переключения, первый вход которого соединен с выходом блока фильтрации, а второй вход - со вторым выходом приемного интерфейса, при этом к узлов перехода соединены по кольцевой схеме с третьим и четвертым входами и вторым и третьим выходами блоков резервного переключения, а (к+2)-й узел перехода соединен с (к+1)-ым и (к+3)-ым узлами перехода, при этом каждый блок резервного переключения содержит первый триггер, вход которого является вторым входом блока резервного переключения, первым входом которого являются объединенные входы первой, второй и третьей схем И, вторые входы первой и второй схем И соединены соответственно с первым и вторым выходами первого триггера, второй триггер, первый и второй выходы которого соединены соответственно с третьим входом второй схемы И и вторым входом третьей схемы И, при этом вход второго триггера соединен с выходом четвертой схемы И, входы которой являются соответствующими входами блока резервного переключения как и первый и второй входы схемы ИЛИ, третий вход которой соединен с выходом первой схемы И, причем блок обработки адреса содержит последовательно соединенные выделитель адреса и первый регистр адреса, выход которого соединен с входами выделителя широковещательного адреса и первого, второго и третьего компараторов, вторые входы первого, второго и третьего компараторов соединены соответственно с выходами выделителя тетрады адреса порта, второго регистра адреса и третьего регистра адреса, а выходы первого, второго и третьего компараторов соединены соответственно с входами схемы формирования адреса порта, второго регистра адреса порта и третьего регистра адреса порта, причем второй выход выделителя тетрады адреса порта соединен со вторым входом схемы формирования адреса порта, первый и второй выходы которого соединены с первыми входами второй схемы ИЛИ и схемы НЕ, выходы второго и третьего регистров адреса порта соединены соответственно с первым входом третьей схемы ИЛИ и вторым входом второй схемы ИЛИ, и вторым входом третьей схемы ИЛИ и третьим входом второй схемы ИЛИ, выход выделителя широковещательного адреса через регистр порта нулевого сигнала соединен со вторым входом схемы НЕ и четвертым входом второй схемы ИЛИ, пятый вход которой соединен с выходом схемы НЕ, третий вход которой соединен с выходом третьей схемы ИЛИ, а выход второй схемы ИЛИ соединен со входом первого регистра адреса порта, при этом введено (к+1)+(кxк) сдвоенных блоков обработки и обеспечения передачи широковещательного трафика, подключенных к внутренней шине узлов коммутации.

| RU 2004946 C1, 15.12.1993 | |||

| US 5043979 A, 27.08.1991 | |||

| US 5408231 A, 18.04.1995 | |||

| Бесколесный шариковый ход для железнодорожных вагонов | 1917 |

|

SU97A1 |

| Прибор, замыкающий сигнальную цепь при повышении температуры | 1918 |

|

SU99A1 |

Авторы

Даты

2002-08-27—Публикация

2000-12-25—Подача