Изобретение относится к полевым транзисторам, соответственно, к полевому транзистору с управляющим р-n переходом и к полевому транзистору со структурой металл - оксид - полупроводник (полевому МОП-транзистору) (MOSFET), имеющим, по существу, вертикальную геометрию, причем полевые транзисторы содержат плоскую подложку из непроводящего материала. Изобретение также относится к способу изготовления полевых транзисторов этого типа с, по существу, вертикальной геометрией, причем транзистор содержит плоскую подложку из непроводящего материала.

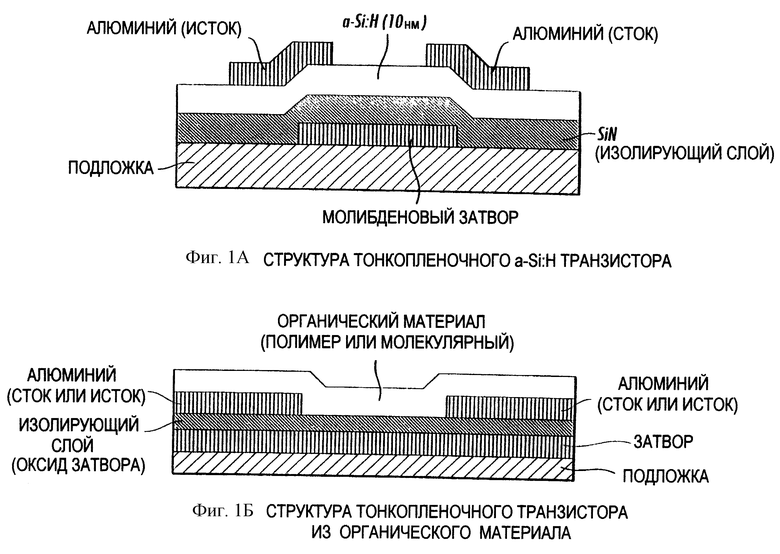

Полевые транзисторы, ПТ (FET), в которых в качестве активного полупроводника используют аморфный материал, традиционно конструируют с горизонтальной геометрией, например, представленной на фиг.1, на которой изображены два примера (фиг.1А, Б) реализации тонкопленочного полевого транзистора из известного уровня техники. Здесь электрод стока и электрод истока отделены один от другого каналом транзистора. Этот канал состоит из аморфного полупроводникового материала. Электрод затвора определяют как горизонтальный слой, который изолирован от канала посредством изолятора затвора. Транзисторный эффект определяют либо как режим обеднения, либо как режим обогащения, в зависимости от потенциала затвора. В качестве активного аморфного полупроводникового материала в полевых транзисторах этого типа используют сопряженные полимеры, ароматические молекулы и аморфные неорганические полупроводники.

Например на фиг.1 представлен тонкопленочный транзистор с активным полупроводниковым материалом в виде слоя аморфного Si:H толщиной 10 нм (Д.Б. Томассон и др. / "Электронные приборы. Письма ИИЭР", том 18, стр.117, март 1997 г.) (D.B. Thomasson & al., IEEE El. Dev. Lett., Vol. 18, p. 117; March 1997).

На подложке обеспечивается электрод затвора, который может быть металлическим. Поверх этого электрода затвора обеспечивается изолирующий слой из нитрида кремния (SiN), a на изолятор нанесен активный полупроводниковый материал в виде слоя аморфного Si:H толщиной 10 нм. На активном полупроводниковом материале обеспечиваются электрод стока и электрод истока, которые разнесены в пространстве один относительно другого. Они выполнены из иного металла, чем электрод затвора, например, из алюминия. Другой пример тонкопленочного транзистора из органического материала показан на фиг.1Б (А.Додабалапур и др., журнал "Эпплайд Физикс Леттерз", том 69, стр. 4227-29, декабрь 1996 г.) (А. Dodabalapur & аl. Арр1. Phys. Lett.: Vol. 69, pp. 4227-29. December 1996). Здесь активным полупроводниковым материалом является органическое соединение, например, полимер или ароматические молекулы. Как и в примере, представленном на фиг.1А, на подложке обеспечивается электрод затвора, а выше электрода затвора - изолятор в виде слоя, который может быть выполнен путем нанесения оксидного слоя на поверхность электрода затвора, что может быть осуществлено путем окисления материала на поверхности электрода затвора. На изолирующем слое обеспечиваются разнесенные в пространстве электрод истока и электрод стока, а поверх электродов стока и истока имеются отстоящие одна от другой вертикальные боковые стенки, обе из которых с одного конца соединены с аналогичной вертикальной поперечной стенкой. Следовательно, в плоскости, перпендикулярной к стенкам, канал транзистора имеет U-образное сечение, в котором боковые стороны U образованы боковыми стенками, а пересекающая линия образована поперечной стенкой. Слои могут быть выполнены таким образом, что они находятся на соответствующей подложке и полностью закрыты слоем из изолирующего материала. Поверх изолирующего слоя находится проводящий слой, который образует электрод затвора транзистора. Торцы боковых стенок или торцы боковых сторон канала U-образной формы являются открытыми, и в этих торцевых участках канала сформированы, соответственно, электроды истока и стока, например, посредством процесса ионной имплантации. Главной целью обеспечения тонкопленочного транзистора такого типа является получение достаточной длины канала на меньшей площади, по сравнению с той, которая может быть получена при традиционных вариантах осуществления, наряду с уменьшением тока утечки при закрытом состоянии транзистора.

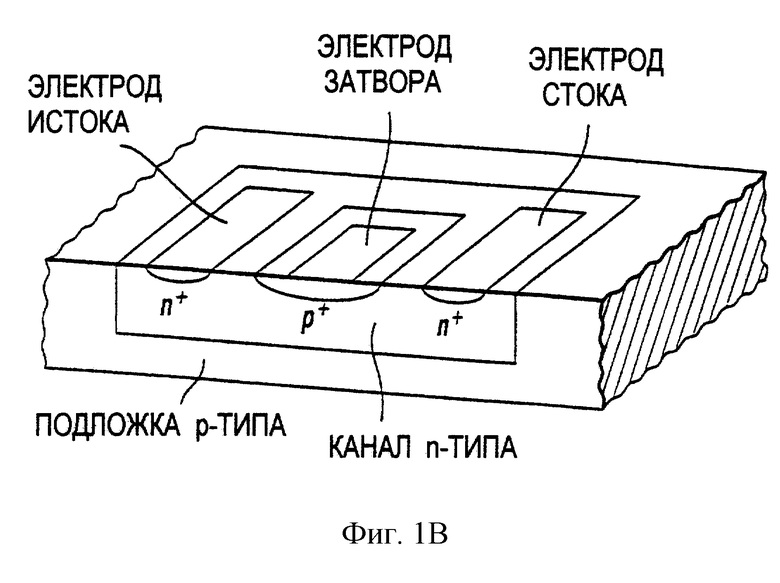

На фиг. 1В показана принципиальная схема структуры планарного полевого транзистора с управляющим р-n переходом (ПТУП) (JFET) из известного уровня техники, который в этом варианте осуществлен в виде n-канального полевого транзистора с управляющим р-n переходом (ПТУП) (JFET).

Использование аморфного полупроводникового материала позволяет реализовать различную геометрию транзисторов при использовании совершенно особых свойств обработки аморфных материалов. Следовательно, целью настоящего изобретения является обеспечение полевого транзистора, соответственно, полевого транзистора с управляющим р-n переходом (ПТУП) (JFET) и полевого транзистора со структурой металл - оксид - полупроводник (полевого МОП-транзистора) (MOSFET) с вертикальной геометрией, а более конкретной целью является осаждение активного аморфного полупроводникового материала в виде органических молекул, сопряженного полимера или аморфного неорганического полупроводника на вертикальную структуру, которая содержит в себе и электрод затвора, и электрод стока либо электрод истока. И, наконец, еще одной целью является создание канала транзистора с вертикальной ориентацией.

Ранее традиционные полупроводниковые приборы изготавливали с вертикальной геометрией. Целью этого являлось более эффективное использование площади микросхемы. Закономерно, что для транзистора с вертикальной геометрией необходимо меньшее пространство, чем для транзистора с горизонтальной геометрией.

Например, из патента США 5563077 (Г.К. Хэ) (Н.С. На) известен тонкопленочный транзистор с вертикальным каналом, в котором канал образован двумя разнесенными в пространстве одна относительно другой вертикальными боковыми стенками, которые с одного конца соединены с аналогичной вертикальной торцевой стенкой. Следовательно, в плоскости, перпендикулярной к стенкам, канал транзистора имеет U-образное сечение, в котором боковые стороны U образованы боковыми стенками, а пересекающая линия образована поперечной стенкой. Стенки могут быть выполнены таким образом, что они находятся на соответствующей подложке и полностью закрыты слоем из изолирующего материала. Поверх изолирующего слоя находится проводящий слой, который образует электрод затвора транзистора. Торцы боковых стенок или торец канала U-образной формы являются открытыми, и в этих торцевых участках канала сформированы, соответственно, электроды истока и стока, например, посредством процесса ионной имплантации. Главной целью создания тонкопленочного транзистора такого типа является получение достаточной длины канала на меньшей площади, по сравнению с той, которая может быть получена при традиционных вариантах осуществления, наряду с уменьшением тока утечки тогда, когда транзистор находится в закрытом состоянии.

В соответствии с изобретением, вышеупомянутых целей и иных преимуществ достигают посредством полевого транзистора с управляющим р-n-переходом (ПТУП) (JFET), отличающегося тем, что на подложке обеспечивают слой проводника, содержащий первый электрод, при этом поверх первого электрода формируют слой из изолирующего материала, который образует первый изолятор, что поверх первого изолятора формируют слой из проводящего материала, который образует второй электрод, что поверх второго электрода обеспечивают дополнительный слой из изолирующего материала, который образует второй изолятор, что поверх второго изолятора создают слой из проводящего материала, который образует третий электрод, причем указанные первый и третий электроды образуют, соответственно, электроды стока и истока транзистора, или наоборот, а указанный второй электрод является электродом затвора транзистора, что по меньшей мере указанный второй и указанный третий электроды и указанный первый и второй изоляторы с соответствующими слоями в виде многослойной структуры образуют ступеньку, ориентированную вертикально относительно указанного первого электрода и/или указанной подложки, и что поверх открытой части указанного первого электрода, указанного второго электрода и указанного третьего электрода находится полупроводниковый материал, образующий активный полупроводник транзистора, причем указанный активный полупроводник имеет непосредственный контакт с электродом затвора и образует, по существу, вертикально ориентированный канал транзистора между указанным первым и указанным третьим электродами; и посредством полевого транзистора со структурой металл - оксид - полупроводник (полевого МОП-транзистора) (MOSFET), отличающегося тем, что на подложке обеспечивают слой проводника, который содержит первый электрод, что поверх первого электрода формируют слой из изолирующего материала, который образует первый изолятор, что поверх первого изолятора создают слой из проводящего материала, который образует второй электрод, что поверх второго электрода обеспечивают дополнительный слой из изолирующего материала, который формирует второй изолятор, что поверх второго изолятора создают слой из проводящего материала, который образует третий электрод, причем указанные первый и третий электроды обеспечивают, соответственно, электроды стока и истока транзистора, или наоборот, а указанный второй электрод образует электрод затвора транзистора, что по меньшей мере указанный второй и указанный третий электроды и указанный первый и второй изоляторы с соответствующими слоями в виде многослойной структуры образуют ступеньку, ориентированную вертикально относительно указанного первого электрода и/или указанной подложки, что поверх указанного второго электрода и поверх указанной вертикальной ступеньки обеспечивают вертикальный слой из изолирующего материала, который формирует изолятор затвора, и что поверх открытой части указанного первого электрода, указанной вертикальной ступеньки с указанным изолятором затвора и указанного третьего электрода нанесен полупроводниковый материал, посредством которого осуществлен активный полупроводник транзистора и сформирован, по существу, вертикально ориентированный канал транзистора между указанным первым и указанным третьим электродами.

Кроме того, согласно изобретению, вышеуказанных целей и преимуществ достигают посредством способа изготовления полевого транзистора, отличающегося тем, что способ включает в себя следующие операции: на указанную подложку наносят слой проводника, образующего первый электрод; на первом электроде посредством фотолитографического процесса формируют ступеньку, состоящую из фоторезиста и расположенную вертикально относительно указанного первого электрода и/или указанной подложки; поверх указанного слоя проводника и указанного фоторезиста, образующего вертикальную ступеньку, наносят, соответственно, первый изолятор, проводник, который формирует второй электрод, второй изолятор и проводящий материал, образующий третий электрод, в виде многослойной структуры; указанную многослойную структуру над указанным фоторезистом и сам фоторезист удаляют способом обратной литографии, посредством чего оставшаяся структура изоляторов-электродов, обеспеченная на первом электроде, формирует ступеньку, ориентированную вертикально относительно указанного первого электрода и/или указанной подложки; и на указанный первый электрод и указанную вертикальную ступеньку наносят растворимый активный аморфный полупроводниковый материал таким образом, что полупроводниковый материал имеет контакт как с указанным первым электродом, так и с указанным третьим электродом, образующими, соответственно, электроды стока или истока полевого транзистора, и наоборот, и с указанным вторым электродом, образующим электрод затвора полевого транзистора, формируя таким образом вертикальный канал транзистора.

В том случае, когда полевой транзистор представляет собой полевой транзистор со структурой металл - оксид - полупроводник (полевой МОП-транзистор), преимуществом является то, что изолирующий материал наносят на вертикальную ступеньку в виде вертикального слоя, который обеспечивается поверх второго электрода и формирует изолятор затвора в полевом транзисторе, причем нанесение производят после удаления указанной многослойной структуры и указанного фоторезиста, но до нанесения растворимого активного аморфного полупроводникового материала.

Согласно изобретению, преимущество также состоит в том, что в качестве активного полупроводникового материала может быть использован аморфный неорганический или органический полупроводниковый материал, но он не обязательно должен являться аморфным полупроводниковым материалом, поскольку он может быть также выбран из поликристаллических или микрокристаллических неорганических или органических полупроводниковых материалов.

Дополнительные признаки и преимущества станут очевидными из остальных зависимых пунктов приложенной формулы изобретения.

Теперь будет приведено более подробное описание изобретения со ссылкой на чертежи, на которых:

На фиг.1А показан вышеупомянутый пример из известного уровня техники.

На фиг. 1Б показан другой вышеупомянутый пример из известного уровня техники.

На фиг.1В изображен пример планарного полевого транзистора с управляющим р-n-переходом согласно известному уровню техники.

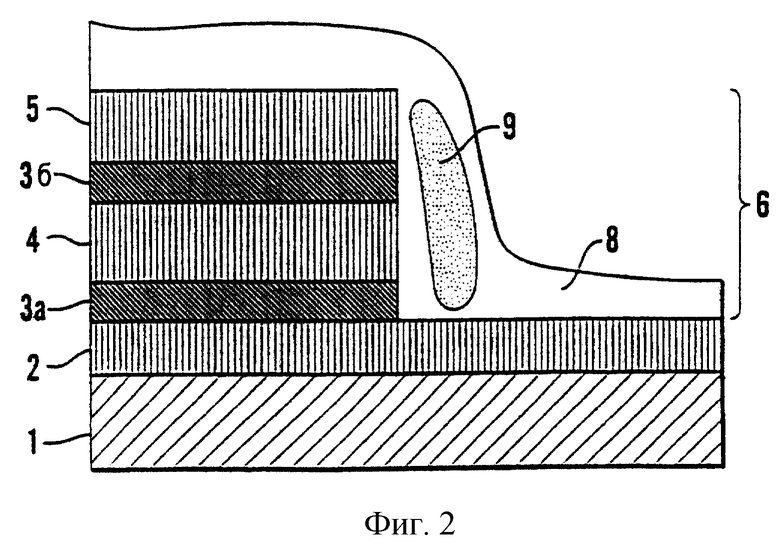

На фиг.2 изображен предпочтительный вариант осуществления полевого транзистора с управляющим р-n-переходом согласно изобретению.

На фиг. 3 изображен предпочтительный вариант осуществления полевого МОП-транзистора (MOSFET) согласно изобретению.

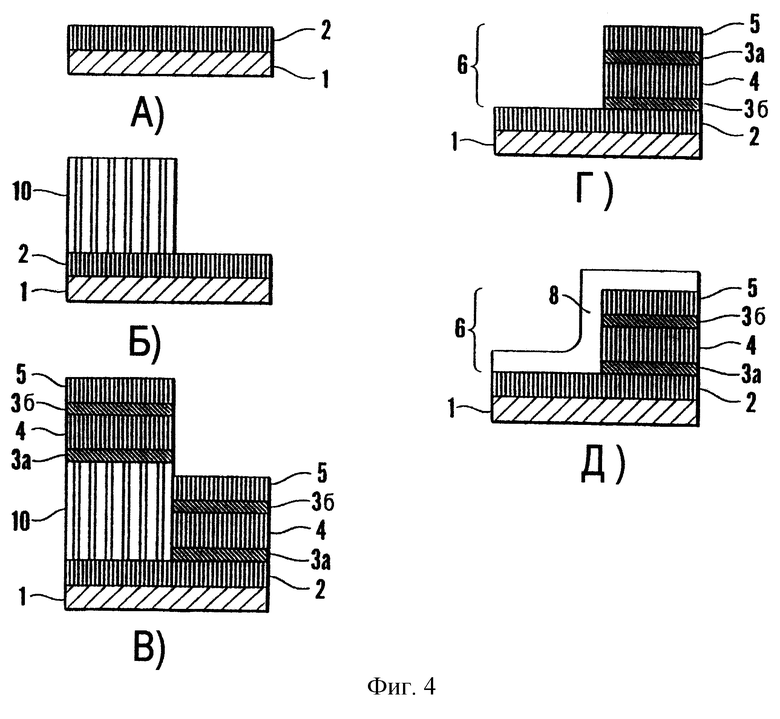

На фиг. 4А - 4Д показаны различные этапы процесса в варианте осуществления способа согласно изобретению, посредством которого осуществляют реализацию полевого транзистора в виде полевого транзистора с управляющим р-n-переходом, и

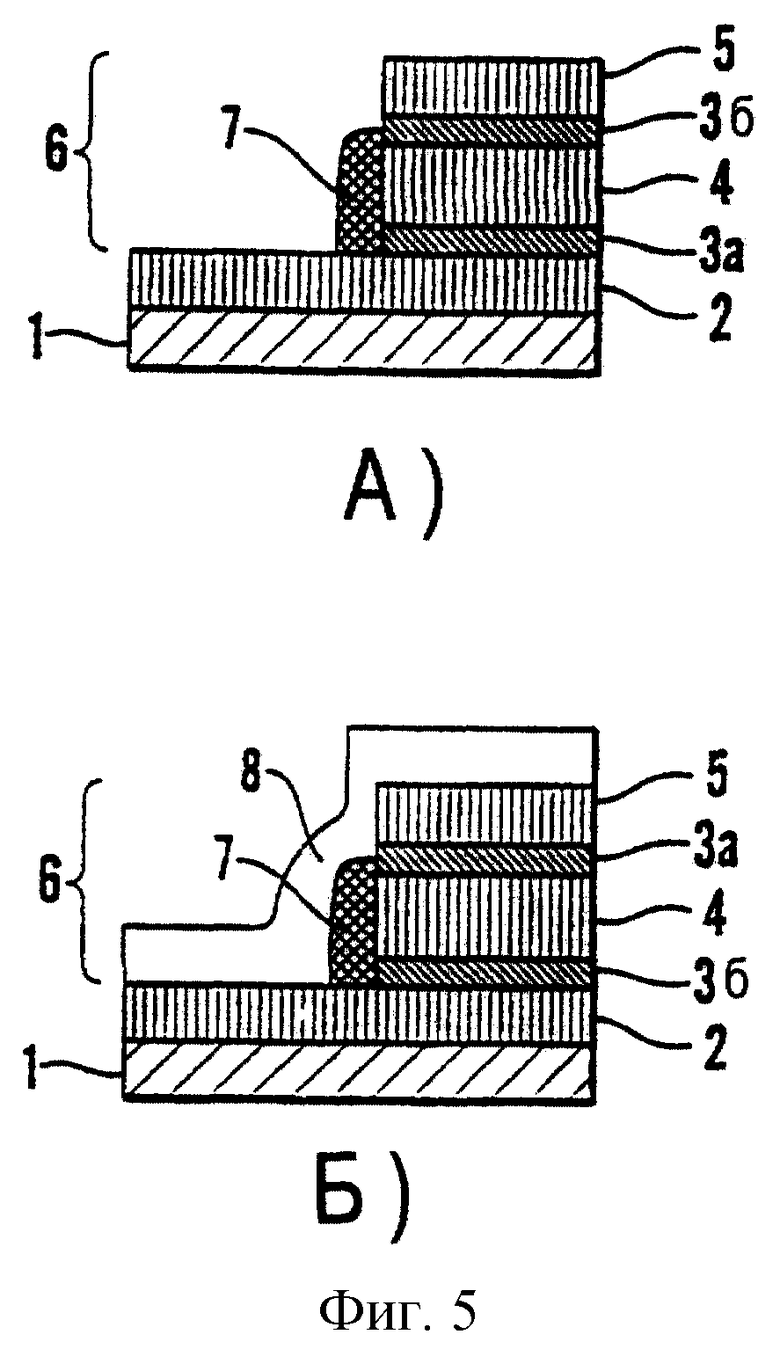

На фиг. 5А - 5Б показаны дополнительные этапы процесса для реализации полевого МОП-транзистора согласно изобретению.

На фиг.2 показан вариант осуществления полевого транзистора с управляющим р-n-переходом (ПТУП) (JFET) согласно изобретению. Он полностью выполнен посредством тонкопленочной технологии, более подробное объяснение которой будет приведено ниже. На подложке 1 обеспечивают слой 2 из проводящего материала, который формирует первый электрод транзистора. На этот слой нанесен изолирующий материал 3а, образующий первый изолятор, а на первый изолятор 3а нанесен дополнительный проводящий материал 4, например, металл, который образует второй электрод 4 транзистора. На второй электрод 4 нанесен изолирующий материал 3б, который формирует второй изолятор транзистора, а поверх второго изолятора 3б создают слой 5 из проводящего материала, образующий третий электрод транзистора.

В варианте реализации в виде полевого транзистора с управляющим р-n-переходом первый электрод 2 и третий электрод 5 теперь, соответственно, образуют электрод стока и электрод истока транзистора, или наоборот. Второй электрод 4 образует электрод затвора. На первом электроде 2 расположены второй и третий электроды 4, 5, а также изоляторы 3а, 3б, таким образом, что они образуют вертикальную ступеньку по отношению к первому электроду 2 и к подложке 1, продолжение которой на фиг.2 обозначено номером 6 ссылки. Таким образом, структура, состоящая из второго и третьего электродов 4, 5 и изолятора 3, закрывает только часть подложки 1, а горизонтальная протяженность слоев, образующих вертикальную ступеньку 6 на первом электроде 2 или на подложке 1, может быть сделана достаточно малой.

Поверх третьего электрода 5, который, например, может представлять собой электрод истока транзистора, поверх вертикальной ступеньки 6 и открытой вертикальной поверхности электрода 4 затвора, содержащегося в вертикальной ступеньке 6, создают слой 8, продолжающийся вниз до первого электрода 2, состоящий из активного полупроводникового материала, который может представлять собой аморфный, поликристаллический или микрокристаллический неорганический или органический полупроводниковый материал. Электрод затвора 2 и полупроводниковый материал 8 теперь образуют р-n переход. По существу, вертикальный канал транзистора 9 в активном полупроводящем материале 8 определяют либо как канал р-типа, либо как канал n-типа, и он имеет протяженность от первого электрода 2 до третьего электрода 5 и, по существу, расположен рядом с р-n-переходом в электроде 4 затвора. Реализованная таким образом структура, показанная на фиг.2, образует полевой транзистор с управляющим р-n-переходом (ПТУП) (JFET). Возможен как вариант его выполнения, в котором в качестве электрода стока используют первый электрод 2, а третий электрод 5 используют в качестве электрода истока, так и обратный вариант. Управление транзисторным эффектом, в этом случае - эффективным размером канала транзистора, осуществляют посредством электрического поля, которое прикладывают к каналу транзистора через р-n-переход.

На фиг.3 показан вариант осуществления полевого МОП-транзистора (MOSFET) согласно изобретению. Он полностью выполнен посредством тонкопленочной технологии, более подробное объяснение которой будет приведено ниже. На подложке 1 обеспечивают слой 2 из проводящего материала, который образует первый электрод транзистора. На этот слой нанесен изолирующий материал 3а, образующий первый изолятор, а на первый изолятор 3а нанесен дополнительный проводящий материал, например металл, который образует второй электрод 4 транзистора. На второй электрод 4 нанесен изолирующий материал 3б, который образует второй изолятор транзистора, а поверх второго изолятора 3б создают слой 5 из проводящего материала, образующий третий электрод транзистора.

В варианте реализации в виде полевого МОП-транзистора (MOSFET) первый электрод 2 и третий электрод 5 теперь, соответственно, образуют электрод стока и электрод истока транзистора, или наоборот. Второй электрод 4 образует электрод затвора. На первом электроде 2 расположены второй и третий электроды 4, 5, а также изоляторы 3а, 3б, таким образом, что они образуют вертикальную ступеньку относительно первого электрода 2 и подложки 1, продолжение которой на фиг.2 обозначено номером 6 ссылки. Таким образом, структура, состоящая из второго и третьего электродов 4, 5 и изолятора 3, закрывает только часть подложки 1, а горизонтальная протяженность слоев, образующих вертикальную ступеньку 6 на первом электроде 2 или на подложке 1, может быть сделана достаточно малой.

На открытой вертикальной поверхности электрода 4 затвора, содержащегося в вертикальной ступеньке 6, нанесен изолирующий материал 7, который образует изолятор затвора полевого транзистора. Поверх третьего электрода 5, который, например, может представлять собой электрод истока транзистора, поверх вертикальной ступеньки 6 создают слой, продолжающийся вниз до первого электрода 2, состоящий из активного полупроводникового материала, который может представлять собой аморфный, поликристаллический или микрокристаллический неорганический или органический полупроводниковый материал. Электрод 4 затвора изолирован от активного полупроводникового материала 8 изолятором 7 затвора таким образом, что инжекция заряда предотвращена. В активном полупроводниковом материале 8 выделен, по существу, вертикальный канал транзистора, и он имеет протяженность от первого электрода 2 до третьего электрода 5 и, по существу, расположен рядом с вертикальной ступенькой 6. Реализованная таким образом структура, показанная на фиг.2, образует полевой транзистор со структурой металл - оксид - полупроводник (полевой МОП-транзистор) (MOSFET). Возможен как вариант его выполнения, в котором в качестве электрода стока используют первый электрод 2, а третий электрод 5 используют в качестве электрода истока, так и обратный вариант. В зависимости от потенциала затвора, транзисторный эффект дает либо режим обеднения, либо режим обогащения.

Следует понимать, что подложка 1 в вариантах осуществления из фиг.2 и 3 предназначена исключительно для того, чтобы являться носителем структуры транзистора. Кроме того, проводящий слой 2 и первый электрод обеспечивают на всей подложке, то есть они не являются структурированными, но они равным образом могут быть структурированными и могут в этом случае, например, покрывать часть подложки, соответствующей той части, которая покрыта структурой с вертикальной ступенькой. Например в этом случае первый электрод в варианте осуществления из фиг.2 может находиться на одном уровне с поверхностью вертикальной ступеньки 6 и представлять собой вертикальную ступеньку по отношению к подложке 1. Эта вертикальная ступенька может при этом, например, находиться на одном уровне с вертикальной поверхностью изолятора 7 затвора. Конечно же, необходимым условием является обеспечение контакта с активным полупроводниковым материалом 8. Наличие первого электрода с вертикальной ступенькой относительно подложки может являться дополнительным преимуществом в том случае, если первый электрод должен иметь гальваническую связь с соответствующими электродами других транзисторов в транзисторной цепи. Для этой цели горизонтальная поверхность подложки может быть снабжена электрическим проводником вне вертикальной ступеньки.

Теперь, со ссылкой на фиг.4А - 4Д будет более подробно рассмотрен способ изготовления полевого транзистора с управляющим р-n-переходом согласно изобретению с использованием тонкопленочной технологии. Главной задачей, связанной с изготовлением полевых транзисторов с управляющим р-n-переходом, показанных на фиг. 2 и 3, является формирование вертикальной ступеньки, в которой транзисторный эффект будет присутствовать во всей своей полноте. Например, может быть использован так называемый способ обратной литографии, который доказал свою эффективность в качестве способа формирования вертикальной поверхности.

Следует понимать, что различные этапы процесса, которые изображены на фиг.4А - 4Д и будут рассмотрены ниже, представлены схематично и в упрощенном виде.

Как показано на фиг.4А, на первом этапе процесса на подложку 1, которая сама изготовлена из изолирующего или диэлектрического материала, наносят слой 2 из проводящего материала. Теперь проводящий материал 2 образует первый электрод транзистора. Поверх проводника 2 наносят фоторезист, на который накладывают маску и осуществляют травление согласно известной технологии фотолитографии таким образом, что на первом электроде 2 формируют структурированный слой 10 фоторезиста с вертикальной ступенькой 11. Это показано на фиг. 4Б и является вторым этапом процесса из настоящего способа. На третьем этапе процесса, показанном на фиг.4В, последовательно создают изолирующий слой 3а, который образует первый изолятор, проводник 4, который образует второй электрод транзистора, второй изолирующий слой 3б, который образует второй изолятор, а поверх них - слой 5 из проводящего материала, который образует третий электрод транзистора. Посредством использования, например, процесса осаждения из паров слои 3,4,5 теперь покрывают и открытую часть первого электрода 2, и верхнюю часть фоторезиста 10 в виде горизонтального многослойного покрытия, что очевидно из фиг.4В.

Теперь на четвертом этапе процесса для удаления слоя на верхней поверхности фоторезиста и самого фоторезиста 10 используют способ обратной литографии. Это осуществляют посредством процесса растворения, например, при помощи ацетона. Когда фоторезист 10 и слои на его верхней поверхности удалены, изделие после четвертого этапа процесса имеет вид, показанный на фиг.4Г, причем ступенька 6 ориентирована вертикально относительно первого электрода 2 или подложки 1.

Затем на пятом этапе процесса на первый электрод 2, второй электрод 4, вертикальную ступеньку 6 и на верхнюю поверхность третьего электрода 5 наносят растворимый активный аморфный полупроводниковый материал 8, что показано на фиг.4Д. Таким образом, активным полупроводником 8 покрывают слоистые структуры как по горизонтали, так и по вертикали. В том случае, когда первый электрод 2 является структурированным и покрывает только часть подложки 1, например, таким образом, что он сам по себе образует вертикальную ступеньку, которая находится на одном уровне с вертикальной ступенькой 6, дополнительных проблем, связанных с обеспечением контакта между первым электродом 2 и активным полупроводниковым материалом 8, не возникает.

При изготовлении полевого МОП-транзистора (MOSFET) с использованием тонкопленочной технологии согласно изобретению, после четвертого этапа процесса, показанного на фиг.4Г, применяют промежуточный этап процесса, показанный на фиг.5А. На этом дополнительном этапе процесса поверх второго электрода 4 создают изолирующий слой 6 таким образом, что его поверхность покрывает вертикальную ступеньку 6. Теперь этот изолирующий слой 7 содержит в себе изолятор затвора полевого МОП-транзистора и предотвращает инжекцию заряда. Изолятор 7 затвора может быть создан в процессе оксидирования при использовании первого электрода 2 в качестве подложки. В таком случае для формирования изолятора 7 затвора, ориентированного в вертикальном направлении таким образом, что он покрывает электрод 4 затвора, используют операцию вертикального травления. В альтернативном варианте изолятор 7 затвора также может быть осуществлен путем создания электрода 4 затвора в материале, который может быть селективно оксидирован или обработан тем или иным образом так, чтобы на поверхности электрода затвора сформировать изолирующий слой. В предпочтительном варианте это осуществляют путем селективного оксидирования материала поверхности электрода 4 затвора.

После создания изолятора 7 затвора на дополнительном этапе процесса, показанном на фиг.5А, на этапе процесса, показанном на фиг.5Б, поверх первого электрода 2, изолятора 7 затвора, вертикальной ступеньки 6 и верхней поверхности третьего электрода 5 наносят растворимый активный аморфный полупроводниковый материал 8. Этот этап процесса соответствует пятому этапу процесса, показанному на фиг.4Д.

Таким образом, активным полупроводниковым материалом 8 покрывают слоистые структуры как по горизонтали, так и по вертикали. В том случае, когда первый электрод 2 является структурированным и покрывает только часть подложки 1, но таким образом, что он слегка выступает за пределы вертикально уложенных слоев, дополнительных проблем, связанных с обеспечением контакта между первым электродом 2 и активным полупроводниковым материалом 8, не возникает.

Для нанесения активного аморфного полупроводникового материала 8 могут быть использованы такие способы, как сублимация в вакууме, вакуумное напыление, покрытие, полученное способом центрифугирования, и формование из раствора. При этом подразумевается, что активный аморфный полупроводниковый материал 8 в принципе может быть выполнен в виде различных структур, которые, например, покрывают электрод 4 затвора с различной ориентацией как по вертикали, так и по горизонтали. Также следует понимать, что для обеспечения полевого транзистора специальными функциями в аморфном полупроводниковом материале могут быть смешаны или объединены различные активные вещества. Если полевой транзистор представляет собой ПТУП (JFET), то может оказаться особенно желательным использовать такие материалы, которые самопроизвольно образуют барьер Шотки с электродом затвора, получая структуру полевого транзистора с барьером Шотки (MESFET).

Даже при том, что изготовление полевых транзисторов согласно изобретению из фиг. 2 и 3 показано, в принципе, для дискретных компонент, не имеется никаких возражений против изготовления транзисторов такого типа и использования способа в частично или полностью непрерывных технологических процессах с рулонной перемоткой с нанесением всех слоев. В этом случае процесс нанесения подобным способом активного полупроводникового материала 8 может быть непрерывным. Соответственно, если полевой транзистор представляет собой полевой МОП-транзистор, то и процесс нанесения подобным способом изолятора затвора также может быть непрерывным. При непрерывном процессе вертикальную ступеньку 6 в предпочтительном варианте формируют параллельной направлению перемещения партии изделий, а нанесение и изолятора 7 затвора, и активного полупроводникового материала может быть осуществлено в виде непрерывных полос на вертикальной ступеньке. После заключительного этапа процесса, показанного на фиг.4Д или на фиг.5Б, отдельные транзисторы могут быть отделены от партии изделий и скомплектованы в виде дискретных компонент.

Однако не имеется возражений против того, что из больших частей партии изделий с большим количеством транзисторов может быть сформирована транзисторная матрица, которая, в свою очередь, может быть использована для осуществления модулей активной памяти с отдельным транзистором в качестве запоминающего элемента. В этом случае транзистор должен быть соединен с гальванической цепью путем формирования соответствующих проводящих структур для обеспечения соединений.

Раскрытый здесь вертикальный полевой транзистор в общем случае может быть осуществлен в виде двух- и трехмерных структурных частей электронных интегральных схем. Возможными применениями таких схем могут быть устройства памяти, процессоры и т. д. Очевидное преимущество использования компонент активной памяти, основанных на транзисторах из настоящего изобретения, заключается в возможности записи в режиме малого сигнала и считывания в режиме большого сигнала, что, в частности, является преимуществом при электрической адресации ячеек памяти в модулях запоминающих устройств большой емкости, реализованных в матричной сети.

Что касается процесса изготовления полевых транзисторов согласно изобретению, то, как упомянуто выше, он может быть осуществлен в общем случае посредством использования непрерывных производственных линий. В этом случае полевые транзисторы ПТУП (JFET) и полевые МОП-транзисторы (MOSFET) для компонент СБИС (сверхбольших интегральных схем) (VLSI), имеющие структуру с вертикальной геометрией, возможно изготавливать также посредством способа литографии, а не только посредством использования известных процессов изготовления.

Создан полевой транзистор, имеющий электроды (2, 4, 5) и изоляторы (3) в вертикально расположенных слоях, такой, что, по меньшей мере, электроды (4, 5) и изоляторы (3) образуют ступеньку (6), ориентированную вертикально относительно первого электрода (2) или подложки (1). В вариантах осуществления в виде полевого транзистора с управляющим р-n переходом (ПТУП) или в виде полевого транзистора со структурой металл - оксид - полупроводник (полевого МОП-транзистора) электроды (2, 5) образуют соответственно электроды стока и источника полевого транзистора, или наоборот, а электрод (4) образует электрод затвора полевого транзистора, поверх слоев вертикальной ступеньки (6) нанесен аморфный поликристаллический или микрокристаллический неорганический или органический полупроводниковый материал, образующий активный полупроводник транзистора, который имеет прямой или косвенный контакт с электродом (8) затвора и образует вертикально ориентированный канал (9) транзистора р- или n-типа между первым (2) и вторым (5) электродами. В способе изготовления полевого транзистора вертикальную ступеньку (6) формируют посредством фотолитографического процесса, а нанесение растворимого активного аморфного полупроводникового материала (8) поверх первого электрода (2) и вертикальной ступеньки (6) осуществляют таким образом, что между электродами стока и истока (2, 5) получают вертикально ориентированный канал транзистора. В ПТУП полупроводниковый материал (8) непосредственно соприкасается с электродом (4) затвора. В полевом МОП-транзисторе между электродом затвора (4) и полупроводниковым материалом (8) создают вертикально ориентированный изолятор (7) затвора. Техническим результатом является получение достаточной длины канала на меньшей площади. 3 с. и 14 з.п. ф-лы, 7 ил.

| US 4677451 А, 30.06.1987 | |||

| US 4735918 А, 05.04.1988 | |||

| ПОЛЕВОЙ ВЕРТИКАЛЬНЫЙ ТРАНЗИСТОР | 1992 |

|

RU2045112C1 |

| SU 1482479 А1, 27.11.1996. | |||

Авторы

Даты

2002-09-20—Публикация

1999-01-14—Подача