Область назначения изобретения

Настоящее изобретение относится к устройству обработки данных, передаваемых от передатчика к приемнику.

Уровень техники

В наземной системе связи 8 VSB (т.е. наземной системе связи с частично подавленной боковой полосой, которая передает символы, каждый из которых имеет один из 8 возможных уровней сигнала) информация обычно передается передающей станцией к принимающей станции по воздуху. В одном примере такой системы каждые два бита, подлежащих передаче данных, кодируются передающей станцией как символ, имеющий один из восьми возможных уровней амплитуды сигнала, так что каждый байт данных, имеющий восемь бит, представлен четырьмя символами.

В одной такой системе, раскрытой в стандарте для цифрового телевидения ATSC, опубликованном 16 сентября 1995 г., каждая пара бит подается в устройство предварительного кодирования (предкодер) и в решетчатый кодер. Устройство предварительного кодирования и решетчатый кодер, каждый из них, включает в себя двенадцать битовых элементов задержки. Таким образом, устройство предварительного кодирования и решетчатый кодер можно представить как двенадцать тождественных устройств предварительного кодирования и решетчатых кодеров с (1) входным мультиплексором для последовательного соединения входных наборов из двух бит с двенадцатью тождественными устройствами предварительного кодирования и решетчатыми кодерами и (2) выходным мультиплексором для последовательного соединения выходных наборов из трех бит с устройством отображения символов. Двенадцать устройств предварительного кодирования и решетчатых кодеров чередуют пары бит таким образом, что каждая пара бит в первом байте данных обрабатывается первым устройством предварительного кодирования и решетчатым кодером, каждая пара бит во втором байте данных обрабатывается вторым устройством предварительного кодирования и решетчатым кодером,... и так, что каждая пара бит в двенадцатом байте данных обрабатывается двенадцатым устройством предварительного кодирования и решетчатым кодером. Каждые последующие наборы из двенадцати бит обрабатываются аналогичным образом.

Устройство предварительного кодирования и решетчатый кодер преобразуют каждую пару входных бит в три соответствующие выходные биты, которые подаются в устройство отображения символов. Устройство отображения символов преобразовывает каждую последовательность из трех выходных бит в символ, имеющий соответствующий один из восьми уровней сигнала в восьмиуровневую совокупность. Получившиеся символы подаются в мультиплексор, который добавляет символы синхронизации к символам данных, чтобы структурировать данные и символы синхронизации в блоке.

Блок структурирован таким образом, что он имеет 313 сегментов. Первый сегмент блока (сегмент синхронизации блока) включает в себя (1) синхронизирующий участок сегмента, содержащий четыре символа синхронизации сегмента, и (2) синхронизирующий участок поля, содержащий 828 псевдослучайно генерированных синхронизирующих символов поля. Каждый из других 312 сегментов включает в себя (1) синхронизирующий участок сегмента, содержащий четыре символа синхронизации сегмента, и (2) участок данных, содержащий 828 символов данных.

После этого символы в описанной выше структуре блока передаются и принимаются приемником. Приемник включает в себя гребенчатый фильтр и решетчатый декодер. Гребенчатый фильтр присутствует для того, чтобы отфильтровывать интерференцию, которая может вызываться каналами НТСЦ (Национального комитета по телевидению США), вещающими с соседних станций. Решетчатый декодер в приемнике присутствует для того, чтобы декодировать символы в принимаемых блоках в их соответствующие первоначальные пары бит. Решетчатый декодер аналогичен решетчатому кодеру в том смысле, что решетчатый декодер обрабатывает символы одного и того же байта вместе. Таким образом, эти символы должны поступать в решетчатый декодер в правильной последовательности.

Как можно заметить из приведенного выше описания блока данных, блоки данных, используемые в типичной системе 8 VSB, содержат только 17,25 групп символов данных на сегмент данных, причем каждая группа содержит двенадцать байтов, когда каждый байт содержит четыре символа. Соответственно, каждый сегмент данных каждого блока данных переносит неполную группу данных, так что байты неполной группы расщеплены между двумя сегментами данных. В результате синхронизирующие символы сегмента в синхронизирующем участке сегмента данных отделяют некоторые символы данных некоторых байтов от других символов данных этих байтов. Таким образом, если символы данных уплотняются в блок данных в той же последовательности, в какой они выдаются устройством отображения (преобразования) символов, символы не поступят в решетчатый декодер в правильной последовательности. Соответственно, решетчатый декодер в приемнике не будет обрабатывать символы одних и тех же байтов вместе, что вызовет ошибки при декодировании передаваемых символов.

Данное изобретение предполагает наличие устройства для чередования (циклического сдвига) данных, подлежащих включению в структуру блока данных, таким образом, что символы поступают в решетчатый декодер в правильной последовательности, так что можно избежать ошибок в декодировании, вызываемых наличием синхронизирующих символов сегмента. Данное изобретение также предполагает наличие приемника для обработки таких чередующихся данных.

Сущность изобретения

В соответствии с одним аспектом данного изобретения устройство обработки обрабатывает элементы данных, которые нужно вставить в блок данных. Блок данных имеет ряд сегментов данных, и каждый сегмент данных имеет синхронизирующий участок и участок данных. Устройство обработки содержит средство кодирования, средство чередования и средство вставки. Средство кодирования кодирует данные как элементы данных. Средство чередования чередует элементы данных, так что элементы данных, соответствующие друг другу по синхронизирующему участку сегмента, располагаются так, чтобы их обрабатывали вместе. Средство вставки вставляет чередующиеся элементы данных в участки данных блока данных.

В соответствии с другим аспектом данного изобретения приемник принимает символы данных, организованные в блок данных. Блок данных имеет ряд сегментов данных. Каждый сегмент данных имеет синхронизирующий участок и участок данных. Каждый синхронизирующий участок содержит четыре синхронизирующих символа, а каждый участок данных содержит 828 символов данных. Символы данных чередуются, так что символы данных одних и тех же байтов, разделенные синхронизирующим участком сегмента данных, располагаются так, чтобы их обрабатывали вместе. Приемник содержит принимающее средство и средство обработки. Принимающее средство принимает символы данных блока данных. Средство обработки обрабатывает соответствующие пары символов данных тех же самых байтов вместе, даже если символы данных тех же самых байтов разделены синхронизирующими участками каждого сегмента данных.

В соответствии с еще одним аспектом данного изобретения приемник принимает элементы данных, организованные в блок данных. Блок данных имеет ряд сегментов данных, так что каждый сегмент данных имеет синхронизирующий участок и участок данных. Каждый синхронизирующий участок содержит S синхронизирующих элементов, а каждый участок данных содержит N элементов данных. Элементы данных чередуются, так что элементы данных, соответствующие друг другу по каждому синхронизирующему участку каждого сегмента данных, располагаются для совместной обработки. Приемник содержит принимающее средство и средство обработки. Принимающее средство принимает элементы данных блока данных. Средство обработки обрабатывает соответствующие пары элементов данных в зависимости от разделения между соответствующими элементами данных по синхронизирующим участкам каждого элемента данных.

Краткое описание чертежей

Эти и другие признаки и преимущества данного изобретения станут очевиднее из подробного рассмотрения изобретения в сочетании с чертежами, на которых приведены:

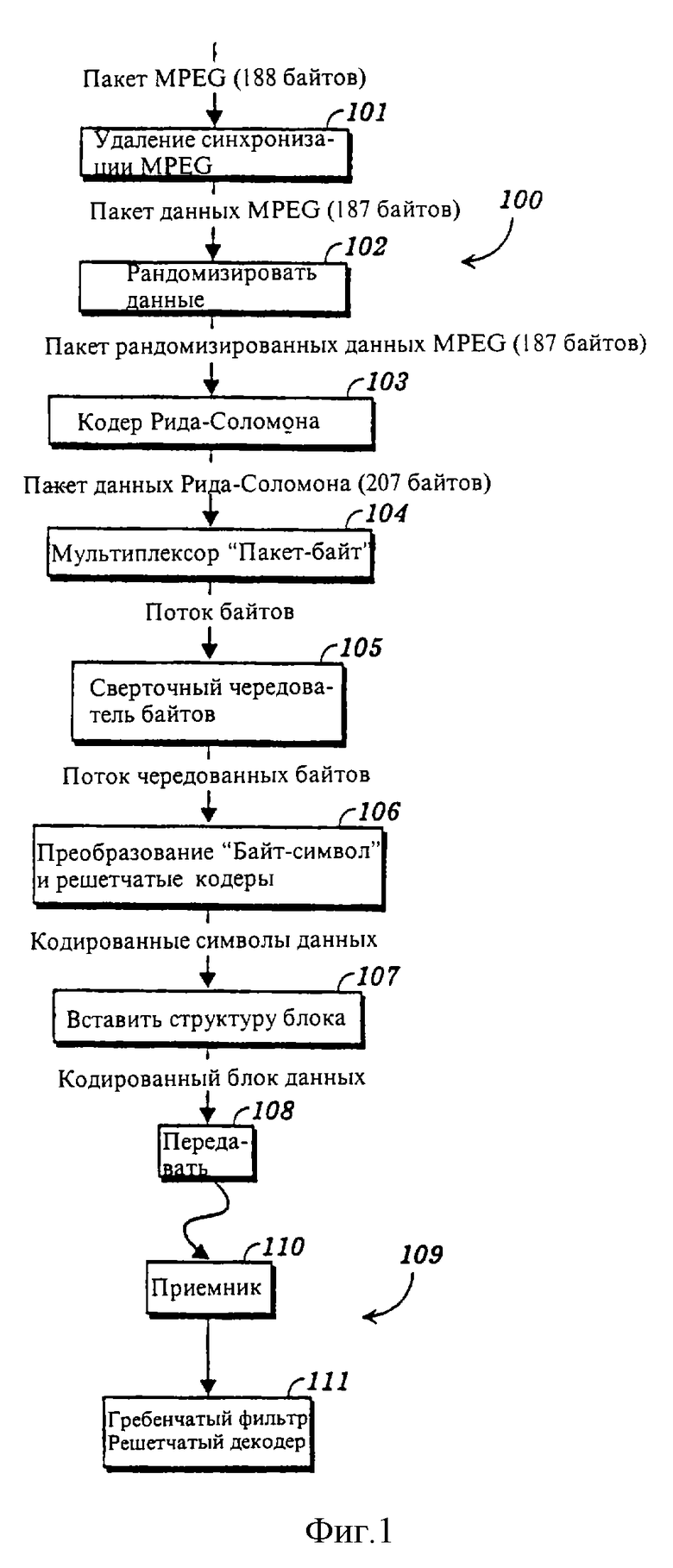

фиг.1 - блок-схема устройства, воплощающего данное изобретение;

фиг. 2 - генератор псевдослучайных чисел, который можно реализовать для рандомизатора данных фиг.1 для того, чтобы рандомизировать данные;

фиг. 3 - свертывающее устройство чередования байтов, которое можно реализовать для свертывающего устройства чередования байтов фиг.1;

фиг. 4 - группирование символов как результат кодирования преобразователем байтов в символы и решеточным кодером фиг.1;

фиг.5 - чередующиеся символы фиг.4, к которым добавлены синхронизирующие символы сегмента;

фиг. 6 - более подробно преобразователь типа байт-символ и решеточный кодер фиг.1;

фиг.7 - таблица, показывающая чередование (ротацию) байтов, реализованное вращателем байтов фиг.6;

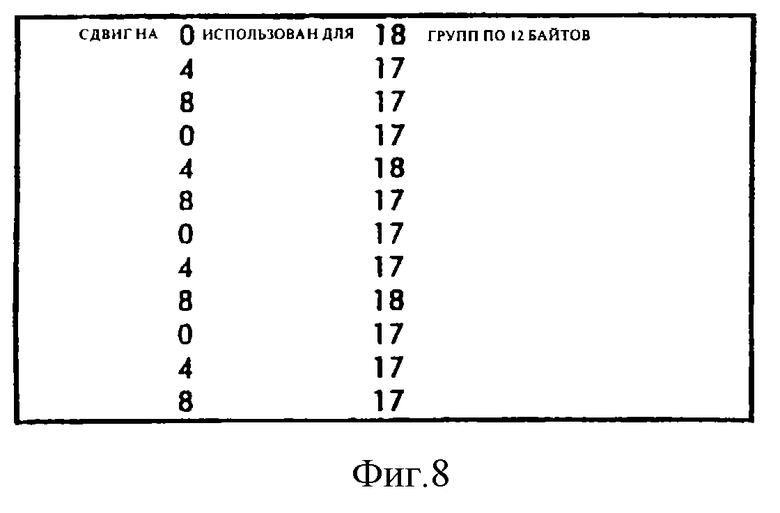

фиг. 8 - таблица, показывающая соответствие между чередованием, реализованным в соответствии с таблицей фиг.7, и группами чередуемых данных;

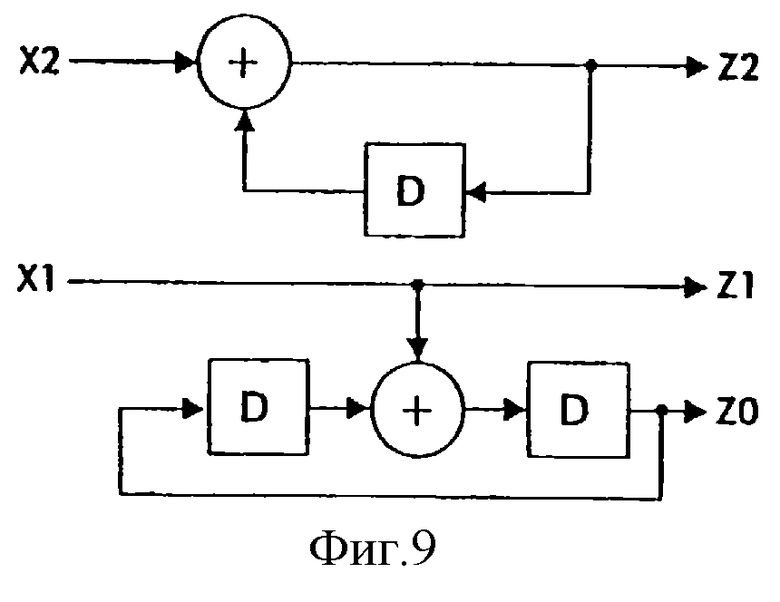

фиг.9 - устройство предварительного кодирования и решеточный кодер, которые можно использовать в таком их качестве на фиг.6;

фиг. 10 - таблица, показывающая чередование, реализуемое вращателем символов фиг.6;

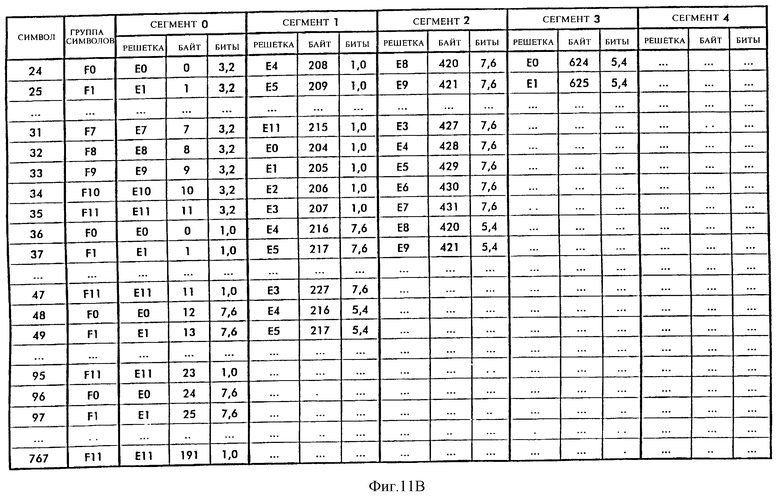

фиг. 11А, 11В, 11С и 11D - таблицы, показывающие последовательность, с которой символы данных вставляются в блок данных согласно данному изобретению;

фиг. 12 - структура блока данных, в которых вводятся данные согласно данному изобретению;

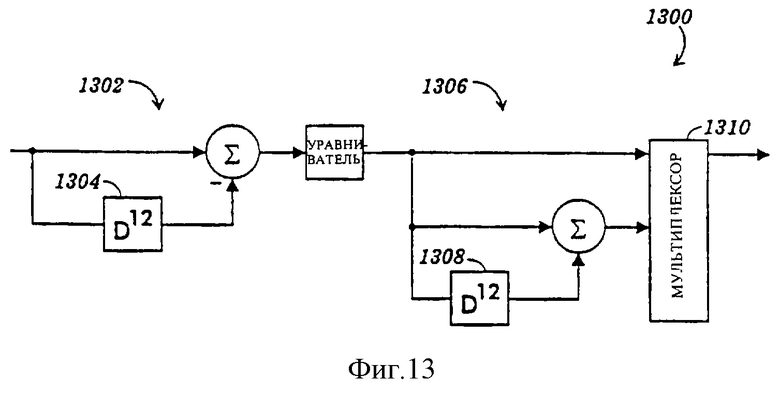

фиг.13 - гребенчатый фильтр, который вносит правильную величину задержки для данных, представленных на фиг.11А, 11В, 11С и 11D для того, чтобы решетчатый декодер в приемнике правильно совместно обрабатывал символы одного и того же байта.

Подробное описание

Как показано на фиг.1, первая станция 100 включает в себя компенсатор синхронизации 101 MPEG, который получает пакеты данных MPEG из источника данных MPEG2 (не показан) и который полнее описан в заявке 08/479428, поданной 7 июня 1995 г. Пакеты данных MPEG приходят со скоростью примерно 12,893 Кпакета в секунду. Эти пакеты MPEG включают в себя 187 байтов данных MPEG и один байт синхронизации MPEG. Поскольку синхронизация MPEG не нужна для обработки оставшейся части кодером наземного модема 8 VSB, согласно данному изобретению компенсатор синхронизации 101 MPEG удаляет один байт синхронизации MPEG из пакетов MPEG и пропускает только 187 байтов данных MPEG к рандомизатору данных 102, который рандомизирует каждый пакет данных MPEG, выдаваемый компенсатором синхронизации 101 MPEG. Рандомизатор данных 102 может осуществлять битовую операцию ИСКЛЮЧАЮЩЕЕ ИЛИ между каждым байтом данных, получаемых от компенсатора синхронизации 101 MPEG, и псевдослучайной последовательностью.

Псевдослучайную последовательность можно получить, например, с помощью генератора псевдослучайных последовательностей, показанного на фиг.2. Псевдослучайная последовательность, сформированная генератором псевдослучайных последовательностей фиг. 2, инициализируется у первого пакета данных блока данных и после этого повторно инициализируется через каждый 312 пакетов данных. Регистры этого генератора случайных последовательностей, показанного на фиг. 2, инициализируются на OxF180 в начале каждого блока данных (где выходы регистров Х16, Х15, Х14, Х13, Х9, Х8 установлены на значение один). Генератор псевдослучайных последовательностей, показанный на фиг.2, опережает на каждый байт входного пакета данных. Псевдослучайная последовательность, формируемая этим генератором случайных последовательностей, выдается на выходах D0-D7, которые могут быть соединены с соответствующими входами ИСКЛЮЧАЮЩЕЕ ИЛИ. Другие входы ИСКЛЮЧАЮЩЕЕ ИЛИ принимают соответствующие биты в байтах от компенсатора синхронизации 101 MPEG.

Выходной сигнал от рандомизатора 102 данных подается в кодер 103 Рида-Соломона. Кодер 103 Рида-Соломона высчитывает двадцать байтов контроля по четности Рида-Соломона и прилагает эти двадцать байтов к пакетам рандомизированных данных, выдаваемых рандомизатором 102 данных. Соответственно, кодер 103 Рида-Соломона формирует пакеты данных, каждый из которых содержит 207 байтов (т. е. 187 байтов рандомизированных данных от рандомизатора 102 данных и двадцать байтов четности Рида-Соломона).

Пакеты данных от кодера 103 Рида-Соломона подаются в мультиплексор 104 типа "пакет-байт". Мультиплексор 104 типа "пакет-байт" преобразует каждый пакет данных Рида-Соломона из 207 байтов в непрерывный поток байтов. Затем этот поток байтов обрабатывается свертывающим устройством 105 чередования байтов, которое условно показано на фиг.3 и которое полнее описано в заявке 08/315153, которая была подана 29 сентября 1994 г. Каждый блок на фиг.3 является регистром, хранящим один байт. Свертывающее устройство 105 чередования байтов синхронизовано таким образом, что первый байт первого пакета данных Рида-Соломона поступает в самое верхнее плечо устройства чередования, показанного на фиг.3, второй байт первого пакета данных Рида-Соломона поступает во второе плечо устройства чередования, показанного на фиг.3,... пятьдесят второй байт первого пакета данных Рида-Соломона поступает в самое нижнее плечо устройства чередования, показанного на фиг.3, пятьдесят третий байт пакета данных Рида-Соломона поступает в самое верхнее плечо устройства чередования, показанного на фиг.3, и т.д.

Поток чередующихся байтов от свертывающего устройства 105 чередования байтов подается к преобразователю "байт-символ" и к решетчатому кодеру 106, который кодирует биты данных в принимаемых байтах как символы данных. Как будет подробнее объяснено ниже, часть решетчатого кодера преобразователя "байт-символ" и решетчатый кодер 106 - это, в результате, двенадцать решетчатых кодеров, предназначенных для размещения задержки на двенадцать символов гребенчатого фильтра, который используется в приемнике, таком, как вторая станция 109 на фиг.1. То есть присутствие гребенчатого фильтра в приемнике требует, чтобы преобразователь "байт-символ" и решетчатый кодер 106 кодировали биты данных принимаемых байтов данных как кодированные символы данных, так что кодированные символы данных каждого решетчатого кодера были разделены символами данных одиннадцати других решетчатых кодеров. Поэтому в результате имеется двенадцать решетчатых кодеров. Кроме того, преобразователь "байт-символ" и решетчатый кодер 106 должны кодировать пары бит данных принимаемых байтов данных как кодированные символы данных, так что пары бит данных одних и тех же байтов кодируются одним и тем же кодером.

На фиг. 4 представлены переданные символы данных. Например, символ Е0 группы n-1 может представлять собой символ, полученный в результате кодирования кодером ноль бит 7, 6 байта ноль, символ Е0 группы n может представлять собой символ, полученный в результате кодирования кодером ноль бит 5, 4 байта ноль, символ Е0 группы n+1 может представлять собой символ, полученный в результате кодирования кодером ноль бит 3, 2 байта ноль, и т.д. Таким образом, каждый символ Е0 отделен от других ближайших символов Е0 одиннадцатью символами.

Аналогичным образом, символ Е1 группы n-1 может представлять собой символ, полученный в результате кодирования кодером один бит 7, 6 байта один, символ Е1 группы n может представлять собой символ, полученный в результате кодирования кодером один бит 5, 4 байта один, символ Е1 группы n+1 может представлять собой символ, полученный в результате кодирования кодером один бит 3, 2 байта один и т.д. Каждый символ Е1 отделен от других ближайших символов Е1 одиннадцатью символами. Таким образом, кодер ноль кодирует символы первого байта, кодер один кодирует символы второго байта, кодер два кодирует символы третьего байта и т.д. Соответственно, символы кодируются по группам из двенадцати байтов и передаются группами из двенадцати байтов.

Как говорилось выше, каждый сегмент включает в себя 832 символа в потоке данных. Эти 832 символа включают в себя четыре синхронизирующих сегмент символа и 828 символов данных. Таким образом, символы данных в передаваемом потоке данных периодически прерываются синхронизирующими сегмент символами, как показано на фиг. 5. Поскольку передаваемые символы данных из каждого кодера должны быть отделены друг от друга, чтобы их можно было правильно обработать решетчатым декодером приемника, и поскольку синхронизирующие сегмент символы, в противном случае, нарушили бы нужное расстояние между символами данных, в настоящем изобретении символы данных ротируются (чередуются) в каждом сегменте на заранее установленную величину, чтобы восстановить символы данных на нужном расстоянии друг от друга.

Например, эта величина чередования может быть нулевой для символов данных в первом сегменте данных, следующих за синхронизирующим блок данных сегментом, может быть равна четырем для символов в следующем сегменте данных, может быть равна восьми для символов данных в следующем сегменте данных, может быть нулевой для символов данных в следующем сегменте данных и т.д. Таким образом, символ данных, следующий немедленно за синхронизирующими сегмент символами в участке данных первого сегмента данных следом за тем же самым синхронизирующим блок данных сегментом, - это символ Е0, соответствующий решетчатому кодеру ноль. Следующие символы данных в этом сегменте данных по порядку - это Е1, Е2, Е3, Е4, Е5, Е6, Е7, Е8, Е9, Е10 и Е11, как показано группой (n-1) символов данных на фиг.5. Эта структура повторяется на протяжении этого сегмента данных (сегмент ноль), как показано решетчатым столбцом для сегмента 0 на таблицах фиг.11А, 11В, 11С и 11D.

Однако символ данных, следующий сразу же за синхронизирующими сегмент символами (т.е. синхронизирующими сегмент символами S0, S1, S2 и S3 на фиг. 5) во втором сегменте данных, следующем за синхронизирующим блок данных сегментом, - это символ Е4, соответствующий решетчатому кодеру четыре. Следующие символы данных в этом сегменте данных по порядку - это Е5, Е6, Е7, Е8, Е9, Е10, Е11, Е0, Е1, Е2 и Е3, как показано группой (n) символов на фиг.5. Эта структура повторяется по всему этому сегменту данных (сегмент один), как показано решетчатым столбцом для сегмента 1 на таблицах фиг.11А, 11В, 11С и 11D.

Аналогичным образом, символ данных, следующий сразу же за синхронизирующими сегмент символами (т.е. синхронизирующими сегмент символами S0, S1, S2 и S3) в третьем сегменте данных, следующем за синхронизирующим блок данных сегментом, - это символ Е8, соответствующий решетчатому кодеру восемь. Следующие символы данных в этом сегменте данных по порядку - это Е9, Е10, Е11, Е0, Е1, Е2, Е3, Е4, Е5, Е6 и Е7. Эта структура повторяется по всему этому сегменту данных (сегмент два), как показано решетчатым столбцом для сегмента 2 на таблицах фиг.11А, 11В, 11С и 11D.

Преобразователь "байт-символ" и решетчатый кодер 106, которые показаны подробнее на фиг.6, преобразуют поток чередующихся байтов от свертывающего устройства 105 чередования байтов в символы, имеющие правильную последовательность символом, которую должна должным образом обработать вторая станция 109 (фиг.1). Преобразователь "байт-символ" и решетчатый кодер 106 включают в себя демультиплексор 201 байтов, вращатель 202 байтов, мультиплексоры 203 типа "байт-пара бит", устройства предварительного кодирования и решетчатые кодеры 204, вращатель символов 205 и мультиплексор 206 символов.

Поток чередующихся байтов от свертывающего устройства 105 чередования байтов поступает в демультиплексор 201 байтов. Байты группируются демультиплексором 201 байтов в группы байтов, содержащих двенадцать байтов на группу. Эти двенадцать байтов появляются на выходах В0-В11 демультиплексора 201 байтов. Каждая группа из двенадцати байтов чередуется вращателем 202 байтов. Вращатель 202 байтов имеет выходы С0-С11 и чередует байты на выходах В0-В11 демультиплексора 201 байтов согласно таблице, представленной на фиг.7. Как показано на таблицах фиг.11А, 11В, 11С и 11D, порядок байтов в потоке чередующихся байтов, подаваемом в преобразователь "байт-символ" и решетчатый кодер 106, меняется из-за чередования (ротации) символов, которое реализуется благодаря синхронизирующим сегмент символам в начале каждого сегмента данных. Чередование байтов в каждой группе байтов, выдаваемой демультиплексором 201 байтов к вращателю 202 байтов, желательно, чтобы восстановить порядок байтов вследствие регулировки, сделанной из-за синхронизирующих сегмент символов.

Как показано в таблице фиг.7, вращатель 202 байтов чередует байты на выходах В0-В11 на ноль, четыре или восемь позиций. Это чередование байтов реализуется, чтобы правильно приписать байты требуемому решетчатому кодеру. Чередование байтов следует периодической структуре, которая повторяется после каждых двенадцати сегментов блока данных. Длительность каждого чередования байтов следует повторяющейся структуре 18, 17, 17, 17. То есть, как показано в таблице фиг.8, первые восемнадцать групп двенадцати байтов, принимаемых вращателем 202 байтов, чередуются на ноль следующие семнадцать групп двенадцати байтов чередуются на четыре следующие семнадцать групп двенадцати байтов, принимаемых вращателем 202 байтов, чередуются (вращаются) на восемь, следующие семнадцать групп двенадцати байтов, принимаемых вращателем 202 байтов, чередуются на ноль, следующие восемнадцать групп двенадцати байтов, принимаемых вращателем 202 байтов, чередуются на четыре, и т.д., так что эта структура 18, 17, 17, 17... повторяется через каждые двенадцать сегментов данных.

Это чередование байтов показано на фиг.11А, 11В, 11С и 11D. Фиг.11А, 11В, 11С и 11D показывают первые пять сегментов данных, следующих за синхронизирующим блок данных сегментом блока данных. Последние восемь символов данных сегмента данных ноль (т.е. символы данных 816-827 на фиг.11D) соответствуют парам бит 7, 6 байтов 204-215. Эти байты 204-215 завершаются первыми 36 символами данных в сегменте данных один. 828 символов данных в сегменте данных ноль и первые 36 символов данных в сегменте данных один представляют собой первые восемнадцать групп из двенадцати байтов данных, обрабатываемых вращателем 202 байтов. Как указывалось выше, вращатель 202 байтов применяет нулевое чередование к этим первым восемнадцати группам из двенадцати байтов. Эти первые 216 байтов подаются по порядку (без чередования) на соответствующие решетчатые кодеры Е0-Е11.

Затем вращатель 202 байтов применяет чередование четыре к следующим семнадцати группам байтов данных, принимаемых вращателем 202 байтов, чтобы вернуть байты в их начальный порядок следования байтов. Эти байты являются байтами 216-419. Это чередование на четыре заставляет эти байты кодироваться соответствующими решетчатыми кодерами Е4-Е3. Таким образом, символ данных тридцать шесть в сегменте данных один, соответствующем битам 7, 6, - это байт 216 и соответствует решетчатому кодеру четыре. Соответственно, порядок следования байтов восстанавливается в сегменте данных один, начиная с символа данных тридцать шесть. Эти семнадцать групп из двенадцати байтов заканчиваются символом данных двадцать три сегмента данных два.

Затем вращатель 202 байтов применяет чередование восемь к следующим семнадцати группам из двенадцати байтов, принимаемых вращателем 202 байтов, чтобы вернуть байты в их начальный порядок следования байтов. Эти байты являются байтами 420-623. Это чередование на восемь заставляет эти байты кодироваться соответствующими решетчатыми кодерами Е8-Е7. Таким образом, символ данных двадцать четыре в сегменте данных два, соответствующем битам 7, 6, - это байт 420 и соответствует решетчатому кодеру восемь. Соответственно, порядок следования байтов восстанавливается в сегменте данных два, начиная с символа данных двадцать четыре. Эти семнадцать групп по двенадцати байтов заканчиваются символом данных одиннадцать сегмента данных три.

Затем вращатель 202 байтов применяет чередование ноль к следующим семнадцати группам из двенадцати байтов, принимаемым вращателем 202 байтов, чтобы вернуть байты в их начальный порядок следования байтов. Эти байты являются байтами 624-827. Это нулевое чередование заставляет эти байты кодироваться соответствующими решетчатыми кодерами Е0-Е11. Таким образом, символ данных двенадцать в сегменте данных три, соответствующий битам 7, 6, - это байт 624 и соответствует решетчатому кодеру ноль. Эти семнадцать групп из двенадцати байтов кончаются символом данных 827 сегмента данных три. Соответственно, порядок следования байтов восстановлен в сегменте данных три, начиная с символа данных двенадцать.

Мультиплексоры 203 "байт-пара бит" мультиплексируют каждый байт данных, подаваемых на выходные линии С0-С11 вращателем 202 данных, в четыре соответствующих последовательности пар бит. Эти биты выдаются мультиплексором 203 "байт-пара бит" на выходы D0-D11 и обрабатываются устройствами предварительного кодирования и решетчатыми кодерами 204. Устройства предварительного кодирования и решетчатые кодеры 204 преобразуют пары бит на выходах D0-D11 в соответствующие наборы трех выходных бит и преобразовывают наборы трех выходных бит в символы данных. Таким образом, каждый символ данных имеет один из восьми возможных уровней, определяемых тремя битами. Устройства предварительного кодирования и решетчатые кодеры 204 включают в себя устройства предварительного кодирования и решетчатые кодеры Е0-Е11, который выдают символы данных через соответствующие выходы Е0-Е11.

На фиг. 9 показаны устройство предварительного кодирования и решетчатый кодер. Устройство предварительного кодирования и решетчатый кодер фиг.9 можно дублировать двенадцать раз, чтобы отдельно кодировать каждый поток пар бит на соответствующих выходах D0-D11 мультиплексора 203 "байт-пара бит". В этом случае элементы задержки устройства предварительного кодирования и решетчатого кодера фиг.9 - это элементы задержки на один бит. Соответственно, бит Х2 пары бит в потоке D0 пар бит кодируется устройством предварительного кодирования устройства предварительного кодирования и решетчатого кодера Е0 как выходной бит Z2, а бит Х1 пары бит в потоке D0 пар бит кодируется решетчатым кодером устройства предварительного кодирования и решетчатого кодера Е0 как выходные биты Z1 и Z0. Устройство преобразования (отображения) символов (не показано) устройства предварительного кодирования и решетчатого кодера Е0 преобразует выходные биты Z2, Z1, Z0 в соответствующий символ данных. Аналогичным образом, бит Х2 пары бит в потоке D1 пар бит кодируется устройством предварительного кодирования устройства предварительного кодирования и решетчатого кодера Е1 как выходной бит Z2, а бит Х1 пары бит в потоке D1 пар бит кодируется решетчатым кодером устройства предварительного кодирования и решетчатого кодера Е1 как выходные биты Z1 и Z0. Устройство преобразования символов устройства предварительного кодирования и решетчатого кодера Е1 преобразует эти выходные биты Z2, Z1, Z0 в соответствующий символ данных. Остальные потоки байтов аналогичным образом обрабатываются другими устройствами предварительного кодирования и решетчатыми кодерами Е2-Е11.

Символы данных на выходных линиях Е0-Е11 устройства предварительного кодирования и решетчатых кодеров 204 чередуются вращателем 205 символов согласно таблице, показанной на фиг.10. Это чередование (ротация) символов обеспечивает необходимые расстояния между двенадцатью символами каждого кодированного потока символов в рамках сегмента и по синхронизирующим символам сегмента. Каждое чередование применяется ко всем шестидесяти девяти группам из двенадцати символов данных в участке данных сегмента данных. Соответственно, символы данных в участке данных первого сегмента данных (сегмент ноль), следующие за синхронизирующим блок данных сегментом, чередуются с нулем, символы данных в участке данных второго сегмента данных (сегмент один) чередуются на четыре, символы данных в участке данных третьего сегмента данных (сегмент два) чередуются на восемь, символы данных в участке данных четвертого сегмента данных (сегмент три) чередуются с нулем, и так далее по всем 312 сегментам данных блока данных.

Таким образом, со ссылками на фиг.10 и на фиг.11А, 11В, 11С и 11D, символы данных сегмента ноль (первый сегмент данных, следующий за синхронизирующим блок данных сегментом) чередуются с нулем. Соответственно, кодированные символы данных от кодеров Е0, Е1, Е2,... Е11 на фиг.6 появляются на выходах F0, F1, F2,... F11 вращателя 205 символов и передаются в порядке Е0-Е11. Однако символы в сегменте данных один (второй сегмент данных, следующий за синхронизирующим блок данных сегментом) чередуются на четыре. Таким образом, кодированные символы данных от кодеров Е4, Е5, Е6,... Е11, Е0,... Е3 на фиг. 6 появляются на выходах F0, F1, F2,... F11 вращателя 205 символов и передаются в порядке Е4,... Е3.

Более того, символы данных в сегменте данных два (третий сегмент данных, следующий за синхронизующим блок данных сегментом) чередуются на восемь. Таким образом, кодированные символы данных от кодеров Е8, Е9, Е10, Е11, Е0,... Е7 на фиг.6 появляются на выходах F0, F1, F2,... F11 вращателя 205 символов и передаются в порядке Е8, . .. Е7. Символы данных в сегменте данных три (четвертый сегмент данных, следующий за синхронизирующим блок данных сегментом) чередуются с нулем. Соответственно, кодированные символы данных от кодеров Е0, Е1, Е2,... Е11 на фиг.6 появляются на выходах F0, F1, F2,... F11 вращателя 205 символов и передаются в порядке Е0-Е11.

При таком распределении чередования первый символ данных в сегменте данных один (т.е. символ данных, соответствующий битам 5, 4 байта 208) обрабатывается с символом, который передается на двенадцать символов раньше (т.е. символом данных, соответствующим битам 7, 6 байта 208). Аналогичным образом, второй символ данных в сегменте данных один (т.е. символ данных, соответствующий битам 5, 4 байта 209) обрабатывается с символом данных, который передается на двенадцать символов раньше (т.е. символом данных, соответствующим битам 7, 6 байта 209). Аналогично каждый из символов данных, соответствующий битам 5, 4 байтов 210-215, обрабатывается во второй станции 109 с битами 7, 6 байтов 210-215, имеющих место до четырех символов сегмента, которые вставляются в начале сегмента данных один.

Однако символ данных, соответствующий битам 5, 4 байта 204 отделен двадцатью тремя другими символами данных от символа, соответствующего битам 7, 6 байта 204. Соответственно, как будет обсуждено ниже, девятый, десятый, одиннадцатый и двенадцатый символы данных в сегменте данных, следующем за четырьмя синхронизирующими сегмент символами в начале сегмента данных, имеют место спустя двадцать четыре символа после предыдущих символов данных от соответствующих решетчатых кодеров. Поэтому эта задержка на двадцать четыре символа должна приниматься во внимание, чтобы эти символы данных, соответствующие битам 5, 4 в этих байтах 204-207, могли быть обработаны с символами, соответствующими битам 7, 6 соответствующих байтов 204-207 около конца сегмента данных ноль. После этого в сегменте данных один задержку на двенадцать символов снова можно использовать во второй станции 109.

Соответственно, вращатель 205 символов вместе с задержкой на двенадцать и двадцать четыре символа, наложенной второй станцией 109, обеспечивает, чтобы символы данных одних и тех же байтов обрабатывались одним и тем же решетчатым кодером и потому обрабатывались вместе. Аналогичным образом вращатель 202 байтов обеспечивает, чтобы вслед за этим переходом по синхронизирующему сегмент участку байты чередовались так, чтобы они опять были в восходящем порядке, а не в смешанном порядке.

Мультиплексор 206 мультиплексирует символы данных, выдаваемых вращателем 205 символов, обратно в поток символов данных, который подается в устройство ввода 107 в структуру блока данных (фиг.1). Устройство ввода 107 в структуру блока данных делает вставку в структуру блока данных путем добавления синхронизирующего блок данных сегмента и синхронизирующие сегмент символы к символам данных в структуре данных, которая была обсуждена выше и представлена на фиг.12. Соответственно, блок данных включает в себя синхронизирующий блок данных сегмент (который является первым сегментом в блоке данных) и 312 сегментов данных. Начало каждого сегмента включает в себя четыре синхронизирующих сегмент символа. Передатчик 108 принимает блоки данных от устройства ввода 107 в структуру блока данных, осуществляет некоторое согласование устройств по уровням сигнала по данным, содержащимся в блоках данных, и передает блоки символов в структуре блока данных, показанной на фиг. 12.

Вторая станция 109 принимает информацию, передаваемую первой станцией 100, чтобы декодировать символы к их соответствующим парам бит Х2/Х1. Вторая станция 109 включает в себя, кроме всего прочего, приемник 110 и гребенчатый фильтр и решетчатый декодер 111. Приемник 110 осуществляет некоторое согласование по уровням сигнала, такое как демодуляция. Гребенчатый фильтр и решетчатый декодер 111 отфильтровывают интерференцию от соседних станций НТСЦ и декодируют символы для восстановления начальных бит.

Гребенчатый фильтр 1300, который является участком гребенчатого фильтра и решетчатого декодера 111, показан на фиг.13. Этот участок решетчатого декодера гребенчатого фильтра и решетчатого декодера 111 может быть обычным декодером Витерби.

Гребенчатый фильтр 1300 включает в себя первый участок 1302 фильтра, который имеет элемент задержки 1304 для наложения задержки в двенадцать символов на символы данных, обрабатываемые гребенчатым фильтром 1300. Гребенчатый фильтр 1300 также включает в себя второй участок 1306 фильтра, который имеет дополнительный элемент задержки 1308 для наложения второй задержки в двенадцать символов на символы данных, обрабатываемые гребенчатым фильтром 1300. Первый и второй участки фильтров 1302 и 1306 могут разделяться обычным выравнивателем. Мультиплексор 1310 выбирает первый участок фильтра 1302 для всех символов данных в сегменте данных за исключением от девятого до двенадцатого символов данных вслед за четырьмя синхронизирующими сегмент символами в начале каждого сегмента данных. Соответственно, все символы данных в сегменте данных за исключением от девятого до двенадцатого символов данных вслед за четырьмя синхронизирующими сегмент символами в начале сегмента данных обрабатываются с задержкой в двенадцать символов. В противном случае мультиплексор 1310 выбирает второй участок фильтра 1306 для от девятого до двенадцатого символов данных вслед за четырьмя синхронизирующими сегмент символами в начале сегмента данных. Соответственно, от девятого до двенадцатого символов данных вслед за четырьмя синхронизирующими сегмент символами в начале сегмента данных обрабатываются с задержкой в двадцать четыре символа.

Определенные модификации данного изобретения были обсуждены выше. Другие модификации представятся тем, кто на практике реализует это изобретение. Например, можно использовать одно устройство предварительного кодирования и решетчатый кодер для устройства предварительного кодирования и решетчатых кодеров 204 (Е0-Е11), если элементы задержки в устройстве предварительного кодирования и решетчатом кодере, показанных на фиг.9, - это элементы задержки на двенадцать бит. Поскольку элемент задержки имеет длину двенадцать бит, устройство предварительного кодирования и решетчатый кодер, показанные на фиг. 9, - это эквивалент двенадцати устройств предварительного кодирования и решетчатых кодеров 204 (Е0-Е11), показанных на фиг.6. Например, устройство предварительного кодирования и решетчатый кодер на фиг.9 обрабатывают биты 7 (Х2) и 6 (Х1) байта ноль, а на двенадцать символов позже обрабатывают биты 5 (Х2) и 4 (Х1) байта ноль. Аналогичным образом, устройство предварительного кодирования и решетчатый кодер, показанные на фиг.9, обрабатывают биты 7 (Х2) и 6 (Х1) байта один, а двенадцатью символами позже обрабатывают биты 5 (Х2) и 4 (Х1) байта один. Если используются устройство предварительного кодирования и решетчатый кодер, показанные на фиг.9, с задержкой в двенадцать символов, демультиплексор 201 байтов можно исключить, вращатель 202 байтов может содержать, например, память и адресатор, который записывает байты в память и считывает их из нее, так что байты чередуются, как говорилось выше, мультиплексор 203 типа "байт-пара бит" можно исключить, вращатель 205 символов может содержать, например, память и адресатор, который записывает символы в память и считывает их из нее, так что символы чередуются, как говорилось выше, и мультиплексор 206 символов можно исключить.

Более того, хотя данное изобретение было здесь конкретно раскрыто в терминах символов данных, имеющих по соответствующему одному из восьми возможных уровней сигнала, возможно, что передаваемые данные могут быть элементы данных, имеющие любое количество возможных уровней сигнала. Кроме того, здесь были раскрыты конкретные кодеры и декодеры. Однако в этом изобретении можно использовать другие виды кодеров и декодеров. В дополнение, можно исключить вращатель 202 байтов. Если это так, то вторую станцию 109 можно организовать так, чтобы она распознавала правильное соответствие между символами данных и байтами. Функции описанных здесь блоков можно в качестве альтернативы реализовать программными средствами.

Соответственно, описание данного изобретения следует толковать только как иллюстрацию и как объяснение для специалистов лучшего пути осуществления изобретения. Детали могут быть значительно изменены, не отходя от сущности изобретения, и оговаривается исключительное использование всех модификаций, включенных в объем прилагаемой формулы изобретения.

Изобретение относится к устройствам обработки данных, передаваемых от передатчика к приемнику. Достигаемый технический результат - исключение ошибок при декодировании передаваемых символов. Первая станция кодирует данные как символы данных, циклически сдвигает символы данных так, что символы данных, соответствующие друг другу по участкам синхронизации сегментов данных блока данных, располагаются так, чтобы их обрабатывали вместе, и вставляет циклически сдвинутые символы данных в участки данных сегментов данных блока данных так, что блок данных имеет ряд сегментов данных, где каждый сегмент данных имеет участок синхронизации сегмента и участок данных. Вторая станция обрабатывает символы данных, так что соответствующие символы данных в первом наборе символов данных обрабатываются с задержкой в двенадцать символов данных и соответствующие символы данных во втором наборе символов данных обрабатываются с задержкой в двадцать четыре символа данных в зависимости от позиций символов данных относительно синхронизирующих участков. 2 c. и 15 з.п. ф-лы, 13 ил.

| Приспособление в пере для письма с целью увеличения на нем запаса чернил и уменьшения скорости их высыхания | 1917 |

|

SU96A1 |

| СПОСОБ КОДИРОВАНИЯ ЦИФРОВОЙ ИНФОРМАЦИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1992 |

|

RU2060593C1 |

| Кодер телевизионного сигнала | 1988 |

|

SU1681385A1 |

| US 5535228 A, 09.07.1996 | |||

| US 5509031 A, 16.04.1996 | |||

| Устройство для кодирования чернобелых изображений | 1977 |

|

SU666659A1 |

Авторы

Даты

2003-01-10—Публикация

1997-09-11—Подача