Область техники, к которой относится изобретение

Настоящее изобретение относится к устройству обработки данных и способу обработки данных и, в частности, к устройству обработки данных и способу обработки данных, которые позволяют повысить устойчивость к ошибке данных.

Уровень техники

LDPC (код контроля четности с низкой плотностью) имеет высокую способность коррекции ошибок и в последнее время широко принят в передающей системе, включающей в себя спутниковое цифровое широковещание, такое как DVB (цифровое видеошироковещание)-S.2, выполненное в Европе (например, смотри непатентную литературу 1). В дополнение к этому, проведены исследования принятия LDPC-кода к наземному цифровому широковещанию следующего поколения.

Из приведенных недавно исследований известно, что производительность, близкая к пределу Шеннона, получается из LDPC-кода, когда длина кода увеличивается, аналогично турбокоду. Так как LDPC-код имеет свойство, которое состоит в том, что кратчайшее расстояние пропорционально длине кода, LDPC-код имеет преимущества, связанные с превосходными характеристиками вероятности блочной ошибки, и редко встречается так называемое явление минимального уровня ошибок, наблюдаемого в характеристике декодирования турбокода, в качестве его характеристики.

В дальнейшем будет, главным образом, описан LDPC-код. LDPC-код является линейным кодом, и LDPC-код необязательно должен представлять собой двоичный код. Однако, в этом случае, предполагается, что LDPC-код является двоичным кодом.

Максимальная характеристика LDPC-кода состоит в том, что матрица контроля четности, определяющая LDPC-код, является разреженной. В этом случае, разреженная матрица представляет собой матрицу, в которой число 1 элементов матрицы является очень маленьким (то есть матрицу, в которой большая часть элементов равна 0).

Фиг.1 иллюстрирует пример матрицы Н контроля четности LDPC-кода.

В матрице H контроля четности, показанной на фиг.1, вес каждого столбца (вес столбца) (число 1) становится равным "3", и вес каждой строки (вес строки) становится равным "6".

При кодировании с использованием LDPC-кода (LDPC-кодирование), например, порождающая матрица G генерируется на основе матрицы Н контроля четности, и порождающая матрица G умножается на двоичные информационные биты таким образом, чтобы сгенерировать кодовое слово (LDPC-код).

В частности, устройство кодирования, которое выполняет LDPC-кодирование, сначала вычисляет порождающую матрицу G, в которой выполняется выражение GHT=0, между транспонированной матрицей HT матрицы Н контроля четности и порождающей матрицей G. В этом случае, когда порождающая матрица G представляет собой матрицу K×N, устройство кодирования перемножает порождающая матрица G с битовой строкой (вектором и) информационных бит, включающих в себя N битов, и генерирует кодовое слово с (= uG), включающее в себя N битов. Кодовое слово (LDPC-код), которое генерируется с помощью кодирующего устройства, принимается на приемной стороне через заданный канал связи.

LDPC-код можно декодировать с помощью алгоритма, который называется вероятностным декодированием, предложенным Галлагером (Gallager), то есть алгоритм передачи сообщений, использующий распространение степени уверенности на так называемом графе Таннера (Tanner), включающим в себя переменный узел (который также называется узлом сообщения) и проверочный узел. В дальнейшем переменный узел и проверочный узел будут, соответственно, называться просто узлами.

Фиг.2 иллюстрирует последовательность декодирования LDPC-кода.

В дальнейшем, действительное значение, которое получается путем представления правдоподобия, равного 0, значения i-того бита кода LDPC-кода (одного кодового слова), принятого на приемной стороне с помощью отношения логарифмического правдоподобия, соответственно, называется как значение u0i приема. В дополнение к этому, сообщение, выводимое из проверочного узла, называется как uj, и сообщение, выводимое из переменного узла, называется как vi.

Сначала, при декодировании LDPC-кода, как иллюстрировано на фиг.2, на этапе S11 принимают LDPC-код, сообщению (сообщению проверочного кода) uj присваивают начальное значение 0, и переменной k, принимающей целочисленные значения в качестве счетчика процесса повторения, присваивают начальное значение 0, и процесс продолжается на этапе S12. На этапе S12 сообщение (сообщение переменного узла) vi вычисляется путем выполнения операции (операции переменного узла), представленной выражением (1), на основании значения u0i приема, полученного путем приема LDPC-кода, и сообщение uj вычисляется путем выполнения операции (операции проверочного узла) представленной выражением (2) на основании сообщения vi.

(Выражение 1)

(Выражение 2)

В этом случае, dv и dc в выражениях (1) и (2) представляют собой параметры, которые показывают числа 1 матрицы H контроля четности в продольном направлении (столбец) и в поперечном направлении (строка), соответственно, и можно произвольно установить, соответственно. Например, в случае кода (3, 6), dv принимает значение 3, и dc принимает значение 6.

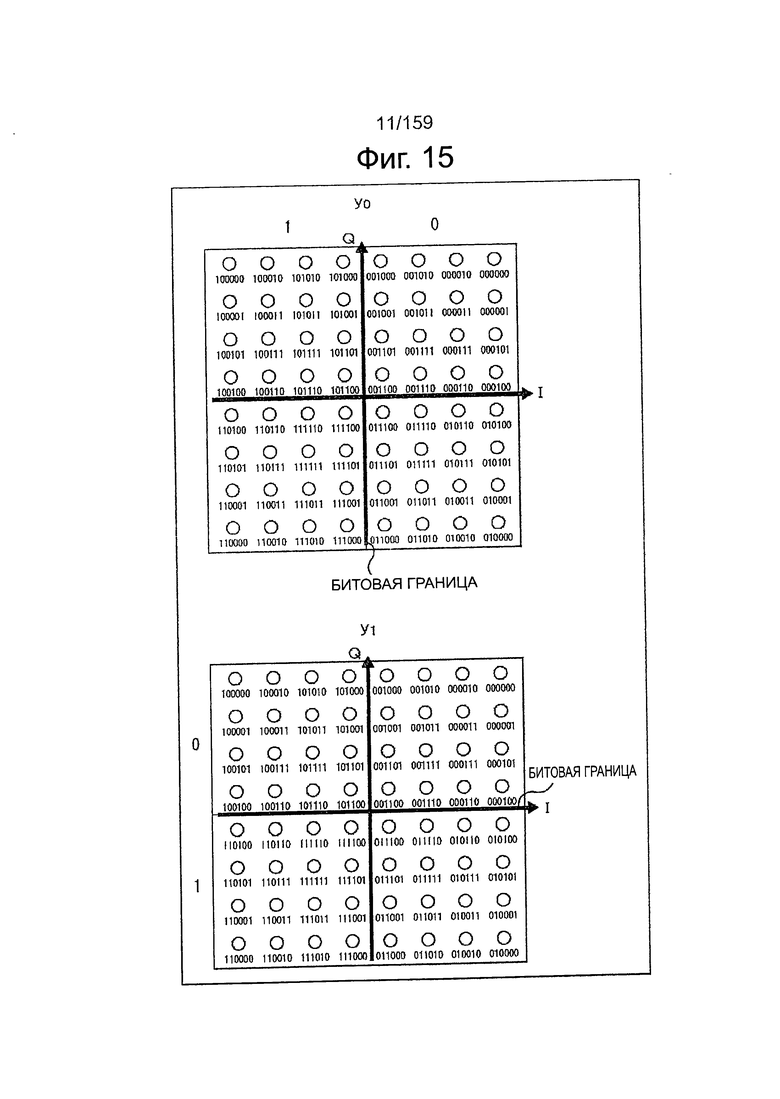

При работе переменного узла согласно выражению (1) и при работе проверочного узла согласно выражению (2), так как сообщение, выходящее из ребра графа (линия, связывающая переменный узел и проверочный узел) для вывода сообщения, не является целью работы, рабочий диапазон становится равным от 1 до dv - 1 или от 1 до dc - 1. Работа проверочного узла согласно выражению (2) выполняется фактически за счет предварительного создания таблицы функции R (v1, v2), представленной выражением (3), определенным одним входом по отношению к двум выходам v1 и v2 и использующего таблицу последовательно (рекурсивно), как представлено выражением (4).

(Выражение 3)

(Выражение 4)

На этапе S12 переменная k увеличивает свое значение на 1, и процесс переходит к этапу S13. На этапе S13 определяют, больше ли значение переменной k, чем заданное число раз C повторного декодирования. Когда на этапе S13 определено, что переменная k не больше, чем C, процесс возвращается на этап S12, и в дальнейшем повторяется тот же самый процесс.

Когда на этапе S13 определено, что переменная k больше, чем C, процесс переходит на этап S14, сообщение vi, которое соответствует результату декодирования, который будет окончательно выводиться, вычисляется путем выполнения операции, представленной выражением (5), и выводится, и процесс декодирования LDPC-кода заканчивается.

(Выражение 5)

В этом случае, работа согласно выражению (5) выполняется с использованием сообщений uj из всех ребер, соединенных с переменным узлом, которая отличается от работы переменного узла согласно выражению (1).

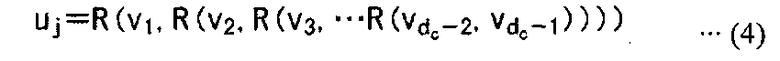

Фиг.3 иллюстрирует пример матрицы Н контроля четности LDPC-кода (3, 6) (скорость кодирования равна 1/2, и длина кода равна 12).

В матрице H контроля четности, показанной на фиг.3, вес столбца установлен на 3, и вес строки установлен на 6 аналогично фиг.1.

Фиг.4 иллюстрирует граф Таннера матрицы H контроля четности, показанной на фиг.3.

На фиг.4 проверочный узел представлен знаком "+", и переменный узел представлен знаком "=". Проверочный узел и переменный узел соответствуют строке и столбцу матрицы H контроля четности. Линия, которая соединяет проверочный узел и переменный узел, представляет собой ребро и соответствует значению 1 элементов матрицы контроля четности.

Иными словами, когда элемент j-ой строки и i-го столбца матрицы контроля четности равен 1, как показано на фиг.4, i-ый переменный узел (узел "=") с верхней стороны и j-ый проверочный узел (узел "+") с верхней стороны соединены ребром. Ребро показывает, что бит кода, соответствующий переменному узлу, имеет условие ограничения, соответствующее проверочному узлу.

В алгоритме суммы произведений, который представляет собой способ декодирования LDPC-кода, операция переменного узла и операция проверочного узла выполняются последовательно одна за другой.

Фиг.5 иллюстрирует операцию переменного узла, которая выполняется с помощью переменного узла.

В переменном узле сообщение vi, которое соответствует ребру для вычисления, вычисляется с помощью операции переменного узла согласно выражению (1) с использованием сообщений u1 и u2 из оставшихся ребер, соединенных с переменным узлом, и значения u0i приема. Сообщения, которые соответствуют другим ребрам, также вычисляются тем же самым способом.

Фиг.6 иллюстрирует операцию проверочного узла, которая выполняется с помощью проверочного узла.

В этом случае, операцию проверочного узла согласно выражению 2 можно переписать с помощью выражения 6, используя уравнение в виде выражения a×b=exp{ln(|a|)+ln(|b|)}×sign(a)×sign(b). Однако значение sign(x) равно 1 в случае x≥0, и равно -1 в случае x<0.

(Выражение 6)

При x≥0, если функция ϕ(x) задана в виде выражения ϕ(x)=ln(tanh(x/2)), выполняется выражение ϕ-1(x)=2tanh-1 (e-x). По этой причине выражение (6) можно заменить на выражение (7).

(Выражение 7)

В проверочном узле операция проверочного узла согласно выражению (2) выполняется согласно выражению (7).

Иными словами, в проверочном узле, как иллюстрировано на фиг.6, сообщение uj, которое соответствуют ребру графа для вычисления, вычисляется с помощью операции проверочного узла согласно выражению (7) с использованием сообщений v1, v2, v3, v4, и v5 из оставшихся ребер, соединенных с проверочным узлом. Сообщения, которые соответствуют другим ребрам, также вычисляются с помощью того же самого способа.

Функцию ϕ(x) из выражения (7) можно представить в виде ϕ(x)=ln((ex+1)/(ex-1)), и условие ϕ(x)=ϕ-1(x) выполняется при x>0. Когда функции ϕ(x) и ϕ-1(x) осуществлены в аппаратных средствах, функции ϕ(x) и ϕ-1(x) можно осуществить с использованием LUT (справочная таблица). Однако обе функции ϕ(x) и ϕ-1(x) принимают вид той же самой LUT.

Цитируемая литература

Непатентная литература

Непатентная литература 1: DVB-S.2: ETSI EN 302 307 V1.1.2 (2006-06)

Раскрытие изобретения

Техническая задача

LDPC-код принят для DVB-S.2 в качестве стандарта спутникового цифрового широковещания или DVB-T.2 в качестве стандарта наземного цифрового широковещания следующего поколения. Помимо этого планируется принятие LDPC-кода в DVB-C.2 в качестве стандарта цифрового широковещания следующего поколения CATV (кабельного телевидения).

При цифровом широковещании на базе стандарта DVB, такого как DVB-S.2, LDPC-код принимает вид символа (символизируется) ортогональной модуляцией (цифровой модуляцией), такой как QPSK (квадратурная фазовая манипуляция), и символ отображается в сигнальную точку и передается.

При символизации LDPC-кода выполняется перестановка кодовых битов LDPC-кода в блоке кодовых битов из двух битов или более, и переставленные кодовые биты принимают вид битов символа.

В качестве способа перестановки кодовых бит для символизации LDPC-кода предложены различные способы. Например, способ перестановки определен в DVB-T.2.

Между тем, DVB-T.2 является стандартом цифрового широковещания, который используется исключительно для фиксированного оконечного устройства, такого как телевизионный приемник, установленный дома, и который не может соответствовать предъявляемым требованиям при цифровом широковещании, которое используется исключительно для портативного оконечного устройства.

Иными словами, по сравнению с фиксированном оконечным устройством, в портативном оконечном устройстве необходимо уменьшить размеры схемы и уменьшить потребляемую мощность. Поэтому в цифровом широковещании, которое используется исключительно для портативного оконечного устройства, для того, чтобы облегчить нагрузку, необходимую для обработки, такой как декодирование LDPC-кода в портативном оконечном устройстве, число раз повторений (число раз C повторного декодирования) декодирования LDPC-кода или кодовой длины LDPC-кода можно сократить больше, чем в случае цифрового широковещания, используемого исключительно для фиксированного оконечного устройства.

Однако в рамках ограничений необходимо поддерживать до некоторой степени устойчивость к ошибке.

Настоящее изобретение было выполнено с учетом вышеупомянутых обстоятельств, и оно позволяет обеспечить устойчивость к ошибке данных, таких как LDPC-код.

Решение задачи

Согласно первому варианту осуществления настоящей технологии выполнены устройство обработки данных или способ обработки данных, включающее в себя, соответственно, блок кодирования или этап кодирования, для выполнения LDPC-кодирования, при котором длина кода составляет 16200 битов, и скорость кодирования составляет 1/3, на основе матрицы контроля четности LDPC-кода, и блок перестановки или этап перестановки, для выполнения перестановки кодовых битов кодированного LDPC-кода с символьными битами символа, соответствующего любой одной из 16 сигнальных точек, определенных с помощью 16QAM. Кодированный LDPC-код включает в себя информационные биты и биты четности. Матрица контроля четности включает в себя область информационной матрицы, соответствующую информационным битам, и область матрицы четности, соответствующую битам четности. Область информационной матрицы представлена с помощью таблицы исходных значений матрицы контроля четности. Таблица исходных значений матрицы контроля четности представляет собой таблицу, которая представляет позиции элементов 1 области информационной матрицы для каждых 360 столбцов, и сконфигурирована следующим образом:

416 8909 4156 3216 3112 2560 2912 6405 8593 4969 6723 6912

8978 3011 4339 9312 6396 2957 7288 5485 6031 10218 2226 3575

3383 10059 1114 10008 10147 9384 4290 434 5139 3536 1965 2291

2797 3693 7615 7077 743 1941 8716 6215 3840 5140 4582 5420

6110 8551 1515 7404 4879 4946 5383 1831 3441 9569 10472 4306

1505 5682 7778

7172 6830 6623

7281 3941 3505

10270 8669 914

3622 7563 9388

9930 5058 4554

4844 9609 2707

6883 3237 1714

4768 3878 10017

10127 3334 8267.

Когда кодовые биты из 8 битов, сохраненные в восьми запоминающих устройствах, имеющих объем памяти 16200/8 битов, и побитно считанные из соответствующих запоминающих устройств, назначены двум последовательным символам, блок перестановки или этап перестановки устанавливает (#i+1)-ый бит из наиболее значимого бита кодовых битов из 8 битов в качестве бита b#i и (#i+1)-го бита из наиболее значимого бита символьных битов из 8 битов из двух символов в качестве бита y#i и выполняет перестановку битов b0, b1, b2, b3, b4, b5, b6 и b7 с битами y6, y0, y3, y4, y5, y2, y1 и y7, соответственно.

Согласно второму варианту осуществления настоящей технологии выполнены устройство обработки данных или способ обработки данных, включающее в себя, соответственно, блок кодирования или этап кодирования, для выполнения LDPC-кодирования, при котором длина кода составляет 16200 битов, и скорость кодирования составляет 2/5, на основе матрицы контроля четности LDPC-кода, и блок перестановки или этап перестановки, для выполнения перестановки кодовых битов кодированного LDPC-кода с символьными битами символа, соответствующего любой одной из 16 сигнальных точек, определенных с помощью 16QAM. Кодированный LDPC-код включает в себя информационные биты и биты четности. Матрица контроля четности включает в себя область информационной матрицы, соответствующую информационным битам, и область матрицы четности, соответствующую битам четности. Область информационной матрицы представлена с помощью таблицы исходных значений матрицы контроля четности. Таблица исходных значений матрицы контроля четности представляет собой таблицу, которая представляет позиции элементов 1 в области информационной матрицы для каждых 360 столбцов, и сконфигурирована следующим образом:

5650 4143 8750 583 6720 8071 635 1767 1344 6922 738 6658

5696 1685 3207 415 7019 5023 5608 2605 857 6915 1770 8016

3992 771 2190 7258 8970 7792 1802 1866 6137 8841 886 1931

4108 3781 7577 6810 9322 8226 5396 5867 4428 8827 7766 2254

4247 888 4367 8821 9660 324 5864 4774 227 7889 6405 8963

9693 500 2520 2227 1811 9330 1928 5140 4030 4824 806 3134

1652 8171 1435

3366 6543 3745

9286 8509 4645

7397 5790 8972

6597 4422 1799

9276 4041 3847

8683 7378 4946

5348 1993 9186

6724 9015 5646

4502 4439 8474

5107 7342 9442

1387 8910 2660.

Когда кодовые биты из 8 битов, сохраненные в восьми запоминающих устройствах, имеющих объем памяти 16200/8 битов, и побитно считанные из соответствующих запоминающих устройств, назначены двум последовательным символам, блок перестановки или этап перестановки устанавливает (#i+1)-ый бит из наиболее значимого бита кодовых битов из 8 битов в качестве бита b#i и (#i+1)-го бита из наиболее значимого бита символьных битов из 8 битов из двух символов в качестве бита y#i и выполняет перестановку битов b0, b1, b2, b3, b4, b5, b6 и b7 с битами y7, y5 y4, y0, y3, y1, y2 и y6, соответственно.

Согласно третьему варианту осуществления настоящей технологии выполнены устройство обработки данных или способ обработки данных, включающее в себя, соответственно, блок обратной перестановки или этап обратной перестановки, для выполнения перестановки символьных битов символа, соответствующего любой одной из 16 сигнальных точек, определенных с помощью 16QAM, с кодовыми битами LDPC-кода, в котором длина кода составляет 16200 битов, и скорость кодирования составляет 1/3, и блок декодирования или этап декодирования, для декодирования LDPC-кода, переставленного с помощью блока обратной перестановки или этапа обратной перестановки, на основе матрицы контроля четности LDPC-кода. Когда кодовые биты из 8 битов, сохраненные в восьми запоминающих устройствах, имеющих объем памяти 16200/8 битов, и побитно считанные из соответствующих запоминающих устройств, назначены двум последовательным символам, блок обратной перестановки или этап обратной перестановки устанавливает (#i+1)-ый бит из наиболее значимого бита кодовых битов из 8 битов в качестве бита b#i и (#i+1)-го бита из наиболее значимого бита символьных битов из 8 битов из двух символов в качестве бита y#i и выполняет перестановку битов y6, y0, y3, y4, y5, y2, y1 и y7 с битами b0, b1, b2, b3, b4, b5, b6 и b7, соответственно. LDPC-код включает в себя информационные биты и биты четности. Матрица контроля четности включает в себя область информационной матрицы, соответствующую информационным битам, и область матрицы четности, соответствующую битам четности. Область информационной матрицы представлена с помощью таблицы исходных значений матрицы контроля четности. Таблица исходных значений матрицы контроля четности представляет собой таблицу, которая представляет позиции элементов 1 области информационной матрицы для каждых 360 столбцов, и сконфигурирована следующим образом:

416 8909 4156 3216 3112 2560 2912 6405 8593 4969 6723 6912

8978 3011 4339 9312 6396 2957 7288 5485 6031 10218 2226 3575

3383 10059 1114 10008 10147 9384 4290 434 5139 3536 1965 2291

2797 3693 7615 7077 743 1941 8716 6215 3840 5140 4582 5420

6110 8551 1515 7404 4879 4946 5383 1831 3441 9569 10472 4306

1505 5682 7778

7172 6830 6623

7281 3941 3505

10270 8669 914

3622 7563 9388

9930 5058 4554

4844 9609 2707

6883 3237 1714

4768 3878 10017

10127 3334 8267.

Согласно четвертому варианту осуществления настоящей технологии выполнены устройство обработки данных или способ обработки данных, включающее в себя, соответственно, блок обратной перестановки или этап обратной перестановки, для выполнения перестановки символьных битов символа, соответствующего любой одной из 16 сигнальных точек, определенных с помощью 16QAM, с кодовыми битами LDPC-кода, в котором длина кода составляет 16200 битов, и скорость кодирования составляет 2/5, и блок декодирования или этап декодирования, для декодирования LDPC-кода, переставленного с помощью блока обратной перестановки или этапа обратной перестановки, на основе матрицы контроля четности LDPC-кода. Когда кодовые биты из 8 битов, сохраненные в восьми запоминающих устройствах, имеющих объем памяти, равный 16200/8 битам, и побитно считанные из соответствующих запоминающих устройств, назначены двум последовательным символам, блок обратной перестановки или этап обратной перестановки устанавливает (#i+1)-ый бит из наиболее значимого бита кодовых битов из 8 битов в качестве бита b#i и (#i+1)-го бита из наиболее значимого бита символьных битов из 8 битов из двух символов в качестве бита y#i и выполняет перестановку битов y7, y5, y4, y0, y3, y1, y2 и y6 с битами b0, b1, b2, b3, b4, b5, b6 и b7, соответственно. LDPC-код включает в себя информационные биты и биты четности. Матрица контроля четности включает в себя область информационной матрицы, соответствующую информационным битам, и область матрицы четности, соответствующую битам четности. Область информационной матрицы представлена с помощью таблицы исходных значений матрицы контроля четности. Таблица исходных значений матрицы контроля четности представляет собой таблицу, которая представляет позиции элементов 1 области информационной матрицы для каждых 360 столбцов, и сконфигурирована следующим образом:

5650 4143 8750 583 6720 8071 635 1767 1344 6922 738 6658

5696 1685 3207 415 7019 5023 5608 2605 857 6915 1770 8016

3992 771 2190 7258 8970 7792 1802 1866 6137 8841 886 1931

4108 3781 7577 6810 9322 8226 5396 5867 4428 8827 7766 2254

4247 888 4367 8821 9660 324 5864 4774 227 7889 6405 8963

9693 500 2520 2227 1811 9330 1928 5140 4030 4824 806 3134

1652 8171 1435

3366 6543 3745

9286 8509 4645

7397 5790 8972

6597 4422 1799

9276 4041 3847

8683 7378 4946

5348 1993 9186

6724 9015 5646

4502 4439 8474

5107 7342 9442

1387 8910 2660.

Согласно первому варианту осуществления настоящей технологии LDPC-кодирование, при котором длина кода составляет 16200 битов, и скорость кодирования составляет 1/3, выполняется на основе матрицы контроля четности LDPC-кода, и кодовые биты кодированного LDPC-кода перестанавливаются с символьными битами символа, соответствующего любой одной из 16 сигнальных точек, определенных с помощью 16QAM. Кодированный LDPC-код включает в себя информационные биты и биты четности. Матрица контроля четности включает в себя область информационной матрицы, соответствующую информационным битам, и область матрицы четности, соответствующую битам четности. Область информационной матрицы представлена с помощью таблицы исходных значений матрицы контроля четности. Таблица исходных значений матрицы контроля четности представляет собой таблицу, которая представляет позиции элементов 1 области информационной матрицы для каждых 360 столбцов, и сконфигурирована следующим образом:

416 8909 4156 3216 3112 2560 2912 6405 8593 4969 6723 6912

8978 3011 4339 9312 6396 2957 7288 5485 6031 10218 2226 3575

3383 10059 1114 10008 10147 9384 4290 434 5139 3536 1965 2291

2797 3693 7615 7077 743 1941 8716 6215 3840 5140 4582 5420

6110 8551 1515 7404 4879 4946 5383 1831 3441 9569 10472 4306

1505 5682 7778

7172 6830 6623

7281 3941 3505

10270 8669 914

3622 7563 9388

9930 5058 4554

4844 9609 2707

6883 3237 1714

4768 3878 10017

10127 3334 8267.

Когда кодовые биты из 8 битов, сохраненные в восьми запоминающих устройствах, имеющих объем памяти 16200/8 битов, и побитно считанные из соответствующих запоминающих устройств, назначены двум последовательным символам, блок перестановки или этап перестановки устанавливает (#i+1)-ый бит из наиболее значимого бита кодовых битов из 8 битов в качестве бита b#i и (#i+1)-го бита из наиболее значимого бита символьных битов из 8 битов из двух символов в качестве бита y#i и выполняет перестановку битов b0, b1, b2, b3, b4, b5, b6 и b7 с битами y6, y0, y3, y4, y5, y2, y1 и y7, соответственно.

Согласно второму варианту осуществления настоящей технологии LDPC-кодирование, при котором длина кода составляет 16200 битов, и скорость кодирования составляет 2/5, выполняется на основе матрицы контроля четности LDPC-кода, и кодовые биты кодированного LDPC-кода перестанавливаются с символьными битами символа, соответствующего любой одной из 16 сигнальных точек, определенных с помощью 16QAM. Кодированный LDPC-код включает в себя информационные биты и биты четности. Матрица контроля четности включает в себя область информационной матрицы, соответствующую информационным битам, и область матрицы четности, соответствующую битам четности. Область информационной матрицы представлена с помощью таблицы исходных значений матрицы контроля четности. Таблица исходных значений матрицы контроля четности представляет собой таблицу, которая представляет позиции элементов 1 области информационной матрицы для каждых 360 столбцов, и сконфигурирована следующим образом:

5650 4143 8750 583 6720 8071 635 1767 1344 6922 738 6658

5696 1685 3207 415 7019 5023 5608 2605 857 6915 1770 8016

3992 771 2190 7258 8970 7792 1802 1866 6137 8841 886 1931

4108 3781 7577 6810 9322 8226 5396 5867 4428 8827 7766 2254

4247 888 4367 8821 9660 324 5864 4774 227 7889 6405 8963

9693 500 2520 2227 1811 9330 1928 5140 4030 4824 806 3134

1652 8171 1435

3366 6543 3745

9286 8509 4645

7397 5790 8972

6597 4422 1799

9276 4041 3847

8683 7378 4946

5348 1993 9186

6724 9015 5646

4502 4439 8474

5107 7342 9442

1387 8910 2660.

Когда кодовые биты из 8 битов, сохраненные в восьми запоминающих устройствах, имеющих объем памяти 16200/8 битов, и побитно считанные из соответствующих запоминающих устройств, назначены двум последовательным символам, блок перестановки или этап перестановки устанавливает (#i+1)-ый бит из наиболее значимого бита кодовых битов из 8 битов в качестве бита b#i и (#i+1)-го бита из наиболее значимого бита символьных битов из 8 битов из двух символов в качестве бита y#i и выполняет перестановку битов b0, b1, b2, b3, b4, b5, b6 и b7 с битами y7, y5 y4, y0, y3, y1, y2 и y6, соответственно.

Согласно третьему варианту осуществления настоящей технологии символьные биты символа, соответствующего любой одной из 16 сигнальных точек, определенных с помощью 16QAM, перестанавливаются с кодовыми битами LDPC-кода, в котором длина кода составляет 16200 битов, и скорость кодирования составляет 1/3, и LDPC-код с выполненной перестановкой декодируется на основе матрицы контроля четности LDPC-кода. Когда кодовые биты из 8 битов, сохраненные в восьми запоминающих устройствах, имеющих объем памяти 16200/8 битов, и побитно считанные из соответствующих запоминающих устройств, назначены двум последовательным символам, блок или этап обратной перестановки устанавливает (#i+1)-ый бит из наиболее значимого бита кодовых битов из 8 битов в качестве бита b#i и (#i+1)-го бита из наиболее значимого бита символьных битов из 8 битов из двух символов в качестве бита y#i и выполняет перестановку битов y6, y0, y3, y4, y5, y2, y1 и y7 с битами b0, b1, b2, b3, b4, b5, b6 и b7, соответственно. LDPC-код включает в себя информационные биты и биты четности. Матрица контроля четности включает в себя область информационной матрицы, соответствующую информационным битам, и область матрицы четности, соответствующую битам четности. Область информационной матрицы представлена с помощью таблицы исходных значений матрицы контроля четности. Таблица исходных значений матрицы контроля четности представляет собой таблицу, которая представляет позиции элементов 1 области информационной матрицы для каждых 360 столбцов, и сконфигурирована следующим образом:

416 8909 4156 3216 3112 2560 2912 6405 8593 4969 6723 6912

8978 3011 4339 9312 6396 2957 7288 5485 6031 10218 2226 3575

3383 10059 1114 10008 10147 9384 4290 434 5139 3536 1965 2291

2797 3693 7615 7077 743 1941 8716 6215 3840 5140 4582 5420

6110 8551 1515 7404 4879 4946 5383 1831 3441 9569 10472 4306

1505 5682 7778

7172 6830 6623

7281 3941 3505

10270 8669 914

3622 7563 9388

9930 5058 4554

4844 9609 2707

6883 3237 1714

4768 3878 10017

10127 3334 8267.

Согласно четвертому варианту осуществления настоящей технологии символьные биты символа, соответствующего любой одной из 16 сигнальных точек, определенных с помощью 16QAM, перестанавливаются с кодовыми битами LDPC-кода, в котором длина кода составляет 16200 битов, и скорость кодирования составляет 2/5, и LDPC-код с выполненной перестановкой декодируется на основе матрицы контроля четности LDPC-кода. Когда кодовые биты из 8 битов, сохраненные в восьми запоминающих устройствах, имеющих объем памяти 16200/8 битов, и побитно считанные из соответствующих запоминающих устройств, назначены двум последовательным символам, блок или этап обратной перестановки устанавливает (#i+1)-ый бит из наиболее значимого бита кодовых битов из 8 битов в качестве бита b#i и (#i+1)-го бита из наиболее значимого бита символьных битов из 8 битов из двух символов в качестве бита y#i и выполняет перестановку битов y7, y5, y4, y0, y3, y1, y2 и y6 с битами b0, b1, b2, b3, b4, b5, b6 и b7, соответственно. LDPC-код включает в себя информационные биты и биты четности. Матрица контроля четности включает в себя область информационной матрицы, соответствующую информационным битам, и область матрицы четности, соответствующую битам четности. Область информационной матрицы представлена с помощью таблицы исходных значений матрицы контроля четности. Таблица исходных значений матрицы контроля четности представляет собой таблицу, которая представляет позиции элементов 1 области информационной матрицы для каждых 360 столбцов, и сконфигурирована следующим образом:

5650 4143 8750 583 6720 8071 635 1767 1344 6922 738 6658

5696 1685 3207 415 7019 5023 5608 2605 857 6915 1770 8016

3992 771 2190 7258 8970 7792 1802 1866 6137 8841 886 1931

4108 3781 7577 6810 9322 8226 5396 5867 4428 8827 7766 2254

4247 888 4367 8821 9660 324 5864 4774 227 7889 6405 8963

9693 500 2520 2227 1811 9330 1928 5140 4030 4824 806 3134

1652 8171 1435

3366 6543 3745

9286 8509 4645

7397 5790 8972

6597 4422 1799

9276 4041 3847

8683 7378 4946

5348 1993 9186

6724 9015 5646

4502 4439 8474

5107 7342 9442

1387 8910 2660.

Устройство обработки данных может представлять собой независимое устройство и может представлять собой внутренний блок, образующий одно устройство.

Полезные эффекты изобретения

Согласно настоящему изобретению можно повысить устойчивость к ошибке.

Краткое описание чертежей

Фиг.1 - иллюстрация матрицы Н контроля четности LDPC-кода.

Фиг.2 - схема последовательности операций, иллюстрирующая последовательность декодирования LDPC-кода.

Фиг.3 - иллюстрация примера матрицы контроля четности LDPC-кода.

Фиг.4 - иллюстрация графа Таннера (Tanner) матрицы контроля четности.

Фиг.5 - иллюстрация переменного узла.

Фиг.6 - иллюстрация проверочного узла.

Фиг.7 - иллюстрация примера конфигурации варианта осуществления передающей системы, к которой применимо настоящее изобретение.

Фиг.8 - блок-схема, иллюстрирующая пример конфигурации передающего устройства 11.

Фиг.9 - блок-схема, иллюстрирующая пример конфигурации битового перемежителя 116.

Фиг.10 - иллюстрация матрицы контроля четности.

Фиг.11 - иллюстрация матрицы четности.

Фиг.12 - иллюстрация матрицы контроля четности LDPC-кода, заданного в стандарте DVB-S.2.

Фиг.13 - иллюстрация матрицы контроля четности LDPC-кода, заданного в стандарте DVB-S.2.

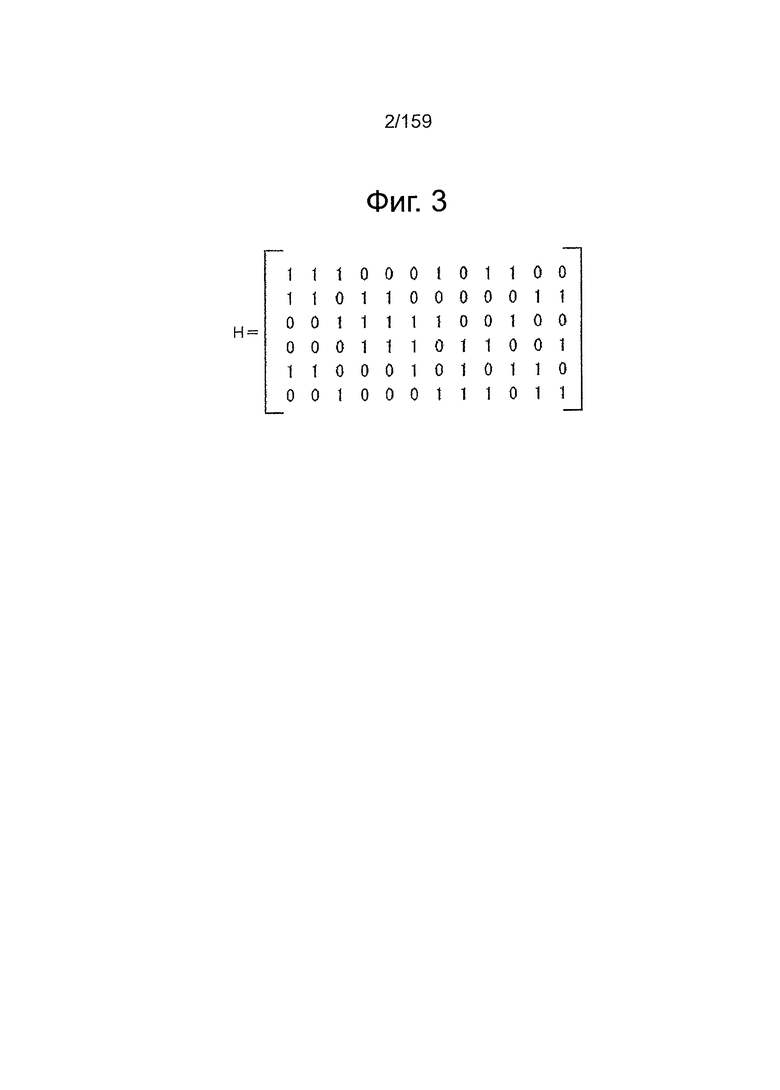

Фиг.14 - иллюстрация размещения сигнальных точек для формата модуляции 16QAM.

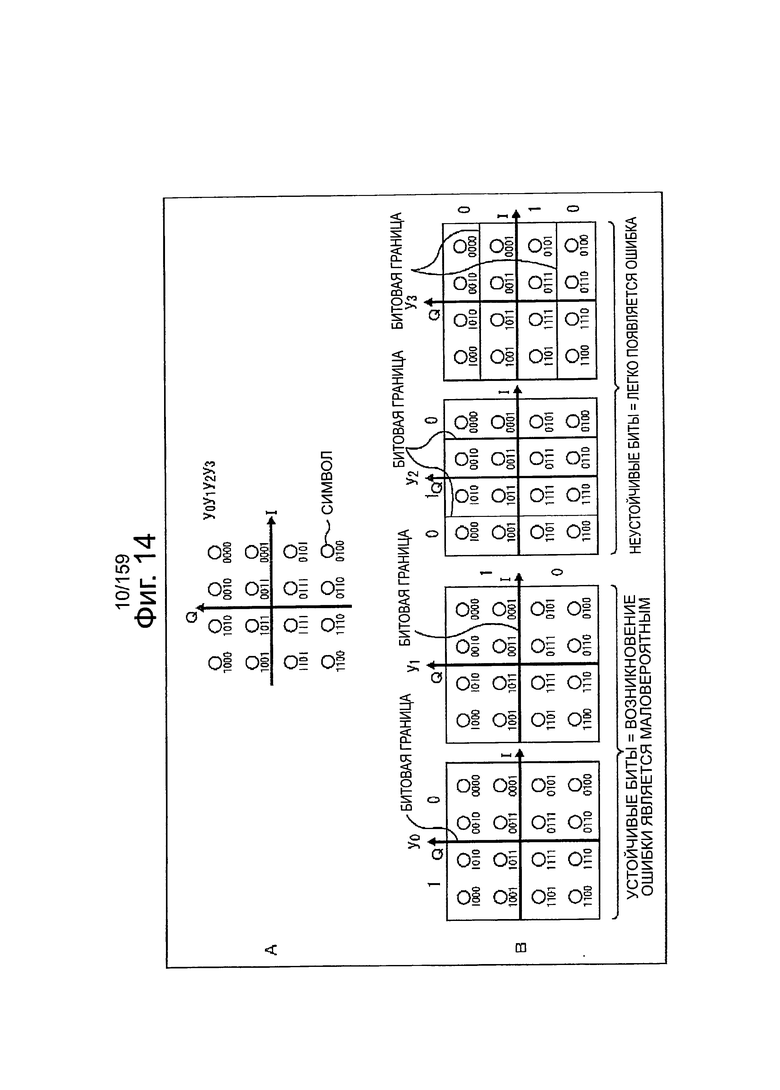

Фиг.15 - иллюстрация размещения сигнальных точек для формата модуляции 64QAM.

Фиг.16 - иллюстрация размещения сигнальных точек для формата модуляции 64QAM.

Фиг.17 - иллюстрация размещения сигнальных точек для формата модуляции 64QAM.

Фиг.18 - иллюстрация процесса, выполняемого демультиплексором 25.

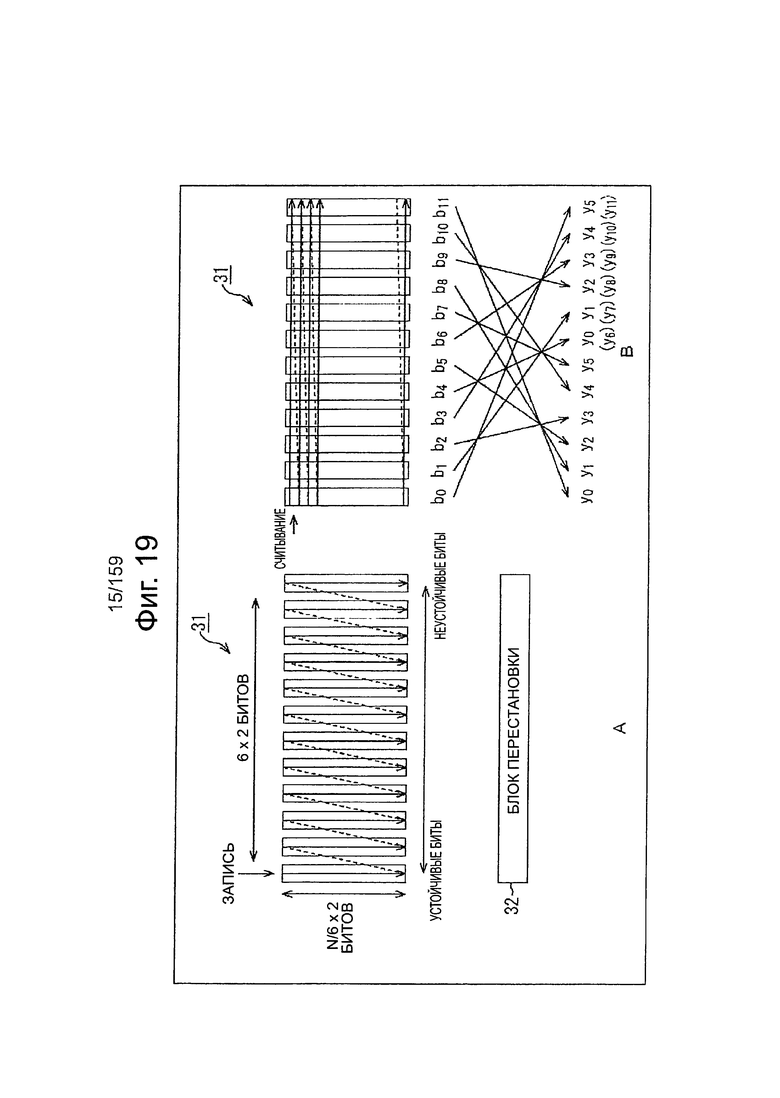

Фиг.19 - иллюстрация процесса, выполняемого демультиплексором 25.

Фиг.20 - иллюстрация графа Таннера для декодирования LDPC-кода.

Фиг.21 - иллюстрация матрицы четности HT, которая принимает вид ступенчатой структуры, и графа Таннера, соответствующего матрице HT четности.

Фиг.22 - иллюстрация матрицы HT четности матрицы H контроля четности, соответствующей LDPC-коду после перемежения четности.

Фиг.23 - иллюстрация преобразованной матрицы контроля четности.

Фиг.24 - иллюстрация процесса, выполняемого перемежителем 24 с закручиванием столбцов.

Фиг.25 - иллюстрация количества столбцов памяти 31, необходимого для перемежения с закручиванием столбцов, и адреса начальной позиции записи.

Фиг.26 - иллюстрация количества столбцов памяти 31, необходимого для перемежения с закручиванием столбцов, и адреса начальной позиции записи.

Фиг.27 - схема последовательности операций, иллюстрирующая процесс, выполняемый битовым перемежителем 116 и QAM-кодером 117.

Фиг.28 - иллюстрация модели канала связи, принятой за основу моделирования.

Фиг.29 - иллюстрация зависимости частоты появления ошибок, которая принята за основу моделирования и допплеровской частоты fd дрожания.

Фиг.30 - иллюстрация зависимости частоты появления ошибок, которая принята за основу моделирования и допплеровской частоты fd дрожания.

Фиг.31 - блок-схема, иллюстрирующая пример конфигурации LDPC-кодера 115.

Фиг.32 - схема последовательности операций, иллюстрирующая процесс, выполняемый LDPC-кодером 115.

Фиг.33 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 1/4, и длина кода составляет 16200.

Фиг.34 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 1/3, и длина кода составляет 16200.

Фиг.35 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 2/5, и длина кода составляет 16200.

Фиг.36 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 1/2, и длина кода составляет 16200.

Фиг.37 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 3/5, и длина кода составляет 16200.

Фиг.38 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 2/3, и длина кода составляет 16200.

Фиг.39 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 3/4, и длина кода составляет 16200.

Фиг.40 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 4/5, и длина кода составляет 16200.

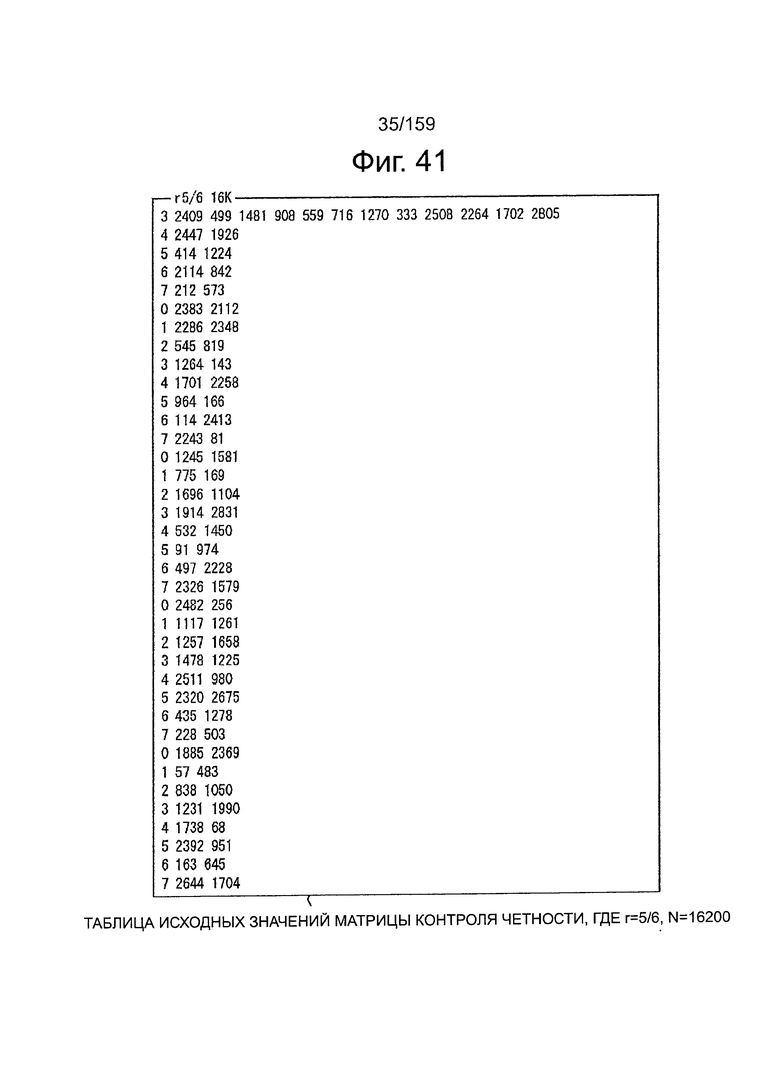

Фиг.41 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 5/6, и длина кода составляет 16200.

Фиг.42 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 8/9, и длина кода составляет 16200.

Фиг.43 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 1/4, и длина кода составляет 64800.

Фиг.44 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 1/4, и длина кода составляет 64800.

Фиг.45 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 1/3, и длина кода составляет 64800.

Фиг.46 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 1/3, и длина кода составляет 64800.

Фиг.47 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 2/5, и длина кода составляет 64800.

Фиг.48 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 2/5, и длина кода составляет 64800.

Фиг.49 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 1/2, и длина кода составляет 64800.

Фиг.50 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 1/2, и длина кода составляет 64800.

Фиг.51 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 1/2, и длина кода составляет 64800.

Фиг.52 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 3/5, и длина кода составляет 64800.

Фиг.53 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 3/5, и длина кода составляет 64800.

Фиг.54 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 3/5, и длина кода составляет 64800.

Фиг.55 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 2/3, и длина кода составляет 64800.

Фиг.56 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 2/3, и длина кода составляет 64800.

Фиг.57 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 2/3, и длина кода составляет 64800.

Фиг.58 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 3/4, и длина кода составляет 64800.

Фиг.59 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 3/4, и длина кода составляет 64800.

Фиг.60 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 3/4, и длина кода составляет 64800.

Фиг.61 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 3/4, и длина кода составляет 64800.

Фиг.62 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 4/5, и длина кода составляет 64800.

Фиг.63 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 4/5, и длина кода составляет 64800.

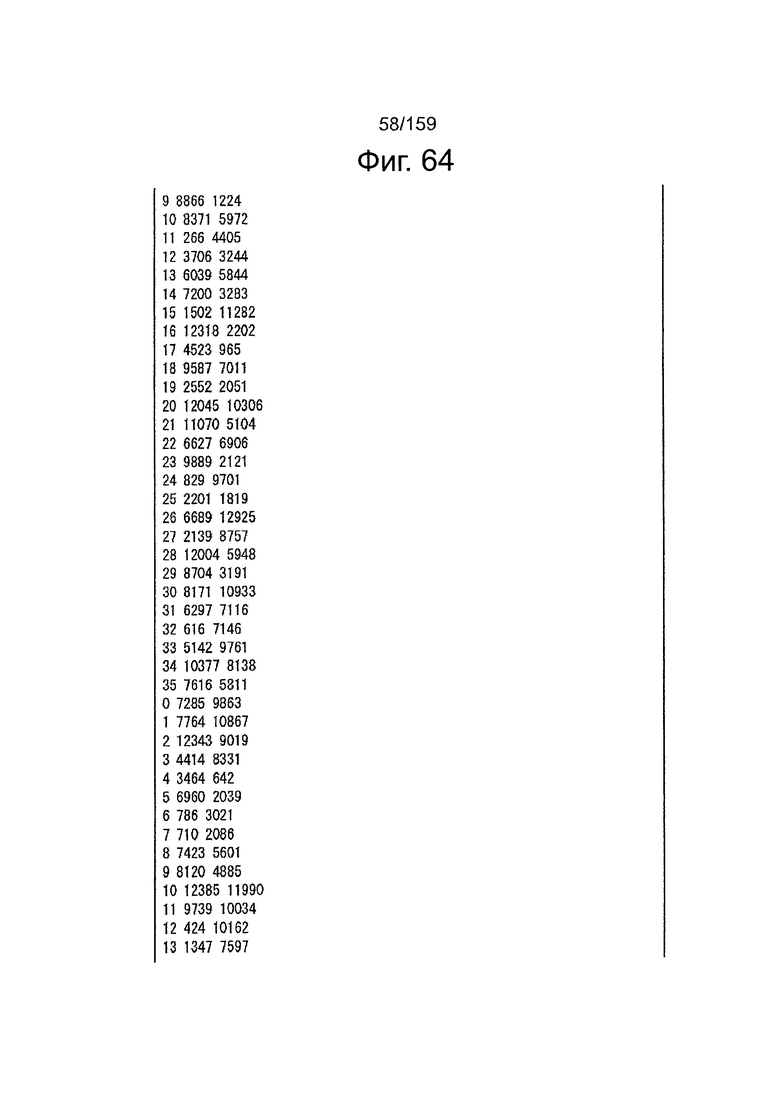

Фиг.64 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 4/5, и длина кода составляет 64800.

Фиг.65 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 4/54, и длина кода составляет 64800.

Фиг.66 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 5/6, и длина кода составляет 64800.

Фиг.67 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 5/6, и длина кода составляет 64800.

Фиг.68 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 5/6, и длина кода составляет 64800.

Фиг.69 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 5/6, и длина кода составляет 64800.

Фиг.70 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 8/9, и длина кода составляет 64800.

Фиг.71 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 8/9, и длина кода составляет 64800.

Фиг.72 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 8/9, и длина кода составляет 64800.

Фиг.73 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 8/9, и длина кода составляет 64800.

Фиг.74 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 9/10, и длина кода составляет 64800.

Фиг.75 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 9/10, и длина кода составляет 64800.

Фиг.76 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 9/10, и длина кода составляет 64800.

Фиг.77 - иллюстрация примера таблицы исходных значений матрицы контроля четности, в котором скорость кодирования составляет 9/10, и длина кода составляет 64800.

Фиг.78 - иллюстрация способа вычисления матрицы Н контроля четности из таблицы исходных значений матрицы контроля четности.

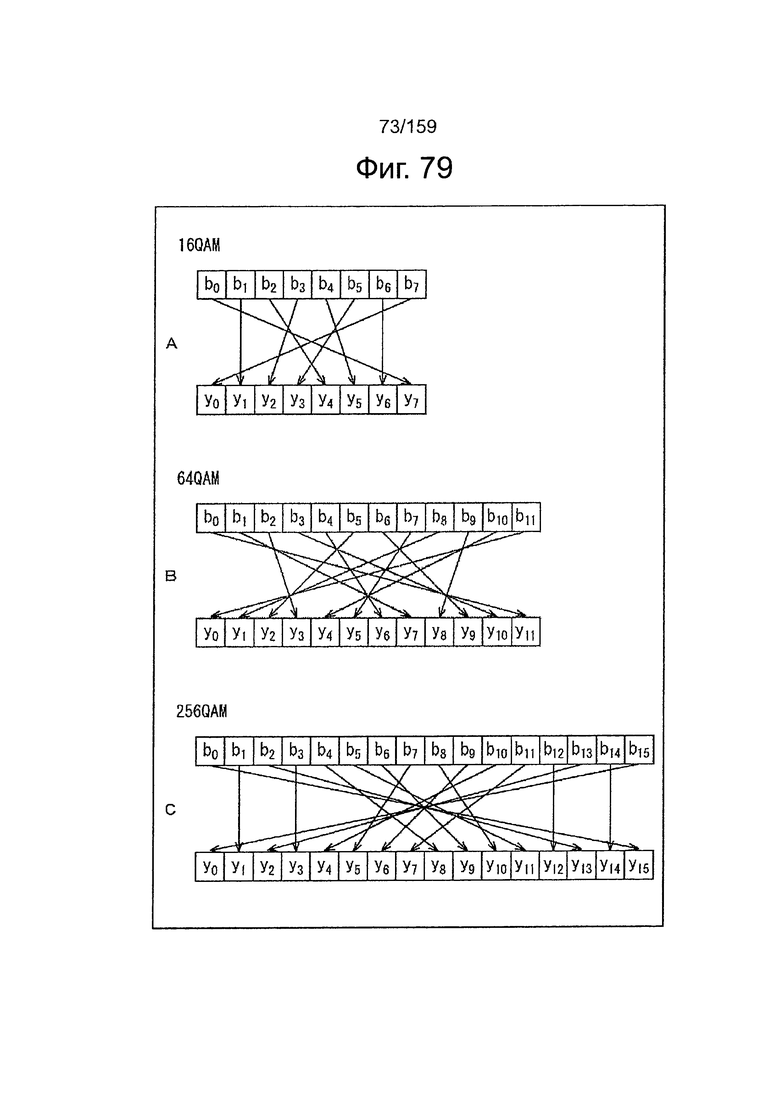

Фиг.79 - иллюстрация процесса перестановки согласно настоящему способу.

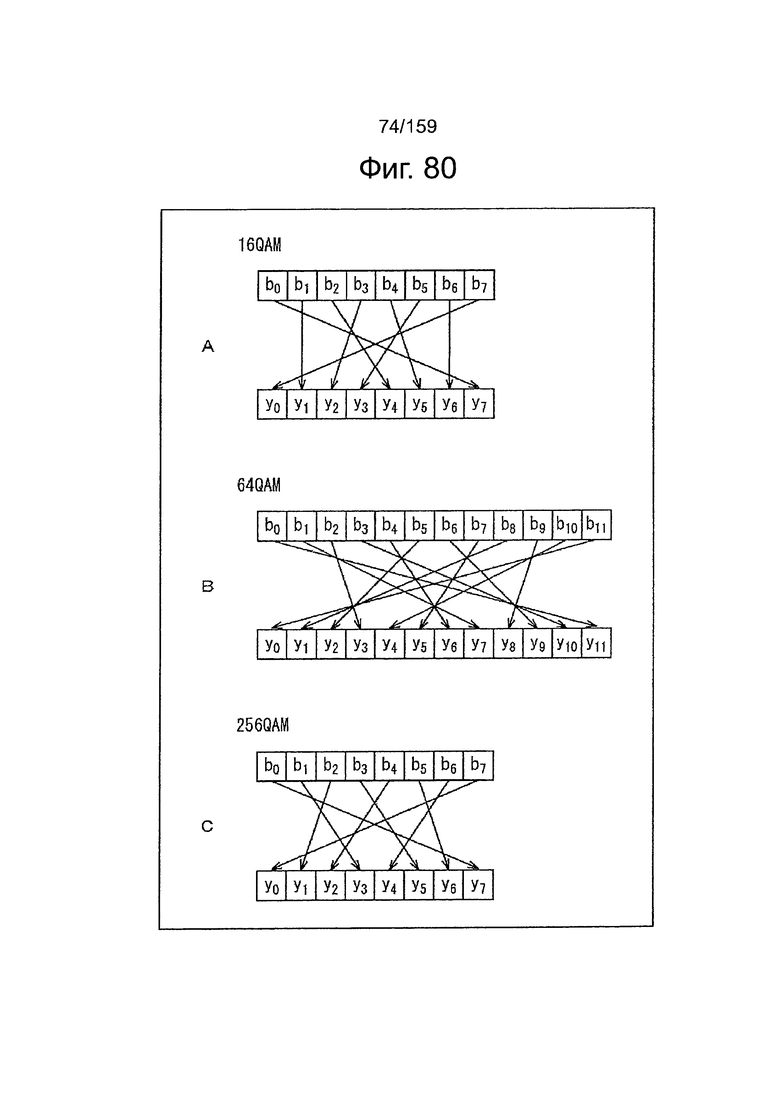

Фиг.80 - иллюстрация процесса перестановки согласно настоящему способу.

Фиг.81 - иллюстрация группы кодовых битов и группы символьных битов, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 1/4, модулируется с помощью 64QAM, и множитель b равен 2.

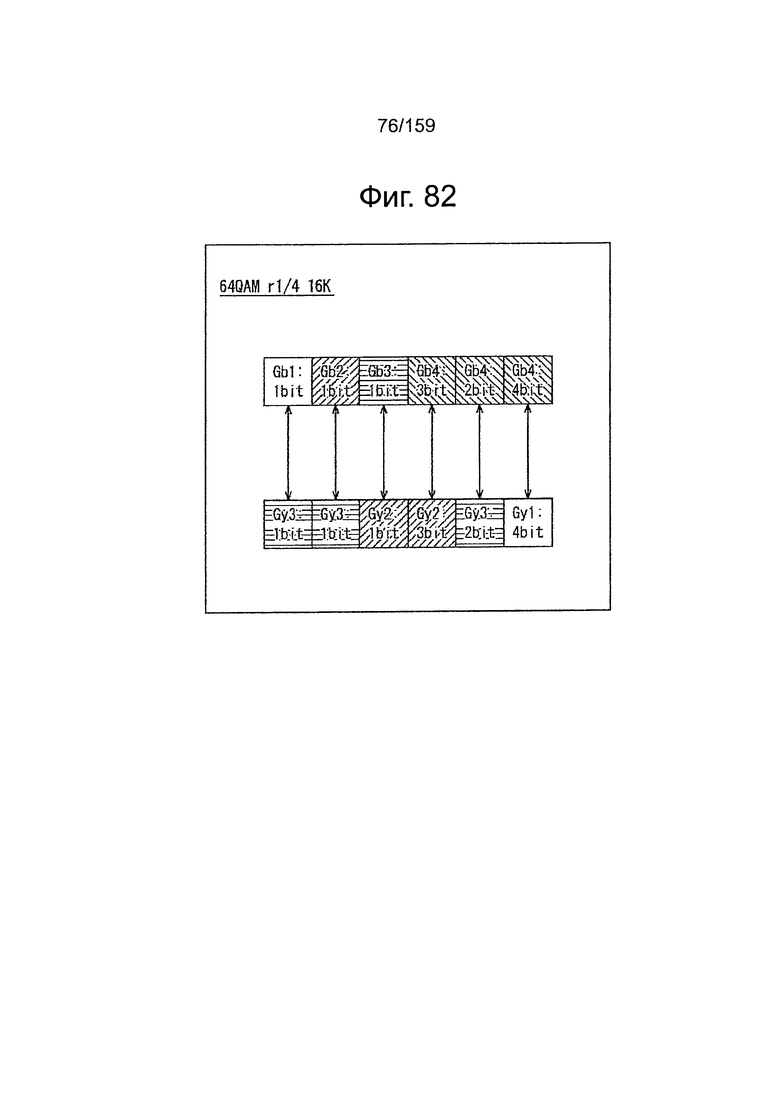

Фиг.82 - иллюстрация правила назначения, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 1/4, модулируется с помощью 64QAM, и множитель b равен 2.

Фиг.83 - иллюстрация перестановки кодовых битов согласно правилу назначения, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 1/4, модулируется с помощью 64QAM, и множитель b равен 2.

Фиг.84 - иллюстрация группы кодовых битов и группы символьных битов, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 1/3, модулируется с помощью 64QAM, и множитель b равен 2.

Фиг.85 - иллюстрация правила назначения, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 1/3, модулируется с помощью 64QAM, и множитель b равен 2.

Фиг.86 - иллюстрация перестановки кодовых битов согласно правилу назначения, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 1/3, модулируется с помощью 64QAM, и множитель b равен 2.

Фиг.87 - иллюстрация перестановки кодовых битов, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 2/5, модулируется с помощью 64QAM, и множитель b равен 2.

Фиг.88 - иллюстрация группы кодовых битов и группы символьных битов, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 1/2, модулируется с помощью 64QAM, и множитель b равен 2.

Фиг.89 - иллюстрация правила назначения, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 1/2, модулируется с помощью 64QAM, и множитель b равен 2.

Фиг.90 - иллюстрация перестановки кодовых битов согласно правилу назначения, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 1/2, модулируется с помощью 64QAM, и множитель b равен 2.

Фиг.91 - иллюстрация перестановки кодовых битов, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 3/5, модулируется с помощью 64QAM, и множитель b равен 2.

Фиг.92 - иллюстрация группы кодовых битов и группы символьных битов, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 3/5, модулируется с помощью 64QAM, и множитель b равен 2.

Фиг.93 - иллюстрация правила назначения, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 2/3, модулируется с помощью 64QAM, и множитель b равен 2.

Фиг.94 - иллюстрация перестановки кодовых битов согласно правилу назначения, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 2/3, модулируется с помощью 64QAM, и множитель b равен 2.

Фиг.95 - иллюстрация группы кодовых битов и группы символьных битов, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 3/4, модулируется с помощью 64QAM, и множитель b равен 2.

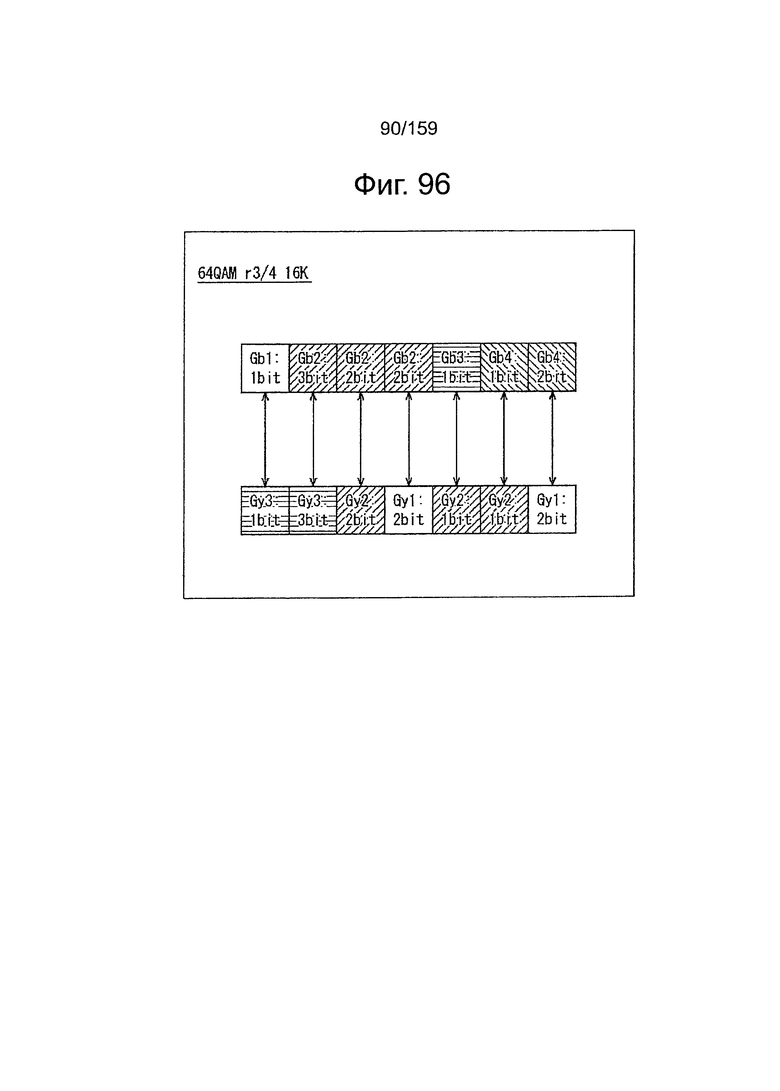

Фиг.96 - иллюстрация правила назначения, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 3/4, модулируется с помощью 64QAM, и множитель b равен 2.

Фиг.97 - иллюстрация перестановки кодовых битов согласно правилу назначения, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 3/4, модулируется с помощью 64QAM, и множитель b равен 2.

Фиг.98 - иллюстрация группы кодовых битов и группы символьных битов, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 4/5, модулируется с помощью 64QAM, и множитель b равен 2.

Фиг.99 - иллюстрация правила назначения, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 4/5, модулируется с помощью 64QAM, и множитель b равен 2.

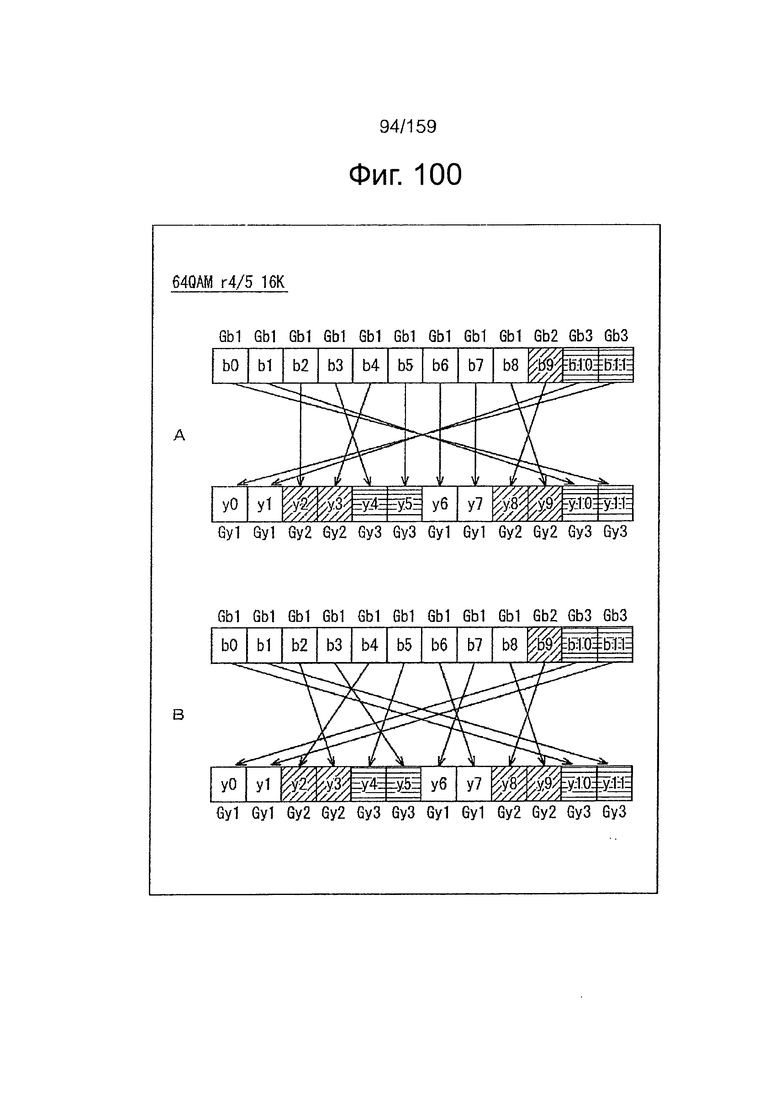

Фиг.100 - иллюстрация перестановки кодовых битов согласно правилу назначения, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 4/5, модулируется с помощью 64QAM, и множитель b равен 2.

Фиг.101 - иллюстрация группы кодовых битов и группы символьных битов, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 5/6, модулируется с помощью 64QAM, и множитель b равен 2.

Фиг.102 - иллюстрация правила назначения, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 5/6, модулируется с помощью 64QAM, и множитель b равен 2.

Фиг.103 - иллюстрация перестановки кодовых битов согласно правилу назначения, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 5/6, модулируется с помощью 64QAM, и множитель b равен 2.

Фиг.104 - иллюстрация группы кодовых битов и группы символьных битов, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 8/9, модулируется с помощью 64QAM, и множитель b равен 2.

Фиг.105 - иллюстрация правила назначения, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 8/9, модулируется с помощью 64QAM, и множитель b равен 2.

Фиг.106 - иллюстрация перестановки кодовых битов согласно правилу назначения, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 8/9, модулируется с помощью 64QAM, и множитель b равен 2.

Фиг.107 - иллюстрация группы кодовых битов и группы символьных битов, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 1/4, модулируется с помощью 16QAM, и множитель b равен 2.

Фиг.108 - иллюстрация правила назначения, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 1/4, модулируется с помощью 16QAM, и множитель b равен 2.

Фиг.109 - иллюстрация перестановки кодовых битов согласно правилу назначения, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 1/4, модулируется с помощью 16QAM, и множитель b равен 2.

Фиг.110 - иллюстрация группы кодовых битов и группы символьных битов, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 1/3, модулируется с помощью 16QAM, и множитель b равен 2.

Фиг.111 - иллюстрация правила назначения, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 1/3, модулируется с помощью 16QAM, и множитель b равен 2.

Фиг.112 - иллюстрация перестановки кодовых битов согласно правилу назначения, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 1/3, модулируется с помощью 16QAM, и множитель b равен 2.

Фиг.113 - иллюстрация группы кодовых битов и группы символьных битов, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 2/5, модулируется с помощью 16QAM, и множитель b равен 2.

Фиг.114 - иллюстрация правила назначения, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 2/5, модулируется с помощью 16QAM, и множитель b равен 2.

Фиг.115 - иллюстрация перестановки кодовых битов согласно правилу назначения, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 2/5, модулируется с помощью 16QAM, и множитель b равен 2.

Фиг.116 - иллюстрация группы кодовых битов и группы символьных битов, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 1/2, модулируется с помощью 16QAM, и множитель b равен 2.

Фиг.117 - иллюстрация правила назначения, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 1/2, модулируется с помощью 16QAM, и множитель b равен 2.

Фиг.118 - иллюстрация перестановки кодовых битов согласно правилу назначения, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 1/2, модулируется с помощью 16QAM, и множитель b равен 2.

Фиг.119 - иллюстрация перестановки кодовых битов, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 3/5, модулируется с помощью 16QAM, и множитель b равен 2.

Фиг.120 - иллюстрация группы кодовых битов и группы символьных битов, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 2/3, модулируется с помощью 16QAM, и множитель b равен 2.

Фиг.121 - иллюстрация правила назначения, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 2/3, модулируется с помощью 16QAM, и множитель b равен 2.

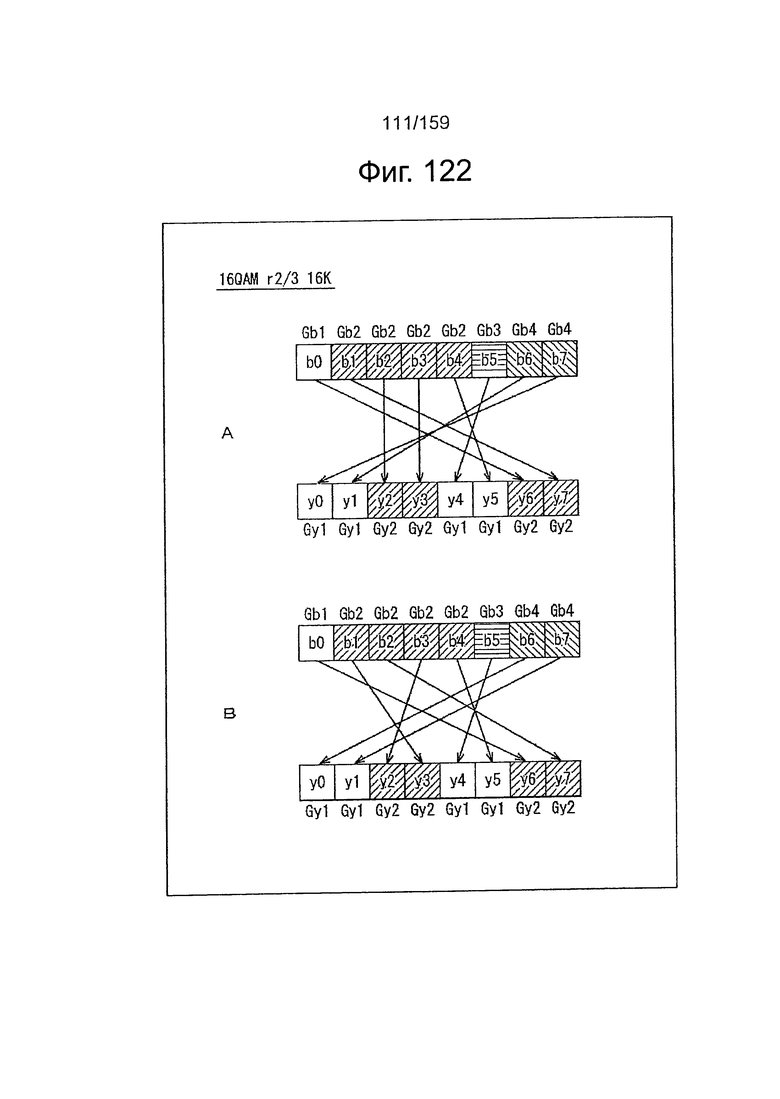

Фиг.122 - иллюстрация перестановки кодовых битов согласно правилу назначения, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 2/3, модулируется с помощью 16QAM, и множитель b равен 2.

Фиг.123 - иллюстрация группы кодовых битов и группы символьных битов, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 3/4, модулируется с помощью 16QAM, и множитель b равен 2.

Фиг.124 - иллюстрация правила назначения, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 3/4, модулируется с помощью 16QAM, и множитель b равен 2.

Фиг.125 - иллюстрация перестановки кодовых битов согласно правилу назначения, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 3/4, модулируется с помощью 16QAM, и множитель b равен 2.

Фиг.126 - иллюстрация группы кодовых битов и группы символьных битов, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 4/5, модулируется с помощью 16QAM, и множитель b равен 2.

Фиг.127 - иллюстрация правила назначения, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 4/5, модулируется с помощью 16QAM, и множитель b равен 2.

Фиг.128 - иллюстрация перестановки кодовых битов согласно правилу назначения, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 4/5, модулируется с помощью 16QAM, и множитель b равен 2.

Фиг.129 - иллюстрация группы кодовых битов и группы символьных битов, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 5/6, модулируется с помощью 16QAM, и множитель b равен 2.

Фиг.130 - иллюстрация правила назначения, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 5/6, модулируется с помощью 16QAM, и множитель b равен 2.

Фиг.131 - иллюстрация перестановки кодовых битов согласно правилу назначения, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 5/6, модулируется с помощью 16QAM, и множитель b равен 2.

Фиг.132 - иллюстрация группы кодовых битов и группы символьных битов, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 8/9, модулируется с помощью 16QAM, и множитель b равен 2.

Фиг.133 - иллюстрация правила назначения, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 8/9, модулируется с помощью 16QAM, и множитель b равен 2.

Фиг.134 - иллюстрация перестановки кодовых битов согласно правилу назначения, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 8/9, модулируется с помощью 16QAM, и множитель b равен 2.

Фиг.135 - иллюстрация результатов моделирования BER, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 1/4, модулируется с помощью 64QAM, и множитель b равен 2.

Фиг.136 - иллюстрация результатов моделирования BER, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 1/3, модулируется с помощью 64QAM, и множитель b равен 2.

Фиг.137 - иллюстрация результатов моделирования BER, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 1/2, модулируется с помощью 64QAM, и множитель b равен 2.

Фиг.138 - иллюстрация результатов моделирования BER, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 2/3, модулируется с помощью 64QAM, и множитель b равен 2.

Фиг.139 - иллюстрация результатов моделирования BER, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 3/4, модулируется с помощью 64QAM, и множитель b равен 2.

Фиг.140 - иллюстрация результатов моделирования BER, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 4/5, модулируется с помощью 64QAM, и множитель b равен 2.

Фиг.141 - иллюстрация результатов моделирования BER, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 5/6, модулируется с помощью 64QAM, и множитель b равен 2.

Фиг.142 - иллюстрация результатов моделирования BER, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 8/9, модулируется с помощью 64QAM, и множитель b равен 2.

Фиг.143 - иллюстрация результатов моделирования BER, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 1/4, модулируется с помощью 16QAM, и множитель b равен 2.

Фиг.144 - иллюстрация результатов моделирования BER, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 1/3, модулируется с помощью 16QAM, и множитель b равен 2.

Фиг.145 - иллюстрация результатов моделирования BER, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 2/5, модулируется с помощью 16QAM, и множитель b равен 2.

Фиг.146 - иллюстрация результатов моделирования BER, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 1/2, модулируется с помощью 16QAM, и множитель b равен 2.

Фиг.147 - иллюстрация результатов моделирования BER, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 2/3, модулируется с помощью 16QAM, и множитель b равен 2.

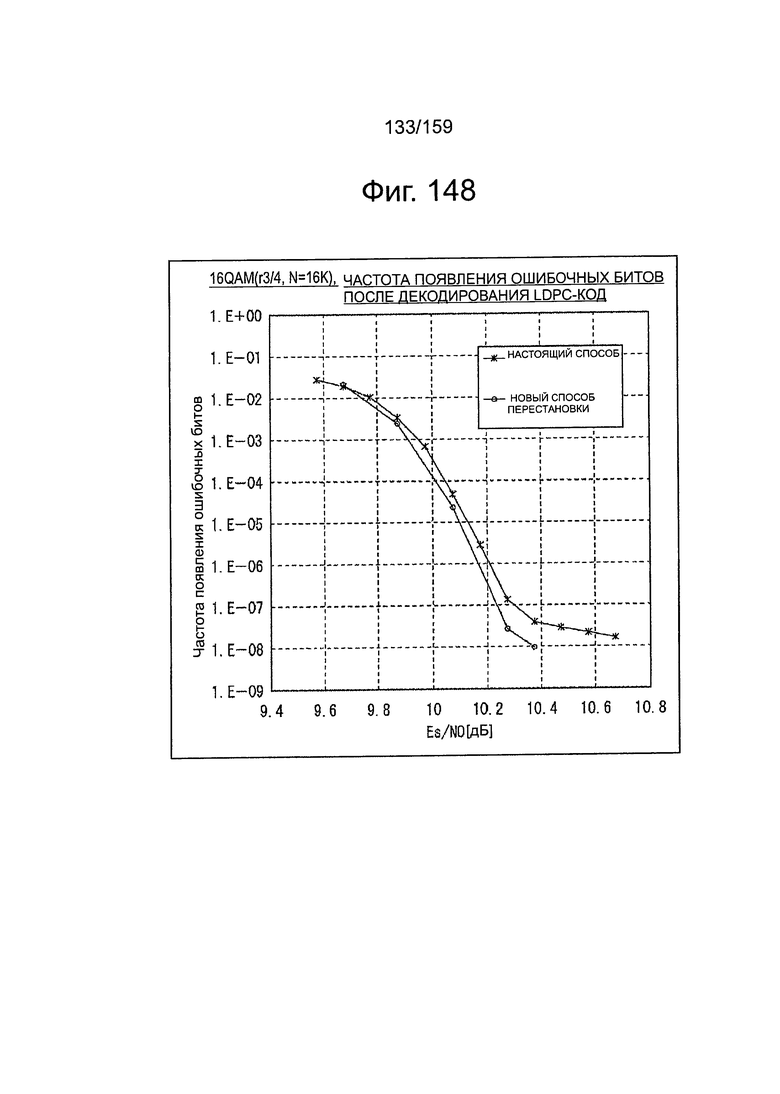

Фиг.148 - иллюстрация результатов моделирования BER, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 3/4, модулируется с помощью 16QAM, и множитель b равен 2.

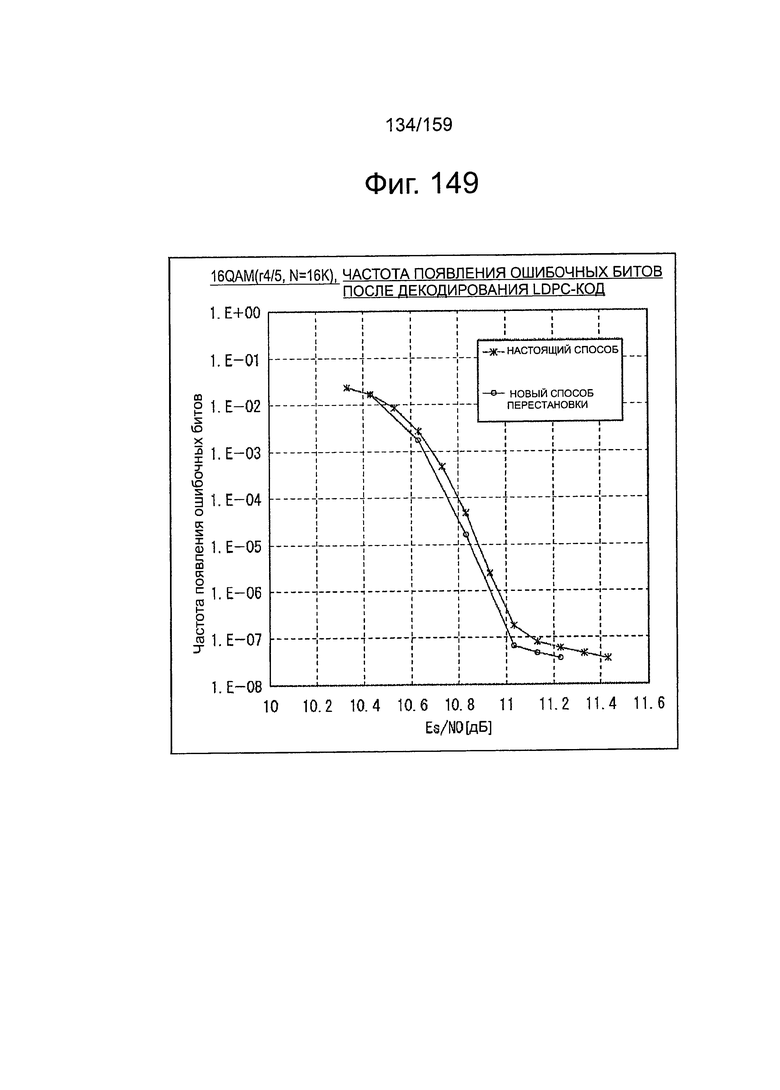

Фиг.149 - иллюстрация результатов моделирования BER, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 4/5, модулируется с помощью 16QAM, и множитель b равен 2.

Фиг.150 - иллюстрация результатов моделирования BER, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 5/6, модулируется с помощью 16QAM, и множитель b равен 2.

Фиг.151 - иллюстрация результатов моделирования BER, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 8/9, модулируется с помощью 16QAM, и множитель b равен 2.

Фиг.152 - блок-схема, иллюстрирующая пример конфигурации приемного устройства 12.

Фиг.153 - блок-схема, иллюстрирующая пример конфигурации битового деперемежителя 165

Фиг.154 - схема последовательности операций, иллюстрирующая процесс, выполняемый с помощью QAM-декодера 164, битового деперемежителя 165 и LDPC-декодера 166.

Фиг.155 - иллюстрация примера матрицы контроля четности LDPC-кода.

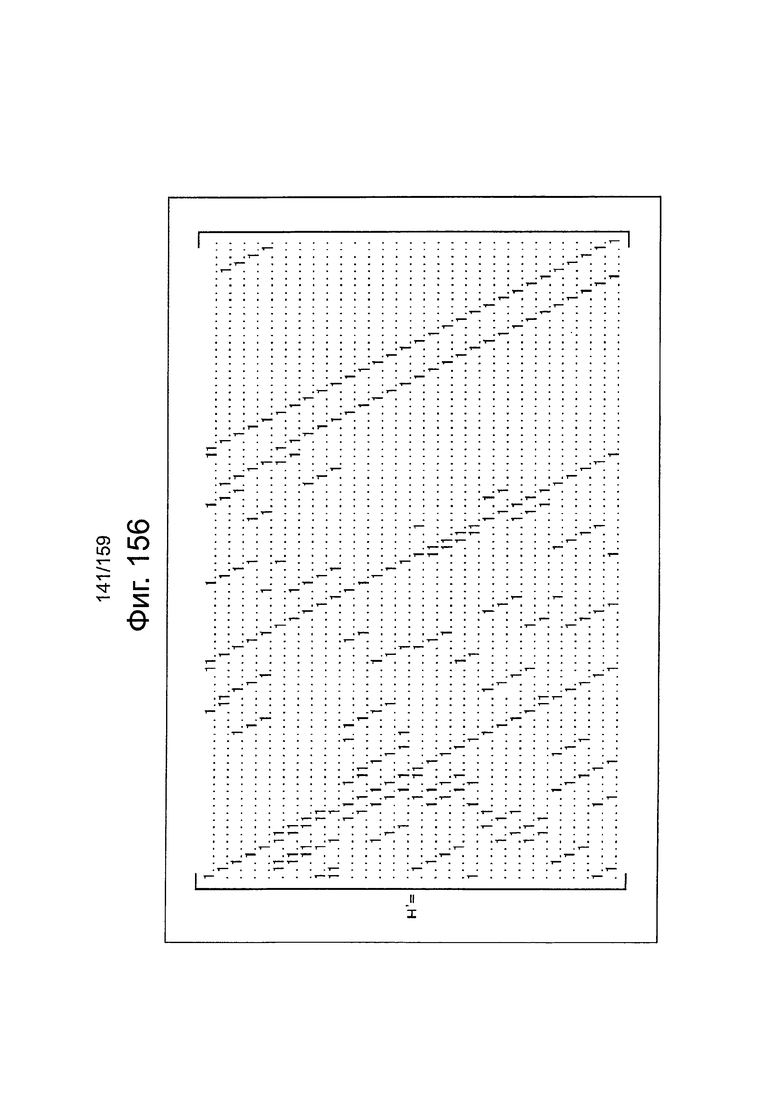

Фиг.156 - иллюстрация матрицы (преобразованной матрицы контроля четности), полученной в результате выполнения замены строк и замены столбцов по отношению к матрице контроля четности.

Фиг.157 - иллюстрация преобразованной матрицы контроля четности, разделенной на блок 5x5.

Фиг.158 - блок-схема, иллюстрирующая пример конфигурации декодирующего устройства, который совместно выполняет операции узла Р.

Фиг.159 - блок-схема, иллюстрирующая пример конфигурации LDPC-декодера 166.

Фиг.160 - иллюстрация процесса мультиплексора 54, образующего битовый деперемежитель 165.

Фиг.161 - иллюстрация процесса деперемежителя 55 с закручиванием столбцов.

Фиг.162 - блок-схема, иллюстрирующая другой пример конфигурации битового деперемежителя 165.

Фиг.163 - блок-схема, иллюстрирующая первый пример конфигурации приемной системы, которую можно применять в приемном устройстве 12.

Фиг.164 - блок-схема, иллюстрирующая второй пример конфигурации приемной системы, которую можно применять в приемном устройстве 12.

Фиг.165 - блок-схема, иллюстрирующая третий пример конфигурации приемной системы, которую можно применять в приемном устройстве 12.

Фиг.166 - иллюстрация группы кодовых битов и группы символьных битов, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 1/3, модулируется с помощью 16QAM, и множитель b равен 2.

Фиг.167 - иллюстрация правила назначения, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 1/3, модулируется с помощью 16QAM, и множитель b равен 2.

Фиг.168 - иллюстрация перестановки кодовых битов согласно правилу назначения, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 1/3, модулируется с помощью 16QAM, и множитель b равен 2.

Фиг.169 - иллюстрация группы кодовых битов и группы символьных битов, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 2/5, модулируется с помощью 16QAM, и множитель b равен 2.

Фиг.170 - иллюстрация правила назначения, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 2/5, модулируется с помощью 16QAM, и множитель b равен 2.

Фиг.171 - иллюстрация перестановки кодовых битов согласно правилу назначения, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 2/5, модулируется с помощью 16QAM, и множитель b равен 2.

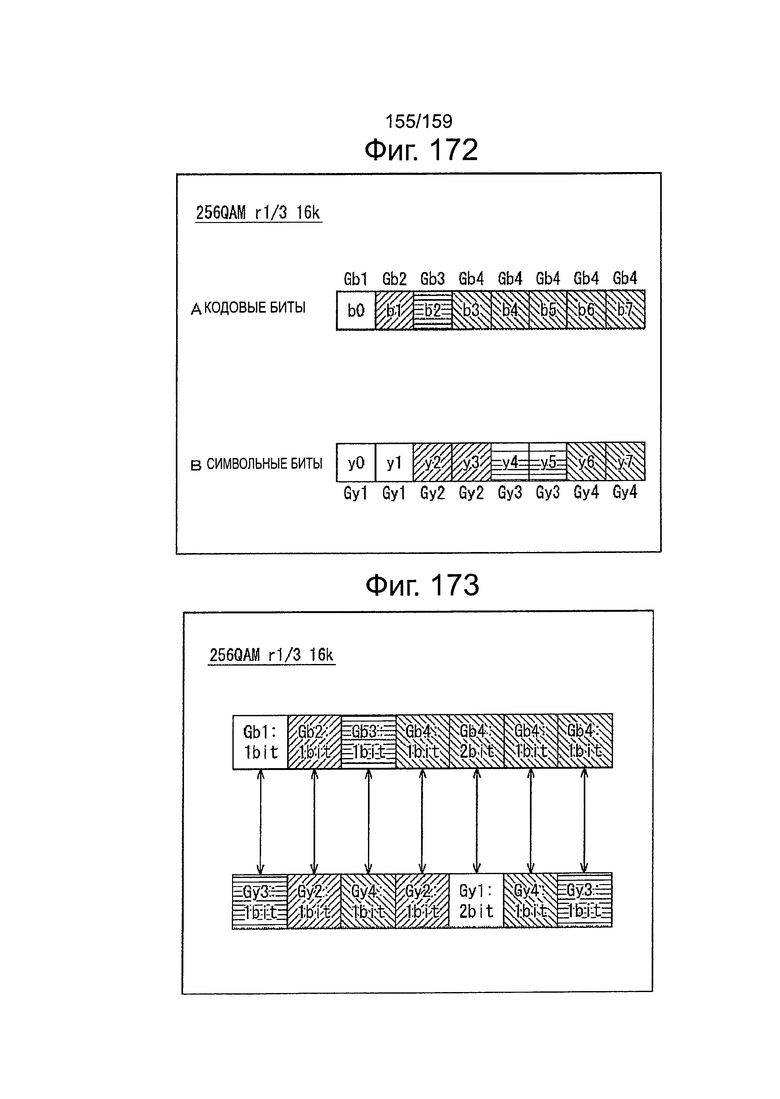

Фиг.172 - иллюстрация группы кодовых битов и группы символьных битов, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 1/3, модулируется с помощью 256QAM, и множитель b равен 2.

Фиг.173 - иллюстрация правила назначения, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 1/3, модулируется с помощью 256QAM, и множитель b равен 2.

Фиг.174 - иллюстрация перестановки кодовых битов согласно правилу назначения, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 1/3, модулируется с помощью 256QAM, и множитель b равен 2.

Фиг.175 - иллюстрация группы кодовых битов и группы символьных битов, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 2/5, модулируется с помощью 256QAM, и множитель b равен 2.

Фиг.176 - иллюстрация правила назначения, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 2/5, модулируется с помощью 256QAM, и множитель b равен 2.

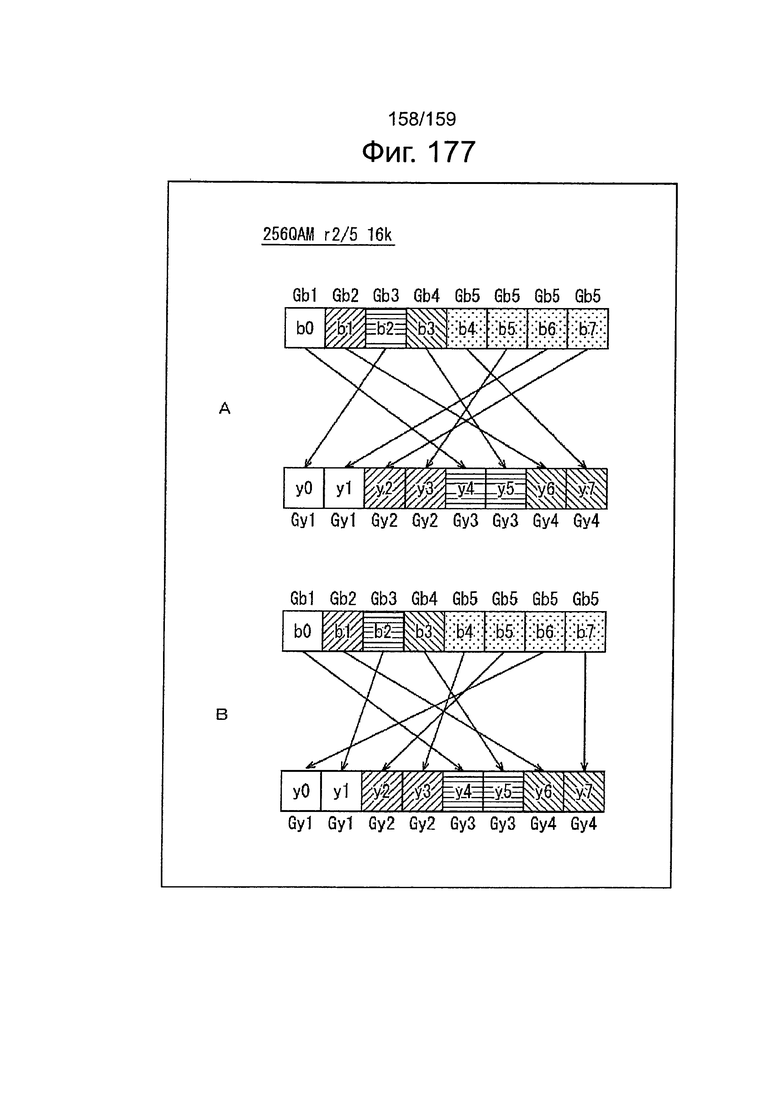

Фиг.177 - иллюстрация перестановки кодовых битов согласно правилу назначения, когда LDPC-код, имеющий длину кода 16k и скорость кодирования 2/5, модулируется с помощью 256QAM, и множитель b равен 2.

Фиг.178 - блок-схема, иллюстрирующая пример конфигурации варианта осуществления компьютера, к которому применимо настоящее изобретение.

Осуществление изобретения

Далее, со ссылкой на прилагаемые чертежи, будут подробно описаны предпочтительные варианты осуществления настоящего изобретения. Следует отметить, что в данном описании и на чертежах, элементы, который имеют, по существу, одну и ту же функцию и структуру, обозначены одинаковыми ссылочными позициями, и их повторное объяснение будет опущено.

Фиг.7 иллюстрирует пример конфигурации варианта осуществления передающей системы (система означает логический ряд из множества устройств, и устройство каждой конфигурации можно разместить или нельзя разместить в одном и том же корпусе), к которой применимо настоящее изобретение.

На фиг.7, передающая система включает в себя передающее устройство 11 и приемное устройство 12.

Передающее устройство 11 передает (транслирует) программу, которая используется исключительно для фиксированного оконечного устройства или портативного оконечного устройства. Иными словами, передающее устройство 11 кодирует целевые данные, которые будут представлять собой цель передачи, такие как данные изображения или данные звука, соответствующие программе, используемой исключительно для фиксированного оконечного устройства или портативного оконечного устройства с LDPC-кодом, и передает LDPC-код через канал 13 связи, который будет представлять собой поверхностную волну.

Приемное устройство 12 представляет собой, например, портативное оконечное устройство и принимает LDPC-код, переданный от передающего устройства 11 через канал 13 связи, декодирует LDPC-код для получения целевых данных и выводит целевые данные.

В этом случае, известно, что LDPC-код, используемый передающей системой, показанной на фиг.7, демонстрирует очень большие возможности в канале связи с AWGN (аддитивным белым гауссовым шумом).

Однако в канале 13 связи, таком как земная радиоволна, может вырабатываться ошибка или стирание пакета. Например, в системе с мультиплексированием с ортогональным частотным разделением каналов (OFDM), мощность определенного символа может становиться равной 0 (стирание) согласно задержке эхо-сигнала (траектория которого отличается от основной траектории) в условиях многолучевого распространения, при которых D/U (отношение сигнал/шум) равно 0 дБ (мощность шума = эхо-сигнала равен мощности сигнала = основной тракт).

При дрожании (добавляется канал связи, в котором задержка равна 0, и эхо-сигнал, имеющей доплеровскую частоту), когда D/U равно 0 дБ, полная мощность OFDM-символа в определенный момент времени может становиться равной 0 (стирание) за счет доплеровской частоты.

В добавление к этому, ошибка пакета может вырабатываться в результате ситуации проводной линии, выходящей из блока приема (не показанного на чертежах) со стороны приемного устройства 12, такого как антенна для приема сигнала, переданного из передающего устройства 11 в приемное устройство 12, или нестабильности источника питания приемного устройства 12.

Между тем, при декодировании LDPC-кода в переменном узле, соответствующем столбцу матрицы Н контроля четности и кодовому биту LDPC-кода, как иллюстрировано на фиг.5 описанным выше, выполняется операция переменного узла согласно выражению (1) с помощью сложения (значения u0i приема) кодового бита LDPC-кода. По этой причине, если ошибка генерируется в кодовых битах, используемых для операции переменного узла, точно вычисленного сообщения ухудшается.

При декодировании LDPC-кода, в проверочном узле, выполняется операция проверочного узла согласно выражению (7) с использованием сообщения, вычисленного с помощью переменного узла, соединенного с проверочным узлом. По этой причине, если увеличивается число проверочных узлов, в которых ошибка (включающая в себя стирание) генерируется одновременно в (кодовых битах LDPC-кодов, соответствующих) множестве соединенных переменных узлов, то эффективность декодирования ухудшается.

Иными словами, если два или более переменных узла из переменных узлов, соединенных с проверочным узлом, одновременно стираются, то проверочный узел возвращает сообщение, в котором вероятность значения, равного 0, и вероятность значения, равного 1, равны друг другу, во все переменные узлы. В этом случае, проверочный узел, который возвращает сообщение с равными вероятностями, не вносит вклад ни в один процесс декодирования (один набор из операции переменного узла и операции проверочного узла). В результате, необходимо увеличивать число раз повторений процесса декодирования, эффективность декодирования ухудшается, и потребляемая мощность приемного устройства 12, которое выполняет декодирование LDPC-кода, увеличивается.

Поэтому в передающей системе, показанной на фиг.7, устойчивость к ошибке пакета или стиранию повышается при сохранении эффективности в канале связи AWGN.

На фиг.8 изображена блок-схема, иллюстрирующая пример конфигурации передающего устройства 11 (фиг.7).

В передающем устройстве 11 один или более входных потоков, соответствующих целевым данным, подаются в мультиплексор 111 с адаптацией режима.

Мультиплексор 111 с адаптацией режима выполняет выбор режима и мультиплексирование одного или более входных потоков, подаваемых в него, и подает полученные в результате данные в устройство 112 заполнения.

Устройство 112 заполнения выполняет обязательное заполнение нулями (вставку нуля) по отношению к данным, поданным из мультиплексора 111 с адаптацией режима, и подает полученные в результате данные в BB-скремблер 113.

BB-скремблер 113 выполняет рассеяние энергии по отношению к данным, поданным из устройства 112 заполнения, и подает полученные в результате данные в ВСН-кодер 114.

ВСН-кодер 114 выполняет ВСН-кодирование по отношению к данным, поданным из ВВ-скремблера 113, и подает полученные в результате данные в качестве целевых данных LDPC, которые будут представлять собой цель LDPC-кодирования, в LDPC-кодер 115.

LDPC-кодер 115 выполняет LDPC-кодирование согласно матрице контроля четности, в которой матрица четности будет представлять собой область, соответствующую биту четности LDPC-кода, принимает вид ступенчатой структуры, в виде LDPC-кодирования по отношению к целевым данным LDPC, поданным из ВСН-кодер 114, и выводит LDPC-код, в котором целевые данные LDPC представляют собой информационные биты.

Иными словами, LDPC-кодер 115 выполняет LDPC-кодирование для кодирования целевых данных LDPC с помощью LDPC, такого как LDPC-код, заданный в стандарте DVB-T.2, и выводит полученный в результате LDPC-код.

В этом случае, в стандарте DVB-T.2 принят LDPC-код, заданный в стандарте DVB-S.2, за исключением случая, в котором длина кода составляет 16200 битов, и скорость кодирования составляет 3/5. LDPC-код, заданный в стандарте DVB-T.2 представляет собой IRA-код (нерегулярный повторяющийся код накопления), и матрица четности матрицы контроля четности LDPC-кода принимает вид ступенчатой структуры. Матрица четности и ступенчатая структура будут описаны позже. IRA-код равно описан, например, в работе "Irregular Repeat-Accumulate Codes", Н. Jin, A. Khandekar, and R.J. McEliece, in Proceedings of 2nd International Symposium on Turbo codes and Related Topics, pp.1-8, Sept. 2000.

LDPC-код, который выводится с помощью LDPC-кодера 115, подается в битовый перемежитель 116.

Битовый перемежитель 116 представляет собой устройство обработки данных, которое выполняет перемежение данных и выполняет перемежение битов, как будет описано позже по отношению к LDPC-коду, подаваемому из LDPC-кодера 115, и подает LDPC-код после битового перемежения на QAM-кодер 117.

QAM-кодер 117 отображает LDPC-код, подаваемый из битового перемежителя 116 в сигнальную точку, представляющую собой один символ ортогональной модуляции в блоке (блоке символов) кодовых битов одного или более битов LDPC-кода, и выполняет ортогональную модуляцию (многоуровневую модуляцию).

Иными словами, QAM-кодер 117 выполняет отображение LDPC-кода, подаваемого из битового перемежителя 116, в сигнальную точку, которая определяется с помощью способа модуляции, выполняющего ортогональную модуляцию LDPC-кода, на плоскости IQ (созвездие IQ), заданной с помощью оси I, представляющей I-компонент той же самой фазы, как и несущая, и оси Q, представляющей Q-компонент, ортогональный к несущей, и выполняет ортогональную модуляцию.

В этом случае, в качестве способа модуляции ортогональной модуляции, выполняемой с помощью QAM-кодера 117, например, существуют способы модуляции, включающие в себя способ модуляции, заданный в стандарте DVB-T, то есть QPSK (квадратурная фазовая манипуляция), 16QAM (квадратурная амплитудная модуляция), 64QAM, 256QAM, 1024QAM и 4096QAM. В QAM-кодере 117 выполняется ортогональная модуляция, на основании которой предварительно устанавливается способ модуляции согласно операции оператора передающего устройства 11. В QAM-кодере 117, например, можно выполнить 4РАМ (импульсно-амплитудную модуляцию) или другие виды ортогональной модуляции.

Данные (символ, отображенный в сигнальную точку), которые получаются в процессе, выполняемом в QAM-кодере 117, подаются во временной перемежитель 118.

Временной перемежитель 118 выполняет временное перемежение для каждого символа по отношению к данным (символу), подаваемым из QAM-кодера 117, и подает полученные в результате данные в MISO/MIMO-кодер (MISO/MIMO-кодер) 119.

MPABHOO/MIMO-кодер 119 выполняет пространственно-временное кодирование по отношению к данным (символу), подаваемым из временного перемежителя 118, и подает данные в частотный перемежитель 120.

Частотный перемежитель 120 выполняет частотное перемежение для каждого символа по отношению к данным (символу), подаваемым из MISO/MIMO-кодера 119, и подает данные в формирователь кадров/блок 131 назначения ресурсов.

Между тем, сигнализация для управления, такая как преамбула, называемая L1, подается в ВСН-кодер 121.

ВСН-кодер 121 выполняет ВСН-кодирование по отношению к сигнализации, подаваемой в него, и подает полученные в результате данные в LDPC-кодер 122, аналогичный ВСН-кодер 114.

LDPC-кодер 122 устанавливает данные, поданные из ВСН-кодера 121, в качестве целевых данных LDPC, выполняет LDPC-кодирование по отношению к данным и подает полученный в результате LDPC-код в QAM-кодер 123, аналогичный LDPC-кодеру 115.

QAM-кодер 123 отображает LDPC-код, поданный из LDPC-кодера 122, в сигнальную точку, представляющую один символ ортогональной модуляции в блоке (блоке символов) кодовых битов из одного или более битов LDPC-кода, выполняет ортогональную модуляцию и подает полученные в результате данные (символ) в частотный перемежитель 124, аналогичный QAM-кодеру 117.

Частотный перемежитель 124 выполняет частотное перемежение для каждого символа по отношению к данным (символу), подаваемым из QAM-кодера 123, и подает данные в формирователь кадров/блок 131 назначения ресурсов, аналогичный частотному перемежителю 120.

Формирователь кадров/блок 131 назначения ресурсов вставляет символы пилот-сигналов в необходимые позиции данных (символов), подаваемых из частотных перемежителей 120 и 124, конфигурирует кадр, включающий в себя символы с предопределенным числом из полученных в результате данных (символов), и подает кадр на блок 132 генерирования OFDM.

Блок 132 генерирования OFDM генерирует OFDM-сигнал, соответствующий кадру, из кадра, поданного из формирователя кадров/блока 131 назначения ресурсов, и передает OFDM-сигнал через канал связи 13 (фиг.7).

Фиг.9 иллюстрирует пример конфигурации битового перемежителя 116, показанного на фиг.8.

Битовый перемежитель 116 представляет собой устройство обработки данных, которое выполняет перемежение данных и включает в себя перемежитель 23 четности, перемежитель 24 с закручиванием столбцов и демультиплексор (DEMUX) 25.

Перемежитель 23 четности выполняет перемежение четности для перемежения битов четности LDPC-кода, подаваемого из LDPC-кодера 115 в позиции других битов четности, и подает LDPC-код после перемежения четности в перемежитель 24 с закручиванием столбцов.

Перемежитель 24 с закручиванием столбцов выполняет перемежение с закручиванием столбцов по отношению к LDPC-коду, подаваемому из перемежителя 23 четности, и подает LDPC-код после перемежения с закручиванием столбцов в демультиплексор 25.

Иными словами, в QAM-кодере 117, показанном на фиг.8, кодовые биты из одного или более битов LDPC-кода отображаются в сигнальную точку, представляющую один символ ортогональной модуляции, и передаются.

В перемежителе 24 с закручиванием столбцов выполняется перемежение с закручиванием столбцов, которое будет описано позже в качестве процесса перегруппировки для перегруппировки кодовых битов LDPC-кода, подаваемого из перемежителя 23 четности, таким образом, чтобы множество кодовых битов LDPC-кода, соответствующего 1 в любой одной строке матрицы контроля четности, используемой LDPC-кодером 115, не включалось в один символ.

Демультиплексор 25 выполняет процесс перестановки для перестановки позиций двух или более кодовых битов LDPC-кода, принимающего вид символа, по отношению к LDPC-коду, подаваемому из перемежителя 24 с закручиванием столбцов, и получают LDPC-код, в котором усилена устойчивость к AWGN. В дополнение к этому, демультиплексор 25 подает два или более кодовых битов LDPC-кода, полученных в процессе перестановки, в виде символа в QAM-кодер 117 (фиг.8).

Далее фиг.10 иллюстрирует матрицу Н контроля четности, которая используется для LDPC-кодирования с помощью LDPC-кодером 115, показанным на фиг.8.

Матрица Н контроля четности принимает вид LDGM (порождающей матрицы низкой плотности) структуры и может быть представлена с помощью выражения H=[HA|HT] (матрица, в которой элементы информационной матрицы HA установлены в левых элементах, и элементы матрицы HT четности установлены в правых элементах), с использованием информационной матрицы HA области, соответствующей информационным битам среди кодовых битов LDPC-кода, и матрицы HT четности, соответствующей битам четности.

В этом случае число битов информационных битов среди кодовых битов одного LDPC-кода (одного кодового слова) и число битов четности называются информационной длиной K и длиной M четности, соответственно, и число битов кодовых битов одного LDPC-кода называется кодовой длиной N (=K+M).

Информационная длина K и длина M четности LDPC-кода, имеющего определенную кодовую длину N, определяются с помощью скорости кодирования. Матрица H контроля четности принимает вид матрицы, в которой строка×столбец представляет собой M×N. Информационная матрица HA принимает вид матрицы M×K, и матрица HT четности становится матрицей M×M.

Фиг.11 иллюстрирует матрицу HT четности матрицы Н контроля четности LDPC-кода, которая задана в стандарте DVB-T.2 (и DVB-S.2).

Матрица HT четности матрицы Н контроля четности LDPC-кода, которая задана в стандарте DVB-T.2, принимает вид ступенчатой структуры, в которой элементы 1 размещены в ступенчатой форме, как иллюстрировано на фиг.11. Вес строки матрицы HT четности становится равным 1 по отношению к первой строке и становится равным 2 по отношению к оставшимся строкам. Вес столбца становится равным 1 по отношению к конечному столбцу и становится равным 2 по отношению к оставшимся столбцам.

Как описано выше, LDPC-код матрицы Н контроля четности, в которой матрица HT четности принимает вид ступенчатой структуры, можно легко сгенерировать с использованием матрицы Н контроля четности.

Иными словами, LDPC-код (одно кодовое слово) выражается с помощью вектора-строки c, и вектор столбца, полученный путем транспонирования вектора-строки, представлен с помощью CT. В добавление к этому, область информационных битов вектора-строки с, которая будет представлять собой LDPC-код, представлен вектором-строкой A, и часть битов четности представлена вектором-строкой T.

В этом случае вектор-строку с можно представить с помощью выражения c=[A|T] (вектор-строка, в котором элементы вектора-строки установлены в левых элементах, и элементы вектора-строки T установлены в правых элементах), с использованием вектора-строки, соответствующего информационным битам, и вектора-строки T, соответствующего битам четности.

В матрице Н контроля четности вектор-строка c=[A|T], соответствующий LDPC-коду, должен удовлетворять выражению HcT=0. Вектор-строка T, который соответствует битам четности, образующим вектор-строку c=[A|T], удовлетворяющий выражению HcT=0, можно последовательно вычислить путем установки элемента в каждой строке на 0, последовательно из элементов первой строки вектора-столбца HcT в выражении HCT=0, когда матрица HT четности матрицы H=[HA|HT] контроля четности принимает вид ступенчатой структуры, иллюстрированной на фиг.11.

Фиг.12 - иллюстрация матрицы Н контроля четности LDPC-кода, которая задана в стандарте DVB-T.2.

Вес столбца становится равным X по отношению к столбцам КХ из первого столбца матрицы Н контроля четности LDPC-кода, заданного в стандарте DVB-T.2, становится равным 3 по отношению к следующим Столбцам K3, становится равным 2 по отношению к следующим столбцам (М-1) и становится равным 1 по отношению к последнему столбцу.

В этом случае выражение KX+K3+M-1+1 равно кодовой длине N.

На фиг.13 изображена иллюстрация чисел KX, K3 и M столбцов и вес X столбца по отношению к каждой скорости г кодирования LDPC-кода, заданного в стандарте DVB-T.2.

В стандарте DVB-T.2 заданные LDPC-коды, которые имеют кодовые длины N, равные 64800 битов и 16200 битов.

По отношению к LDPC-коду, имеющему кодовую длину N, равную 64800 битов, заданы 11 скоростей кодирования (номинальных скоростей) равных 1/4, 1/3, 2/5, 1/2, 3/5, 2/3, 3/4, 4/5, 5/6, 8/9 и 9/10. По отношению к LDPC-коду, имеющему кодовую длину N, равную 16200 битов, заданы 10 скоростей кодирования, равные 1/4, 1/3, 2/5, 1/2, 3/5, 2/3, 3/4, 4/5, 5/6 и 8/9.

В дальнейшем длина кода N, равная 64800 битов, называется как 64 кбитов, и длина кода N, равная 16200, называется как 16 кбитов.

В отношении LDPC-кода, известно, что скорость ошибки является низкой в кодовом бите, соответствующем столбец, вес столбца которого в матрице H контроля четности является большим.

В матрице Н контроля четности, которая иллюстрирована на фиг.12 и 13 и задана в стандарте DVB-T.2, вес столбца верхней стороны (левой стороны) имеет тенденцию быть большим. Таким образом, по отношению к LDPC-коду, соответствующему матрице Н контроля четности, кодовый бит верхней стороны имеет тенденцию быть устойчивым к ошибке (существует устойчивость к ошибке), и кодовый бит конечной стороны имеет тенденцию быть неустойчивым к ошибке.

Далее фиг.14 иллюстрирует размещение (сигнальные точки, соответствующие,) 16 символов на плоскости IQ, когда 16QAM выполняется с помощью QAM-кодера 117, показанного на фиг.8.

Иными словами, поз.A на фиг.14 иллюстрирует символы 16QAM DVB-T.2.

В 16QAM один символ представлен 4 битами, и существуют 16 символов (=24). 16 символов размещаются таким образом, чтобы направление I×направление Q принимали форму квадрата 4×4, на основе оригинальной точки плоскости IQ.

Если (i+1)-ый бит из наиболее значимого бита битовой строки, представленной одним символом, представлен в виде бита yi, то 4 бита, представленные одним символом 16QAM, могут быть представлены в виде битов y0, y1, y2 и y3, соответственно, последовательно от наиболее значимого бита. Когда способ модуляции представляет собой 16QAM, 4 бита кодовых битов LDPC-кода принимают вид символа (принимают значение символа) из 4 битов y0-y3 (символизируются).

Поз.B на фиг.14 иллюстрирует битовую границу по отношению к каждому из 4 битов (которые в дальнейшем называются символьными битами) y0-y3, представленных с помощью символа 16QAM.

В этом случае битовая граница по отношению к символьному биту yi (на фиг.14, i=0, 1, 2 и 3) означает границу символа, символьный бит yi которого становится равным 0, и символа, символьный бит yi которого становится равным 1.

Как показано B на фиг.14, только одно место оси Q плоскости IQ принимает вид битовой границы по отношению к наиболее значимому символьному биту y0 из 4 символьных битов y0-y3 представленных с помощью символа 16QAM, и только одно место оси I плоскости IQ принимает вид битовой границы по отношению ко второму (второму из наиболее значимого бита) символьному биту y1.

По отношению к третьему символьному биту y2, два места из места между первым и вторым столбцами с левой стороны и места между третьим и четвертым столбцами среди символов 4×4 принимают вид битовых границ.

Что касается четвертого символьного бита y3, два места из места между первой и второй строками с верхней стороны и места между третьей и четвертой строками, среди символов 4×4 принимают вид битовых границ.

В символьных битах yi, которые представлены с символами, когда число символов в стороне от битовых границ является большим, возникновение ошибки является трудным (вероятность ошибки является низкой), и когда число символов, которые находятся близко к битовым границам, является большим, легко возникает ошибка (вероятность ошибки становится высокой).