Область техники

Изобретение относится к устройству и способу для осуществления обращенного циклического сдвига и/или обращенного перемежения данных.

Предпосылки создания изобретения

В системе наземной связи 8 VSB (с частичным подавлением боковой полосы) передача информации к приемной станции может быть осуществлена при помощи беспроводной радиосвязи. В приведенном в качестве примера варианте такой системы каждые два бита передаваемых данных преобразуют в трехбитный решетчатый код, который отображают как символ, имеющий восемь возможных уровней так, чтобы каждый байт данных был представлен четырьмя символами. Перед тем, как осуществить передачу символов в кадрах данных, осуществляют их перемежение (изменение чередования), а для некоторых символов осуществляют их циклический сдвиг.

Кадр данных, используемый в системе 8 VSBT, раскрыт в Стандарте Цифрового Телевидения ATSC (опубликованном 16 сентября 1995 г.) и, в частности, в разделе 4.1 Приложения D к нему. Этот кадр данных включает в себя множество сегментов (т.е. строк), в котором каждый сегмент содержит группы данных, и в котором каждая группа данных включает в себя множество элементов данных. Например, каждый сегмент может содержать шестьдесят девять групп данных, каждая группа данных может включать в себя двенадцать элементов данных, а элемент данных может быть символом данных. Первый сегмент такого кадра данных содержит информацию синхронизации кадра, а каждый последующий сегмент в кадре данных имеет начальную часть, содержащую информацию синхронизации сегмента (в виде четырех символов синхронизации сегмента), и последующую часть, содержащую данные.

Из-за того, что кадр данных содержит информацию синхронизации кадра и сегмента, для облегчения обработки данных приемником в некоторых группах данных может быть осуществлен циклический сдвиг элементов данных. Этот циклический сдвиг описан в разделе 4.2.5 Приложения D и в табл.2 вышеуказанного стандарта. Следовательно, должны быть осуществлены обращение циклического сдвига и обращенное перемежение полученных приемником данных, имеющих циклический сдвиг и перемежение.

Настоящее изобретение ориентировано на устройство для осуществления обращения циклического сдвига и/или обращенного перемежения таких элементов данных, как символы.

Сущность изобретения

В соответствии с одной отличительной особенностью настоящего изобретения устройство для обработки данных с циклическим сдвигом и перемежением включает в себя средство обращения циклического сдвига и средство обращенного перемежения. Средство обращения циклического сдвига осуществляет обращение циклического сдвига данных с циклическим сдвигом и перемежением для того, чтобы получить данные с обращенным циклическим сдвигом и перемежением. Средство обращенного перемежения осуществляет обращенное перемежение данных с обращенным циклическим сдвигом и перемежением для того, чтобы получить данные с обращенным циклическим сдвигом и обращенным перемежением.

В соответствии с другой отличительной особенностью настоящего изобретения устройство для обработки данных с циклическим сдвигом и перемежением включает в себя первое и второе средства памяти и первое и второе средства адресации. В первом средстве памяти хранят D элементов данных с циклическим сдвигом и перемежением. Первое средство адресации осуществляет такую адресацию первого средства памяти, чтобы осуществлять считывание данных с обращенным циклическим сдвигом и перемежением из первого средства памяти и осуществлять запись данных с циклическим сдвигом и перемежением в первое средство памяти. Во втором средстве памяти хранят nD элементов данных с обращенным циклическим сдвигом и перемежением, считанных из первого средства памяти. Второе средство адресации осуществляет такую адресацию второго средства памяти, чтобы осуществлять считывание данных с обращенным циклическим сдвигом и обращенным перемежением из второго средства памяти и осуществлять запись данных с обращенным циклическим сдвигом и перемежением из первого средства памяти во второе средство памяти.

В соответствии с еще одной отличительной особенностью настоящего изобретения осуществлено устройство для обращения циклического сдвига данных с циклическим сдвигом. Циклический сдвиг данных с циклическим сдвигом осуществляют по D элементам данных. Устройство включает в себя средство памяти и средство адресации. В средстве памяти хранят D элементов данных из данных, имеющих циклический сдвиг, в соответствующих D ячейках памяти. Средство адресации осуществляет адресацию средства памяти так, чтобы считывать данные с обращенным циклическим сдвигом из D ячеек памяти и записывать данные с циклическим сдвигом в D ячеек памяти.

Краткое описание чертежей

Эти и другие признаки и преимущества настоящего изобретения станут более очевидными при подробном рассмотрении изобретения совместно с чертежами, на которых:

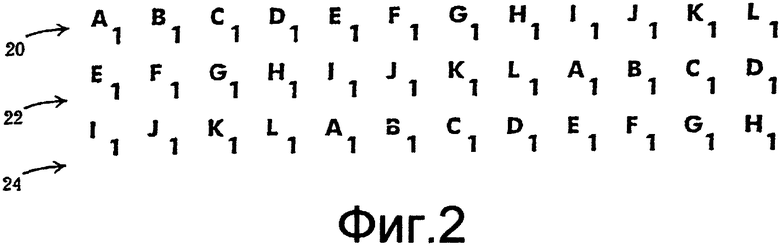

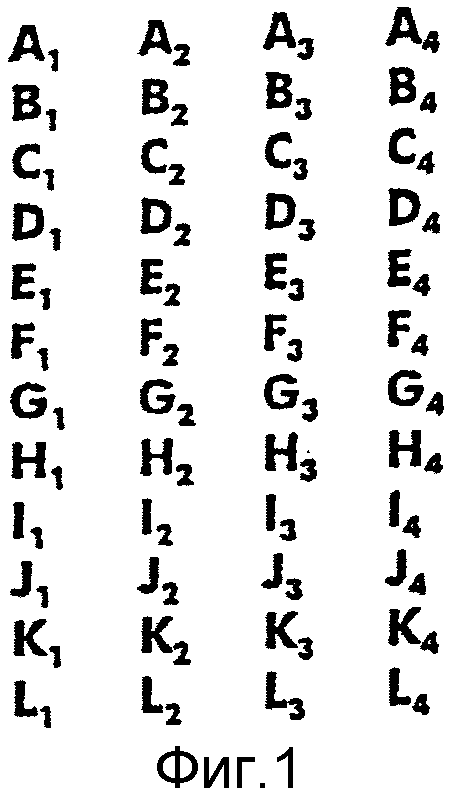

на фиг. 1 показан пример данных с построчным порядком записи, который полезен для объяснения процедуры перемежения данных, обращенное перемежение которых должно быть осуществлено в соответствии с настоящим изобретением;

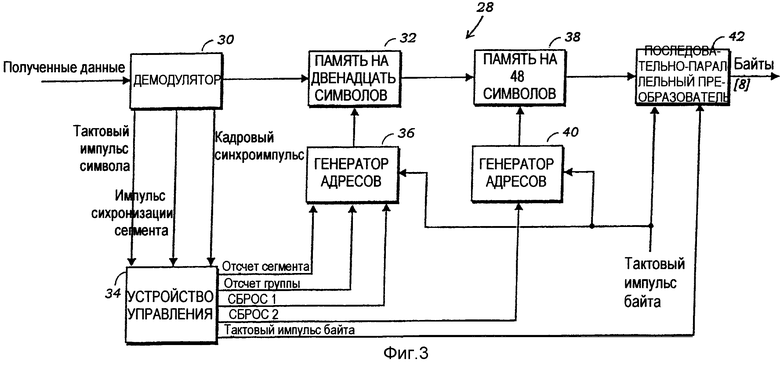

на фиг. 2 показан пример данных, который полезен для объяснения циклического сдвига данных, обращение циклического сдвига которых должно быть осуществлено в соответствии с настоящим изобретением;

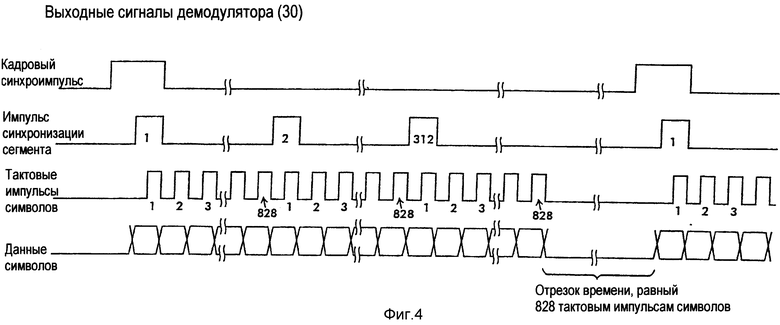

на фиг. 3 показано устройство обращения циклического сдвига и обращенного перемежения в соответствии с настоящим изобретением;

фиг. 4 представляет собой временную диаграмму для демодулятора 30 из фиг. 3;

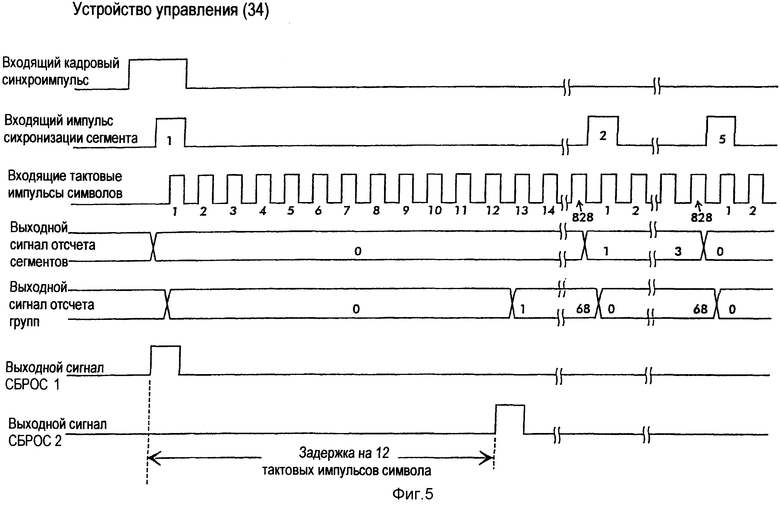

фиг. 5 представляет собой временную диаграмму для контроллера 34 из фиг. 3;

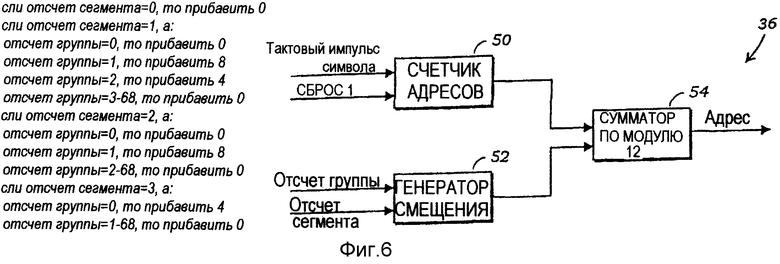

на фиг. 6 показан более подробный вид генератора 36 адресов из фиг. 3;

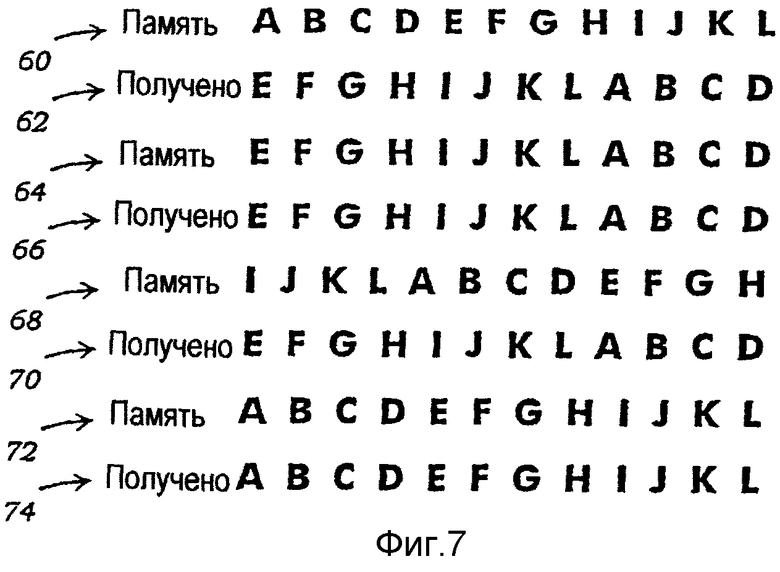

на фиг. 7 показан пример данных, который полезен для объяснения работы генератора 36 адресов, показанного на фиг. 6;

на фиг. 8 показан более подробный вид одного из вариантов осуществления генератора 40 адресов из фиг. 3;

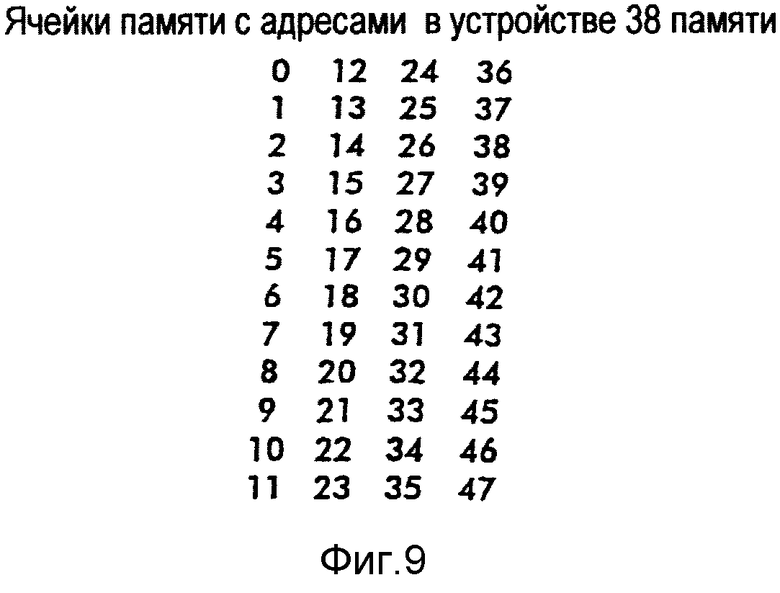

на фиг. 9 изображены ячейки памяти второго средства 38 памяти;

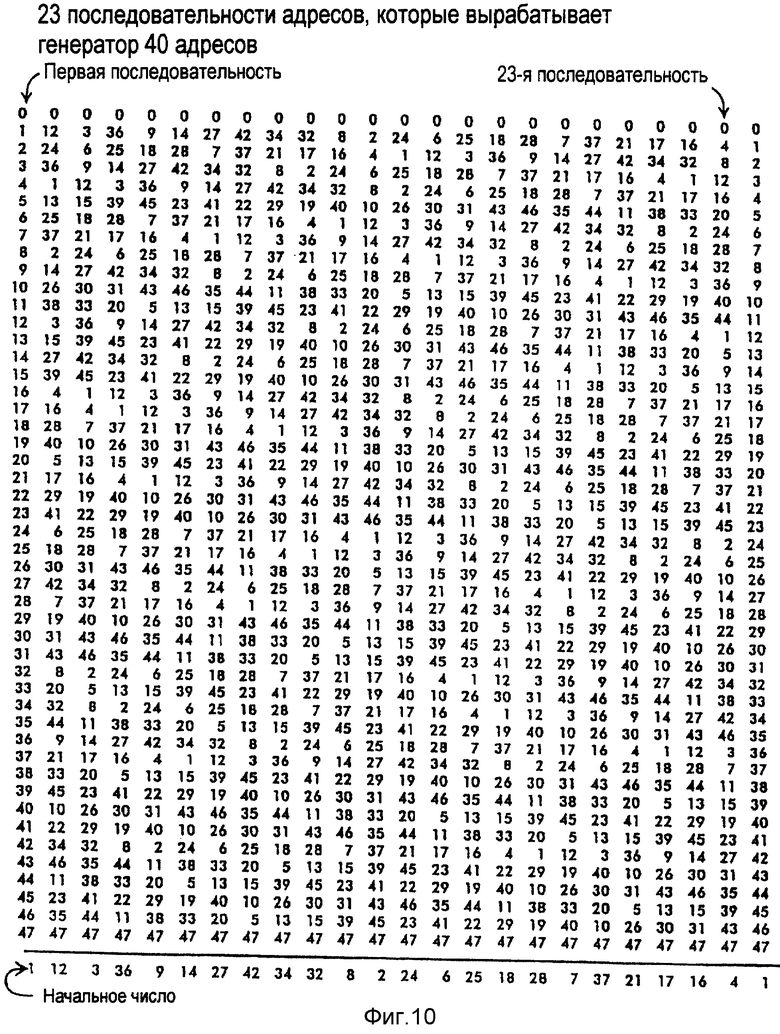

на фиг. 10 показаны последовательности адресов, созданные генератором 40 адресов из фиг. 3;

фиг. 11А и фиг. 11Б представляют собой временные диаграммы для генератора 40 адресов из фиг. 3;

на фиг. 12 показан более подробный вид первого варианта осуществления генератора 82 начальных чисел из фиг. 8;

на фиг. 13 показан более подробный вид второго варианта осуществления генератора 82 начальных чисел из фиг. 8;

на фиг. 14 показан более подробный вид оператора 98 умножения на двенадцать и корректировки по модулю сорок семь из фиг. 13;

на фиг. 15 показан более подробный вид логического устройства 106 корректировки по модулю сорок семь из фиг. 14; и

на фиг. 16 показан более подробный вид другого варианта осуществления генератора 40 адресов из фиг. 3.

Подробное описание

На фиг. 1 показано множество байтов элементов данных, которые являются результатом сканирования части изображения. Первый байт данных содержит символы данных A1, А2, А3 и А4. Каждый из этих символов данных может представлять собой, например, два бита данных. Следовательно, первый байт символов данных представляет собой восемь битов данных. Второй байт данных содержит символы данных B1-B4, третий байт данных содержит символы данных C1-C4,. .., а двенадцатый байт данных содержит символы данных L1-L4.

Устройство перемежения символов в передатчике может иметь такую конфигурацию, чтобы осуществлять перемежение символов данных из фиг. 1, хотя может быть осуществлено перемежение и любой другой последовательности символов данных или элементов данных. Соответственно, устройство перемежения символов преобразует упорядоченные по строкам символы данных, показанные на фиг. 1, в упорядоченные по столбцам так, чтобы осуществлять передачу символов данных как элементов данных, упорядоченных по столбцам. Следовательно, вместо того, чтобы передатчик осуществлял передачу символа данных А2 после символа данных A1, символа данных А3 после символа данных A2, символа данных А4 после символа данных А3, символа данных B1 после символа данных А4 и так далее, передатчик (не принимая во внимание другую обработку, которая может изменить упорядочение символов данных) осуществляет передачу в следующей последовательности: символ данных A1, символ данных B1,..., символ данных L1, символ данных А2,.... Таким образом, каждый столбец символов данных, показанных на фиг. 1, представляет собой такую группу из двенадцати элементов данных, в которой первым передают первый столбец, вторым передают второй столбец, и так далее.

На фиг. 2 показана одна группа символов данных в сегменте 20 кадра данных. Как показано на фиг. 2, группа символов данных в этой группе символов данных в сегменте 20 не имеет циклического сдвига. Однако другие группы символов данных в сегменте 20 или в других сегментах могут иметь циклический сдвиг. Например, символы данных в группе символов данных в сегменте 22 имеют циклический сдвиг на восемь, а символы данных в группе символов данных в сегменте 24 имеют циклический сдвиг на четыре (хотя в описанном далее варианте осуществления настоящего изобретения предполагают, что передатчик не осуществляет циклический сдвиг данных на четыре). Таким образом, последующую передачу символов данных, показанных на фиг. 1 и 2, осуществляют как данных, имеющих перемежение и циклический сдвиг.

На фиг. 3 показано устройство 28 для обращения циклического сдвига и обращенного перемежения данных, имеющих перемежение и циклический сдвиг. Устройство 28 включает в себя демодулятор 30 (например, демодулятор системы ATSC 8 VSB). Демодулятор 30 принимает сигнал системы 8 VSB в стандарте ATSC в режиме наземной связи и вырабатывает следующие четыре выходных сигнала: сигнал синхронизации кадра, который находится в конце сегмента кадрового синхроимпульса; сигнал синхронизации сегмента, который совпадает с тактом первого символа каждого сегмента данных; тактовый сигнал символа; и данные с перемежением и циклическим сдвигом. Данные с перемежением и циклическим сдвигом подают на первое устройство 32 памяти. Для каждого кадра вырабатывают 312 сигналов синхронизации сегментов, но не существует никаких синхроимпульсов сегмента, созданных для сегмента кадрового синхроимпульса. Для каждого сегмента данных создают 828 тактовых импульсов символа, а каждый тактовый импульс символа совпадает с соответствующим символом данных. Однако не существует никаких тактовых импульсов символа, которые созданы либо в течение отрезка времени, соответствующего сегменту кадрового синхроимпульса, либо в течение отрезка времени, соответствующего четырем символам синхроимпульса сегмента в сигнале синхронизации сегмента. Следовательно, существуют только те тактовые импульсы символа, которые соответствуют символам данных. Фиг. 4 представляет собой временную диаграмму, на которой показаны выходные сигналы демодулятора 30.

Сигнал синхронизации кадра, сигнал синхронизации сегмента и сигнал тактового импульса символа подают на контроллер 34, а контроллер 34 вырабатывает следующие пять выходных сигналов: сигнал отсчета сегмента, сигнал отсчета группы, два сигнала сброса СБРОС 1 и СБРОС 2; и тактовый сигнал байта. Сигнал отсчета сегмента является выходным сигналом счетчика деления на четыре, сброс которого в нулевое состояние осуществляют при совпадении сигналов синхронизации кадра и синхронизации сегмента. Затем увеличивают содержимое счетчика при каждом сигнале синхронизации сегмента, что приводит к циклическому изменению сигнала отсчета сегмента, принимающего значения отчетов 0, 1, 2, 3, 0, 1, 2, 3.... Поскольку каждый кадр имеет 312 сигналов синхронизации сегмента, и так как число 312 делится на четыре, то значение отсчета сегмента, соответствующего последнему сегменту кадра, будет равно 3. Следовательно, сигнал отсчета сегмента циклически проходит через свои четыре значения 78 раз (312/4) за кадр.

Сигнал отсчета группы является выходным сигналом счетчика, который отсчитывает группы по двенадцать тактовых импульсов символа. Сигнал отсчета группы увеличивают на единицу тогда, когда прошли двенадцать тактовых импульсов символа. Сброс его в нулевое состояние осуществляют при совпадении сигнала синхронизации сегмента и тактового сигнала символа. Поскольку каждый сегмент имеет 828 символов, и так как 828/12=69, то сигнал отсчета группы циклически повторяется от 0 до 68 при прохождении каждого сегмента данных. Таким образом, выходной сигнал отсчета группы циклически проходит значения отчетов 0, 1... 68, 0, 1... 68, 0.... Сигнал СБРОС 1 получают из сигнала синхронизации кадра. Сигнал СБРОС 2 представляет собой вариант сигнала СБРОС 1 с задержкой на двенадцать тактов символа. Генерацию тактового сигнала байта осуществляют каждый четвертый такт символа. Фиг. 5 представляет собой временную диаграмму, на которой показаны выходные сигналы контроллера 34.

Сигнал отсчета сегмента, сигнал отсчета группы, тактовый сигнал символа и сигнал СБРОС 1 подают на первый генератор 36 адресов, который подает адреса в первое устройство 32 памяти. Соответственно в ответ на сигнал отсчета сегмента, сигнал отсчета группы, тактовый сигнал символа и сигнал СБРОС 1 из контроллера 34, генератор 36 адресов осуществляет считывание из первого устройства 32 памяти группы данных, имеющих обращенный циклический сдвиг и перемежение, и осуществляет запись в первое устройство 32 памяти группы данных, имеющих циклический сдвиг и перемежение, заменяя считанную группу данных.

В вышеупомянутом примере, в котором группа данных включает в себя двенадцать символов данных и в котором каждый символ данных соответствует двум битам информации, первое устройство 32 памяти представляет собой устройство памяти на двенадцать символов. Таким образом, в ответ на сигнал отсчета сегмента, сигнал отсчета группы, тактовый сигнал символа и сигнал СБРОС 1, генератор 36 адресов осуществляет считывание из первого устройства 32 памяти двенадцать символов данных, имеющих обращенный циклический сдвиг и перемежение, и осуществляет запись в первое устройство 32 памяти двенадцати символов данных, имеющих циклический сдвиг и перемежение, для замены двенадцати считанных символов данных. В частности, в ответ на первый тактовый импульс символа генератор 36 адресов считывает из первой ячейки памяти первого устройства 32 памяти первый символ данных и записывает в первую ячейку памяти первого устройства 32 памяти символ данных так, чтобы произвести замену первого считанного символа данных. В ответ на второй тактовый импульс символа генератор 36 адресов осуществляет приращение на единицу его адреса на выходе, считывает из второй ячейки памяти первого устройства 32 памяти второй символ данных и записывает во вторую ячейку памяти первого устройства 32 памяти символ данных так, чтобы произвести замену второго считанного символа данных, и так далее до тех пор, пока не будут считаны и заменены все двенадцать символов данных в группе. Адреса, которые первый генератор 36 адресов подает на первое устройство 32 памяти, расположены в таком порядке, чтобы осуществить обращение циклического сдвига символов данных, хранящихся в первом устройстве 32 памяти. Процесс обращения циклического сдвига данных, хранящихся в первом устройстве 32 памяти, будет объяснен более подробно при описании фиг. 6.

Следовательно, подаваемые на выход первого устройства 32 памяти данные имеют обращение циклического сдвига, но все еще имеют перемежение. Для осуществления обращенного перемежения данных с обращенным циклическим сдвигом, но еще сохраняющих перемежение, предложены второе устройство 38 памяти и второй генератор 40 адресов. На генератор 40 адресов подают тактовый сигнал символа из демодулятора 30 и сигнал СБРОС 2 из контроллера 34. В ответ на тактовый сигнал символа второй генератор 40 адресов осуществляет генерацию адреса для второго устройства 38 памяти так, что каждый адрес побуждает выполнять считывание одного из символов данных, хранящихся в соответствующей ячейке памяти второго устройства 38 памяти, и осуществлять запись символа данных из первого устройства 32 памяти в эту ячейку памяти второго устройства 38 памяти так, чтобы произвести замену только что считанного символа данных, и так далее. На основании этих адресов, генерация которых произведена вторым генератором 40 адресов, осуществляют такое считывание данных с обращенным циклическим сдвигом, но имеющих перемежение, которые хранятся во втором устройстве 38 памяти, что данные получают обращенный циклический сдвиг и обращенное перемежение. Эти данные с обращенным циклическим сдвигом и обращенным перемежением подают на преобразователь 42 последовательного кода в параллельный, который получает каждый двухбитный символ данных из второго устройства 38 памяти, и осуществляет преобразование битов четырех символов данных в байт из восьми параллельных битов в ответ на тактовый сигнал байта из контроллера 34.

Первый генератор 36 адресов из фиг. 3 более подробно показан на фиг. 6. Первый генератор 36 адресов включает в себя счетчик 50 адресов, генератор 52 смещений, и сумматор 54 по модулю двенадцать. Счетчик 50 адресов отсчитывает двенадцать тактов символа, а затем осуществляют его сброс. Следовательно, значение на выходе счетчика 50 адресов изменяется от нуля до одиннадцати, а затем сбрасывается до нуля. Генератор 52 смещений реагирует на сигнал отсчета группы и сигнал отсчета сегмента из контроллера 34 так, чтобы осуществить генерацию смещения (на которое в альтернативном варианте может быть ссылка как на начальное число). Для того чтобы осуществить генерацию адреса, который подают на первое устройство 32 памяти, сумматор 54 по модулю двенадцать суммирует отсчет на выходе счетчика 50 адресов со значением смещения от генератора 52 смещений. Генератор 52 смещений может представлять собой просто набор стандартных логических элементов, которые скомпонованы в соответствии с показанными на фиг. 6 уравнениями. В альтернативном варианте генератор 52 смещений может включать в себя постоянное запоминающее устройство и декодер адреса, который декодирует сигналы отсчета группы и отсчета сегмента для того, чтобы иметь доступ к определенным ячейкам памяти в постоянном запоминающем устройстве для получения смещений, подаваемых в сумматор 54 по модулю двенадцать.

На фиг. 6 приведен пример смещений, генерация которых может быть осуществлена генератором 52 смещений. Эти смещения вырабатывают на основании следующего протокола циклического сдвига (см. вышеупомянутый Стандарт Цифровой Телевизионной Связи ATSC), реализуемого передатчиком: (1) циклический сдвиг символов данных в первом сегменте каждого набора из четырех сегментов не производят; (2) осуществляют циклический сдвиг символов данных на восемь в группах 0, 1, и 2 второго сегмента в каждом наборе из четырех сегментов, а циклический сдвиг других групп символов данных в этом сегменте не производят; (3) осуществляют циклический сдвиг символов данных на восемь в группах 0 и 1 из третьего сегмента в каждом наборе из четырех сегментов, а циклический сдвиг символов данных в других группах данных в этом сегменте не производят; и (4) осуществляют циклический сдвиг символов данных на восемь в группе 0 из четвертого сегмента в каждом наборе из четырех сегментов, а циклический сдвиг символов данных в других группах данных в этом сегменте не производят. Таким образом, протокол циклического сдвига повторяют через каждые четыре сегмента, а циклический сдвиг осуществляют только для определенных групп данных в определенных сегментах.

Таким образом, поскольку первый сегмент в каждом наборе из четырех сегментов (который соответствует отсчету сегмента, равному нулю) не имеет циклического сдвига, то для первого сегмента в каждом наборе из четырех сегментов генератор 52 смещений подает на выход значение смещения, равное нулю. Для того чтобы осуществить генерацию двенадцати адресов для считывания двенадцати символов данных из первого устройства 32 памяти и записи двенадцати новых символов данных в первое устройство 32 памяти, сумматор 54 по модулю двенадцать прибавляет этот выходное значение смещения, равное нулю, к двенадцати отсчетам на выходе счетчика адресов 50.

Когда отсчет сегмента равен единице, а отсчет группы равен нулю (то есть, это первая группа из двенадцати символов данных, которая находится во втором сегменте каждого набора из четырех сегментов, и для которой был осуществлен циклический сдвиг на восемь), то генератор 52 смещений выдает на выходе смещение, равное нулю. Для того чтобы осуществить генерацию двенадцати адресов для считывания двенадцати символов данных из первого устройства 32 памяти, сумматор 54 по модулю двенадцать прибавляет это выходное значение смещения, равное нулю, к двенадцати отсчетам на выходе счетчика адресов 50. Когда отсчет сегмента равен единице, а отсчет группы равен единице (то есть, это вторая группа из двенадцати символов данных, которая находится во втором сегменте каждого набора из четырех сегментов, и для которой был осуществлен циклический сдвиг на восемь), то генератор смещений 52 выдаст на выходе смещение, равное восьми. Для того чтобы осуществить генерацию двенадцати адресов для считывания двенадцати символов данных из первого устройства 32 памяти, сумматор 54 по модулю двенадцать прибавляет это выходное значение смещения, равное восьми, к двенадцати отсчетам на выходе счетчика адресов 50 по закону пересчета по модулю двенадцать. Когда отсчет сегмента равен единице, а отсчет группы равен двум (то есть, это третья группа двенадцати символов данных, которая находится во втором сегменте каждого набора из четырех сегментов, и для которой был осуществлен циклический сдвиг на восемь), то генератор смещений выдает на выходе смещение, равное четырем, которое по закону пересчета по модулю двенадцать прибавляют в сумматоре 54 по модулю двенадцать к двенадцати отсчетам на выходе счетчика 50 адресов для того, чтобы осуществить генерацию двенадцати адресов для считывания двенадцати символов данных из первого устройства 32 памяти. Когда отсчет сегмента равен единице, а отсчет группы принимает значения от трех до шестидесяти восьми, то генератор смещений выдает на выходе смещение, равное нулю, которое по закону пересчета по модулю двенадцать прибавляют в сумматоре 54 по модулю двенадцать к наборам из двенадцати отчетов на выходе счетчика 50 адресов для того, чтобы осуществить генерацию соответствующих наборов из двенадцати адресов для считывания из первого устройства 32 памяти соответствующих наборов из двенадцати символов данных.

Когда отсчет сегмента равен двум, а отсчет группы равен нулю (то есть, это первая группа из двенадцати символов данных в третьем сегменте каждого набора из четырех сегментов), то генератор 52 смещений выдает на выходе смещение, равное нулю, которое прибавляют в сумматоре 54 по модулю двенадцать к двенадцати отсчетам на выходе счетчика 50 адресов для того, чтобы осуществить генерацию адресов для считывания двенадцати символов данных из первого устройства 32 памяти. Когда отсчет сегмента равен двум, а отсчет группы равен единице (то есть, это вторая группа из двенадцати символов данных во втором сегменте каждого набора из четырех сегментов), то генератор 52 смещений выдает на выходе смещение, равное восьми, которое по закону пересчета по модулю двенадцать прибавляют в сумматоре 54 по модулю двенадцать к двенадцати отсчета на выходе счетчика 50 адресов для того, чтобы осуществить генерацию двенадцати адресов для считывания двенадцати символов данных из первого устройства 32 памяти. Когда отсчет сегмента равен двум, а отсчет группы принимает значения от двух до шестидесяти восьми, то генератор смещений выдает на выходе смещение, равное четырем, которое по закону пересчета по модулю двенадцать прибавляют в сумматоре 54 по модулю двенадцать к наборам из двенадцати отчетов на выходе счетчика 50 адресов для того, чтобы осуществить генерацию соответствующих наборов из двенадцати адресов для считывания из первого устройства 32 памяти соответствующих наборов из двенадцати символов данных.

Когда отсчет сегмента равен трем, а отсчет группы равен нулю (то есть, это первая группа из двенадцати символов данных в четвертом сегменте каждого набора из четырех сегментов), то генератор 52 смещений выдает на выходе смещение, равное четырем, которое по закону пересчета по модулю двенадцать прибавляют в сумматоре 54 по модулю двенадцать к двенадцати отсчетам на выходе счетчика 50 адресов для того, чтобы осуществить генерацию двенадцати адресов для считывания двенадцати символов данных из первого устройства 32 памяти. Когда отсчет сегмента равен трем, а отсчет группы принимает значения от единицы до шестидесяти восьми, генератор смещений выдает на выходе смещение, равное нулю, которое прибавляют в сумматоре 54 по модулю двенадцать к наборам из двенадцати отчетов на выходе счетчика 50 адресов для того, чтобы осуществить генерацию соответствующих наборов из двенадцати адресов для считывания из первого устройства 32 памяти соответствующих наборов из двенадцати символов данных.

На фиг. 7 изображен пример того, как генератор 36 адресов функционирует во взаимодействии с первым устройством 32 памяти для осуществления обращения циклического сдвига данных из демодулятора 30, имеющих циклический сдвиг и перемежение. Когда данные в последней группе нулевого сегмента сохранены в первом устройстве 32 памяти, то эти данные сохраняют в ячейках памяти первого устройства 32 памяти в таком порядке данных, который показан в строке 60. Эти данные не имеют циклического сдвига. Строка 62 содержит первую группу данных первого сегмента, прием которого в настоящее время осуществляет демодулятор 30. Эти данные имеют циклический сдвиг на восемь, что показано в строке 62. Поскольку в этот момент времени отсчет сегмента равен единице, а отсчет группы равен нулю, то смещение, которое генератор 52 смещений направляет к сумматору 54 по модулю двенадцать, равно нулю. Соответственно и адреса, создаваемые сумматором 54 по модулю двенадцать, имеют ту же последовательность, что и выходные отсчеты, которые поступают из счетчика 50 адресов.

Таким образом, для того чтобы осуществить считывание символа данных А строки 60 из нулевой ячейки памяти первого устройства 32 памяти и запись символа данных Е из строки 62 в нулевую ячейку памяти первого устройства 32 памяти, сумматор 54 по модулю двенадцать подает в устройство 32 памяти адрес, равный нулю. Затем для того чтобы считать символ данных В строки 60 из первой ячейки памяти первого устройства 32 памяти и записать символ данных F из строки 62 в первую ячейку памяти первого устройства 32 памяти сумматор 54 по модулю двенадцать подает в устройство 32 памяти адрес, равный единице. Адреса, которые подает сумматор 54 по модулю двенадцать, последовательно увеличивают до одиннадцати так, чтобы символы данных строки 60 были считаны из первого устройства 32 памяти и заменены соответствующими символами данных из строки 62. Следовательно, строка 64 указывает содержимое первого устройства 32 памяти в тот момент, когда в первое устройство 32 памяти записана строка 62.

В этот момент отсчет сегмента равен единице, а отсчет группы увеличивается до единицы, и демодулятор 30 осуществляет прием следующей группы символов данных, показанных в строке 66. Когда эти данные приняты, генератор 52 смещений генерирует смещение, равное восьми, которое подают на сумматор 54 по модулю двенадцать. Соответственно для того чтобы осуществить генерацию адреса, равного восьми, сумматор 54 по модулю двенадцать прибавляет смещение восемь к первому, равному нулю, отсчету на выходе счетчика 50 адресов. В ответ на адрес, равный восьми, осуществляют считывание символа данных А, хранящегося в восьмой ячейке памяти первого устройства 32 памяти (см. строку 64), и заменяют его первым полученным символом данных первой группы, то есть, символом данных Е из строки 66. Подобным образом, когда адрес равен девяти (смещение, равное восьми, плюс отсчет, равный единице), то считывают символ данных В и заменяют его символом данных F, когда адрес равен десяти (смещение, равное восьми, плюс отсчет, равный двум), то считывают символ данных С и заменяют его символом данных G, когда адрес равен одиннадцати (смещение, равное восьми, плюс отсчет, равный трем), то считывают символ данных D и заменяют его символом данных Н, когда адрес равен нулю (смещение, равное восьми, плюс отсчет, равный четырем, что после операции по модулю двенадцать дает адрес, равный нулю), то считывают символ данных Е и заменяют его символом данных I, и так далее, так что в строке 68 из фиг. 7 указаны символы данных, хранящиеся теперь в ячейках памяти с нулевой по одиннадцатую первого устройства 32 памяти.

В строке 70 показана следующая принятая группа данных, то есть, когда отсчет сегмента равен единице, а отсчет группы равен двум. Когда отсчет сегмента равен единице, а отсчет группы равен двум, то генератор 52 смещений генерирует смещение, равное четырем. Для того, чтобы осуществить генерацию адресов для первого устройства 32 памяти, сумматор 54 по модулю двенадцать прибавляет это смещение, равное четырем, к значениям выходных отчетов, которые поступают из счетчика 50 адресов. Когда данные в строке 70 приняты, то для того, чтобы осуществить генерацию адреса, равного четырем, сумматор 54 по модулю двенадцать прибавляет смещение, равное четырем, к первому, равному нулю, отсчету на выходе счетчика 50 адресов. В ответ на адрес, равный четырем, считывают символ данных А, хранящийся в четвертой ячейке памяти первого устройства 32 памяти (см. строку 68) и заменяют его первым полученным символом данных второй группы, то есть, символом данных Е из строки 70. Подобным образом, когда адрес равен пяти (смещение, равное четырем, плюс отсчет, равный единице), то считывают символ данных В и заменяют его символом данных F, когда адрес равен шести (смещение, равное четырем, плюс отсчет, равный двум), то считывают символ данных С и заменяют его символом данных G, когда адрес равен семи (смещение, равное четырем, плюс отсчет, равный трем), то считывают символ данных D и заменяют его символом данных Н, когда адрес равен восьми (начальное число четыре плюс отсчет, равный четырем), то считывают символ данных Е и заменяют его символом данных I, и так далее, так что в строке 72 из фиг. 7 указаны символы данных, хранящиеся теперь в ячейках памяти с нулевой по одиннадцатую первого устройства 32 памяти. Следует отметить, что, когда отсчет на выходе счетчика 50 адресов достигает восьми, сумматор 54 по модулю двенадцать выдает первому устройству 32 памяти адрес, равный нулю (отсчет, равный восьми, плюс смещение, равное четырем, с последующей операцией по модулю двенадцать).

Строка 74 показывает, что данные первого сегмента третьей группы не имеют циклического сдвига. Таким образом, при нулевом смещении содержимое первого устройства 32 памяти, которое показано в строке 72, заменяют полученными символами данных, показанными в строке 74 так, чтобы содержимое устройства 32 памяти, показанное в строке 72 после первого сегмента, являющееся данными третьей группы, было полностью сохранено в первом устройстве 32 памяти.

При считывании данных из первого устройства 32 памяти данные имеют обращенный циклический сдвиг, но все еще сохраняют перемежение. Для того, чтобы осуществить обращенное перемежение этих данных, уже имеющих обращенный циклический сдвиг, но сохраняющих перемежение, производят обработку этих имеющих обращенный циклический сдвиг, но сохраняющих перемежение данных посредством второго устройства 38 памяти и второго генератора 40 адресов. Поскольку символы данных в каждом байте данных перемежаются с соответствующими символами данных в одиннадцати других байтах данных, и поскольку на байт приходится четыре символа, то второе устройство 38 памяти является памятью на 48 символов.

Первый вариант осуществления генератора 40 адресов показан на фиг. 8. Этот генератор адресов включает в себя счетчик 80 с делением на сорок восемь, который выдает какой-либо выходной сигнал при каждом сорок восьмом отсчете тактового сигнала символа. Выходной сигнал переноса от счетчика 80 с делением на сорок восемь подают на генератор 82 начальных чисел, а генератор 82 начальных чисел подает начальное число на первый вход сумматора 84. Значение на выходе сумматора 84 подают на устройство 86 пересчета по модулю сорок семь, которое осуществляет пересчет по модулю сорок семь значения на выходе сумматора 84. Выход устройства 86 пересчета по модулю сорок семь соединен с регистром-фиксатором 88, управляемым тактовым сигналом символа, который фиксирует значение на выходе устройства 86 пересчета по модулю сорок семь. На выходе регистра-фиксатора 88 получают адрес, который подают на второе устройство 38 памяти, а также по цепи обратной связи подают на второй вход сумматора 84.

Второе устройство 38 памяти должно иметь количество ячеек памяти, достаточное для хранения сорока восьми символов. Хотя второе устройство 38 памяти является однострочной матрицей памяти, имеющей ячейки памяти с адресами от 0 до 47, ее можно рассматривать как прямоугольную матрицу с R=12 строками и С= 4 столбцами. Отсюда, N=R•С=48. На фиг. 9 показаны адреса второго устройства 38 памяти при рассмотрении с этой точки зрения. Если Хn - последовательность входных символов (где n=0...47), и если Mi(n) представляет собой распределение входных символов Хn по ячейкам памяти во втором устройстве 38 памяти, то Mi(n) является тем адресом во втором устройстве 38 памяти, где должен быть сохранен соответствующий символ Хn (Распределение Mi(n) имеет нижний индекс i, так как существует несколько карт распределений, то есть второй генератор 40 адресов обеспечивает несколько последовательностей адресов). Если начальная последовательность распределения М0(n) выбрана так, что М0(n)= n для n=0,1,2...(N-1), то каждый входной символ Хn первого блока из сорока восьми символов хранится в ячейке памяти n. Это может быть наглядно показано путем наложения фиг. 1 на верхнюю часть фиг. 9.

Для осуществления обращенного перемежения этого блока данных он должен быть считан из второго устройства 38 памяти в порядке чередования, отличающемся от того порядка чередования, в котором он был записан во второе устройство 38 памяти. Таким образом, при одновременном приеме символа из следующего блока из сорока восьми символов осуществляют считывание символов первого блока из второго устройства 38 памяти и замену их соответствующими символами, только что принятыми из второго блока. Для осуществления обращенного перемежения первого блока Mi(n) должно быть равно 0, 12, 24, 36, 1, 13...... . ..... 35, 47. Обращенное перемежение первого блока символов в соответствии с этими адресами приводит к тому, что запись второго блока во второе устройство 38 памяти осуществляют в порядке, отличном от того, в котором был записан первый блок. Следовательно, чтобы осуществить обращенное перемежение второго блока (при одновременной записи третьего блока во второе устройство 38 памяти), должна быть создана новая адресная последовательность М2(n), которая отличается от Mi(n). Для осуществления непрерывного приема и обращенного перемежения блоков символов этот процесс продолжают для всего ряда адресных последовательностей.

Если первая последовательность распределения М0(n)=0,1,2,3,4......... 47, то M1(n) может быть записана в виде:

M1(n)=M0((n-R)mod(N-1)) для n= 0,... N-1 (1)

Это выражение возникает потому, что глубина перемежения равна R. В функции распределения соседние горизонтальные символы отделены друг от друга на R единиц. Модульная часть осуществляет правильное управление циклическим возвратом конца строки и приводит к правильному смещению при последовательном изменении индекса в функции распределения.

Подобным образом может быть осуществлена генерация распределения с любой последовательностью по предшествующему распределению, согласно следующему уравнению:

Mi(n)=Mi-1((n-R)mod(N-l)) для n=0,1,2,... N-1 (2)

Соответствующим образом, используя индуктивный метод, можно обобщить эту функцию распределения и записать выражение для n-го элемента i-той последовательности с использованием начальной (i=0) последовательности в следующем виде:

Mi(n)=M0((n•Ri)mod(N-l)) для n= 0,1,2,... N-1 (3)

Если сделано предположение, что начальной последовательностью является Мg(n)=n, то уравнение (3) можно упростить следующим образом:

Mi(n)=(n•Ri)mod(N-l)) для n= 0,1,2,... N-1 (4)

Уравнение (4) приводит к следующему выражению для вычисления n-го элемента любой последовательности по n-му элементу предшествующей последовательности:

Mi(n)=(Mi+1(n)-R)mod(N-l)) для п=0,1,2,... N-1 (5)

Уравнение (4) описывает все адресные последовательности, которые необходимы для обращенного перемежения входных данных от одного блока к следующему. Существует конечное число различных адресных последовательностей, которые дает уравнение (4) до того, как вернется к начальной последовательности. Это конечное число последовательностей зависит от значений R и С (или соответственно значений R и N). Следовательно, существует L единственных в своем роде распределений, где L является наименьшим из чисел, для которых:

(RL)mod(N-l)=1 для L≠0 (6)

В конечном счете, выражение для зависимости n-го элемента любой i-той последовательности от (n-l)-ro элемента той же самой последовательности может быть определено следующим образом:

Mi(n)=0 для n=0

Mi(n)=(Mi(n-1)+Ri)mod(N-l) для n= 0,1,2,...,N-1 (7)

Если R равно 12 (как в примере, показанном на фиг. 1), то уравнению (6) удовлетворяет значение L, равное 23. То есть, уравнение (4) дает 23 единственные в своем роде последовательности, которые повторяются, начиная с L=24. Следовательно, для показанной на фиг. 1 матрицы данных существуют 23 последовательности, необходимые для обращенного перемежения данных с перемежением, описание которых приведено выше для фиг. 1. На фиг. 10 изображены двадцать три последовательности и соответствующие им начальные числа.

Для генерации требуемых повторяющихся последовательностей адресов генератор 40 адресов функционирует в соответствии с уравнением (7). Для того, чтобы осуществить генерацию начальных чисел для каждой последовательности адресов, также необходим генератор начальных чисел, который реализует уравнение (6).

Начальные числа, вырабатываемые генератором 82 начальных чисел, заданы уравнением (6), в котором в приведенном в настоящей заявке на изобретение примере L изменяется от 0 до 22. Эти начальные числа состоят из следующих чисел: 1, 12, 3, 36, 9, 14, 27, 42, 34, 32, 8, 2, 24, 6, 25, 18, 28, 7, 37, 21, 17, 16 и 4. При каждом сорок восьмом тактовом импульсе символа генератор 82 начальных чисел подает соответствующее одно из этих начальных чисел на сумматор 84, который при каждом тактовом импульсе символа прибавляет начальное число к значению на выходе регистра-фиксатора 88. Устройство 86 пересчета по модулю сорок семь выполняет операцию пересчета по модулю сорок семь (если > 47, то вычитают 47) значения на выходе сумматора 84 и подает результирующее значение на регистр-фиксатор 88. Регистр-фиксатор 88 фиксирует этот результат и подает этот фиксированный результат в качестве адреса на второе устройство 38 памяти. Так создают единственную последовательность из сорока восьми адресов для каждого начального числа, выработанного генератором 82 начальных чисел.

Поскольку обработка, производимая в первом устройстве 32 памяти, занимает ровно 12 тактовых импульсом символа, то генератор 40 адресов приводят в действие сигналом СБРОС 2 и тактовым импульсом символа. Так как символы, которые проходят через первое устройство 32 памяти, имеют задержку на двенадцать тактов символа, то при выводе из первого устройства 32 памяти сигнал СБРОС 2 расположен в нужном месте вместе с первым символом кадра. Во временных диаграммах на фиг. 11А и фиг. 11Б сделано предположение, что прием сигнала 8 VSB осуществлен недавно, так что начальное значение счетчика 80, выходной сигнал переноса от счетчика 80, значения генератора 82 начальных чисел и регистра-фиксатора 88 неизвестны. Сигнал СБРОС 2 и первый тактовый импульс символа вызывают инициализацию счетчика 80 в нулевое состояние, что в свою очередь обеспечивает низкий уровень сигнала переноса на выходе. Сигнал СБРОС 2 также вызывает вывод первого (1) начального числа из генератора 82 начальных чисел. Сигнал СБРОС 2 и первый тактовый импульс символа также вызывают синхронную очистку и обнуление значения на выходе регистра-фиксатора 88. Последующие тактовые импульсы символа вызывают приращение содержимого счетчика 80.

Когда отсчет счетчика 80 достигает значения, равного 47, он выдает сигнал переноса, который в свою очередь вызывает выдачу генератором начальных чисел 82 следующего начального числа последовательности (12). Этот сигнал переноса также вызывает синхронную очистку регистра-фиксатора 88 при следующем тактовом импульсе символа. Таким образом, сигналы переноса из счетчика 80 приводят к тому, что генератор 82 начальных чисел многократно циклически повторяет свою последовательность из 23 начальных чисел. Следовательно, каждое начальное число имеет длительность, равную 48-ми тактам символов. Поэтому полная последовательность из 23 начальных чисел включает в себя 23x48= 1104 символа. Поскольку кадр имеет 258336 символов данных, то в каждом кадре последовательность из 23 начальных чисел встречается точно 234 раза (234x1104=258336). Следовательно, начало нового кадра (обозначенное на временной диаграмме на фиг. 11А и 11Б вторым импульсом СБРОС 2 (#2)) всегда совпадает с первым начальным числом (1). Это совпадение является преимуществом, так как это позволяет использовать первый сигнал СБРОС 2 (который, как было объяснено ранее, получен из сигнала синхронизации кадра) после приема сигнала 8 VSB для того, чтобы инициализировать генератор 82 начальных чисел для вывода значения 1, не беспокоясь о влиянии последующих сигналов СБРОС 2 (по одному на кадр), так как они будут всегда совпадать по времени с тем моментом, когда генератор начальных чисел 82 должен иметь на выходе значение 1.

Нельзя нарушать последовательность начальных чисел, когда уже произведена ее инициализация после получения сигнала. Это необходимо для правильной непрерывной работы устройства обращенного перемежения. На временной диаграмме также показан выходной сигнал регистра-фиксатора 88, соответствующий требуемому Mi(n). Показаны части Mo(n), M1(n), и М2(n), которые появляются после первого импульса СБРОС 2 (#1). Предполагают, что последовательности циклически повторяются для всех Mi(n) много раз до тех пор, пока, как показано, в конце первого кадра не появится М22(n) непосредственно перед вторым импульсом СБРОС 2 (#2). Как и ожидалось, второй кадр начинается с Мо(n).

Операция обращенного перемежения подобна операции обращения циклического сдвига, объяснение которой было приведено со ссылкой на чертежи фиг. 6 и 7. То есть, когда символ данных считан из ячейки памяти второго устройства 38 памяти, которая определена вторым генератором 40 адресов, то этот символ данных заменяют следующим символом данных, который получен из первого устройства 32 памяти Соответственно, когда тактовые импульсы символа приводят к тому, что содержимое счетчика 80 с делением на 48 достигает значения отсчета 47, счетчик 80 выдает сигнал переноса, который подают на генератор 82 начальных чисел и на регистр-фиксатор 88 (через логический элемент 89 ИЛИ). Этот выходной сигнал переноса вызывает подачу нового начального числа из генератора 82 начальных чисел в сумматор 84. Этот выходной сигнал переноса также осуществляет сброс значения на выходе регистра-фиксатора 88 в нулевое состояние (в следующем такте символа). Значение с выхода регистра-фиксатора также подают обратно на второй вход сумматора 84.

Для каждой из 23-х последовательностей, показанных на фиг. 10, сумматор 84 прибавляет равное нулю значение на выходе регистра-фиксатора 88 (который представляет собой первый адрес в каждой последовательности) к начальному числу, которое подают с генератора 82 начальных чисел. Это значение на выходе сумматора 84 контролируют устройством пересчета по модулю сорок семь, а результат подают на вход регистра-фиксатора 88. Следующий тактовый импульс символа приводит к тому, что регистр-фиксатор 88 подает это результирующее значение из устройства 86 пересчета по модулю сорок семь во второе устройство 38 памяти. Это значение на выходе регистра-фиксатора 88 снова подают обратно на сумматор 84 и прибавляют его к начальному числу от генератора 82 начальных чисел. Таким образом, для создания соответствующей последовательности адресов, которую подают во второе устройство памяти 38, начальное число из генератора начальных чисел 82 рекурсивно прибавляют к нему же по модулю сорок семь.

Каждая такая последовательность адресов задана уравнением (7). При каждом циклическом сдвиге этих двадцати трех последовательностей первая последовательность всегда упорядочена от нуля до 47. К тому же, начальное число для этой первой последовательности, которое подает генератор 82 начальных чисел, равно единице, что определяется уравнением (6).

На фиг. 12 изображен более подробный вид первого варианта осуществления генератора 82 начальных чисел. Генератор 82 начальных чисел включает в себя умножитель 92, устройство 94 пересчета по модулю сорок семь и регистр-фиксатор 96.

Умножитель 92 умножает значение на выходе регистра-фиксатора 96 на двенадцать, устройство 94 пересчета по модулю сорок семь выполняет операцию пересчета по модулю сорок семь значения на выходе сумматора 92, а регистр-фиксатор 96 фиксирует значение на выходе устройства 94 пересчета по модулю сорок семь.

Когда контроллер 34 выдает сигнал СБРОС 2, то осуществляют сброс регистра-фиксатора 96 так, чтобы значение на его выходе стало равным единице. Эту единицу подают в качестве начального числа на сумматор 84. Эту единицу также умножают на двенадцать посредством умножителя 92, а результат обрабатывают устройством 94 пересчета по модулю сорок семь. Значение с выхода устройства 94 пересчета по модулю сорок семь подают на регистр-фиксатор 96, который фиксирует это выходное значение на протяжении всего времени до получения следующего выходного сигнала переноса из счетчика 80 с делением на сорок восемь. После получения этого выходного сигнала переноса значение с выхода регистра-фиксатора 96,

равное двенадцати, подают обратно на умножитель 92, который умножает это значение, равное двенадцати, на двенадцать и вырабатывает на выходе значение, равное 144, которое обрабатывают устройством 94 пересчета по модулю сорок семь. Значение с выхода устройства 94 пересчета по модулю сорок семь (три) подают на регистр-фиксатор 96, который фиксирует это выходное значение на протяжении всего времени до получения следующего выходного сигнала переноса из счетчика 80 с делением на сорок восемь. После получения этого выходного сигнала переноса значение на выходе регистра-фиксатора 96, равное трем, подают обратно на умножитель 92, который умножает это значение три на двенадцать, получая значение на выходе, равное тридцати шести, которое обрабатывают устройством 94 пересчета по модулю сорок семь. Значение с выхода устройства 94 пересчета по модулю сорок семь (то есть тридцать шесть) подают на регистр-фиксатор 96, который фиксирует это выходное значение на протяжении всего времени до получения следующего выходного сигнала переноса из счетчика 80 с делением на сорок восемь. После получения этого выходного сигнала переноса значение на выходе регистра-фиксатора 96, равное тридцати шести, подают по цепи обратной связи на умножитель 92, который умножает это значение тридцать шесть на двенадцать, получая на выходе значение, равное 432, и так далее. Таким образом, генератор 82 начальных чисел вырабатывает двадцать три описанных выше начальных числа.

На Фиг. 13 изображен более подробный вид второго варианта осуществления генератора 82 начальных чисел. Этот генератор 82 начальных чисел включает в себя устройство 98 умножения на двенадцать и пересчета по модулю сорок семь и регистр-фиксатор 100. Устройство 98 умножения на двенадцать и пересчета по модулю сорок семь, показанное более подробно на Фиг. 14, включает в себя сумматор 102, который после того, как в устройстве 104 были отброшены два младших бита, прибавляет четыре старших бита значения на выходе регистра-фиксатора 100 к коэффициенту коррекции логического устройства 106 коррекции по модулю сорок семь, которое более подробно показано на Фиг. 15.

Когда контроллер 34 выдает сигнал СБРОС 2, то осуществляют сброс регистра-фиксатора 100 так, чтобы его выходное значение стало равным единице. Эту единицу подают в качестве начального числа на сумматор 84. Эту единицу также умножают на двенадцать, и результат обрабатывают по модулю сорок семь в устройстве 98 умножения на двенадцать и пересчета по модулю сорок семь. Значение с выхода устройства 98 умножения на двенадцать и пересчета по модулю сорок семь подают на регистр-фиксатор 100, который фиксирует это выходное значение на протяжении всего времени до получения следующего сигнала переноса на выходе счетчика 80 с делением на сорок восемь. Значение с выхода регистра-фиксатора, равное двенадцати, подают по цепи обратной связи на умножитель 100, который умножает это значение, равное двенадцати, на двенадцать, а результат (144) обрабатывают по модулю сорок семь в устройстве 98 умножения на двенадцать и пересчета по модулю сорок семь, получая на выходе значение три. Значение на выходе устройства 98 умножения на двенадцать и пересчета по модулю сорок семь, равное трем, подают на регистр-фиксатор 104, который фиксирует это выходное значение на протяжении всего времени до получения следующего выходного сигнала переноса из счетчика 80 с делением на сорок восемь, и так далее. Таким образом, генератор 82 начальных чисел вырабатывает двадцать три начальных числа, описанных выше.

Устройство 98 умножения на двенадцать и пересчета по модулю сорок семь более подробно показано на Фиг. 14. Когда значение на выходе регистра-фиксатора 100 равно единице (то есть, цифровое значение равно 000001), два младших бита (01) подают в логическое устройство 106 коррекции по модулю сорок семь, которое дает на выходе значение двенадцать. Сумматор 102 прибавляет выходное значение, равное двенадцати, к четырем старшим битам (0000) значения на выходе регистра-фиксатора 100, а результирующее значение двенадцать подают на регистр-фиксатор 102. Регистр-фиксатор 102 фиксирует значение двенадцать на своем выходе после получения следующего выходного сигнала переноса из счетчика 80 с делением на сорок восемь. Когда значение на выходе регистра-фиксатора 100 равно двенадцати (то есть цифровое значение равно 001100), два младших бита (00) подают на логическое устройство 106 коррекции по модулю сорок семь, которое даст на выходе значение ноль. Это выходное значение, равное нулю, сумматор 102 прибавляет к четырем старшим битам (0011) значения на выходе регистра-фиксатора 100, и результирующее значение три подают на регистр-фиксатор 102. Регистр-фиксатор 100 фиксирует это значение три на своем выходе после получения следующего выходного сигнала переноса из счетчика 80 с делением на сорок восемь, и так далее.

Логическое устройство 106 коррекции по модулю сорок семь более подробно показано на Фиг. 15 и включает в себя логическое устройство 108. Два младших разряда на выходе логического устройства 108, ВЫХ 0 (OUT 0) и ВЫХ 1 (OUT 1) всегда равны нулю. Управление четырьмя старшими разрядами на выходе логического устройства 108, ВЫХ 2-ВЫХ 5 (OUT 2-OUT 5) осуществляют двумя младшими битами с выхода регистра-фиксатора 100, ВХ 0 (IN 0)и BX1(IN 1).

Второй вариант осуществления второго генератора 40 адресов, основанный на уравнении (4), показан на Фиг. 16. Этот второй вариант осуществления включает в себя счетчик 112, который отсчитывает тактовые импульсы символа, каждый выходной отсчет которого подают на умножитель 114. Выходной сигнал переноса счетчика 112 подают на генератор 116 начальных чисел, который может представлять собой либо конечный автомат, либо оперативную память со случайной выборкой, либо подобен генератору 82 начальных чисел. Для того, чтобы при каждом переключении обеспечить подачу соответствующих начальных чисел, определяемых уравнением (6), генератор начальных чисел 116 переключается по двадцати трем состояниям посредством выходного сигнала переноса от счетчика 112. Умножитель 114 умножает отсчет на выходе счетчика 112 на начальное число, которое выдает генератор 116 начальных чисел, и подает результирующее значение в устройство 118 пересчета по модулю сорок семь. Значение с выхода устройства пересчета по модулю сорок семь подают на вход регистра-фиксатора 120. Посредством выходного сигнала переноса из счетчика 112 осуществляют сброс и обнуление выходного значения регистра-фиксатора 120. Таким образом, в начале каждой последовательности адресов выходное значение регистра-фиксатора 120, равное нулю, которое всегда является первым адресом каждой последовательности адресов. В конце каждой последовательности адресов (то есть отсчет равен сорока восьми) осуществляют переключение генератора 116 начальных чисел так, чтобы он подавал на умножитель 114 новое начальное число.

Выше были рассмотрены некоторые видоизменения настоящего изобретения. Специалистами в области техники, относящейся к данному изобретению, могут быть придуманы и другие видоизменения. Например, хотя описание настоящего изобретения было произведено конкретно для двух битных символов данных, следует понимать, что настоящее изобретение применимо и для других элементов данных. Настоящее изобретение также может быть использовано для различных компоновок кадра данных и различных протоколов циклического сдвига и/или перемежения.

Следовательно, описание настоящего изобретения должно рассматриваться только в качестве пояснительного материала и имеет цель сообщить специалистам в данной области техники о наилучшем способе осуществления изобретения. Его части могут быть существенно изменены без отступления от сущности изобретения, а исключительные права на использование всех видоизменений, которые подпадают под объем приложенной формулы изобретения, сохраняются.

Изобретение относится к устройству обращения циклического сдвига и/или обращенного перемежения данных. Техническим результатом является возможность осуществления обращенного перемежения данных, уже имеющих обращенный циклический сдвиг. Устройство для переупорядочения поблочно упорядоченных первой и второй групп элементов данных из первой упорядоченности блоков данных ко второй упорядоченности блоков данных содержит устройство памяти, включающее множество ячеек памяти, и генератор адресов. 16 з.п. ф-лы, 16 ил.

(RL) mod (mD-1) = 1,

где L= 0,1,2, . . . до тех пор, пока начальные числа не начинают повторяться при Lmax;

R= D,

и в котором последовательности адресов заданы следующим уравнением:

M1(n)= 0 для n= 0, Mi(n)= (М1(n-1)+Ri)mоd(mD-1) для n= 0,1, 2, . . . , mD-1, где i изменяется от 0 до Lmax-1.

(RL)mod(mD-l) = 1,

где L= 0,1,2, . . . до тех пор, пока начальные числа не начинают повторяться при Lmax;

R= D,

и в котором последовательности адресов заданы следующим уравнением:

Mi(n) = (n Ri) mod (N-1) для n= 0,1,2, . . . , N-1,

где i изменяется от 0 до Lmax - 1,4,

в котором единственный генератор адресов включает в себя средство отсчета адреса, выполненное с возможностью осуществления отсчета от 0 до D-1, для создания соответствующего выходного значения отсчета, имеющего значение от 0 до D-1, и для сброса после того, как значение отсчета достигнет D-1, средство генерации смещения, выполненное с возможностью генерации смещения, в котором смещение зависит от величины циклического сдвига D элементов данных, и средство суммирования, выполненное с возможностью суммирования смещения и выходного значения отсчета для осуществления генерации адреса.

| US 5369652 А, 29.11.1994 | |||

| Устройство для сдвига информации | 1988 |

|

SU1697119A1 |

| RU 94014268 А1, 20.06.1996 | |||

| Система упорядочения информации | 1975 |

|

SU608161A1 |

| Прибор для очистки паром от сажи дымогарных трубок в паровозных котлах | 1913 |

|

SU95A1 |

| US 5537420 A, 04.05.1995. | |||

Авторы

Даты

2002-09-20—Публикация

1997-07-18—Подача