Изобретение относится к радиоэлектронике и может быть использовано в различных вычислительных устройствах при обработке информации в разнообразных радиолокационных, радионавигационных и вычислительных системах как наземного, так и бортового базирования.

Наиболее близким к предлагаемому является управляющий страничный автомат с "жесткой" логикой [1], содержащий блок формирования сигналов микроопераций, каждый выход которого связан с соответствующим входом блока формирователей сигналов микроопераций. Основными недостатками данного устройства являются относительно невысокие быстродействие, надежность и интеграция, а также невозможность организации страничных циклов управляющих сигналов.

Техническим результатом является повышение быстродействия, надежности и интеграции устройства, а также расширение его функциональных возможностей за счет выполнения страничных циклов управляющих сигналов.

Это достигается тем, что в управляющий страничный автомат с "жесткой" логикой, содержащий блок формирования сигналов микроопераций, каждый выход которого связан с соответствующим входом блока формирователей сигналов микроопераций, введены блок регистров кодов операций, блок дешифраторов кодов операций, блок тактовых дешифраторов операций, первый и второй логические блоки, блок тактовых дешифраторов циклов, блок демультиплексоров, блок счетчиков циклов, блок формирования тактовых сигналов микроопераций, блок формирователей тактовых сигналов микроопераций, причем информационный вход и управляющий вход блока регистров кодов операций являются соответствующими входами управляющего страничного автомата с "жесткой" логикой, каждый выход блока регистров кодов операций через блок дешифраторов кодов операций связан с соответствующим входом блока тактовых дешифраторов операций, (1...(i-1))-е и ((j+1)...m)-е (где i < j, a i, j = 1, 2, 3,...m, а m - максимальное число тактов в операции) группы выходов которого через блок формирования сигналов микроопераций связаны с соответствующими группами входов блока формирователей сигналов микроопераций, соответствующие группы выходов которого являются соответственно первой и второй страницами выходов управляющего страничного автомата с "жесткой" логикой, третьей страницей выходов которого является группа выходов блока формирователей тактовых сигналов микроопераций, каждая группа входов которого через блок формирователей тактовых сигналов микроопераций связана с соответствующей группой тактовых выходов блока тактовых дешифраторов циклов, каждая группа входов которого соответственно связана с соответствующей группой выходов первого логического блока, страница входов которого соответственно связана со страницей (i...j)-х групп выходов блока тактовых дешифраторов операций, каждая группа цикловых выходов блока тактовых дешифраторов циклов соответственно связана с соответствующей группой входов блока демультиплексоров, первая страница выходов которого соответственно связана со страницей входов блока счетчиков циклов, первая страница выходов которого соответственно связана с первой страницей входов второго логического блока, вторая страница входов которого соответственно связана со второй страницей выходов блока демультиплексоров, страница выходов второго логического блока соответственно связана со второй страницей входов первого логического блока, вторая страница выходов блока счетчиков циклов соответственно связана со страницей входов обратной связи циклов блока тактовых дешифраторов операций.

Блок тактовых дешифраторов операций выполнен в виде трех узлов сдвиговых регистров, причем каждая группа входов первого узла сдвиговых регистров является соответствующей группой входов блока тактовых дешифраторов операций, (1. . . (i-1))-ми группами выходов которого являются соответствующие группы выходов первого узла сдвиговых регистров, страница (i...j)-х групп выходов которого соответственно связана с соответствующей страницей входов второго узла сдвиговых регистров, группы выходов которого являются (i...j)-ми группами выходов блока тактовых дешифраторов операций, ((j+1). ..m)-ми группами выходов которого являются соответствующие группы выходов третьего узла сдвиговых регистров, каждая группа входов которого является соответствующей группой входов обратной связи циклов блока тактовых дешифраторов операций.

Блок тактовых дешифраторов циклов выполнен в виде узла сдвиговых регистров.

Блок счетчиков циклов выполнен в виде узла сдвиговых регистров.

Первый логический блок предназначен для выполнения страничной булевой функции ИЛИ, второй логический блок предназначен для выполнения страничной булевой функции И.

Данная совокупность существенных признаков и связей между ними позволяет получить устройство, обладающее повышенным быстродействием, надежностью и интеграцией, а также позволяет расширить его функциональные возможности за счет выполнения страничных программных циклов.

Сущность изобретения заключается в том, что на основе оригинального алгоритма выполнения математических операций над страницами операндов с фиксированной точкой предложена структура управляющего страничного автомата с "жесткой" логикой, в котором использованы оригинальные способы и схемы построения как отдельных блоков устройства, так и организации страничных циклов управляющих сигналов на основе оптических, оптоэлектронных и/или электронных методов обработки сигналов, за счет чего и получены вышеуказанные достоинства устройства.

Таким образом, предложенный управляющий страничный автомат с "жесткой" логикой обладает свойствами, не присущими известным устройствам. Это объясняется новой совокупностью существенных признаков и новыми связями, изложенными выше.

Сравнение предлагаемого устройства с известными свидетельствует о соответствии его критерию "новизна", а отсутствие в аналогах отличительных признаков предлагаемого устройства - о соответствии критерию "изобретательский уровень".

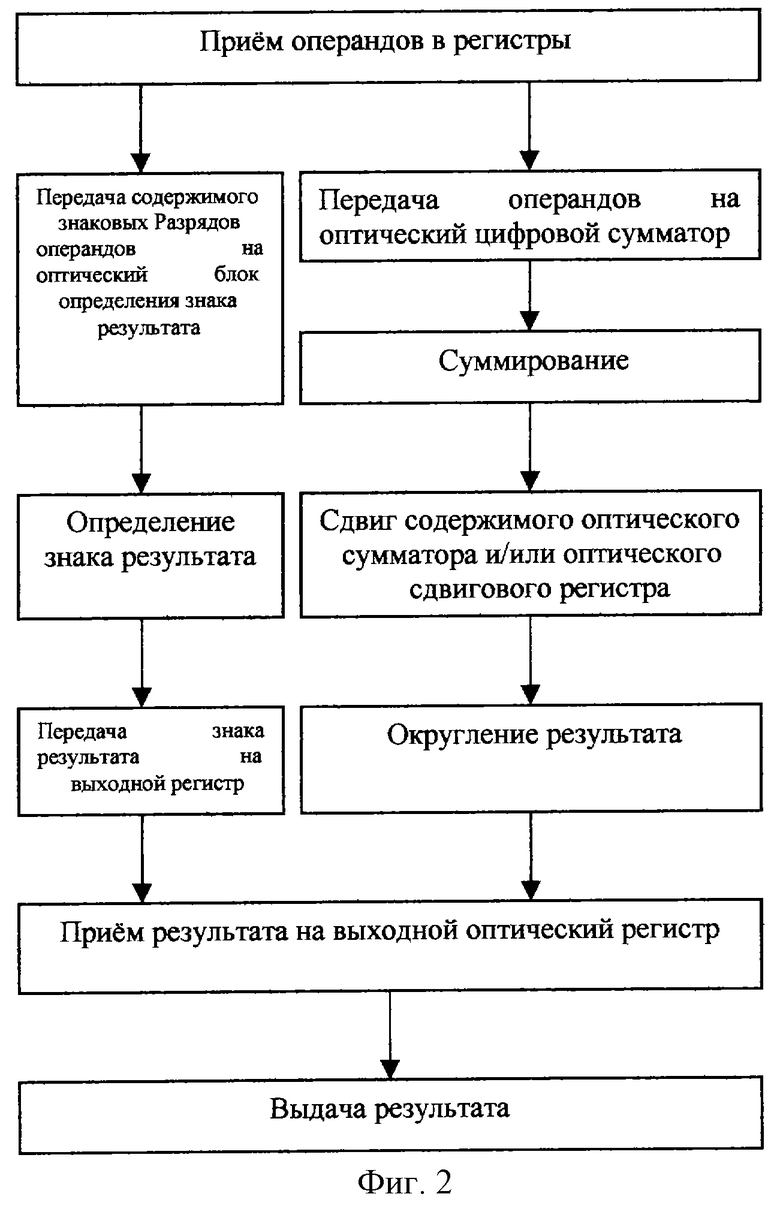

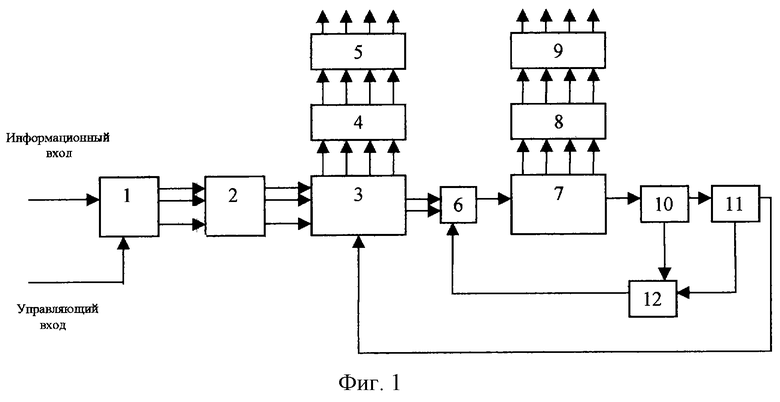

На фиг.1 приведена структурная схема управляющего страничного автомата с "жесткой" логикой, на фиг.2 - блок-схема алгоритма выполнения арифметических операций с фиксированной точкой.

Управляющий страничный автомат с "жесткой" логикой содержит блок регистров кодов операций 1, блок дешифраторов кодов операций 2, блок тактовых дешифраторов операций 3, блок формирования сигналов микроопераций 4, блок формирователей сигналов микроопераций 5, логический блок 6, блок тактовых дешифраторов циклов 7, блок формирования тактовых сигналов микроопераций 8, блок формирователей тактовых сигналов микроопераций 9, блок демультиплексоров 10, блок счетчиков циклов 11, логический блок 12.

Блок регистров кодов операций 1 предназначен для приема, хранения и выдачи страниц кодов операций в виде матриц электрических или оптических сигналов и может иметь электрические и оптические входы/выходы. Блок регистров кодов операций 1 может состоять, например, из последовательно расположенных и связанных матрицы фотоприемников, матрицы электронных регистров и матриц лазерных диодов, причем вход матрицы фотоприемников является оптическим входом блока 1, электрические вход/выход матрицы электронных регистров являются соответственно электрическими входом/выходом блока 1, а оптический выход матрицы лазерных диодов является оптическим выходом блока регистров кодов операций.

Блок дешифраторов кодов операций 2 предназначен для преобразования сигналов каждого кода операции страницы кодов операций, подаваемой на входы блока 2, в сигнал на одном из его выходов. Блок 2 может иметь электронное, оптоэлектронное или оптическое выполнение, например, на основе электронного или оптического дешифратора или оптического разветвителя и оптических фильтров, или на основе дефлектора.

Блок тактовых дешифраторов операций 3 предназначен для преобразования каждого входного сигнала в соответствующий код тактовых сигналов. Блок 3 может иметь электронное, оптоэлектронное или оптическое выполнение, например, на основе электронных шифраторов или оптических разветвителей (демультиплексоров) и оптических фильтров, а также на основе сдвиговых регистров.

Блок формирования сигналов микроопераций 4 предназначен для преобразования каждого входного тактового сигнала в соответствующий код управляющих сигналов микрооперации. Блок 4 может иметь электронное, оптоэлектронное или оптическое выполнение, например, на основе разветвителей, демультиплексоров и фильтров.

Блок формирователей сигналов микроопераций 5 предназначен для формирования управляющих сигналов и может быть выполнен на основе электронных, оптоэлектронных или оптических методов формирования управляющих сигналов.

Логический блок 6 предназначен для выполнения страничных булевых функций (например, функций ИЛИ) и может иметь оптическое выполнение, как это описано, например, в авторских свидетельствах СССР 1394982, 1396827, 2015578, 2015579, 2015580.

Блок тактовых дешифраторов циклов 7 предназначен для преобразования каждого входного сигнала в соответствующую последовательность тактовых сигналов и может иметь электронное, оптоэлектронное или оптическое выполнение, например, на основе сдвиговых регистров или коммутаторов.

Блок формирования тактовых сигналов микроопераций 8 предназначен для преобразования каждого тактового сигнала в соответствующий код управляющих сигналов микроопераций и может иметь электронное, оптоэлектронное или оптическое выполнение, например, на основе разветвителей, демультиплексоров и фильтров.

Блок формирователей тактовых сигналов микроопераций 9 предназначен для формирования управляющих сигналов и может иметь электронное, оптоэлектронное или оптическое выполнение, например, на основе электронных, оптоэлектронных или оптических методов формирования управляющих сигналов.

Блок демультиплексоров 10 предназначен для размножения входных сигналов и может иметь электронное, оптоэлектронное или оптическое выполнение на основе электронной или световодной техники.

Блок счетчиков циклов 11 предназначен для подсчета числа циклов и может быть выполнен, например, на основе электронных, оптоэлектронных или оптических сдвиговых регистров.

Логический блок 12 предназначен для выполнения страничных булевых функций (например, функций И) и может иметь оптическое выполнение, как это описано, например, в авторских свидетельствах СССР 1394982, 1396827, 2015578, 2015579, 2015580.

Управляющий страничный автомат с "жесткой" логикой работает следующим образом (фиг.1).

По команде, поданной на управляющий вход управляющего страничного автомата с "жесткой" логикой, страница кодов операций через его информационный вход записывается в блок регистров кодов операций 1 и храниться на нем до начала вычислений. Эта страница может состоять, например, из v строк (где v = 1, 2, 3,...V, а V - максимальное число групп операционных устройств) и u полей (где n = 1, 2, 3,...U, a U - максимальное число операционных устройств в группе).

Предположим, что управляющий страничный автомат с "жесткой" логикой обеспечивает работу v групп операционных устройств, каждая из которых может содержать любой набор u вычислительных устройств, выполняющих такие арифметические операции над страницами операндов с фиксированной точкой, как умножение, деление, извлечение квадратных корней. Такие устройства описаны, например, в авторских свидетельствах СССР 1367567, 1367753 и в патентах России 2076548, 2079873, 2115950 и 2131617. Алгоритм выполнения арифметических операций в таких устройствах показан на блок-схеме фиг.2.

При поступлении на управляющий вход устройства команды на выполнение операций страница кодов операций из блока регистров кодов операций 1 передается на блок дешифраторов кодов операций 2, который для каждого uv-го кода операции страницы создает единичный сигнал на определенном своем выходе.

Каждый такой сигнал поступает на блок тактовых дешифраторов операций 3, который вырабатывает для него тактовые сигналы, соответствующие uv-му коду операции. Каждый тактовый сигнал данного кода операции поступает на блок формирования сигналов микроопераций 4, который формирует набор логических сигналов, необходимый для выполнения определенной микрооперации в данном такте, а блок формирователей сигналов микроопераций 5 формирует из этих логических сигналов выходные сигналы управляющего страничного автомата с "жесткой" логикой.

При наступлении, например, i-го такта операции, в котором должно быть выполнено n микропрограммных страничных циклов (см. фиг.2), i-й тактовый сигнал поступает через логический блок 6 на блок тактовых дешифраторов циклов 7, создающий последовательность k тактовых единичных сигналов цикла. Каждый k-й тактовый единичный сигнал поступает на вход блока формирования тактовых сигналов микроопераций 8, который создает необходимый набор логических сигналов, необходимый для выполнения данной микрооперации в этом такте, а блок формирователей тактовых сигналов микроопераций 9 формирует соответствующие выходные сигналы управляющего страничного автомата с "жесткой" логикой.

По выполнении k тактов цикла каждый (k+1)-й тактовый сигнал через блок демультиплексоров 10, логический блок 12 и логический блок 6 поступает на вход блока тактовых дешифраторов циклов 7 и осуществляется выполнение следующего цикла.

Одновременно страница сигналов с другого выхода блока демультиплексоров 10 поступает на вход блока счетчиков циклов 11, который с одного выхода выдает страницу сигналов, запирающую логический блок 12, и таким образом прерывается выполнение страничного цикла, а с другого выхода страница сигналов поступает на вход обратной связи циклов блока тактовых дешифраторов операций 3 для вырабатывания дальнейших тактовых сигналов операций. При этом выполнение микропрограммных страничных циклов может происходить вплоть до j-го такта операций. Выполнение страницы операций заканчивается в m-ом такте (где i < j, a i, j = 1, 2, 3,...m, a m - максимальное число тактов в операции).

Использование данного управляющего страничного автомата с "жесткой" логикой в вычислительных устройствах, машинах, системах и комплексах при обработке информации в разнообразных радиолокационных, радионавигационных и других радиоэлектронных системах как наземного, так и бортового базирования позволит увеличить их быстродействие, надежность и компактность.

Литература

1. Б.М. Каган. Электронные вычислительные машины и системы. Москва, Энергоатомиздат, 1991, стр.215-217.

Изобретение относится к радиоэлектронике. Техническим результатом является повышение быстродействия, надежности и интеграции устройства, а также расширение его функциональных возможностей за счет выполнения страничных циклов управляющих сигналов. Для этого управляющий страничный автомат с "жесткой" логикой содержит блок регистров кодов операций, блок дешифраторов кодов операций, блок тактовых дешифраторов операций, блок формирования сигналов микроопераций, блок формирователей сигналов микроопераций, логический блок, блок тактовых дешифраторов циклов, блок формирования тактовых сигналов микроопераций, блок формирователей тактовых сигналов микроопераций, блок демультиплексоров, блок счетчиков циклов, логический блок. 4 з.п.ф-лы, 2 ил.

| КАГАН Б.М | |||

| Электронные вычислительные машины и системы | |||

| - М.: Энергоатомиздат, 1991, с | |||

| Кузнечный горн | 1921 |

|

SU215A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ | 1991 |

|

RU2046395C1 |

| Логический процессор | 1977 |

|

SU746531A1 |

| Устройство управления процессором | 1979 |

|

SU798837A1 |

| US 5935240 A, 10.08.1999 | |||

| Прибор, замыкающий сигнальную цепь при повышении температуры | 1918 |

|

SU99A1 |

| US 5694587 A, 02.12.1997. | |||

Авторы

Даты

2003-02-20—Публикация

2000-01-26—Подача