Изобретение относится -к области вы числительной текники и может быть использовано в устройствах для передачи и обработки информации. Известно логическое ЗУ, }-, содержа щее блок памяти, входной регистр, адрес но-числовой регистр, регистр адреса и выходной регистр. Недостатком этого устройства является многотактное выполнение и ограниченное число типов выполняемых логических операций. Известно также логическое ЗУ 2j, содержащее блок памяти с дешифраторами, причем к адресным входам блока памяти подключены выходы регистра эдреса, а к информационным входам - выходы .мультиплексоров, регистры слова, выходы одноименных разрядов которых подключены к управляющим входам мультиплексов, информационные входы последних соединены с шинами управления. В этом устройстве возможна параллельная логическая обработка запоминаемой информации.

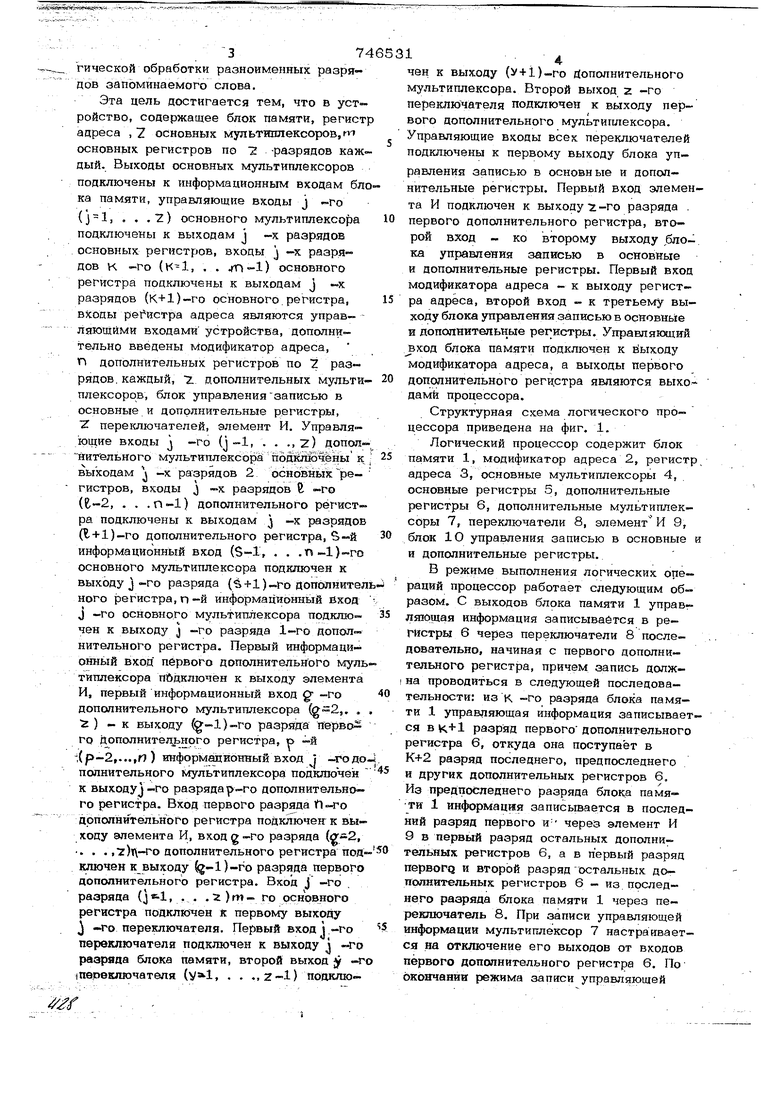

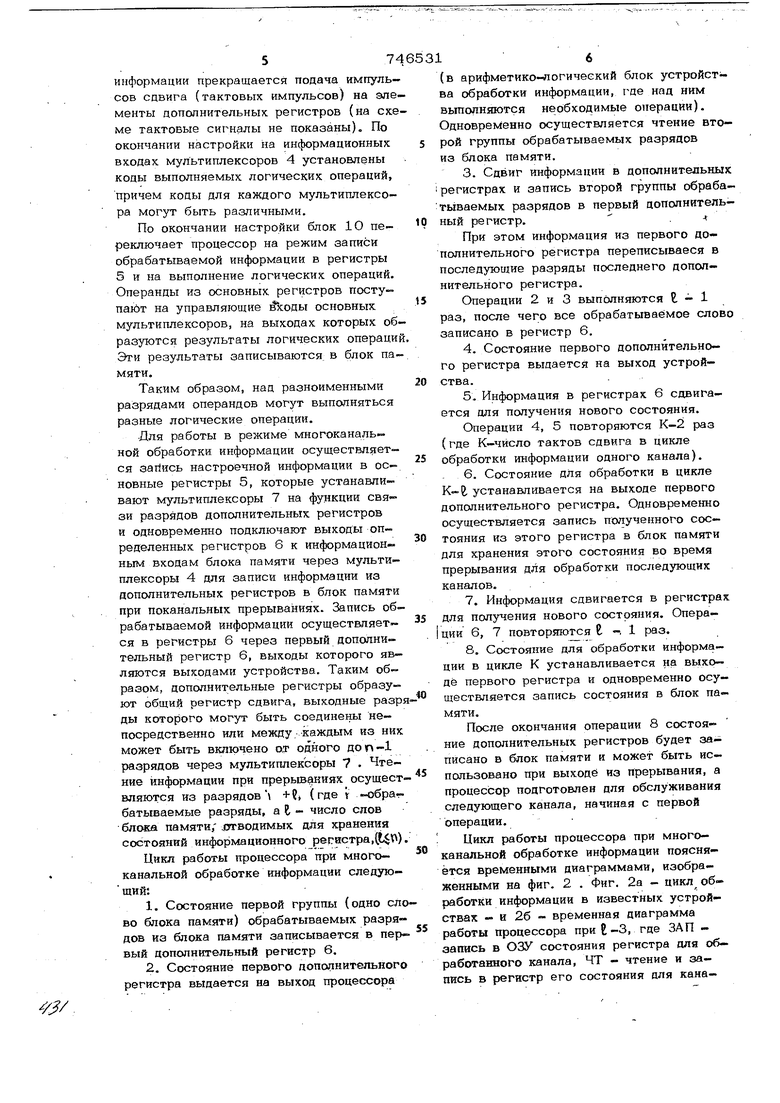

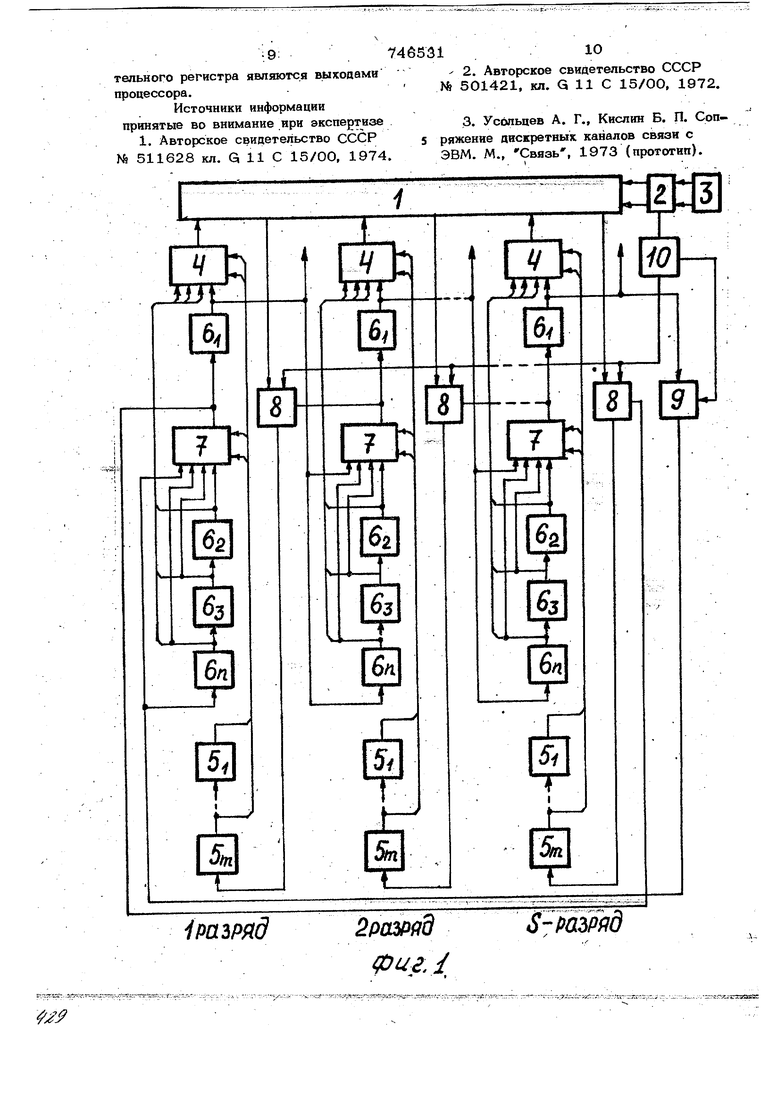

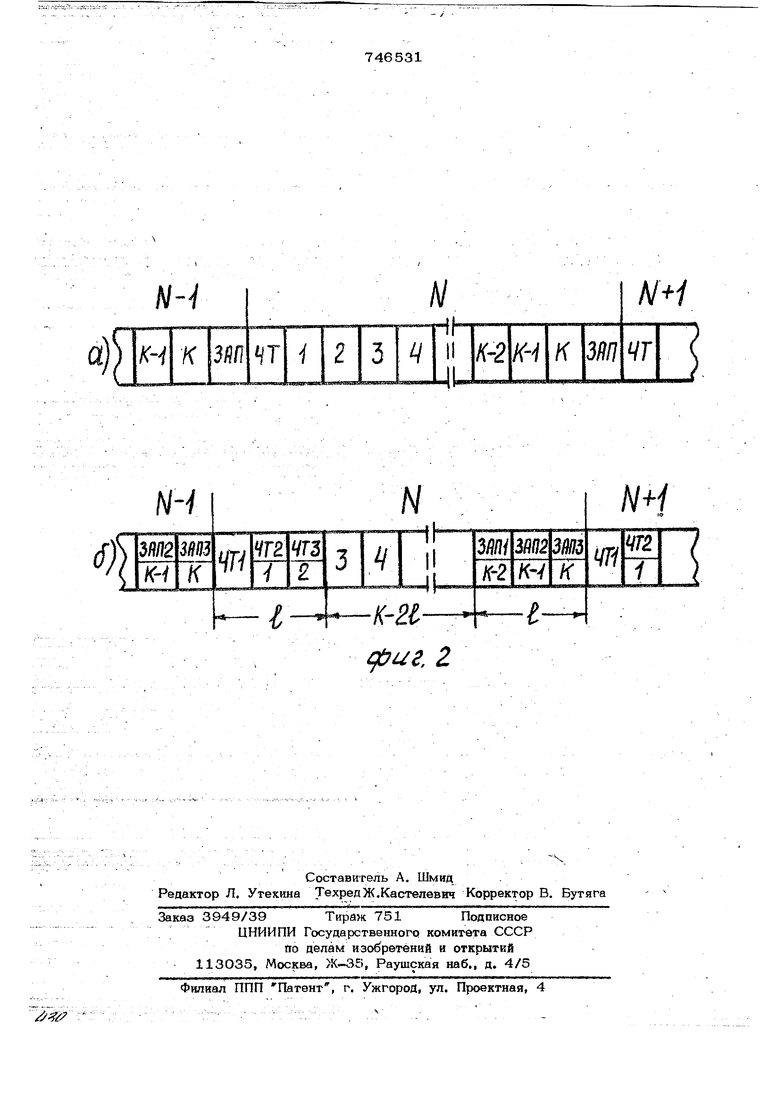

аг-г.., качестве обрабатывающих элемен- JTOB используются мультиплексоры. Принцип их использования основан на врзможности реализации на выходе мультиплексора . произвольной логической функции fr аргументов-управляющих входов мультиплексора. При этом выбор логической функ- ции произвадтггся в информационных вхо- дов, необходимое число которых - 2. В таком устройстве при подаче управляющих сигналов над всеми разрядами регистров выполняется идентичная логическая операция; неэффективно используется логическое ЗУ в качестве оперативной памяти устройств передачи и обработки информации, в том числе в групповых (многоканальных) устройствах передачи информацш (процессорах связи) 3, Это ограничивает возможность его применения в групповых устройствах передачи . Целью изобретения является расширение области применимости устройства за счет создания возможности различной ло- гической обработки разноименных разрядов запоминаемого слова. Эта цель достигается тем, что в устройство, содержащее блок памяти, регист адреса , 7 основных Мультиплексоров.- основных регистров по 2. -разрядов каждый. Выходы основных мультиплексоров подключены к информационным входам бло ка памяти, управляющие входы j -го (J 1, , . . 7) основного мультиплексора подключены к выходам j -х разрядов основных регистров, входы j -х разрядов к -го (К-1, . . jn-1) основного регистра подключены к выходам j разрядов (к+1)-го основного.регистра, ре1 истра адреса являются управ- ляющйми входами устройства, дополнительно введены модификатор адреса, П дополнительных регистров по 2. разрядов, каждый, 7. дополнительных мульти плексоров, блок управления записью в основные и дополнительные регистры, 2Г переключателей, элемент И. Управляющие входы J го (j -1. ., z) ДОПОЛ ниГельного мультиплексора подключены к выходам -X разрядов 2 основных регистров, входы J -х разрядов & -го (2, . . .п-1) дополнительного регистра подключены к выходам j -х разрядов (.+)-го дополнительного регистра, S-и информационный вход , . . .п-1)го основного мультиплексора подключен к выходу j -го разряда {й-ь1)го дополнител ного регистра, п-и информациоиный йход j го основного мультиплексора подключек к выходу j -го разряда 1-го дополнительного регистра. Первый информациошый вход первого дополнительного муль типлексора пбяключен к выходу элемента И, первый информационный вход g -го дополнительного мультиплексора 2,. , ) - к выходу -1)-го разрягда перво го йополниталцзнрго регистра, о -и ,(р-2,..,,г)) информационный вход J -годо полнительного мультиплексора подключе к выходу}-го разряда р-го дополнительного регистра. Вход первого разряда Лчго дбполнительноГо регистра подключен к выходу элемента И, вход g -го разряда (2 . . . ,2) дополнительного регистра под ключей к выходу -1)-го разряда первого дополнительного регистра. Вход j -го разряда (j «,.. . 2 ) m - го основного регистра подключен к первому выходу -го переключателя. Первый вход j -го переключателя подключен к выходу j разряда блока памяти, второй выход у -г (Переключателя (, . . ., 2-1) подключен к выходу (V + i)-ro Дополнительного ультиплексора. Второй выход 2 -го переключателя подключен к выходу перого дополнительного мультиплексора. Управляющие входы всех переключателей подключены к первому выходу блока управления записью в основные и дополнительные регистры. Первый вход элемента И подключен к вы ходуZ-го разряда . первого дополнительного регистра, второй вход - ко второму выходу ,блока управления записью в основные и дополнительные регистры. Первый вход модификатора адреса - к выходу регистра адреса, второй вход - к третьему выходу блока управления записью в основные и дополнительные регистры. Управляющий вход блока памяти подключен к йыходу модификатора адреса, а выходы первого дополнительного регистра являются выходами процессора. Структурная схема логического процессора приведена на фиг. 1. Логический процессор содержит блок памяти 1, модификатор адреса 2, регистр, адреса 3, основные мультиплексоры 4, основные регистры 5, дополнительные регистры 6, дополнительные мультиплексоры 7, переключатели 8, элемент И 9, блок 10 управления записью в основные и и дополнительные регистры. В режиме выполнения логических операций процессор работает следующим образом. С выходов блока памяти 1 управлшощая информация записывается в регистры 6 через переключатели 8 последовательно, начиная с первого дополнительного регистра, причем запись должна проводиться в следующей последовательности: из к -го разряда блока памяти 1 управляющая информация записывается в к+1 разряд первого дополнительного регистра 6, откуда она поступает в К+2 разряд последнего, предпоследнего и других дополнительных регистров 6, Из предпоследнего разряда блока памяти 1 информацися записывается в последний разряд первого и череэ элемент И 9 в первый разряд остальных дополни- тельных регистров 6, а в первый разряд первого и второй разрядостальных дополнительных регистров 6 - из последнего разряда блока памяти 1 через переключатель 8. При записи управляющей информации мультиплексор 7 настраивается на отключение его выходов от входов первого дополнительного регистра 6. По окончании режима записи управляющей информации прекращается подача импуль сов сдвига (тактовых импульсов) на эле менты дополнительных регистров (на схе ме тактовые сигналы не показаны). По окончании настройки на информационных входах мультиплексоров 4 установлены коды выполняемых логических операций, причем коды для каждого мультиплексора могут быть различными. По окончании настройки блок 10 переключает процессор на режим записи обрабатываемой информации в регистры 5 и на выполнение логических операций. Операнды из основных регистров поступают на управляющие йходы основных мультиплексоров, на выходах которых об разуются результаты логических операци Эти результаты записываются в блок памяти. Таким образом, над разноименными разрядами операндов могут выполняться разные логические операции. Для работы в режиме многоканальной обработки информации осуществляется зайись настроечной информации в основные регистры 5, которые устанавливают мультиплексоры 7 на функции связи разрядов дополнительных регистров и одновременно подключают выходы определенных регистров 6 к ин(|юрмациоН ным входам блока памяти через мультиплексоры 4 для записи информации из дополнительных регистров в блок памяти при поканальнык прерываниях. Запись обрабатываемой информации осуществляется в регистры 6 через первый дополнительный регистр 6, выходы которого являются выходами устройства. Таким образом, дополнительные регистры образуют общий регистр сдвига, выходные разр ды которого могут быть соединены непосредственно или между, -каждым из них может быть включено от одного доп-1 разрядов через мультиплексоры 7 . Чтение информации при прерьюаниях осущест вляются из разрядов + (где г -обрабатываемые разряды, а , - число слов блока памяти; зсягводимых для хранения состояний информационного регастра,(411) Цикл работы процессора при многоканальной обработке информации следую- щий: 1.Состояние первой группы (одно сло во блока памяти) обрабатываемых разрядов из блока памяти записывается в первый дополнительный регистр 6. 2.Состояние первого дополнительного регистра выдается на выход процессора (в арифметико-логический блок устройства обработки информации, где над ним выполняются необходимые операции). Одновременно осуществляется чтение второй группы обрабатываемых разрядов из блока памяти. 3.Сдвиг информации в дополнительных регистрах и запись второй группы обрабатываемых разрядов в первый дополнительный регистр.. -f При этом информация из первого дополнительного регистра переписываеся в последующие разряды последнего дополнительного регистра. Операции 2 и 3 выполняются . - 1 раз, после чег;о все обрабатываемое слово записано в регистр 6. 4.Состояние первого дополнительного регистра выдается на выход устройства. 5.Информация в регистрах 6 сдвигается для получения нового состояния. Операции 4, 5 повторяются К-2 раз (где К-число тактов сдвига в цикле обработки информации одного канала). 6.Состояние дЛя обработки в цикле К-и. устанавливается на выходе первого дополнительного регистра. Одновременно осуществляется запись полученного состояния из этого регистра в блок памяти для хранения этого состояния во время прерывания для обработки последующих каналов.7.Информация сдвигается в регистрах для получения нового состояния. Операции 6, 7 повторяются Е. -, 1 раз. 8.Состояние для обработки информации в цикле К устанавливается на выходе первого регистра и одновременно осуществляется запись состояния в блок памяти. После окончания операции 8 состояние дополнительных регистров будет записано в блок памяти и может быть использовано при выходе из прерывания, а процессор подготовлен для обслуживания следующего канала, начиная с первой операции. Цикл работы процессора при многоанальной обработке информации пояснятся временными диаграммами, изобраенными на фиг. 2 . Фиг. 2а - цикл обаботки информации в известных устройтвах и 26 - временная диаграмма аботы процессора при -3, где ЗАП апись в ОЗУ состояния регистра для обаботанного канала, ЧТ - чтение и заись в регистр его состояния для кана746531ла (N ), подлежащего обработке, 1 -К,операции обработки слов со сдвигом. Модификатор адреса служит для образования адресов А. ДО номер обрабатываемого канала) обеспе- чивая процесс разделения Ойного информа ционного слова на несколько слов и об- ратный процесс. Модификатор может быть выпс5л:нен в виде сумматора, производящего вычисления адресов по правилу A-A +Const , где Const изменяется от 1 ДО& -1. Таким образом, предлагаемый кий процессор обеспечивает многоканаль ную обработку информации, совмещая операции обработки информации с операциями записи информации в регистры процессора при выходе из прерываний и операциями чтения информации иёрегист ров в блок памяти при вхождении в прерывания. Кроме того, процессор одновременно обеспечивает выделение обрабатываемых разрядов информационных слов, не затрачивая времени на эти операции, и осуществляет хранение обрабатываемых слов не одним словом блока памяти, а нёсколькими, что позволяет сократить оборудование. При л дополнительных регистрах с разрядностью 6 могут обрабатываться слова с раэряднойтью до разрядности устройства обработки п . ормула изобретения Логический процессор, содержащий . блок памяти, регистр адреса, Z основных мультиплексоров, гп основных регистров по 2: разрядов каждый, причем выходы основных мультиплексоров подключены к информационным входам блока памяти, управляющие входы j -го {j 1, . ., основного мультиплексора подключены к выходам j -X разрядов основных регистров, входы j -X разрядов К -го (ц-1, ...,гп-1) основного регистра подключены к выходам J--X разрядов (К+1)-го основ ного регистра, входы регистра адреса ййрЕШЬя прМйякШйШ входами логичес кого процессора, отличаюши йс я тем, что, с целью расширения облас ти применения процессора за счет созда- ния возможности различной логической о работки разноименных: разрядов запоминаемого слова, в него дополнительно вве дены модификатор адреса,п дополнительных регистров по 2. разрядов каждый, Т11п101И пнительвых мультиплексоров, блок

8 управления записью в основные и дополнительные регистры, Z переключателей . и элемент И, причем управляющие входы J „го (j-1, . . . ,2) дополнительного мультиплексора подключены к выходам J -X разрядов 2 основных регистров, входы -X разрядов -го (t-2,. . .,П-1) дополнительного регистра подключены к выходам j -X разрядов (Е+1)-го дополнительного регистра, -и информационный вход (S-l . . )-го основного мультитиплексора подключен к выходу j -го разряда (S+l)-ro дополнительного регистра, П-и информационный вход j -го основного мультиплексора подключен к выходу j -го разряда 1-го дополнительного регистра, первый информационный вход перврго дополнительного мультиплексора подключен к выходу элемента И, первый информационный вход о-го дополнительного мультиплексора U2-2, . . .,7.)подключен к выходу D-1)-го разряда первого дополнительного регистра,р-и (р-2, . . . ,л) информационный вход j-го дополнительного мультигшексора подключен к выходу j -го разряда р -го до- полнительного регистра, вход первого разряда п -го дополнительного регистра подключен к выходу элемента И, вход -го разряда (д-2, . , ., z) -го дополнительного регистра подключен к выходу (g-l)ro разряда первого дополнительного регистра, вход j -го разряда (j-l, . . . , 2)П1-го основного регистра подключен к первому выходу j -го переключателя, первый вход j -го переключателя подключен к выходу j -го разряда ёлока памяти, второй выход у -го переключателя (, 1 . . , 2-1) подключен к выходу (v+l)-ro сюполнительного мультиплексора, второй выход 2. о реключателя подключен к выходу первого дополнительного мультиплексора, управляющие входы всех переключателей подключены к первому выходу блока управления записью в основные и дополнительные регистры, первый вход элемента И подключен к выходу разряда первого дополнительного регистра, второй вход ко второму выходу блока управления записью в оснсжные и дополнительные ре гистры, первый вход модификатора адреса подключен к выходу регистра адреса, второй вход - к третьему выходу блока управления записью в основные и допол нительные регистры, адресные входы блока памяти Яощслючевы к выходам модификатора адреса, выходы первого дополнительного регистра являются выходами процессора.

Источники информации принятые во внимание ири экспертизе 1. Авторское свидетельство СССР № 511628 кл. Gi 11 С 15/00, 1974.

- 2. Авторское свидетельство СССР № 501421, кл. Q 11 С 15/00, 1972.

3. Усольцев А, Г., Кислин Б. П. Сопряжение дискретнык каналов связи с ЭВМ. М., Связь, 1973 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор программируемого контроллера | 1985 |

|

SU1406595A1 |

| Устройство управления процессора | 1988 |

|

SU1670686A1 |

| Мультипрограммное вычислительное устройство | 1990 |

|

SU1777147A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Процессор программируемого контроллера | 1988 |

|

SU1550515A2 |

| Многофункциональный генератор двоичных последовательностей | 1981 |

|

SU991397A1 |

| Микропроцессор | 1984 |

|

SU1211745A1 |

| Устройство для измерения временных параметров программ | 1982 |

|

SU1136109A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Устройство для адресации памяти | 1989 |

|

SU1656543A1 |

9

2радРйд

.

., . --viftUEtraosas:

(f:

Авторы

Даты

1980-07-05—Публикация

1977-11-29—Подача