Изобретение относится к вычислительной и информационной технике и может быть использовано для создания разнообразной оптоэлектронной аппаратуры компьютерных и информационных технологий, в том числе военной, ракетно-космической, экологической и бытовой.

Известна оптоэлектронная вычислительная система с общей системной шиной [1], содержащая процессоры, оперативную и другие памяти, периферийные устройства, оптическую системную шину для обмена информацией между устройствами системы. Основным недостатком данной структуры является недостаточно высокое быстродействие процессоров из-за относительно невысокой скорости передачи сигналов между блоками процессора.

Наиболее близким к предлагаемому устройству является процессор [2], содержащий блок управления внешней памятью, местную память, блок микропрограммного управления, блок управляющей памяти. Основным недостатком данной структуры является недостаточно высокое быстродействие процессоров из-за относительно невысокой скорости передачи сигналов между блоками процессора и отсутствие функции аппаратного ассоциативного поиска.

Техническим результатом является повышение производительности, помехозащищенности, надежности процессора, а также расширение его функциональных возможностей за счет возможности высокоскоростного, многоканального ассоциативного аппаратного поиска данных.

Это достигается тем, что в оптический ассоциативный поисковый процессор, содержащий блок управления внешней памятью, блок местной памяти, блок микропрограммного управления, блок управляющей памяти, блок управления процессором, введены оптическая матричная общая системная шина, блоки кэш памятей, блок многоканальных оптических ассоциативных корреляторов, оптические блоки пространственно-переменных связей для перекомпоновки слов в странице информации, блоки оптических логических элементов для операций булевой логики, оптический блок ввода/вывода сигналов процессора, внешняя магистраль ввода/вывода сигналов процессора, внутренняя оптическая магистраль ввода/вывода сигналов процессора, местные шины ввода/вывода, оптические блоки ввода/вывода, оптические шины ввода/вывода, оптические блоки дешифрации входных/выходных сигналов, местные шины связи с матричной общей системной шиной, причем входы/выходы каждого блока управления внешней памятью, блока микропрограммного управления, блока управления процессором через соответствующие последовательно расположенные и связанные между собой местную шину ввода/вывода, оптический блок ввода/вывода, оптическую шину ввода/вывода, оптический блок дешифраторов входных/выходных сигналов, местную шину связи с общей системной шиной оптически связаны с оптической общей системной шиной, входы/выходы каждого блока местной памяти, блока управляющей памяти, блока кэш памятей, блок многоканальных оптических ассоциативных корреляторов, через соответствующие последовательно расположенные и связанные между собой местную шину ввода/вывода, оптический блок ввода/вывода, оптическую шину ввода/вывода, оптический блок дешифраторов входных/выходных сигналов, оптические шины ввода/вывода, оптический блок пространственно-переменных связей для перекомпоновки слов в странице информации, оптические шины ввода/вывода, блок оптических логических элементов для операций булевой логики, местные шины связи с общей матричной системной шиной оптически связаны с оптической матричной общей системной шиной, вход/выход которой через последовательно расположенные и связанные внутреннюю оптическую магистраль ввода/вывода сигналов процессора, оптический блок ввода/вывода сигналов в процессор, оптическую шину ввода/вывода, блок оптических логических элементов для операций булевой логики, оптическую шину ввода/вывода, оптический блок пространственно-переменных связей для перекомпоновки слов в странице информации оптически связаны с внешней магистралью ввода/вывода сигналов в процессор.

А также тем, что оптическая матричная общая системная шина содержит одну единственную оптическую магистраль.

А также тем, что оптическая общая системная шина содержит оптическую магистраль адресов, оптическую магистраль данных, оптическую магистраль управления.

Данная совокупность существенных признаков и связей между ними позволяет получить устройство, обладающее более чем в 1000 раз большей производительностью, помехозащищенностью и надежностью и более широкими функциональными возможностями за счет прямого аппаратного ассоциативного поиска информации

Сущность изобретения заключается в том, что на основе использования оптических ассоциативных аппаратных методов поиска и передачи сигналов, применения оптической общей матричной системной шины, использующей в качестве передающей среды свободное пространство и/или матрицы световодов (волоконные и/или интегральные), оригинальных схем оптического ввода/вывода сигналов из блоков процессора, оригинальной структуры процессора создана архитектура оптического ассоциативного поиского процессора ВЕРБ-2 Александра ВЕРБОВЕЦКОГО, позволяющая существенно повысить производительность, помехозащищенность, надежность процессора и различной аппаратуры, построенной на его основе, а также расширить его функциональные возможности за счет аппаратного ассоциативного многоканального высокоскоростного поиска информации.

Таким образом, предложенный оптический ассоциативный процессор ВЕРБ-2 Александра ВЕРБОВЕЦКОГО обладает свойствами, не присущими известным устройствам. Это объясняется новой совокупностью существенных признаков и новыми связями, изложенными выше.

Сравнение предлагаемого устройства с известными свидетельствует о соответствии его критерию «новизна», а отсутствие в аналогах отличительных признаков предлагаемого устройства - о соответствии критерию «изобретательский уровень».

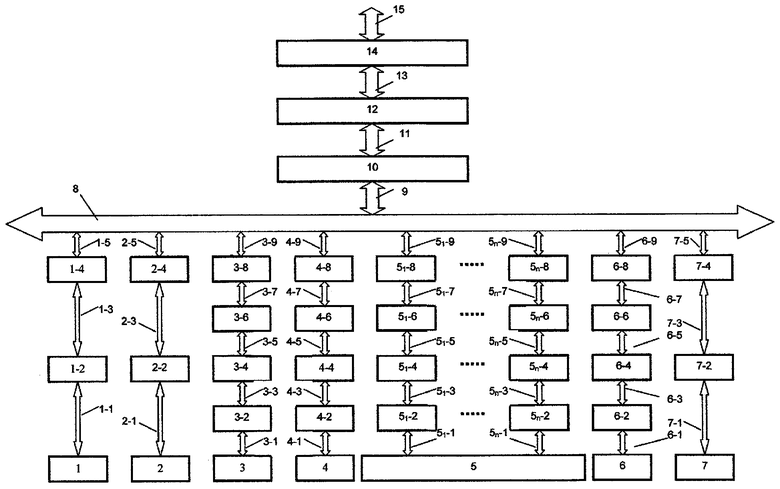

На чертеже приведена функциональная схема оптического ассоциативного поискового процессора ВЕРБ-2 Александра ВЕРБОВЕЦКОГО.

Оптический ассоциативный процессор ВЕРБ-2 Александра ВЕРБОВЕЦКОГО содержит: блок управления внешней памятью 1, имеющий местные шины ввода/вывода 1-1, оптические блоки ввода/вывода 1-2, оптические шины ввода/вывода 1-3, оптические блоки дешифраторов входных/выходных сигналов 1-4, местные шины связи с общей системной шиной 1-5; блок микропрограммного управления 2, имеющий местные шины ввода/вывода 2-1, оптические блоки ввода/вывода 2-2, оптические шины ввода/вывода 2-3, оптические блоки дешифраторов входных/выходных сигналов 2-4, местные шины связи с общей матричной системной шиной 2-5; блок местной памяти 3, имеющий местные шины ввода/вывода 3-1, оптические блоки ввода/вывода 3-2, оптические шины ввода/вывода 3-3, оптические блоки дешифраторов входных/выходных сигналов 3-4, оптические шины ввода/вывода 3-5, оптический блок пространственно-переменных связей для виртуальной перекомпоновки слов в странице информации 3-6, оптические шины ввода/вывода 3-7, блок оптических логических элементов для операций булевой логики 3-8, местные шины связи с общей матричной системной шиной 3-9, блок кэш памятей 4, имеющий местные шины ввода/вывода 4-1, оптические блоки ввода/вывода 4-2, оптические шины ввода/вывода 4-3, оптические блоки дешифраторов входных/выходных сигналов 4-4, оптические шины ввода/вывода 4-5, оптический блок пространственно-переменных связей для виртуальной перекомпоновки слов в странице информации 4-6, оптические шины ввода/вывода 4-7, блок оптических логических элементов для операций булевой логики 4-8, местные шины связи с общей матричной системной шиной 4-9; блок многоканальных оптических ассоциативных корреляторов 5, имеющий местные шины ввода/вывода 5-1, оптические блоки ввода/вывода 5-2. оптические шины ввода/вывода 5-3, оптические блоки дешифраторов входных/выходных сигналов 5-4, оптические шины ввода/вывода 5-5, оптический блок пространственно-переменных связей для виртуальной перекомпоновки слов в странице информации 5-6, оптические шины ввода/вывода 5-7, блок оптических логических элементов для операций булевой логики 5-8, местные шины связи с общей системной шиной 5-9; блок управляющей памяти 6, имеющий местные шины ввода/вывода 6-1, оптические блоки ввода/вывода 6-2, оптические шины ввода/вывода 6-3, оптические блоки дешифраторов входных/выходных сигналов 6-4, оптические шины ввода/вывода 6-5, оптический блок пространственно-переменных связей для виртуальной перекомпоновки слов в странице информации 6-6, оптические шины ввода/вывода 6-7, блок оптических логических элементов для операций булевой логики 6-8, местные шины связи с общей системной шиной 6-9; блок управления процессором 7, имеющий местные шины ввода/вывода 7-1, оптические блоки ввода/вывода 7-2, оптические шины ввода/вывода 7-3, оптические блоки дешифраторов входных/выходных сигналов 7-4, местные шины связи с общей системной шиной 7-5; оптическую матричную общую системную шину 8; внутреннюю оптическую магистраль ввода/вывода сигналов процессора 9; оптический блок ввода/вывода сигналов в процессор 10; оптическую шину ввода/вывода 11, блок оптических логических элементов для операций булевой логики 12, оптическую шину ввода/вывода 13, оптический блок пространственно-переменных связей для виртуальной перекомпоновки слов в странице информации 14, внешняя магистраль ввода/вывода сигналов в процессор 15.

Блок управления внешней памятью 1 предназначен для осуществления динамического обмена данными между процессором и внешней по отношению к процессору памятью, в состав блока могут входить памяти ключей защиты, сверхоперативная память, память многоабонентного доступа, блок динамического преобразования адресов при реализации виртуальной памяти. Блок 1 может быть выполнен на электронных, оптоэлектронных и оптических компонентах.

Местные шины ввода/вывода 1-1 служат для передачи электрических или оптических сигналов, могут содержать магистрали адресов, данных и управления, имеющие в зависимости от варианта передаваемых сигналов в качестве проводящей среды, например, металлические проводники, один, несколько или матрицу световодов (волоконных и/или интегральных) или свободное пространство.

Оптические блоки ввода/вывода 1-2 служат для согласования и, в случае необходимости, преобразования входных/выходных электронных или оптических сигналов в оптические или электрические, в соответствии с типом выполнения блока 1. Для преобразования входных электронных сигналов в оптические эти блоки могут быть выполнены, например, в виде линеек или матриц лазерных диодов, каждый из которых излучает, например, на своей длине волны λi, где i=1,2,3...р, при этом р - максимальное число сигналов, передаваемых параллельным кодом, а при передаче сигналов последовательно-параллельным кодом, последовательные оптические сигналы передаются, например, каждым лазерньм диодом на различных длинах волн λj (где j=1,2,3...s, s - максимальное число сигналов, передаваемых последовательным кодом), отличных от длин волн оптических сигналов, которые передаются параллельным кодом. Если на входы блока 1-2 поступают оптические сигналы, то на их входах дополнительно могут располагаться линейки или матрицы фотоприемников.

Оптические шины ввода/вывода 1-3 служат для передачи оптических сигналов и могут содержать магистрали адресов, данных и магистрали управления, имеющие в качестве передающей среды, например, один, несколько или матрицы световодов (волоконные и/или интегральные) или свободное пространство.

Оптические блоки дешифраторов входных/выходных сигналов 1-4 служат для выделения определенной группы спектральных оптических сигналов из множества групп спектральных оптических сигналов, распространяющихся по оптической общей системной шине 10, которые соответствуют блоку 1. Блок 1-4 может быть выполнен, например, на основе световодной (волоконной и/или интегральной) оптики с использованием дифракционных решеток или спектральных фильтров, мультиплексоров, демультиплексоров.

Местная шина связи с оптической общей системной шиной 1-5 служит для передачи оптических сигналов в/из оптической системной шины 10 от/к блоку 1 и может состоять из одной магистрали или содержать магистрали адресов, данных и управления. Магистрали могут быть выполнены в виде одного, нескольких или матриц световодов (волоконных и/или интегральных) или свободного пространства.

Блок микропрограммного управления 2 осуществляет в режиме разделения времени или спектрального уплотнения управление работой блоками процессора и некоторыми процедурами каналов ввода/вывода, используя для этого микропрограммы, хранящиеся в управляющей памяти. При этом он выдает предписание микрокомандой управляющие сигналы в соответствующие блоки процессора, формирует адрес следующей микрокоманды и обрабатывает прерывание микропрограмм. При прерывании микропрограммы в блоке запоминается адрес следующей подлежащей выполнению микрокоманды. Блок 2 может иметь электронное, оптоэлектронное или оптическое выполнение.

Шины 2-1, 2-3, 2-5 имеют то же назначение и выполнение, что и аналогичные шины 1-1, 1-3, 1-5.

Блоки 2-2, 2-4 имеют то же назначение и выполнение, что и аналогичные блоки 1-2, 1-4.

Блок местной памяти 3 процессора может служить для хранения операндов и результатов операций, значения базовых адресов и индексов, данных блока восстановления и диагностики, управляющих слов активных подканалов. Блок 3 может иметь, например, электронное, оптоэлектронное или оптическое выполнение.

Шины 3-1, 3-3, 3-5, 3-7, 3-9 имеют то же назначение и выполнение, что и аналогичные шины 1-1, 1-3, 1-5.

Блоки 3-2, 3-4 имеют то же назначение и выполнение, что и аналогичные блоки 1-2, 1-4.

Оптический блок пространственно-переменных связей для виртуальной перекомпоновки слов в странице информации 3-6 служит для создания пространственно-переменных связей между словами операндов и может быть выполнен, как это описано в [3] или в Авторских свидетельствах №1531166 от 15.04.88 г., №1596340 от 15.06.88 г., №1603401 от 15.06.1988 г., Патенте №1767534 от 20.12.89 г.

Блок оптических логических элементов для операций булевой логики 3-8 служит для логической обработки разрядов слов в странице информации и может быть выполнен, как это описано в [3] или в Авторских свидетельствах №1394982, 1396827 от 29.09.86 г. и Патентах №2015578, 2015579, 2015580 - все от 10 июля 1991 г.

Блок кэш памятей 4 служит для согласования пропускных способностей внешней к процессору памяти и процессора для реализации в процессоре производительности, равной производительности его операционных блоков, и может состоять из нескольких модулей кэш-памяти. Блок 4 может быть выполнен на электронных, оптоэлектронных и оптических элементах.

Шины 4-1, 4-3, 4-5, 4-7, 4-9 имеют то же назначение и выполнение, что и аналогичные шины 1-1, 1-3, 1-5.

Блоки 4-2, 4-4 имеют то же назначение и выполнение, что и аналогичные блоки 1-2, 1-4.

Блоки 4-6, 4-8 могут быть выполнены так же, как аналогичные блоки 3-6, 3-8.

Блок многоканальных оптических ассоциативных корреляторов 5 служит для многоканального оптического аппаратного поиска информации и может иметь выполнение, описанное в [3].

Шины 5-1, 5-3, 5-5, 5-7, 5-9 имеют то же назначение и выполнение, что и аналогичные шины 1-1, 1-3, 1-5.

Блоки 5-2, 5-4 имеют то же назначение и выполнение, что и аналогичные блоки 1-2, 1-4.

Блоки 5-6, 5-8 могут быть выполнены так же, как аналогичные блоки 3-6, 3-8.

Блок управляющей памяти 6 служит для хранения управляющей информации-микропрограммы и может иметь электронное, оптоэлектронное и оптическое выполнение.

Шины 6-1, 6-3, 6-5, 6-7, 6-9 имеют то же назначение и выполнение, что и аналогичные шины 1-1, 1-3, 1-5.

Блоки 6-2, 6-4 имеют то же назначение и выполнение, что и аналогичные блоки 1-2, 1-4.

Блоки 6-6, 6-8 могут быть выполнены так же, как аналогичные блоки 3-6, 3-8.

Блок управления процессором 7 предназначен для управления работой процессора и основан на смешанном аппаратно-микропрограммном принципе. Блок 7 может быть выполнен на электронных, оптоэлектронных и оптических элементах.

Шины 7-1, 7-3, 7-5 имеют то же назначение и выполнение, что и аналогичные шины 1-1, 1-3, 1-5.

Блоки 7-2, 7-4 имеют то же назначение и выполнение, что и аналогичные блоки 1-2, 1-4.

Оптическая матричная общая системная шина 8 служит для передачи оптических сигналов между различными блоками оптического процессора и может содержать одну единственную оптическую магистраль в виде одного световода (волоконного и/или интегрального) или свободного пространства или может содержать магистраль адресов, магистраль данных и магистраль управления. Каждая магистраль может иметь в качестве передающей оптической среды один, несколько или матрицы световодов (волоконных и/или интегральных) или свободное пространство.

Внутренняя оптическая магистраль ввода/вывода сигналов процессора 9 служит для передачи оптических сигналов из внешних по отношению к процессору устройств в оптическую матричную общую системную шину процессора и может содержать одну магистраль или магистрали адресов, данных и управления, имеющие в качестве передающей среды, например, один, несколько или матрицы световодов (волоконных и/или интегральных) или свободное пространство.

Оптический блок ввода/вывода сигналов в процессор 10 служит для согласования внешних по отношению к процессору сигналов с оптическими сигналами, передаваемыми по оптической общей системной шине процессора, и может иметь выполнение, аналогичное блоку 1-2.

Оптические шины ввода/вывода 11, 13 имеют то же выполнение, что и шины 1-1, 1-3.

Блок оптических логических элементов 12 и оптический блок пространственно-переменных связей 14 имеют то же выполнение, что и ранее описанные аналогичные блоки.

Внешняя магистраль ввода/вывода сигналов в процессор 15 служит для передачи электрических или оптических сигналов из внешних по отношению к процессору устройств в/из процессора и может содержать одну магистраль или магистрали адресов, данных и управления. В зависимости от передаваемых по магистралям сигналов в качестве их передающей среды могут использоваться либо металлические проводники, либо один, несколько или матрицы световодов (волоконных и/или интегральных) или свободное пространство.

Оптический ассоциативный поисковый процессор «ВЕРБ-2» Александра ВЕРБОВЕЦКОГО работает следующим образом.

Входная/выходная для процессора ВЕРБ-2 информация и управляющие сигналы в оптическом или электрическом виде передаются из/во внешних(е) устройств(а) через внешнюю магистраль 15, оптический блок пространственно-переменных связей 14, блок оптических логических связей 12 и оптические шины ввода/вывода 13 в/из оптическую(ой) матричную(ой) общую(ей) системную(ой) шину(ы) 8 оптическими сигналами со спектральным или временным уплотнением.

Каждый из передающих информацию блоков 1-7 процессора передает ее в виде электронных или оптических сигналов, которые через соответствующие шины 1-1, 1-3, 1-5 ... 7-1, 7-3, 7-5 и блоки 1-2, 1-4 ... 7-2, 7-4 поступают в оптическую матричную общую системную шину 8 в виде спектральных оптических сигналов со спектральным или временным уплотнением.

Спектральные оптические сигналы от всех передающих блоков 1-9 одновременно со спектральным уплотнением распространяются по общей системной шине 8 и поступают во все входные местные оптические шины 1-5 ... 7-5.

В каждом из принимающих информацию блоков 1-7 оптические блоки дешифраторов 1-4 ... 7-4 настраиваются управляющими сигналами на пропускание групп спектральных оптических сигналов, передаваемых от соответствующих передающих информацию блоков, с которыми они производят сеанс связи. Затем выделенные этими блоками дешифрации оптические сигналы в данном принимающем канале преобразуются и поступают на обработку в соответствующие блоки 1-9.

Следует отметить, что передача информации по всем шинам системы может производиться сигналами как только со спектральным уплотнением, так и одновременно со спектральным и временным уплотнением, а сеансы связи всех блоков системы могут осуществляться как одновременно, так и группами с разделением во времени.

Использование изобретения позволит реализовать оптическими методами связь между блоками ассоциативного поиского процессора по оптической матричной общей системной шине, увеличив более чем в 1000 раз его производительность, помехозащищенность и надежность, а также расширить его функциональные возможности за счет выполнения высокоскоростного многоканального аппаратного ассоциативного поиска информации, недоступного в настоящее время на иных не оптических принципах. Такие оптические процессоры ВЕРБ-2 Александра ВЕРБОВЕЦКОГО могут широко применяться в разнообразной радиоэлектронной аппаратуре военного, ракетно-космического, экологического и бытового назначения как наземного, так и бортового базирования.

ЛИТЕРАТУРА

1. Патент (Россия) №2144206, МКИ G 06 E 1/00, 19.02.1999.

2. А.А.Вербовецкий. Основы компьютерных технологий & персональные ПК. М.: АЛЕКС, 2003 г., с.314 (с.128).

3. A.A.Вербовецкий. Оптические цифровые ассоциативные информационные технологии. Книга 2. М.: АЛЕКС, 2003 г., 100 с. (с.53-87).

| название | год | авторы | номер документа |

|---|---|---|---|

| ОПТИЧЕСКИЙ ЦИФРОВОЙ СИГНАЛЬНЫЙ ПРОЦЕССОР "ВЕРБ-3" АЛЕКСАНДРА ВЕРБОВЕЦКОГО | 2003 |

|

RU2263340C2 |

| ОПТИЧЕСКИЙ ПРОЦЕССОР ВЕРБ-1 АЛЕКСАНДРА ВЕРБОВЕЦКОГО | 2003 |

|

RU2263945C2 |

| ОПТИЧЕСКИЙ ЦИФРОВОЙ КОМПЬЮТЕР "АЛЕКС-ВЕРБ" АЛЕКСАНДРА ВЕРБОВЕЦКОГО | 2004 |

|

RU2284050C2 |

| ОПТОЭЛЕКТРОННАЯ СИСТЕМНАЯ ПЛАТА ДЛЯ ПЕРСОНАЛЬНОГО КОМПЬЮТЕРА | 2001 |

|

RU2205443C2 |

| ОПТОЭЛЕКТРОННАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА С ОБЩЕЙ СИСТЕМНОЙ ШИНОЙ | 1999 |

|

RU2144206C1 |

| ОПТОЭЛЕКТРОННЫЙ ЛОГИЧЕСКИЙ БЛОК | 1986 |

|

SU1396827A1 |

| МНОГОКАНАЛЬНОЕ ОПТИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1981 |

|

SU1031344A1 |

| УСТРОЙСТВО ДЛЯ ОПТИЧЕСКОЙ АССОЦИАТИВНОЙ ВЫБОРКИ ИНФОРМАЦИИ | 1984 |

|

SU1277803A1 |

| УПРАВЛЯЮЩИЙ СТРАНИЧНЫЙ АВТОМАТ С "ЖЁСТКОЙ" ЛОГИКОЙ | 2000 |

|

RU2199147C2 |

| ОПТОЭЛЕКТРОННЫЙ ЛОГИЧЕСКИЙ БЛОК ДЛЯ ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1991 |

|

RU2015578C1 |

Изобретение относится к компьютерной и информационной технике, а именно к вычислительным устройствам, выполненным на оптоэлектронной элементной базе. Техническим результатом является повышение производительности, помехозащищенности и отказоустойчивости процессора в условиях воздействия мощных электромагнитных полей на аппаратуру как наземного, так и бортового базирования и расширение функциональных возможностей за счет высокоскоростного многоканального аппаратного ассоциативного поиска информации. Для этого процессор содержит блок управления внешней памятью, блок местной памяти, блок микропрограммного управления, блок управляющей памяти, блок управления процессором, оптическая матричная общая системная шина, блоки кэш памятей, блоки многоканальных оптических ассоциативных корреляторов, оптические блоки пространственно-переменных связей, блоки логических элементов, оптический блок ввода/вывода сигналов процессора, внешняя магистраль ввода/вывода сигналов процессора, внутренняя оптическая магистраль ввода/вывода сигналов процессора, местные шины ввода/вывода, оптические блоки ввода/вывода, оптические шины ввода/вывода, оптические блоки дешифрации входных/выходных сигналов, местные шины связи с матричной общей системной шиной. 2 з.п. ф-лы, 1 ил.

| ВЕРБОВЕЦКИЙ А.А | |||

| Основы компьютерных технологий & современные ПК | |||

| М.: Алекс, 2002, с | |||

| Прибор, автоматически записывающий пройденный путь | 1920 |

|

SU110A1 |

Авторы

Даты

2005-11-10—Публикация

2003-10-13—Подача