логического нуля устройства, вход запуска которого соединен с входами запуска коммутаторов добавок и адреса команды, введены регистр пакета команд, счетчик команд пакета, дешифратор команд пакета, коммутатор адреса перехода, дополнительный коммутатор распаковки, дешифратор вто-; рой команды, первый и второй дополнительные сумматоры, причем информационный вход регистра пакета команд соединен с входом команд устройства, выход длины команды регистра пакета команд соединен с информационным входом счетчика команд пакета, вход запуска которого соединен с входом номера слова устройства, выход счетчика команд пакета соединен с первым входом дешифратора ко манд пакета, второй вход которого соединен с входом кода операций регистра пакета команд, адресный выход которого соединен с информационньом входом коммутатора адреса перехода, управляющий вход которого соединен с выходом дешифратора команд пакета выход коммутатора адреса перехода соединен с выходом адреса и типа перехода устройства, группа информационных входов дополнительного коммутатора распаковки соединена со вторыми разрядными выходами буферных регистров команды группы, управляющий вход дополнитёлвного коммутатора распаковки соединен с выходом первого дополнительного сумматора, первый и второй входы которого соединены, соответственно, с адресным выходом и входом длины команды устройства, выход дополнительного коммутатора распаковки соединен с входом дешифратора второй команды, первый и второй выходы которого соединены, соответственно, с управляющими входами коммутаторов добавок и адреса команды, третий выход дешифратора второй команды соединен с первым входом второго дополнительного сумматора, второй вход которого соединен с входом длины команды устройства, а выход второго дополнительного сумматора coeдинe с дополнительным информационным входом коммутатора добавок.

Введение регистра пакета команд, счетчика команд пакета дешифратора команд . пакета, коммутатора адреса перехода позволяет обеспечить вызов новой последовательности команд с опережением по отношению к исполнению команды переходов,

Введение дополнительного коммутатора распаковки, дешифратора вто.рой команды, первого и второго дополнительного сумматора позволяет обнаруживать и выполнять команду перехода параллельно с расшифровкой пре дыдущей команды, что-экономит вре|мя на чтение и расшифровку команды перехода.

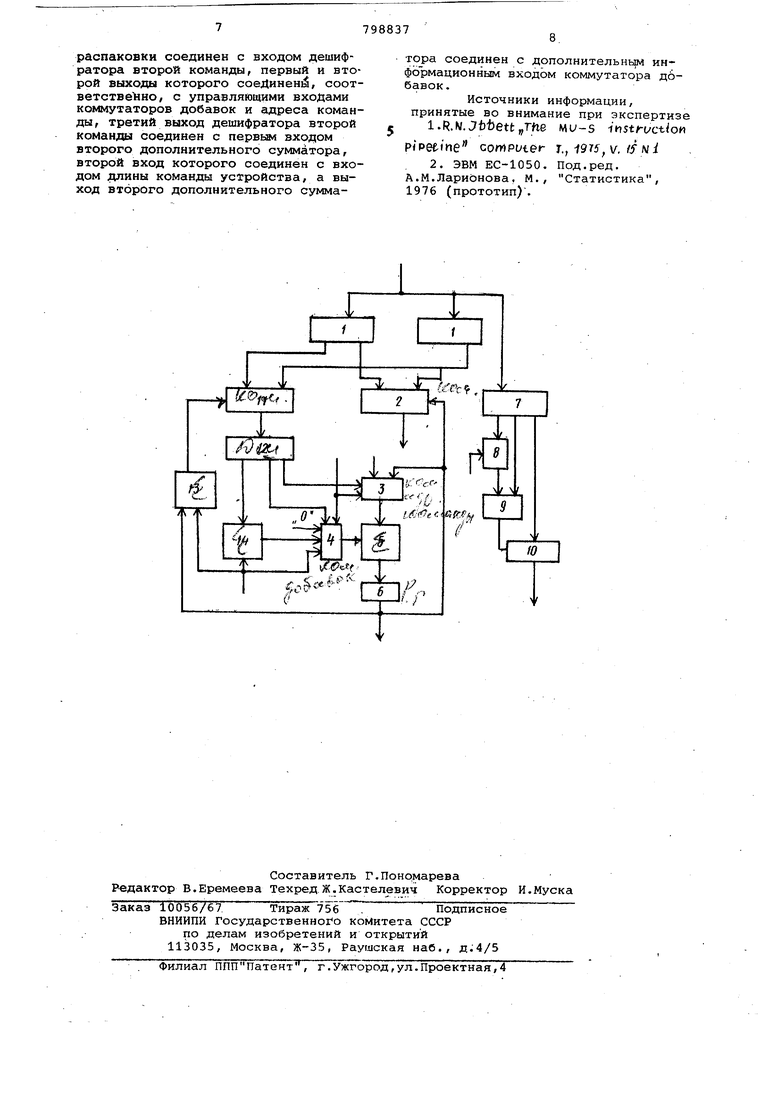

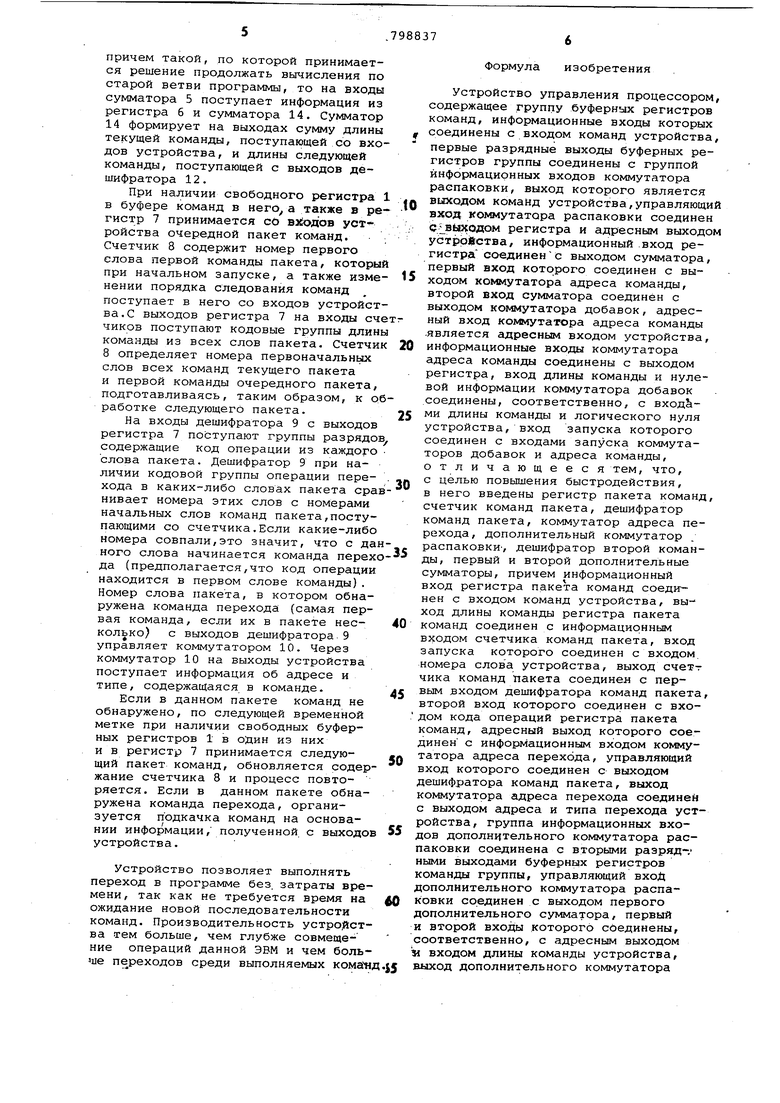

На чертеже представлена структурная схема устройства.

Устройство содержит буферные регистры 1 команд, коммутатор 2 распаковки, коммутатор 3 адреса команды, коммутатор 4 добавок, сумматор 5, регистр 6, регистр 7 пакета команд, счетчик 8 команд пакета, дешифратор 9 команд пакета, коммутатор 10 адреса перехода, дополнительный коммутатор 11 распаковки, дешифратор 12 второй , дополнительные сумматоры 13 и 14.

Устройство работает следующим об-разом.

Команды, подлежащие исполнению, поступают на выходы устройства через коммутатор 2 из регистров 1.Управление коммутатором 2 осуществляется

текущим адресом исполняемой команды (номером ее первого слова), хранящимся в регистре 6.

При начальном запуске программы сигнал со входов устройства управляет коммутаторами 3 и 4. На входы сумматора 5 поступает начальный адрес со входов устройства через коммутатор 3 и нулевая информация через коммутатор 4. С выходов сумматора 5 начальный адрес поступает в регистр 6. Возможность его дальнейшего изменения зависит .прежде всего от результата проверки того, изменяется ли текущая команда в

регистрах 1. Для проверки текущий

адрес выдается из регистра 6 на

выходы устройства, В случае отсутствия команды организуется ее вызов из памяти.

После расшифровки текущей команды ее длина с выходов устройства

через коммутатор 4 поступает на выходы сумматора 5, где складывается с адресом начального слова зтой команды, поступающим на другие входы

сумматора 5, Адрес команды, следующий за текущей, сформированный на выходах сумматора 13, управляет коммутатором 11, который выделяет с выходов регистров 1 следующую команду

и подает ее на дешифра тор 12, распознающий команды перехода.

Если команда на входах дешифратора 12 не является командой перехода, то на выходы сумматора 5 поступает информация из регистра 6 и со входов

устройства.

Если команда на входах дешифратора 12 является командой перехода, причем такой, по которой принимается решение продолжать вычисления по новри ветви,, то на входы 5 поступает нулевая информация через коммутатор 4 и информация со входов устройства через коммутатор 3.

Если команда на входах дешифратора 12 является командой перехода. причем такой, по которой принимается решение продолжать вычисления по старой ветви программы, то на входы сумматора 5 поступает информация из регистра 6 и сумматора 14. Сумматор 14 формирует на выходах сумму длины текущей команды, поступающей со вхо дов устройства, и длины следующей команды, поступающей с выходов дешифратора 12. При наличии свободного регистра в буфере команд в него а также в ре гистр 7 принимается со вз&опов устройства очередной пакет команд. Счетчик 8 содержит номер первого слова первой команды пакета, которы при начальном запуске, а также изме нении порядка следования команд поступает в него со входов устройст ва. С выходов регистра 7 на входы сч чиков поступают кодовые группы длин команды из всех слов пакета. Счетчи 8 определяет номера первоначальных слов всех команд текущего пакета и первой команды очередного пакета, подготавливаясь, таким образом, к о работке следующего пакета. На входы дешифратора 9 с выходов регистра 7 поступают группы разрядо содержащие код операции из каждого слова пакета. Дешифратор 9 при наличии кодовой группы операции перехода в каких-либо словах пакета сра нивает номера этих слов с номерами начальных слов команд пакета,поступающими со счетчика.Если какие-либо номера совпали,это значит, что с да ного слова начинается команда перех да (предполагается,что код операции находится в первом слове команды). Номер слова пакета, в котором обнаружена команда перехода (самая первая команда, если их в пакете несколько) с выходов дешифратора 9 управляет коммутатором 10. Через коммутатор 10 на выходы устройства поступает информация об адресе и типе, содержащаяся в команде. Если в данном пакете команд не обнаружено, по следующей временной метке при наличии свободных буферных регистров 1 в один из них и в регистр 7 принимается следующий пакет команд, обновляется содержание счетчика 8 и процесс повторяется. Если в данном пакете обнаружена команда перехода, организуется подкачка команд на основании информации, полученной с выходов устройства. Устройство позволяет выполнять переход в программе без, затраты времени , так как не требуется время на ожидание новой последовательности команд. Производительность устро Ютва тем больше, чем глубже совмещение операций данной ЭВМ и чем больiie переходов среди выполняемых коман Формула изобретения Устройство управления процессором, содержащее группу буферных регистров команд, информационные входы которых соединены с входом команд устройства, первые разрядные выходы буферных регистров группы соединены с группой информационных входов коммутатора распаковки, выход которого является выходом команд устройства,управляющий вход коммутатора распаковки соединен CiBfcejOflOM регистра и адресным выходом устройства, информационный .вход регистра соединенс выходом сумматора, первый вход которого соединен с выходом коммутатора адреса команды, второй вход сумматора соединён с выходом коммутатора добавок, адресный вход коммутатора адреса команды .является адресным входом устройства, информационные входы коммутатора адреса команды соединены с выходом регистра, вход длины команды и нулевой информации коммутатора добавок соединены, соответственно, с входЬми длины команды и логического нуля устройства, вход запуска которого соединен с входами запуска коммутаторов добавок и адреса команды, отличающееся тем, что, с целью повЕЛшения быстродействия, в него введены регистр пакета команд, счетчик команд пакета, дешифратор команд пакета, коммутатор адреса перехода, дополнительный коммутатор распаковки-, дешифратор второй команды, первый и второй дополнительные сумматоры, причем информационный вход регистра пакета команд соединен с входом команд устройства, выход длины команды регистра пакета команд соединен с информационным входом счетчика команд пакета, вход запуска которого соединен с входом номера слова устройства, выход счетт чика команд Пакета соединен с первым входом дешифратора команд пакета, второй вход которого соединен с входом кода операций регистра пакета команд, адресный выход которого соединен с информационным входом коммутатора адреса перехода, управляющий вход которого соединен с выходом дешифратора команд пакета, выход коммутатора адреса перехода соединен с выходом адреса и типа перехода устройства, группа информационных входов дополнительного коммутатора распаковки соединена с вторыми разряд-, ными выходами буфернь1х регистров команды группы, управляющий вхоЛ дополнительного коммутатора распаковки соединен с выходом первого дополнительного сумматора, первый и второй входы которого соединены, соответственно, с адресным выходом входом длины команды устройства, выход дополнительного коммутатора

распаковки соединен с входом дешифратора второй команды, первый и второй выходы которого соеДиненй, соответстве 1но, с управляющими входами коммутаторов добавок и адреса команды, третий выход дешифратора второй команды соединен с первьал входом второго дополнительного сумматора, второй вход которого соединен с входом длины команды устройства, а выход второго дополнительного сумматора соединен с дополнительньм информационным входом коммутатора добавок.

Источники информации, принятые во внимание при экспертизе I.R.N.JfetJettpTfte MU-S

pipef-ine computer j., . fS Ni

2. ЭВМ EC-1050. Под.ред, A.M.Ларионова, M., Статистика, 1976 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования команд с аппаратной организацией циклических программ | 1979 |

|

SU942018A1 |

| Устройство выборки команд процессора | 1986 |

|

SU1410028A1 |

| Центральный процессор | 1991 |

|

SU1804645A3 |

| Устройство для выборки команд | 1978 |

|

SU726533A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1981 |

|

SU1275521A1 |

| Вычислительная система | 1989 |

|

SU1777148A1 |

| Устройство для распаковки команд | 1990 |

|

SU1702367A1 |

| Устройство буферизации команд процессора | 1983 |

|

SU1092506A1 |

| Процессор ввода-вывода | 1989 |

|

SU1797722A3 |

| Устройство для редактирования информации | 1981 |

|

SU980099A1 |

Авторы

Даты

1981-01-23—Публикация

1979-03-21—Подача