Изобретение относится к радиотехнике, в частности, к приемникам в радиосвязи и радионавигации, в том числе с использованием псевдошумовых сигналов с фазовой или частотной манипуляцией.

Во многих приложениях теории статистических решений, реализуемых в приемных устройствах радиосвязи и радионавигации, используется процедура некогерентного обнаружения сигнала, связанная с вычислением выборки мгновенных значений амплитуды зашумленного сигнала

усреднением элементов этой выборки

и сравнением этой величины с заранее установленным порогом.

Реализация алгоритма (1) требует выполнения арифметических операций (возведение в квадрат, извлечение корня) над многоразрядными числами в реальном времени с достаточно высокой частотой. Что предъявляет ряд жестких требований к микропроцессорной системе, реализующей эту процедуру.

Известное техническое решение по ускорению этих вычислений в узкоспециализированном процессоре за счет аппаратной поддержки - например, "пифагоров процессор" PYTHAGORAS PROCESSOR PDSP16330/A/B фирмы GEC PLESSEY, в котором необходимая величина  формируется в темпе поступления входной информации I и Q за счет аппаратных умножителей, осуществляющих перемножение 16 разрядных чисел (в данном случае самих на себя), т.е. возведения в квадрат, однотактного их суммирования, а также аппаратно реализованного алгоритма быстрого вычисления квадратного корня, но эти процессоры имеют ограничения по входной частоте - 25 МГц [1].

формируется в темпе поступления входной информации I и Q за счет аппаратных умножителей, осуществляющих перемножение 16 разрядных чисел (в данном случае самих на себя), т.е. возведения в квадрат, однотактного их суммирования, а также аппаратно реализованного алгоритма быстрого вычисления квадратного корня, но эти процессоры имеют ограничения по входной частоте - 25 МГц [1].

Наиболее близким прототипом предлагаемого устройства, реализующим формирование величины (1), аппаратно является некогерентный обнаружитель сигнала в шумах, включающий некогерентный гетеродин, первый и второй смесители частот, первый и второй фильтры промежуточной частоты, фазосдвигающую цепочку [2].

В классической схеме обнаружителя синфазная I и квадратурная Q компоненты сигнала образуются в результате преобразования частоты, при котором сигнал гетеродина для одного из смесителей сдвинут по фазе на 90 градусов относительно друг друга. Каждая из этих компонент затем возводится в квадрат, а из их суммы извлекается квадратный корень [3].

Недостатком прототипа являются погрешности нелинейных преобразований сигналов типа возведения в квадрат и извлечения корня, вызванные тем, что любые электрорадиоэлементы с нелинейными характеристиками при преобразовании входного радиосигнала образуют на выходе побочные гармоники. Для устранения этих недостатков, снижающих эффективность обнаружителя в цифровых радиоприемных устройствах после оцифровки мгновенных выборочных значений I и Q, все нелинейные операции в соответствии с формулой (1) выполняются программно микропроцессорным блоком приемника.

Недостатком программной реализации такого обнаружителя является ограниченное быстродействие (низкие входные частоты).

Техническим результатом настоящего изобретения является создание устройства, реализующего точный алгоритм аппаратно без выполнения нелинейных операций (возведения в квадрат, извлечения корня и т.п.), ограничивающих точность и быстродействие (при программной реализации в микропроцессоре).

Сущность предлагаемого изобретения заключается в том, что в устройство некогерентного обнаружителя сигнала в шумах введены первый и второй компараторы напряжений, логическая схема "ИСКЛЮЧАЮЩЕЕ ИЛИ", счетчик-делитель на 2n, N-разрядный накапливающий сумматор, третий компаратор чисел и m-разрядный регистр, выход одного из фильтров промежуточной частоты соединен с сигнальным входом аналого-цифрового преобразователя и неинвертирующим входом первого компаратора напряжений, выход второго фильтра соединен с неинвертирующим входом второго компаратора напряжений, инвертирующие входы упомянутых компараторов соединены с нулевым потенциалом, выходы первого и второго компараторов соединены с первым и вторым входами логической схемы "ИСКЛЮЧАЮЩЕЕ ИЛИ", выход упомянутой схемы соединен с тактовым входом упомянутого аналого-цифрового преобразователя и с входом счетчика-делителя на n, шина цифрового выхода упомянутого аналого-цифрового преобразователя без знакового разряда соединена с входом N-разрядного накапливающего сумматора, m= N-n выходных старших разрядов накапливающего сумматора соединены с входом компаратора чисел, второй вход компаратора чисел соединен с выходом m-разрядного регистра, в который записан двоичный код порога, управляющий вход упомянутого компаратора чисел соединен с выходом упомянутого счетчика-делителя на n.

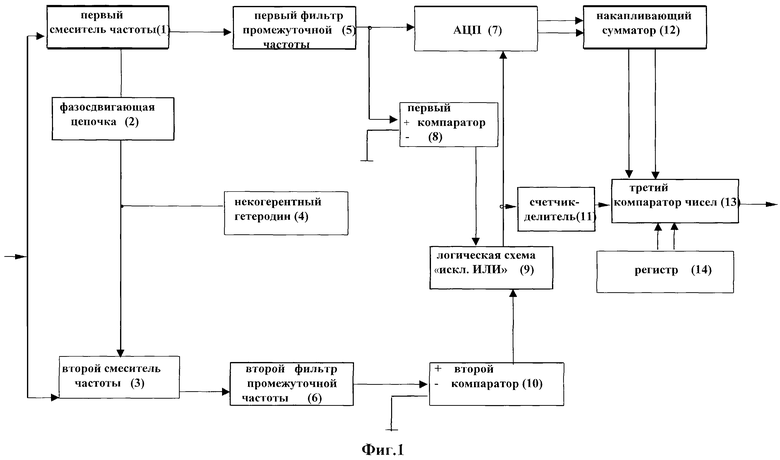

Технический результат достигается тем, что Аi в формуле (1) формируется как  в момент времени ti, когда Q(ti)=0 (см. фиг.2). Из фиг.2 видно, что I(t) Q(t) суть проекции вектора A(t) на оси прямоугольной системы координат (фазовой плоскости). Вектор A(t) вращается в этой плоскости с частотой сигнала промежуточной частоты. Очевидно, что I и Q можно поменять местами.

в момент времени ti, когда Q(ti)=0 (см. фиг.2). Из фиг.2 видно, что I(t) Q(t) суть проекции вектора A(t) на оси прямоугольной системы координат (фазовой плоскости). Вектор A(t) вращается в этой плоскости с частотой сигнала промежуточной частоты. Очевидно, что I и Q можно поменять местами.

Совокупность перечисленных признаков позволяет улучшить точность и быстродействие устройства.

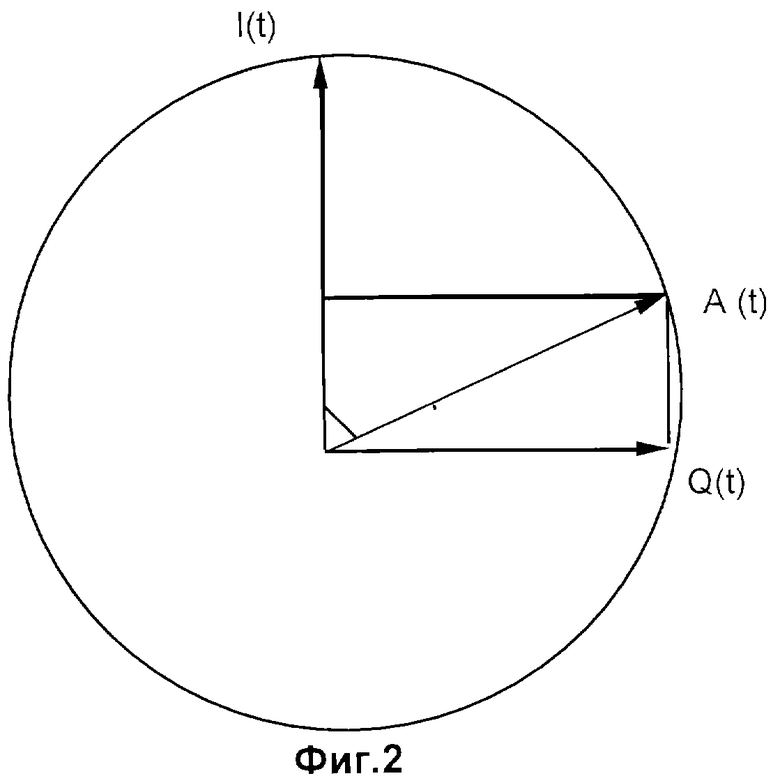

На фиг.1 дана схема предлагаемого устройства.

На фиг. 2 - представление сигнала мгновенной амплитуды А(t) в фазовой плоскости.

Устройство содержит: 1, 3 - первый и второй смесители частот; 2 - фазосдвигающая цепочка; 4 - некогерентный гетеродин; 5, 6 - первый и второй фильтры промежуточной частоты; 7 - аналого-цифровой преобразователь; 8, 10 - первый и второй компараторы напряжений, 9 - логическая схема "ИСКЛЮЧАЮЩЕЕ ИЛИ", 11 - счетчик-делитель на 2n, 12 - N-разрядный накапливающий сумматор, 13 - третий компаратор чисел, 14 - регистр.

Устройство работает следующим образом.

Входной сигнал (в смеси с шумом) поступает на сигнальные входы двух одинаковых смесителей частот (1, 3). На гетеродинный вход смесителя 3 подается непосредственно от некогерентного гетеродина 4, а на гетеродинный вход другого смесителя 4 через фазосдвигающую цепочку на 90 градусов. С выходов этих смесителей необходимая промежуточная частота (разностная или суммарная) выделяется блоками ФПЧ (5, 6) в каждом из квадратурных каналов (при необходимости в них же осуществляется усиление промежуточных частот).

С выхода ФПЧ (5) сигнал поступает одновременно на сигнальный вход АЦП. С выхода ФПЧ (6) - только на инвертирующий вход компаратора (8). Инвертирующие входы этих компараторов соединены с нулевым потенциалом.

Выходы компараторов через схему "ИСКЛЮЧАЮЩЕЕ ИЛИ" (9) соединены с тактовым входом АЦП. На выходе схемы присутствует квазимеандр удвоенной промежуточной частоты и тактирование АЦП (снятие отсчетов) осуществляется дважды за период сигнала - один раз при его положительной полуволне, второй раз - при отрицательной.

Идеальное некогерентное детектирование реализуется тем, что на вход накапливающего сумматора 12 подается число с выхода АЦП без знакового разряда (модуль оценки зашумленной амплитуды).

Накапливающий сумматор 12 осуществляет усредненные выборки в соответствии с формулой.

Разрядность сумматора 12 N определяется из условия непереполнения его при суммировании 2n отсчетов выборки с АЦП, где n - число периодов промежуточной частоты сигнала, усреднение которых обеспечивает обнаружение сигнала с заданными вероятностями пропуска (ложной тревоги).

Собственно операция усреднения с округлениями (деления накопленной суммы на число слагаемых - в предлагаемом устройстве 2n) осуществляется отбрасыванием n младших разрядов накапливающего сумматора и сравнения оставшихся N-n разрядов с m разрядным кодом порога решения из регистра 14 в третьем компараторе чисел 13 по сигналу с делителя 11 на 2n.

Источники информации

1. Каталог - проспект фирмы Geс Plessey, PRELIMINARY INFORMATION, DS3884-1,0, PYTHAGORAS PROCESSOR - PDSP16330/A/B, с. 145-146.

2. Радиоприемные устройства /Под. ред. проф. А.П.Жуковского - M.: Высшая школа, 1989.

3. Бортовые устройства спутниковой радионавигации /И.В.Кудрявцев, И.Н. Мищенко, А.И.Волынкин - М.: Транспорт, 1988/.

| название | год | авторы | номер документа |

|---|---|---|---|

| НЕКОГЕРЕНТНЫЙ ОБНАРУЖИТЕЛЬ РАДИОСИГНАЛОВ В ШУМАХ | 2000 |

|

RU2187198C2 |

| НЕКОГЕРЕНТНЫЙ ФОРМИРОВАТЕЛЬ ОГИБАЮЩЕЙ ПСЕВДОШУМОВОГО ФАЗОМАНИПУЛИРОВАННОГО СИГНАЛА | 2008 |

|

RU2411678C2 |

| СПОСОБ И УСТРОЙСТВО БЕСФИЛЬТРОВОГО ПРЕОБРАЗОВАНИЯ ЧАСТОТЫ | 2008 |

|

RU2414042C2 |

| СПОСОБ И УСТРОЙСТВО БЕСКОДОВОГО ПРИЕМА СИГНАЛОВ СПУТНИКОВЫХ НАВИГАЦИОННЫХ СИСТЕМ | 2007 |

|

RU2363099C2 |

| РАДИОПРИЕМНОЕ УСТРОЙСТВО КОГЕРЕНТНОЙ РЛС С ОПТИМАЛЬНОЙ ФИЛЬТРАЦИЕЙ СИГНАЛА | 2003 |

|

RU2255351C1 |

| КОГЕРЕНТНЫЙ ПРИЕМНИК РЛС С ЦИФРОВЫМ УСТРОЙСТВОМ ДЛЯ АМПЛИТУДНОЙ И ФАЗОВОЙ КОРРЕКТИРОВКИ КВАДРАТУРНЫХ СОСТАВЛЯЮЩИХ ПРИНИМАЕМОГО СИГНАЛА | 2004 |

|

RU2273860C2 |

| ПРИЕМНИК АППАРАТУРЫ ПОТРЕБИТЕЛЕЙ СИГНАЛОВ ГЛОБАЛЬНЫХ СПУТНИКОВЫХ НАВИГАЦИОННЫХ СИСТЕМ | 2007 |

|

RU2416102C2 |

| ФАЗОВЫЙ ПЕЛЕНГАТОР | 2013 |

|

RU2536440C1 |

| МОНОИМПУЛЬСНАЯ РЛС | 2004 |

|

RU2267137C1 |

| ЦИФРОВОЙ ПРИЕМНИК СПУТНИКОВОЙ НАВИГАЦИИ | 1995 |

|

RU2090902C1 |

Изобретение относится к приемникам радиосвязи и радионавигации, в том числе с использованием псевдошумовых сигналов с фазовой или частотной манипуляцией. Некогерентный обнаружитель сигналов в шумах содержит первый и второй смесители частот, фазосдвигающую цепочку, гетеродин, первый и второй фильтры промежуточной частоты, аналого-цифровой преобразователь, первый и второй компараторы напряжений, логическую схему ИСКЛЮЧАЮЩЕЕ ИЛИ, счетчик-делитель на 2n, N-разрядный накапливающий сумматор, компаратор чисел и m-разрядный регистр. Техническим результатом является создание устройства, реализующего точный алгоритм аппаратно без нелинейных операций, ограничивающих точность и быстродействие. 2 ил.

Некогерентный обнаружитель сигнала в шумах, включающий некогерентный гетеродин, фазосдвигающую цепочку, аналого-цифровой преобразователь, первый и второй смесители частот, первый и второй фильтры промежуточной частоты, первые входы упомянутых смесителей соединены с входом сигнала, второй вход первого смесителя соединен с выходом гетеродина через фазосдвигающую цепочку, второй вход второго смесителя частоты соединен также с выходом гетеродина, выходы первого и второго смесителей соединены с входами первого и второго фильтров промежуточной частоты соответственно, отличающийся тем, что в схему введены первый и второй компараторы напряжений, логическая схема Исключающее ИЛИ, счетчик-делитель на 2n, N-разрядный накапливающий сумматор, компаратор чисел и m-разрядный регистр, выход одного из фильтров промежуточной частоты соединен с сигнальным входом аналого-цифрового преобразователя и неинвертирующим входом первого компаратора напряжений, выход второго фильтра соединен с неинвертирующим входом второго компаратора напряжений, инвертирующие входы упомянутых компараторов соединены с нулевым потенциалом, выходы первого и второго компараторов соединены с первым и вторым входами логической схемы Исключающее ИЛИ, выход упомянутой схемы соединен с тактовым входом упомянутого аналого-цифрового преобразователя и с входом счетчика-делителя на 2n, шина цифрового выхода упомянутого аналого-цифрового преобразователя без знакового разряда соединена с входом N-разрядного накапливающего сумматора, m= N-n выходных старших разрядов накапливающего сумматора соединены с входом компаратора чисел, второй вход компаратора чисел соединен с выходом m-разрядного регистра, в который записан двоичный код порога, управляющий вход упомянутого компаратора чисел соединен с выходом упомянутого счетчика-делителя на 2n, где n - число периодов промежуточной частоты сигнала, усреднение которых обеспечивает обнаружение сигнала с заданной вероятностью ложной тревоги.

| Радиоприемные устройства /Под ред | |||

| проф | |||

| А.П | |||

| ЖУКОВСКОГО - М.: Высшая школа, 1989, с | |||

| Крутильный аппарат | 1922 |

|

SU234A1 |

| Радиотехнические системы /Под ред | |||

| проф | |||

| Ю.М | |||

| КАЗАРИНОВА -М.: Высшая школа, 1990, с | |||

| Приспособление для плетения проволочного каркаса для железобетонных пустотелых камней | 1920 |

|

SU44A1 |

| US 4315261, 09.12.1982 | |||

| US 3611369, 05.11.1971. | |||

Авторы

Даты

2003-02-27—Публикация

2000-02-03—Подача