Изобретение относится к радиотехнике, в частности к приемникам радиосвязи и радионавигации, в том числе с использованием псевдошумовых сигналов с фазовой или частотной манипуляцией.

Наиболее близким прототипом предлагаемого устройства является некогерентный обнаружитель сигнала в шумах по заявке 2000102468, включающий некогерентный гетеродин, фазосдвигающую цепочку, аналого-цифровой преобразователь, первый и второй смесители частот, первый и второй фильтры промежуточной частоты, первый и второй компараторы напряжений, логическую схему ИСКЛЮЧАЮЩЕЕ ИЛИ, счетчик-делитель на 2n, N-разрядный накапливающий сумматор, компаратор чисел и m-разрядный регистр [1].

Недостатком прототипа является недостаточная точность.

Техническим результатом настоящего изобретения является повышение точности некогерентного формирования оценки амплитуды за счет удвоения числа усредняемых элементов выборки (независимых в современных приемниках широкополосных сигналов) за один период промежуточной частоты.

Сущность предлагаемого изобретения заключается в том, что в устройство некогерентного обнаружителя сигнала в шумах введены второй аналого-цифровой преобразователь, мультиплексор, схема НЕ, причем первый вход второго аналого-цифрового преобразователя соединен с выходом второго фильтра промежуточной частоты, второй вход соединен с выходом схемы НЕ, вход которой является выходом логической схемы ИСКЛЮЧАЮЩЕЕ ИЛИ, шина выхода второго аналого-цифрового преобразователя является первым входом мультиплексора, второй вход мультиплексора соединен с шиной выхода первого аналого-цифрового преобразователя, а шина выхода мультиплексора является входом накапливающего сумматора.

Технический результат в предлагаемом изобретении достигается тем, что в устройстве некогерентной обработки сигнала квадратурные компоненты I и Q равнозначны. Это не синфазная и квадратурная составляющие, как в когерентных системах, а всего лишь опережающая I и задержанная Q выборки, поэтому в некогерентном обнаружителе можно получить не два отсчета за период промежуточной частоты, а четыре: два отсчета I в моменты, когда Q проходит через нуль и еще два отсчета Q, когда через нуль проходит I.

Сигналы пересечения нуля компонентами I и Q формируется логической схемой ИСКЛЮЧАЮЩЕЕ ИЛИ: передние фронты - это переход запаздывающей компоненты Q через нуль, задние фронты - переход опережающей компоненты I через нуль.

Совокупность перечисленных признаков позволяет улучшить точность и быстродействие устройства.

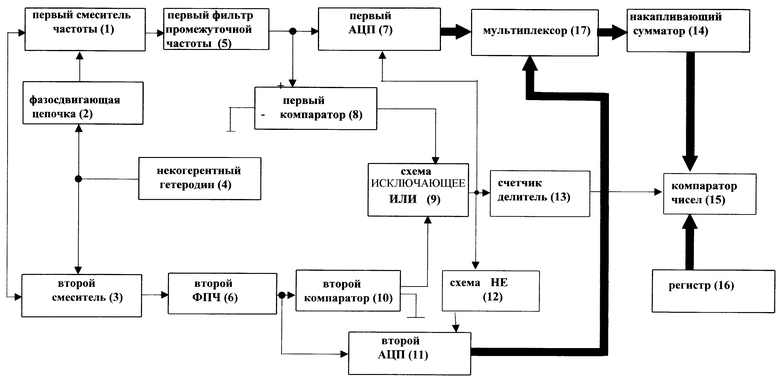

На чертеже показана схема предлагаемого устройства.

Некогерентный обнаружитель радиосигналов в шумах содержит 1, 3 - первый и второй смесители частот; 2 - фазосдвигающая цепочка; 4 - некогерентный гетеродин; 5, 6 - первый и второй фильтры промежуточной частоты; 7, 11 - первый и второй аналого-цифровой преобразователь; 8, 10 - первый и второй компараторы напряжений; 9 - логическая схема ИСКЛЮЧАЮЩЕЕ ИЛИ; 12 - схема НЕ; 13 - счетчик делитель на 2n; 14 - N-разрядный накапливающий сумматор; 15 - компаратор чисел; 16 - регистр, в который записывают двоичный код порога принятия решения о наличии сигнала; 17 - мультиплексор.

Устройство работает следующим образом.

Фазосдвигающая цепочка 2 сдвигает фазу сигнала некогерентного гетеродина 4 на 90o. Гетеродин 4 в режиме обнаружения сигнала всегда некогерентный, так как еще им не засинхронизирован. Первый 5 и второй 6 одинаковые смесители частоты особенностей не имеют. Первый 5 и второй 6 одинаковые фильтры промежуточной частоты (ФПЧ) выделяют нужную частоту преобразования (разностную или суммарную), подавляя остальные ненужные частоты.

Аналоговые сигналы (опережающий и задержанный на 90o, соответственно с выходов этих ФПЧ) поступают на сигнальные входы одинаковых компараторов 8 и 10 напряжений.

Входы опорных сигналов этих компараторов 8 и 10 напряжений заземляют.

На выходах этих компараторов образуются опережающая и задержанная (соответственно) бинарные последовательности в виде квазимеандров промежуточной частоты.

Аналоговые сигналы с выходов ФПЧ 5 и 6 поступают также и на входы аналого-цифровых преобразователей (АЦП) 7 и 11 соответственно.

Фронты импульсов бинарной последовательности с выхода элемента 9 фиксируют снятие отсчетов в АЦП - передние фронты непосредственно первый АЦП 7, задние, через инвертор 12, или с инверсного выхода элемента 9 - второй АЦП 11.

Если применяемые АЦП формируют цифровые отсчеты по передним фронтам тактирующих импульсов, то для правильной работы схемы необходимо, чтобы фазосдвигающая цепочка 2 осуществляла опережение фазы на 90o.

Если эти условия не выполняются, то придется поменять местами прямой и инверсный выходы логической схемы ИСКЛЮЧАЮЩЕЕ ИЛИ, так, чтобы АЦП опережающего канала формировал свои отсчеты в моменты, когда сигнал в запаздывающем канале пересекает нуль (меняет знак) и наоборот.

Этим достигается удвоение количества независимых зашумленных отсчетов модуля амплитуды (четыре отсчета за 1 период промежуточной частоты), что улучшает их сглаживание до пороговой схемы принятия решения.

Цифровые потоки разновременных отсчетов модуля амплитуды сигнала (без знаковых разрядов) с выходов первого АЦП 7 и второго АЦП 11 объединяются мультиплексором 17 и подаются для усреднения на накапливающий сумматор 14. Усреднение в 2m раз осуществляется в сумматоре 14 за счет того, что m его младших разрядов не участвуют в сравнении с порогом принятия решения. Сравнение усредненной амплитуды с порогом принятия решения, код которого записывают в регистр 16, осуществляется компаратором чисел 15 по команде со счетчика делителя 13 разрядностью не менее m+3 (на выходе элемента 9 - удвоенная промежуточная частота, а за каждый период ПЧ формируется четыре отсчета амплитуды).

В схему устройства включены второй АЦП 11 (в канал Q), схема НЕ 12 для инвертирования выходного сигнала с логической схемы ИСКЛЮЧАЮЩЕЕ ИЛИ, еще один разряд в счетчик делитель 13, управляющий снятием отсчета с компаратора чисел, а также мультиплексор цифровых потоков от двух АЦП.

Отличия в работе предлагаемого устройства от прототипа заключается в том, что с обоих выходов фильтров промежуточной частоты сигналы поступают одновременно на сигнальные входы АЦП и на неинвертирующие входы компараторов напряжения 8 и 10. Передние фронты выходных импульсов схемы ИСКЛЮЧАЮЩЕЕ ИЛИ управляют снятием отсчетов АЦП канала I, а задние фронты, после инвертирования в схеме НЕ становятся передними и управляют снятием отсчетов АЦП канала Q. Цифровые потоки с этих АЦП (отсчеты их разновременны) объединяются мультиплексором и подаются в накапливающий сумматор.

Источники информации

1. Некогерентный обнаружитель радиосигналов в шумах. Патент Украины 36305, МКВ Н 04 В 1/06, 16.04.2001.

| название | год | авторы | номер документа |

|---|---|---|---|

| НЕКОГЕРЕНТНЫЙ ОБНАРУЖИТЕЛЬ СИГНАЛОВ В ШУМАХ | 2000 |

|

RU2199762C2 |

| НЕКОГЕРЕНТНЫЙ ФОРМИРОВАТЕЛЬ ОГИБАЮЩЕЙ ПСЕВДОШУМОВОГО ФАЗОМАНИПУЛИРОВАННОГО СИГНАЛА | 2008 |

|

RU2411678C2 |

| СПОСОБ И УСТРОЙСТВО БЕСФИЛЬТРОВОГО ПРЕОБРАЗОВАНИЯ ЧАСТОТЫ | 2008 |

|

RU2414042C2 |

| СПОСОБ ИЗМЕРЕНИЯ УГЛОВЫХ КООРДИНАТ ЦЕЛЕЙ В МОНОИМПУЛЬСНОЙ ОБЗОРНОЙ РЛС И МОНОИМПУЛЬСНАЯ ОБЗОРНАЯ РЛС | 2004 |

|

RU2270458C1 |

| СПОСОБ И УСТРОЙСТВО БЕСКОДОВОГО ПРИЕМА СИГНАЛОВ СПУТНИКОВЫХ НАВИГАЦИОННЫХ СИСТЕМ | 2007 |

|

RU2363099C2 |

| ПРИЕМНИК АППАРАТУРЫ ПОТРЕБИТЕЛЕЙ СИГНАЛОВ ГЛОБАЛЬНЫХ СПУТНИКОВЫХ НАВИГАЦИОННЫХ СИСТЕМ | 2007 |

|

RU2416102C2 |

| ДЕМОДУЛЯТОР ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ | 2008 |

|

RU2393641C1 |

| КОГЕРЕНТНЫЙ ПРИЕМНИК РЛС С ЦИФРОВЫМ УСТРОЙСТВОМ ДЛЯ АМПЛИТУДНОЙ И ФАЗОВОЙ КОРРЕКТИРОВКИ КВАДРАТУРНЫХ СОСТАВЛЯЮЩИХ ПРИНИМАЕМОГО СИГНАЛА | 2004 |

|

RU2273860C2 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ТЕХНИЧЕСКИХ ПАРАМЕТРОВ АВАРИЙНЫХ РАДИОМАЯКОВ/РАДИОБУЕВ | 2011 |

|

RU2453860C1 |

| ФАЗОВЫЙ ПЕЛЕНГАТОР | 2013 |

|

RU2543065C1 |

Изобретение относится к радиотехнике, в частности к приемникам в радиосвязи и радионавигации, в том числе с использованием псевдошумовых сигналов с фазовой или частотной манипуляцией. Техническим результатом настоящего изобретения является повышение точности некогерентного формирования оценки амплитуды за счет удвоения числа усредняемых элементов выборки (независимых в современных приемниках широкополосных сигналов) за один период промежуточной частоты. Некогерентный обнаружитель радиосигналов в шумах содержит первый и второй смесители частот, фазосдвигающую цепочку, некогерентный гетеродин, первый и второй фильтры промежуточной частоты, первый и второй аналого-цифровые преобразователи, первый и второй компараторы напряжений, логическую схему ИСКЛЮЧАЮЩЕЕ ИЛИ, схему НЕ, счетчик-делитель, накапливающий сумматор, компаратор чисел, регистр, в который записывают двоичный код порога принятия решения о наличии сигнала, мультиплексор. 1 ил.

Некогерентный обнаружитель сигнала в шумах, включающий некогерентный гетеродин, фазосдвигающую цепочку, первый аналого-цифровой преобразователь, первый и второй смесители частот, первый и второй фильтры промежуточной частоты, первый и второй компараторы напряжений, логическую схему ИСКЛЮЧАЮЩЕЕ ИЛИ, счетчик-делитель, накапливающий сумматор, компаратор чисел, регистр, в который записан двоичный код порога, причем на первые входы первого и второго смесителей подают входной сигнал, второй вход первого смесителя соединен с выходом некогерентного гетеродина через фазосдвигающую цепочку, второй вход второго смесителя частоты соединен также с выходом некогерентного гетеродина, выходы первого и второго смесителей соединены с входами первого и второго фильтров промежуточной частоты соответственно, выход первого фильтра промежуточной частоты соединен с сигнальным входом первого аналого-цифрового преобразователя и неинвертирующим входом первого компаратора напряжений, выход второго фильтра промежуточной частоты соединен с неинвертирующим входом второго компаратора напряжений, инвертирующие входы упомянутых компараторов соединены с нулевым потенциалом, выходы первого и второго компараторов соединены с первым и вторым входами логической схемы ИСКЛЮЧАЮЩЕЕ ИЛИ, выход упомянутой схемы соединен с тактовым входом первого аналого-цифрового преобразователя и с входом счетчика-делителя, шина выхода накапливающего сумматора соединена с входом компаратора чисел, второй вход компаратора чисел соединен с выходом регистра, в который записан двоичный код порога, управляющий вход упомянутого компаратора чисел соединен с выходом упомянутого счетчика-делителя, отличающийся тем, что в него введены второй аналого-цифровой преобразователь, мультиплексор, схема НЕ, причем первый вход второго аналого-цифрового преобразователя соединен с выходом второго фильтра промежуточной частоты, второй вход соединен с выходом схемы НЕ, вход которой является выходом логической схемы ИСКЛЮЧАЮЩЕЕ ИЛИ, шина выхода второго аналого-цифрового преобразователя является первым входом мультиплексора, второй вход мультиплексора соединен с шиной выхода первого аналого-цифрового преобразователя, а шина выхода мультиплексора является входом накапливающего сумматора.

| Квазиоптимальный некогерентный обнаружитель сигнала с псевдослучайной перестройкой рабочей частоты | 1988 |

|

SU1569998A1 |

| Устройство обнаружения шумоподобных сигналов | 1987 |

|

SU1584112A2 |

| US 4126828, 27.11.1978 | |||

| US 4879729, 07.11.1989 | |||

| Способ водопонижения при проходке щитом шахтного ствола | 1971 |

|

SU546723A1 |

| Приводной механизм тормоза | 1979 |

|

SU898174A1 |

Авторы

Даты

2002-08-10—Публикация

2000-09-11—Подача